Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2010                       |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | ARM® Cortex®-M4                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 84MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SDIO, SPI, UART/USART, USB OTG        |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT          |

| Number of I/O              | 50                                                                    |

| Program Memory Size        | 512KB (512K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 96K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                           |

| Data Converters            | A/D 16x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f401ret6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3 Functional overview

# 3.1 ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU core with embedded Flash and SRAM

The ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU processor is the latest generation of ARM processors for embedded systems. It was developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced response to interrupts.

The ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU 32-bit RISC processor features exceptional codeefficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices. The processor supports a set of DSP instructions which allow efficient signal processing and complex algorithm execution. Its single precision FPU (floating point unit) speeds up software development by using metalanguage development tools, while avoiding saturation.

The STM32F401xD/xE devices are compatible with all ARM tools and software.

Figure 3 shows the general block diagram of the STM32F401xD/xE.

Note: Cortex<sup>®</sup>-M4 with FPU is binary compatible with Cortex<sup>®</sup>-M3.

## 3.2 Adaptive real-time memory accelerator (ART Accelerator<sup>™</sup>)

The ART Accelerator<sup>™</sup> is a memory accelerator which is optimized for STM32 industrystandard ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU processors. It balances the inherent performance advantage of the ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU over Flash memory technologies, which normally requires the processor to wait for the Flash memory at higher frequencies.

To release the processor full 105 DMIPS performance at this frequency, the accelerator implements an instruction prefetch queue and branch cache, which increases program execution speed from the 128-bit Flash memory. Based on CoreMark benchmark, the performance achieved thanks to the ART accelerator is equivalent to 0 wait state program execution from Flash memory at a CPU frequency up to 84 MHz.

## 3.3 Memory protection unit

The memory protection unit (MPU) is used to manage the CPU accesses to memory to prevent one task to accidentally corrupt the memory or resources used by any other active task. This memory area is organized into up to 8 protected areas that can in turn be divided up into 8 subareas. The protection area sizes are between 32 bytes and the whole 4 gigabytes of addressable memory.

The MPU is especially helpful for applications where some critical or certified code has to be protected against the misbehavior of other tasks. It is usually managed by an RTOS (real-time operating system). If a program accesses a memory location that is prohibited by the MPU, the RTOS can detect it and take action. In an RTOS environment, the kernel can dynamically update the MPU area setting, based on the process to be executed.

The MPU is optional and can be bypassed for applications that do not need it.

DocID025644 Rev 3

## 3.9 Nested vectored interrupt controller (NVIC)

The devices embed a nested vectored interrupt controller able to manage 16 priority levels, and handle up to 62 maskable interrupt channels plus the 16 interrupt lines of the  $Cortex^{\$}$ -M4 with FPU.

- Closely coupled NVIC gives low-latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Allows early processing of interrupts

- Processing of late arriving, higher-priority interrupts

- Support tail chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimum interrupt latency.

## 3.10 External interrupt/event controller (EXTI)

The external interrupt/event controller consists of 21 edge-detector lines used to generate interrupt/event requests. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 81 GPIOs can be connected to the 16 external interrupt lines.

## 3.11 Clocks and startup

On reset the 16 MHz internal RC oscillator is selected as the default CPU clock. The 16 MHz internal RC oscillator is factory-trimmed to offer 1% accuracy at 25 °C. The application can then select as system clock either the RC oscillator or an external 4-26 MHz clock source. This clock can be monitored for failure. If a failure is detected, the system automatically switches back to the internal RC oscillator and a software interrupt is generated (if enabled). This clock source is input to a PLL thus allowing to increase the frequency up to 84 MHz. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example if an indirectly used external oscillator fails).

Several prescalers allow the configuration of the two AHB buses, the high-speed APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the two AHB buses is 84 MHz while the maximum frequency of the high-speed APB domains is 84 MHz. The maximum allowed frequency of the low-speed APB domain is 42 MHz.

The devices embed a dedicated PLL (PLLI2S) which allows to achieve audio class performance. In this case, the I<sup>2</sup>S master clock can generate all standard sampling frequencies from 8 kHz to 192 kHz.

## 3.12 Boot modes

At startup, boot pins are used to select one out of three boot options:

- Boot from user Flash

- Boot from system memory

- Boot from embedded SRAM

The boot loader is located in system memory. It is used to reprogram the Flash memory by using either USART1(PA9/10), USART2(PD5/6), USB OTG FS in device mode (PA11/12) through DFU (device firmware upgrade), I2C1(PB6/7), I2C2(PB10/3), I2C3(PA8/PB4), SPI1(PA4/5/6/7), SPI2(PB12/13/14/15) or SPI3(PA15, PC10/11/12).

For more detailed information on the bootloader, refer to Application Note: AN2606, *STM32™ microcontroller system memory boot mode*.

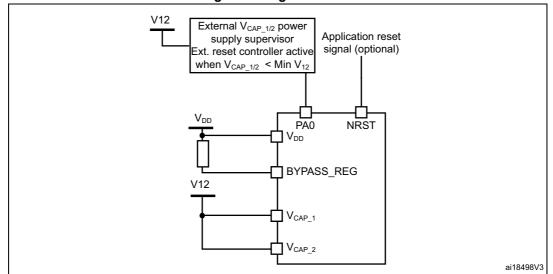

## 3.13 **Power supply schemes**

- V<sub>DD</sub> = 1.7 to 3.6 V: external power supply for I/Os with the internal supervisor (POR/PDR) disabled, provided externally through V<sub>DD</sub> pins. Requires the use of an external power supply supervisor connected to the VDD and PDR\_ON pins.

- V<sub>DD</sub> = 1.8 to 3.6 V: external power supply for I/Os and the internal regulator (when enabled), provided externally through V<sub>DD</sub> pins.

- $V_{SSA}$ ,  $V_{DDA}$  = 1.7 to 3.6 V: external analog power supplies for ADC, Reset blocks, RCs and PLL.  $V_{DDA}$  and  $V_{SSA}$  must be connected to  $V_{DD}$  and  $V_{SS}$ , respectively, with decoupling technique.

- V<sub>BAT</sub> = 1.65 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

Refer to *Figure 18: Power supply scheme* for more details.

The following conditions must be respected:

- V<sub>DD</sub> should always be higher than V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to avoid current injection between power domains.

- If the time for V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to reach V<sub>12</sub> minimum value is faster than the time for V<sub>DD</sub> to reach 1.7 V, then PA0 should be kept low to cover both conditions: until V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> reach V<sub>12</sub> minimum value and until V<sub>DD</sub> reaches 1.7 V (see *Figure 8*).

- Otherwise, if the time for  $V_{CAP_1}$  and  $V_{CAP_2}$  to reach  $V_{12}$  minimum value is slower than the time for  $V_{DD}$  to reach 1.7 V, then PA0 could be asserted low externally (see *Figure 9*).

- If  $V_{CAP_1}$  and  $V_{CAP_2}$  go below  $V_{12}$  minimum value and  $V_{DD}$  is higher than 1.7 V, then a reset must be asserted on PA0 pin.

- Note: The minimum value of V<sub>12</sub> depends on the maximum frequency targeted in the application

5

| 4        |

|----------|

| <u>%</u> |

| 3        |

| Οī       |

|        |      |        |           |                     |                          |                    |                                       |                          |                                 |        | ,             |         |      |              |      |      |              |

|--------|------|--------|-----------|---------------------|--------------------------|--------------------|---------------------------------------|--------------------------|---------------------------------|--------|---------------|---------|------|--------------|------|------|--------------|

| Por    |      | AF00   | AF01      | AF02                | AF03                     | AF04               | AF05                                  | AF06                     | AF07                            | AF08   | AF09          | AF10    | AF11 | AF12         | AF13 | AF14 | AF15         |

|        | Port | SYS_AF | TIM1/TIM2 | TIM3/<br>TIM4/ TIM5 | TIM9/<br>TIM10/<br>TIM11 | I2C1/I2C2/<br>I2C3 | SPI1/SPI2/<br>I2S2/SPI3/<br>I2S3/SPI4 | SPI2/I2S2/<br>SPI3/ I2S3 | SPI3/I2S3/<br>USART1/<br>USART2 | USART6 | 12C2/<br>12C3 | OTG1_FS |      | SDIO         |      |      |              |

|        | PD0  | -      | -         | -                   | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD1  | -      | -         | -                   | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD2  | -      | -         | TIM3_ETR            | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | SDIO_<br>CMD | -    | -    | EVENT<br>OUT |

|        | PD3  | -      | -         | -                   | -                        | -                  | SPI2_SCK/<br>I2S2_CK                  | -                        | USART2_<br>CTS                  |        | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD4  | -      | -         | -                   | -                        | -                  | -                                     | -                        | USART2_<br>RTS                  |        | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD5  | -      | -         | -                   | -                        | -                  | -                                     | -                        | USART2_<br>TX                   | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD6  | -      | -         | -                   | -                        | -                  | SPI3_MOSI<br>/I2S3_SD                 | -                        | USART2_<br>RX                   | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

| Q      | PD7  | -      | -         | -                   | -                        | -                  | -                                     | -                        | USART2_<br>CK                   | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

| Port D | PD8  | -      | -         | -                   | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD9  | -      | -         | -                   | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD10 | -      | -         | -                   | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD11 | -      | -         | -                   | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD12 | -      | -         | TIM4_CH1            | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD13 | -      | -         | TIM4_CH2            | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD14 | -      | -         | TIM4_CH3            | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD15 | -      | -         | TIM4_CH4            | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

STM32F401xD STM32F401xE

Pinouts and pin description

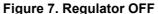

#### 6.1.6 Power supply scheme

#### Figure 18. Power supply scheme

1. To connect PDR\_ON pin, refer to Section 3.14: Power supply supervisor.

- 2. The 4.7  $\mu\text{F}$  ceramic capacitor must be connected to one of the  $V_{DD}$  pin.

- 3.  $V_{CAP_2}$  pad is only available on LQFP100 and UFBGA100 packages.

- 4.  $V_{DDA}=V_{DD}$  and  $V_{SSA}=V_{SS}$ .

- **Caution:** Each power supply pair (V<sub>DD</sub>/V<sub>SS</sub>, V<sub>DDA</sub>/V<sub>SSA</sub> ...) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB to ensure good operation of the device. It is not recommended to remove filtering capacitors to reduce PCB size or cost. This might cause incorrect operation of the device.

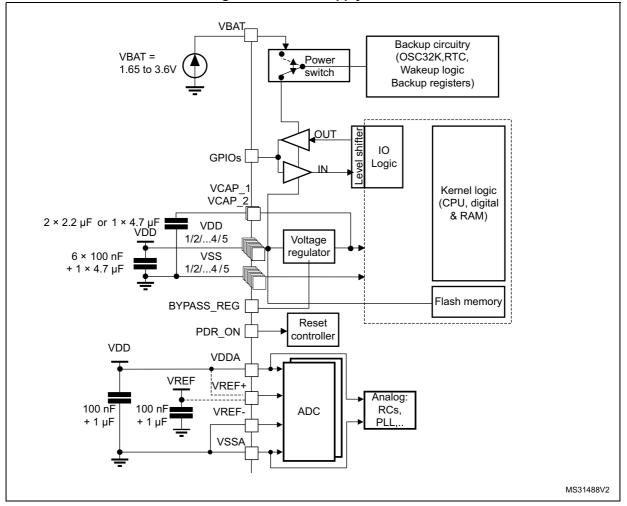

## 6.1.7 Current consumption measurement

#### Figure 19. Current consumption measurement scheme

## 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 11: Voltage characteristics*, *Table 12: Current characteristics*, and *Table 13: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                | Ratings                                                                        | Min                        | Max                                                                            | Unit |

|-----------------------|--------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------|------|

| $V_{DD} - V_{SS}$     | External main supply voltage (including $V_{DDA}, V_{DD}$ and $V_{BAT})^{(1)}$ | -0.3                       | 4.0                                                                            |      |

| V <sub>IN</sub>       | Input voltage on FT pins <sup>(2)</sup>                                        | V <sub>SS</sub> -0.3       | V <sub>DD</sub> +4.0                                                           | V    |

|                       | Input voltage on any other pin                                                 | V <sub>SS</sub> -0.3       | 4.0                                                                            |      |

|                       | Input voltage for BOOT0                                                        | V <sub>SS</sub>            | 9.0                                                                            |      |

| $ \Delta V_{DDx} $    | Variations between different V <sub>DD</sub> power pins                        | -                          | 50                                                                             | mV   |

| $ V_{SSX} - V_{SS} $  | Variations between all the different ground pins                               | -                          | 50                                                                             | IIIV |

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)                             | Absolute n<br>ratings (ele | see Section 6.3.14:<br>Absolute maximum<br>ratings (electrical<br>sensitivity) |      |

#### Table 11. Voltage characteristics

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. V<sub>IN</sub> maximum value must always be respected. Refer to *Table 12* for the values of the maximum allowed injected current.

| Symbol | Parameter                  | Conditions                                          | Min | Тур | Max | Unit |

|--------|----------------------------|-----------------------------------------------------|-----|-----|-----|------|

| TA     | Ambient temperature for 6  | Ambient temperature for 6 Maximum power dissipation |     | -   | 85  |      |

|        | suffix version             | Low power dissipation <sup>(8)</sup>                | -40 | -   | 105 |      |

|        | Ambient temperature for 7  | Maximum power dissipation                           | -40 | -   | 105 | °C   |

|        | suffix version             | Low power dissipation <sup>(8)</sup>                | -40 | -   | 125 |      |

| TJ     | lunction tomporaturo rango | 6 suffix version                                    | -40 | -   | 105 |      |

|        | Junction temperature range | 7 suffix version                                    | -40 | -   | 125 |      |

Table 14. General operating conditions (continued)

1. V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V with the use of an external power supply supervisor (refer to Section 3.14.2: Internal reset OFF).

2. When the ADC is used, refer to *Table 66: ADC characteristics*.

- 3. If  $V_{REF+}$  pin is present, it must respect the following condition:  $V_{DDA}-V_{REF+} < 1.2$  V.

- 4. It is recommended to power  $V_{DD}$  and  $V_{DDA}$  from the same source. A maximum difference of 300 mV between  $V_{DD}$  and  $V_{DDA}$  can be tolerated during power-up and power-down operation.

- 5. Guaranteed by test in production

- 6. To sustain a voltage higher than VDD+0.3, the internal Pull-up and Pull-Down resistors must be disabled

- 7. If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$ .

- 8. In low power dissipation state,  $T_A$  can be extended to this range as long as  $T_J$  does not exceed  $T_{Jmax}$ .

|                                                  | Table 15. F                          | eatures depe                                                                                            | nding on the ope                                                                  | erating power s                                    | upply range                                                                                                  |                                                  |

|--------------------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| Operating<br>power<br>supply<br>range            | ADC<br>operation                     | Maximum<br>Flash<br>memory<br>access<br>frequency<br>with no wait<br>states<br>(f <sub>Flashmax</sub> ) | Maximum Flash<br>memory access<br>frequency with<br>wait states <sup>(1)(2)</sup> | I/O operation                                      | Clock output<br>frequency on<br>I/O pins <sup>(3)</sup>                                                      | Possible<br>Flash<br>memory<br>operations        |

| V <sub>DD</sub> =1.7 to<br>2.1 V <sup>(4)</sup>  | Conversion<br>time up to<br>1.2 Msps | 20 MHz <sup>(5)</sup>                                                                                   | 84 MHz with 4<br>wait states                                                      | <ul> <li>No I/O compensation</li> </ul>            | up to 30 MHz                                                                                                 | 8-bit erase<br>and program<br>operations<br>only |

| V <sub>DD</sub> = 2.1 to<br>2.4 V                | Conversion<br>time up to<br>1.2 Msps | 22 MHz                                                                                                  | 84 MHz with 3<br>wait states                                                      | <ul> <li>No I/O compensation</li> </ul>            | up to 30 MHz                                                                                                 | 16-bit erase<br>and program<br>operations        |

| V <sub>DD</sub> = 2.4 to<br>2.7 V                | Conversion<br>time up to<br>2.4 Msps | 24 MHz                                                                                                  | 84 MHz with 3<br>wait states                                                      | <ul> <li>I/O<br/>compensation<br/>works</li> </ul> | up to 48 MHz                                                                                                 | 16-bit erase<br>and program<br>operations        |

| V <sub>DD</sub> = 2.7 to<br>3.6 V <sup>(6)</sup> | Conversion<br>time up to<br>2.4 Msps | 30 MHz                                                                                                  | 84 MHz with 2<br>wait states                                                      | <ul> <li>I/O<br/>compensation<br/>works</li> </ul> | - up to<br>84 MHz<br>when $V_{DD}$ =<br>3.0 to 3.6 V<br>- up to<br>48 MHz<br>when $V_{DD}$ =<br>2.7 to 3.0 V | 32-bit erase<br>and program<br>operations        |

| Perip                         | heral               | I <sub>DD</sub> (typ) | Unit   |

|-------------------------------|---------------------|-----------------------|--------|

|                               | TIM1                | 5.71                  |        |

|                               | TIM9                | 2.86                  | -      |

|                               | TIM10               | 1.79                  |        |

| <b>APB2</b> - (up to 84MHz) _ | TIM11               | 2.02                  |        |

|                               | ADC1 <sup>(2)</sup> | 2.98                  |        |

|                               | SPI1                | 1.19                  | µA/MHz |

|                               | USART1              | 3.10                  |        |

|                               | USART6              | 2.86                  | -      |

|                               | SDIO                | 5.95                  | -      |

|                               | SPI4                | 1.31                  |        |

|                               | SYSCFG              | 0.71                  |        |

1. I2SMOD bit set in SPI\_I2SCFGR register, and then the I2SE bit set to enable I2S peripheral.

2. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA for the analog part.

#### 6.3.7 Wakeup time from low-power modes

The wakeup times given in *Table 34* are measured starting from the wakeup event trigger up to the first instruction executed by the CPU:

- For Stop or Sleep modes: the wakeup event is WFE.

- WKUP (PA0) pin is used to wakeup from Standby, Stop and Sleep modes.

All timings are derived from tests performed under ambient temperature and  $V_{DD}$ =3.3 V.

| Table 34. Low-power mode wakeup timings <sup>(1)</sup> | Table 34 | ower | Low- | mode | wakeup | timings <sup>(1)</sup> |

|--------------------------------------------------------|----------|------|------|------|--------|------------------------|

|--------------------------------------------------------|----------|------|------|------|--------|------------------------|

| Symbol                                 | Parameter                                                                                   | Min <sup>(1)</sup> | Typ <sup>(1)</sup> | Max <sup>(1)</sup> | Unit                  |  |

|----------------------------------------|---------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|-----------------------|--|

| t <sub>WUSLEEP</sub> <sup>(2)</sup>    | Wakeup from Sleep mode                                                                      | -                  | 4                  | 6                  | CPU<br>clock<br>cycle |  |

| t <sub>wustop</sub> (2)                | Wakeup from Stop mode, usage of main regulator                                              | -                  | 13.5               | 14.5               |                       |  |

|                                        | Wakeup from Stop mode, usage of main regulator, Flash memory in Deep power down mode        | -                  | 105                | 111                | μs                    |  |

|                                        | Wakeup from Stop mode, regulator in low power mode                                          | -                  | 21                 | 33                 |                       |  |

|                                        | Wakeup from Stop mode, regulator in low power mode,<br>Flash memory in Deep power down mode | -                  | 113                | 130                |                       |  |

| t <sub>WUSTDBY</sub> <sup>(2)(3)</sup> | Wakeup from Standby mode                                                                    | -                  | 314                | 407                | μs                    |  |

1. Guaranteed by characterization, not tested in production.

2. The wakeup times are measured from the wakeup event to the point in which the application code reads the first instruction.

3.  $t_{WUSTDBY}$  maximum value is given at -40 °C.

## 6.3.8 External clock source characteristics

#### High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard I/O. The external clock signal has to respect the *Table 54*. However, the recommended clock input waveform is shown in *Figure 22*.

The characteristics given in *Table 35* result from tests performed using an high-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 14*.

| Symbol                                     | Parameter                                           | Conditions                                   | Min         | Тур | Max                | Unit |  |  |  |  |

|--------------------------------------------|-----------------------------------------------------|----------------------------------------------|-------------|-----|--------------------|------|--|--|--|--|

| f <sub>HSE_ext</sub>                       | External user clock source frequency <sup>(1)</sup> |                                              | 1           | -   | 50                 | MHz  |  |  |  |  |

| V <sub>HSEH</sub>                          | OSC_IN input pin high level voltage                 |                                              | $0.7V_{DD}$ | -   | V <sub>DD</sub>    | V    |  |  |  |  |

| V <sub>HSEL</sub>                          | OSC_IN input pin low level voltage                  |                                              | $V_{SS}$    | -   | $0.3V_{\text{DD}}$ | v    |  |  |  |  |

| t <sub>w(HSE)</sub><br>t <sub>w(HSE)</sub> | OSC_IN high or low time <sup>(1)</sup>              |                                              | 5           | -   | -                  | ns   |  |  |  |  |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub> | OSC_IN rise or fall time <sup>(1)</sup>             |                                              | -           | -   | 10                 | 115  |  |  |  |  |

| C <sub>in(HSE)</sub>                       | OSC_IN input capacitance <sup>(1)</sup>             |                                              | -           | 5   | -                  | pF   |  |  |  |  |

| $DuCy_{(HSE)}$                             | Duty cycle                                          |                                              | 45          | -   | 55                 | %    |  |  |  |  |

| ١ <sub>L</sub>                             | OSC_IN Input leakage current                        | $V_{SS} \! \leq \! V_{IN} \! \leq \! V_{DD}$ | -           | -   | ±1                 | μA   |  |  |  |  |

Table 35. High-speed external user clock characteristics

1. Guaranteed by design, not tested in production.

#### Low-speed external user clock generated from an external source

In bypass mode the LSE oscillator is switched off and the input pin is a standard I/O. The external clock signal has to respect the *Table 54*. However, the recommended clock input waveform is shown in *Figure 23*.

The characteristics given in *Table 36* result from tests performed using an low-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 14*.

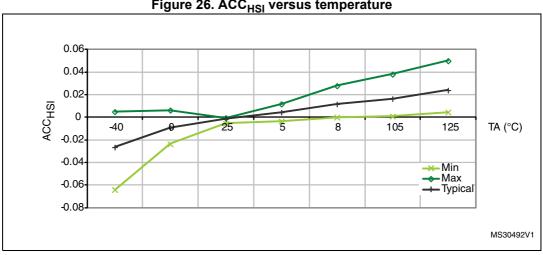

Figure 26. ACC<sub>HSI</sub> versus temperature

1. Guaranteed by characterization, not tested in production.

#### Low-speed internal (LSI) RC oscillator

| Table 40. | LSI oscillator | characteristics | (1) |

|-----------|----------------|-----------------|-----|

| Symbol                              | Parameter                        | Min | Тур | Мах | Unit |

|-------------------------------------|----------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub> <sup>(2)</sup>     | Frequency                        | 17  | 32  | 47  | kHz  |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time      | -   | 15  | 40  | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption | -   | 0.4 | 0.6 | μA   |

1.  $V_{DD}$  = 3 V, T<sub>A</sub> = -40 to 105 °C unless otherwise specified.

2. Guaranteed by characterization, not tested in production.

3. Guaranteed by design, not tested in production.

|                  |                                                                                                                                                                       | Functional s       |                    |      |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                                                                                                                                           | Negative injection | Positive injection | Unit |

|                  | Injected current on BOOT0 pin                                                                                                                                         | -0                 | NA                 |      |

| I <sub>INJ</sub> | Injected current on NRST pin                                                                                                                                          | -0                 | NA                 |      |

|                  | Injected current on PB3, PB4, PB5, PB6,<br>PB7, PB8, PB9, PC13, PC14, PC15, PH1,<br>PDR_ON, PC0, PC1,PC2, PC3, PD1,<br>PD5, PD6, PD7, PE0, PE2, PE3, PE4,<br>PE5, PE6 | -0                 | NA                 | mA   |

|                  | Injected current on any other FT pin                                                                                                                                  | -5                 | NA                 |      |

|                  | Injected current on any other pins                                                                                                                                    | -5                 | +5                 |      |

| Table 53. I/O current in | jection susce | ptibility <sup>(1)</sup> |

|--------------------------|---------------|--------------------------|

|--------------------------|---------------|--------------------------|

1. NA = not applicable.

*Note:* It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

## 6.3.16 I/O port characteristics

#### General input/output characteristics

Unless otherwise specified, the parameters given in *Table 54* are derived from tests performed under the conditions summarized in *Table 14*. All I/Os are CMOS and TTL compliant.

| Symbol          | Parameter                    | Conditions                                                                                            | Min                                     | Тур | Мах                                      | Unit |  |  |

|-----------------|------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------|-----|------------------------------------------|------|--|--|

|                 | FT, and NRST I/O input low   | 17//// 28//                                                                                           |                                         |     | 0.35V <sub>DD</sub> -0.04 <sup>(1)</sup> |      |  |  |

|                 | level voltage                | 1.7 V≤ V <sub>DD</sub> ≤ 3.6 V                                                                        | -                                       | -   | 0.3V <sub>DD</sub> <sup>(2)</sup>        |      |  |  |

| V <sub>IL</sub> | BOOT0 I/O input low level    | $1.75 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V},$<br>-40 °C $\le \text{T}_{A} \le 105 \text{ °C}$ | -                                       | -   |                                          | V    |  |  |

|                 | voltage                      | $1.7 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V},$<br>0 °C ≤ T <sub>A</sub> ≤ 105 °C                | -                                       | -   | 0.1V <sub>DD</sub> +0.1                  |      |  |  |

|                 | FT and NRST I/O input high   |                                                                                                       | 0.45V <sub>DD</sub> +0.3 <sup>(1)</sup> | -   | -                                        |      |  |  |

|                 | level voltage <sup>(5)</sup> | 1.7 V≤ V <sub>DD</sub> ≤ 3.6 V                                                                        | 0.4V <sub>DD</sub> <sup>(2)</sup>       |     |                                          |      |  |  |

| V <sub>IH</sub> | BOOT0 I/O input high level   | $1.75 V \le V_{DD} \le 3.6 V$ ,<br>-40 °C $\le T_A \le 105 °$ C                                       | 0.17V <sub>DD</sub> +0.7 <sup>(1)</sup> | _   |                                          | V    |  |  |

|                 | voltage                      | $1.7 V \le V_{DD} \le 3.6 V$ ,<br>0 °C $\le T_A \le 105 °C$                                           | 0.17 0.7                                | _   |                                          |      |  |  |

| Table | 54  | 1/0 | static  | characteristics |

|-------|-----|-----|---------|-----------------|

| lable | 54. | 1/0 | ้อเลเเบ | characteristics |

| Symbol                         | Parameter                                | Conditions                                                    | Min                                 | Max                | Unit |

|--------------------------------|------------------------------------------|---------------------------------------------------------------|-------------------------------------|--------------------|------|

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin  | CMOS port <sup>(2)</sup>                                      | -                                   | 0.4                |      |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin | $I_{IO}$ = +8 mA<br>2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V | V <sub>DD</sub> -0.4                | -                  | V    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin  | TTL port <sup>(2)</sup>                                       | -                                   | 0.4                |      |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin | $I_{IO}$ =+8 mA<br>2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V  | 2.4                                 | -                  | V    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = +20 mA                                      | -                                   | 1.3 <sup>(4)</sup> | v    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin | $2.7 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V}$           | V <sub>DD</sub> -1.3 <sup>(4)</sup> | -                  | v    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = +6 mA                                       | -                                   | 0.4 <sup>(4)</sup> | v    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin | $1.8 \text{ V} \leq \text{V}_{DD} \leq 3.6 \text{ V}$         | V <sub>DD</sub> -0.4 <sup>(4)</sup> | -                  | v    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = +4 mA                                       | -                                   | 0.4 <sup>(5)</sup> | v    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin | $1.7 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V}$           | $V_{DD}$ -0.4 <sup>(5)</sup>        | -                  |      |

Table 55. Output voltage characteristics

1. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 12*. and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in Table 12 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

- 4. Guaranteed by characterization results, not tested in production.

- 5. Guaranteed by design, not tested in production..

#### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 31* and , respectively.

Unless otherwise specified, the parameters given in *Table 56* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| OSPEEDRy<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                                           | Parameter                                                                       | Conditions                                                  | Min                                              | Тур | Мах | Unit |  |

|-----------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------|-----|-----|------|--|

|                                               | f <sub>max(IO)out</sub>                          |                                                                                 |                                                             | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 2.70 V | -   | -   | 4    |  |

|                                               |                                                  | Maximum frequency <sup>(3)</sup>                                                | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 1.7 V             | -                                                | -   | 2   | MHz  |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.70 V            | -                                                | -   | 8   |      |  |

| 1                                             |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V             | -                                                | -   | 4   |      |  |

|                                               | t <sub>f(IO)out</sub> /<br>t <sub>r(IO)out</sub> | Output high to low level fall<br>time and output low to high<br>level rise time | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.7 V to<br>3.6 V | -                                                | -   | 100 | ns   |  |

| Table 56. I/O AC characteris | tics <sup>(1)(2)</sup> |

|------------------------------|------------------------|

|------------------------------|------------------------|

## 6.3.19 Communications interfaces

#### I<sup>2</sup>C interface characteristics

The I<sub>2</sub>C interface meets the requirements of the standard I<sup>2</sup>C communication protocol with the following restrictions: the I/O pins SDA and SCL are mapped to are not "true" opendrain. When configured as open-drain, the PMOS connected between the I/O pin and V<sub>DD</sub> is disabled, but is still present.

The I<sup>2</sup>C characteristics are described in *Table59*. Refer also to *Section 6.3.16: I/O port characteristics* for more details on the input/output alternate function characteristics (SDA and SCL).

The I<sup>2</sup>C bus interface supports standard mode (up to 100 kHz) and fast mode (up to 400 kHz). The I<sub>2</sub>C bus frequency can be increased up to 1 MHz. For more details about the complete solution, please contact your local ST sales representative.

| Symbol                                     | Parameter                               | Standard mode I <sup>2</sup> C <sup>(1)</sup> |      | Fast mod | Unit               |      |

|--------------------------------------------|-----------------------------------------|-----------------------------------------------|------|----------|--------------------|------|

| Symbol                                     | Falameter                               | Min                                           | Max  | Min      | Max                | Unit |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                      | 4.7                                           | -    | 1.3      | -                  |      |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                     | 4.0                                           | -    | 0.6      | -                  | μs   |

| t <sub>su(SDA)</sub>                       | SDA setup time                          | 250                                           | -    | 100      | -                  |      |

| t <sub>h(SDA)</sub>                        | SDA data hold time                      | 0                                             | -    | 0        | 900 <sup>(3)</sup> |      |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                   | -                                             | 1000 |          | 300                | ns   |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                   | -                                             | 300  | -        | 300                |      |

| t <sub>h(STA)</sub>                        | Start condition hold time               | 4.0                                           | -    | 0.6      | -                  |      |

| t <sub>su(STA)</sub>                       | Repeated Start condition setup time     | 4.7                                           | -    | 0.6      | -                  | μs   |

| t <sub>su(STO)</sub>                       | Stop condition setup time               | 4.0                                           | -    | 0.6      | -                  | μs   |

| t <sub>w(STO:STA)</sub>                    | Stop to Start condition time (bus free) | 4.7                                           | -    | 1.3      | -                  | μs   |

| Cb                                         | Capacitive load for each bus line       | -                                             | 400  | -        | 400                | pF   |

| Table | 59. | I <sup>2</sup> C | characteristics |

|-------|-----|------------------|-----------------|

|-------|-----|------------------|-----------------|

1. Guaranteed by design, not tested in production.

f<sub>PCLK1</sub> must be at least 2 MHz to achieve standard mode I<sup>2</sup>C frequencies. It must be at least 4 MHz to achieve fast mode I<sup>2</sup>C frequencies, and a multiple of 10 MHz to reach the 400 kHz maximum I<sup>2</sup>C fast mode clock.

3. The maximum data hold time has only to be met if the interface does not stretch the low period of SCL signal.

#### I<sup>2</sup>S interface characteristics

Unless otherwise specified, the parameters given in *Table 62* for the I<sup>2</sup>S interface are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 14*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 6.3.16: I/O port characteristics for more details on the input/output alternate function characteristics (CK, SD, WS).

| Symbol                                         | Parameter                      | Conditions                             | Min    | Мах                   | Unit |

|------------------------------------------------|--------------------------------|----------------------------------------|--------|-----------------------|------|

| f <sub>MCK</sub>                               | I2S Main clock output          | -                                      | 256x8K | 256xFs <sup>(2)</sup> | MHz  |

| f                                              | 128 clock froguency            | Master data: 32 bits                   | -      | 64xFs                 | MHz  |

| f <sub>CK</sub>                                | I2S clock frequency            | Slave data: 32 bits                    | -      | 64xFs                 |      |

| D <sub>CK</sub>                                | I2S clock frequency duty cycle | Slave receiver                         | 30     | 70                    | %    |

| t <sub>v(WS)</sub>                             | WS valid time                  | Master mode                            | 0      | 6                     |      |

| t <sub>h(WS)</sub>                             | WS hold time                   | Master mode                            | 0      | -                     |      |

| t <sub>su(WS)</sub>                            | WS setup time                  | Slave mode                             | 1      | -                     |      |

| t <sub>h(WS)</sub>                             | WS hold time                   | Slave mode                             | 0      | -                     |      |

| t <sub>su(SD_MR)</sub>                         | Data input setup time          | Master receiver                        | 7.5    | -                     |      |

| t <sub>su(SD_SR)</sub>                         |                                | Slave receiver                         | 2      | -                     | ns   |

| t <sub>h(SD_MR)</sub>                          | Data input hold time           | Master receiver                        | 0      | -                     |      |

| t <sub>h(SD_SR)</sub>                          | Data input noid time           | Slave receiver                         | 0      | -                     |      |

| t <sub>v(SD_ST)</sub><br>t <sub>h(SD_ST)</sub> | Data output valid time         | Slave transmitter (after enable edge)  | -      | 27                    |      |

| t <sub>v(SD_MT)</sub>                          |                                | Master transmitter (after enable edge) | -      | 20                    |      |

| t <sub>h(SD_MT)</sub>                          | Data output hold time          | Master transmitter (after enable edge) | 2.5    | -                     |      |

1. Guaranteed by characterization, not tested in production.

2. The maximum value of 256xFs is 42 MHz (APB1 maximum frequency).

Note:

Refer to the I2S section of the reference manual for more details on the sampling frequency  $(F_S)$ .

$f_{MCK}$ ,  $f_{CK}$ , and  $D_{CK}$  values reflect only the digital peripheral behavior. The values of these parameters might be slightly impacted by the source clock precision.  $D_{CK}$  depends mainly on the value of ODD bit. The digital contribution leads to a minimum value of (I2SDIV/(2\*I2SDIV+ODD) and a maximum value of (I2SDIV+ODD)/(2\*I2SDIV+ODD).  $F_S$  maximum value is supported for each mode/condition.

| Symbol                           | Parameter                                                                          | Conditions                                           | Min                 | Тур       | Max                                                                                                                                                                                                                                                                                                                         | Unit               |

|----------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------|---------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| + (2)                            | Injection trigger conversion                                                       | f <sub>ADC</sub> = 30 MHz                            | -                   | -         | 0.100                                                                                                                                                                                                                                                                                                                       | μs                 |

| $t_{lat}^{(2)}$                  | latency                                                                            |                                                      | -                   | -         | 3 <sup>(5)</sup>                                                                                                                                                                                                                                                                                                            | 1/f <sub>ADC</sub> |

| t <sub>latr</sub> (2)            | Regular trigger conversion                                                         | f <sub>ADC</sub> = 30 MHz                            | -                   | -         | 0.067                                                                                                                                                                                                                                                                                                                       | μs                 |

| 'latr'                           | latency                                                                            |                                                      | -                   | -         | 2 <sup>(5)</sup>                                                                                                                                                                                                                                                                                                            | 1/f <sub>ADC</sub> |

| ts <sup>(2)</sup>                | Sampling time                                                                      | f <sub>ADC</sub> = 30 MHz                            | 0.100               | -         | 16                                                                                                                                                                                                                                                                                                                          | μs                 |

| U U                              |                                                                                    |                                                      | 3                   | -         | 480                                                                                                                                                                                                                                                                                                                         | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> <sup>(2)</sup> | Power-up time                                                                      |                                                      | -                   | 2         | 3                                                                                                                                                                                                                                                                                                                           | μs                 |

|                                  |                                                                                    | f <sub>ADC</sub> = 30 MHz<br>12-bit resolution       | 0.50                | -         | 16.40                                                                                                                                                                                                                                                                                                                       | μs                 |

| t <sub>CONV</sub> <sup>(2)</sup> |                                                                                    | f <sub>ADC</sub> = 30 MHz<br>10-bit resolution       | 0.43                | -         | $\begin{array}{c cccc} & 3^{(5)} \\ \hline & 0.067 \\ \hline & 2^{(5)} \\ \hline & 16 \\ \hline & 480 \\ 2 & 3 \\ \hline & 16.40 \\ \hline & 16.34 \\ \hline & 16.27 \\ \hline & 16.20 \\ \hline & 16.20 \\ \hline & 2 \\ \hline & 3.75 \\ \hline & 2 \\ \hline & 3.75 \\ \hline & 6 \\ \hline & 500 \\ \hline \end{array}$ | μs                 |

|                                  | Total conversion time (including sampling time)                                    | f <sub>ADC</sub> = 30 MHz<br>8-bit resolution        | 0.37                | -         | 16.27                                                                                                                                                                                                                                                                                                                       | μs                 |

|                                  |                                                                                    | f <sub>ADC</sub> = 30 MHz<br>6-bit resolution        | 0.30                | -         | 16.20                                                                                                                                                                                                                                                                                                                       | μs                 |

|                                  |                                                                                    | 9 to 492 (t <sub>S</sub> for sampling approximation) | +n-bit resolution f | or succes | 1/f <sub>ADC</sub>                                                                                                                                                                                                                                                                                                          |                    |

|                                  |                                                                                    | 12-bit resolution<br>Single ADC                      | -                   | -         | 2                                                                                                                                                                                                                                                                                                                           | Msps               |

| f <sub>S</sub> <sup>(2)</sup>    | Sampling rate<br>(f <sub>ADC</sub> = 30 MHz, and<br>t <sub>S</sub> = 3 ADC cycles) | 12-bit resolution<br>Interleave Dual ADC<br>mode     | -                   | -         |                                                                                                                                                                                                                                                                                                                             | Msps               |

|                                  |                                                                                    | 12-bit resolution<br>Interleave Triple ADC<br>mode   | -                   | -         | 6                                                                                                                                                                                                                                                                                                                           | Msps               |

| I <sub>VREF+</sub> (2)           | ADC V <sub>REF</sub> DC current<br>consumption in conversion<br>mode               |                                                      | -                   | 300       | 500                                                                                                                                                                                                                                                                                                                         | μA                 |

| I <sub>VDDA</sub> <sup>(2)</sup> | ADC V <sub>DDA</sub> DC current<br>consumption in conversion<br>mode               |                                                      | -                   | 1.6       | 1.8                                                                                                                                                                                                                                                                                                                         | mA                 |

#### Table 66. ADC characteristics (continued)

1. V<sub>DDA</sub> minimum value of 1.7 V is possible with the use of an external power supply supervisor (refer to Section 3.14.2: Internal reset OFF).

2. Guaranteed by characterization, not tested in production.

3.  $V_{\mathsf{REF}^+}$  is internally connected to  $V_{\mathsf{DDA}}$  and  $V_{\mathsf{REF}^-}$  is internally connected to  $V_{\mathsf{SSA}}.$

4.  $R_{ADC}$  maximum value is given for V<sub>DD</sub>=1.7 V, and minimum value for V<sub>DD</sub>=3.3 V.

5. For external triggers, a delay of 1/f<sub>PCLK2</sub> must be added to the latency specified in *Table 66*.

#### Equation 1: R<sub>AIN</sub> max formula

$$R_{AIN} = \frac{(k-0.5)}{f_{ADC} \times C_{ADC} \times \ln(2^{N+2})} - R_{ADC}$$

## 6.3.21 Temperature sensor characteristics

| Symbol                             | Parameter                                                      | Min | Тур  | Max | Unit  |

|------------------------------------|----------------------------------------------------------------|-----|------|-----|-------|

| T <sub>L</sub> <sup>(1)</sup>      | V <sub>SENSE</sub> linearity with temperature                  | -   | ±1   | ±2  | °C    |

| Avg_Slope <sup>(1)</sup>           | Average slope                                                  | -   | 2.5  | -   | mV/°C |

| V <sub>25</sub> <sup>(1)</sup>     | Voltage at 25 °C                                               | -   | 0.76 | -   | V     |

| t <sub>START</sub> <sup>(2)</sup>  | Startup time                                                   | -   | 6    | 10  | μs    |

| T <sub>S_temp</sub> <sup>(2)</sup> | ADC sampling time when reading the temperature (1 °C accuracy) | 10  | -    | -   | μs    |

| Table 72. Temperature sensor characteristics |

|----------------------------------------------|

|----------------------------------------------|

1. Guaranteed by characterization, not tested in production.

2. Guaranteed by design, not tested in production.

| Table 73. Temperature sensor calibration value | es |

|------------------------------------------------|----|

|                                                |    |

| Symbol  | Parameter                                                                        | Memory address            |

|---------|----------------------------------------------------------------------------------|---------------------------|

| TS_CAL1 | TS ADC raw data acquired at temperature of 30 °C, $V_{\text{DDA}}\text{=}$ 3.3 V | 0x1FFF 7A2C - 0x1FFF 7A2D |

| TS_CAL2 | TS ADC raw data acquired at temperature of 110 °C, $V_{DDA}$ = 3.3 V             | 0x1FFF 7A2E - 0x1FFF 7A2F |

## 6.3.22 V<sub>BAT</sub> monitoring characteristics

#### Table 74. V<sub>BAT</sub> monitoring characteristics

| Symbol                                | Parameter                                                            |    | Тур | Мах | Unit |

|---------------------------------------|----------------------------------------------------------------------|----|-----|-----|------|

| R                                     | Resistor bridge for V <sub>BAT</sub>                                 | -  | 50  | -   | KΩ   |

| Q                                     | Ratio on V <sub>BAT</sub> measurement                                | -  | 4   | -   |      |

| Er <sup>(1)</sup>                     | Error on Q                                                           | -1 | -   | +1  | %    |

| T <sub>S_vbat</sub> <sup>(2)(2)</sup> | ADC sampling time when reading the V <sub>BAT</sub><br>1 mV accuracy | 5  | -   | -   | μs   |

1. Guaranteed by design, not tested in production.

2. Shortest sampling time can be determined in the application by multiple iterations.

#### 6.3.23 Embedded reference voltage

The parameters given in *Table 75* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| Symbol                                | Parameter                                                        | Conditions                        | Min  | Тур  | Max  | Unit |

|---------------------------------------|------------------------------------------------------------------|-----------------------------------|------|------|------|------|

| V <sub>REFINT</sub>                   | Internal reference voltage                                       | –40 °C < T <sub>A</sub> < +105 °C | 1.18 | 1.21 | 1.24 | V    |

| T <sub>S_vrefint</sub> <sup>(1)</sup> | ADC sampling time when reading the<br>internal reference voltage | -                                 | 10   | -    | -    | μs   |

| V <sub>RERINT_s</sub> <sup>(2)</sup>  | Internal reference voltage spread over the temperature range     | $V_{DD}$ = 3V $\pm$ 10mV          | -    | 3    | 5    | mV   |

| Symbol            |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|-------------------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol            | Min   | Тур         | Мах   | Min    | Тур                   | Мах    |

| A2                | -     | 0.380       | -     | -      | 0.0150                | -      |

| A3 <sup>(2)</sup> | -     | 0.025       | -     | -      | 0.0010                | -      |

| b <sup>(3)</sup>  | 0.220 | 0.250       | 0.280 | 0.0087 | 0.0098                | 0.0110 |

| D                 | 2.994 | 3.029       | 3.064 | 0.1179 | 0.1193                | 0.1206 |

| E                 | 2.994 | 3.029       | 3.064 | 0.1179 | 0.1193                | 0.1206 |

| е                 | -     | 0.400       | -     | -      | 0.0157                | -      |

| e1                | -     | 2.400       | -     | -      | 0.0945                | -      |

| e2                | -     | 2.400       | -     | -      | 0.0945                | -      |

| F                 | -     | 0.3145      | -     | -      | 0.0124                | -      |

| G                 | -     | 0.3145      | -     | -      | 0.0124                | -      |

| aaa               | -     | 0.100       | -     | -      | 0.0039                | -      |

| bbb               | -     | 0.100       | -     | -      | 0.0039                | -      |

| CCC               | -     | 0.100       | -     | -      | 0.0039                | -      |

| ddd               | -     | 0.050       | -     | -      | 0.0020                | -      |

| eee               | -     | 0.050       | -     | -      | 0.0020                | -      |

#### Table 79. STM32F401xCE WLCSP49 wafer level chip size package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Back side coating

3. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

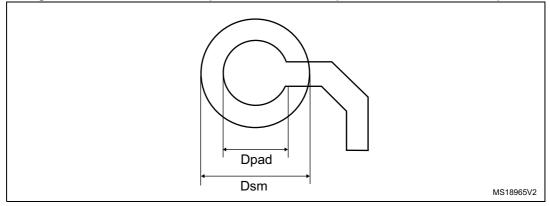

#### Figure 47. WLCSP49 0.4 mm pitch wafer level chip size recommended footprint

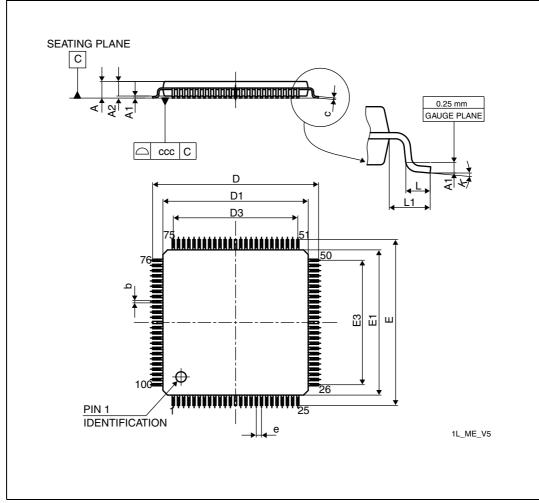

## 7.1.4 LQFP100, 14 x 14 mm, 100-pin low-profile quad flat package

#### Figure 55. LQFP100, 14 x 14 mm, 100-pin low-profile quad flat package outline

1. Drawing is not to scale.

## 8 Part numbering

## Table 86. Ordering information scheme

| Example:                                       | STM32 | F | 401 | С | Е | Y 6 | TR |

|------------------------------------------------|-------|---|-----|---|---|-----|----|

|                                                |       |   |     |   |   |     |    |

| Device family                                  |       |   |     |   |   |     |    |

| STM32 = ARM-based 32-bit microcontroller       |       |   |     |   |   |     |    |

|                                                |       |   |     |   |   |     |    |

| Product type                                   |       |   |     |   |   |     |    |

| F = General-purpose                            |       |   |     |   |   |     |    |

|                                                |       |   |     |   |   |     |    |

| Device subfamily                               |       |   |     |   |   |     |    |

| 401 = 401 family                               |       |   |     |   |   |     |    |

|                                                |       |   |     |   |   |     |    |

| Pin count                                      |       |   |     |   |   |     |    |

| C = 48/49 pins                                 |       |   |     |   |   |     |    |

| R = 64 pins                                    |       |   |     |   |   |     |    |

| V = 100 pins                                   |       |   |     |   |   |     |    |

|                                                |       |   |     |   |   |     |    |

| Flash memory size                              |       |   |     |   |   |     |    |

| D = 384 Kbytes of Flash memory                 |       |   |     |   |   |     |    |

| E = 512 Kbytes of Flash memory                 |       |   |     |   |   |     |    |

|                                                |       |   |     |   |   |     |    |

| Package                                        |       |   |     |   |   |     |    |

| H = UFBGA                                      |       |   |     |   |   |     |    |

| T = LQFP                                       |       |   |     |   |   |     |    |

| U = UFQFPN                                     |       |   |     |   |   |     |    |

| Y = WLCSP                                      |       |   |     |   |   |     |    |

|                                                |       |   |     |   |   |     |    |

| Temperature range                              |       |   |     |   |   |     |    |

| 6 = Industrial temperature range, -40 to 85 °C |       |   |     |   |   |     |    |

|                                                |       |   |     |   |   |     |    |

| Packing                                        |       |   |     |   |   |     |    |

TR = tape and reel

No character = tray or tube