#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Not For New Designs                                                            |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | H8S/2000                                                                       |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 20MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, LPC, SCI                                                     |

| Peripherals                | POR, PWM, WDT                                                                  |

| Number of I/O              | 114                                                                            |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 12K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 12x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 144-TQFP                                                                       |

| Supplier Device Package    | 144-TQFP (16x16)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r4f2113nft-u0 |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## (10) PCS0 to PSC3 (Port CS) (V850ES/SA2) ... 3-state I/O PCS0 to PCS5 (Port CS) (V850ES/SA3) ... 3-state I/O

## [V850ES/SA2]

Port CS is a 4-bit I/O port that can be set to the input or output mode in 1-bit units. Besides functioning as I/O port pins, in the control mode PCS0 to PSC3 also operate as the control signal output pins when the memory and peripheral I/O are expanded externally.

#### (a) Port mode

PCS0 to PSC3 can be set to the input or output mode in 1-bit units by using port mode register CM (PMCS).

#### (b) Control mode

#### (i) $\overline{CS0}$ to $\overline{CS3}$ (chip select) ... Output

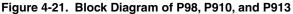

executed, and inactive in the idle state (TI).

These are the chip select signals for the SRAM, external ROM, and external peripheral I/O area. The  $\overline{\text{CSn}}$  signal is assigned to memory block n (n = 0 to 3). Each of these signals is active while the bus cycle accessing the corresponding memory block is being

#### [V850ES/SA3]

Port CS is an 8-bit I/O port that can be set to the input or output mode in 1-bit units.

Besides functioning as I/O port pins, in the control mode PCS0 to PSC3 also operate as the control signal output pins when the memory and peripheral I/O are expanded externally.

#### (a) Port mode

PCS0 to PCS7 can be set to the input or output mode in 1-bit units by using port mode register CS (PMCS).

## (b) Control mode

## (i) $\overline{CS0}$ to $\overline{CS3}$ (chip select) ... Output

These are the chip select signals for the SRAM, external ROM, and external peripheral I/O area. The  $\overline{\text{CSn}}$  signal is assigned to memory block n (n = 0 to 3).

Each of these signals is active while the bus cycle accessing the corresponding memory block is being executed, and inactive in the idle state (TI).

**Remarks 1.** indicates the recommended area.

2. This figure is the recommended memory map of the  $\mu$ PD703204.

## 4.3.13 Port DL

Port DL can be set to the input or output mode in 1-bit units. The number of I/O port bits of each product is the same.

| Commercial Name | Number of I/O Port Bits |

|-----------------|-------------------------|

| V850ES/SA2      | 16-bit I/O port         |

| V850ES/SA3      | 16-bit I/O port         |

## (1) Functions of port DL

○ Input/output data can be specified in 1-bit units by using port register DL (PDL).

- Can be set to the input or output mode in 1-bit units by using port mode register DL (PMDL).

- Can be set to the port mode or control mode (alternate function) in 1-bit units by using port mode control register DL (PMCDL).

Port DL has an alternate function as the following pins.

| Pin Na  | ame      | Alternate-Function Pin      | I/O | PULL <sup>Note 1</sup> | Remark |

|---------|----------|-----------------------------|-----|------------------------|--------|

| Port DL | PDL0 AD0 |                             | I/O | None                   | -      |

|         | PDL1     | AD1                         |     |                        |        |

|         | PDL2     | AD2                         |     |                        |        |

|         | PDL3     | AD3                         |     |                        |        |

|         | PDL4     | AD4                         |     |                        |        |

|         | PDL5     | AD5/FLMD1 <sup>Note 2</sup> |     |                        |        |

|         | PDL6     | AD6                         |     |                        |        |

|         | PDL7     | AD7                         |     |                        |        |

|         | PDL8     | AD8                         |     |                        |        |

|         | PDLDL    | AD9                         |     |                        |        |

|         | PDL10    | AD10                        |     |                        |        |

|         | PDL11    | AD11                        |     |                        |        |

|         | PDL12    | AD12                        |     |                        |        |

|         | PDL13    | AD13                        |     |                        |        |

|         | PDL14    | AD14                        |     |                        |        |

|         | PDL15    | AD15                        |     |                        |        |

#### Table 4-17. Alternate-Function Pins of Port DL

## Notes 1. Software pull-up function

Because these pins are used for setting in the flash programming mode, they do not have to be manipulated by using a port control register. For details, refer to CHAPTER 21 FLASH MEMORY (μPD70F3201, 70F3201Y, 70F3204, and 70F3204Y only).

## Figure 5-8. Multiplexed Bus Hold Timing (Bus Size: 16 Bits, 16-Bit Access)

## 6.2 Configuration

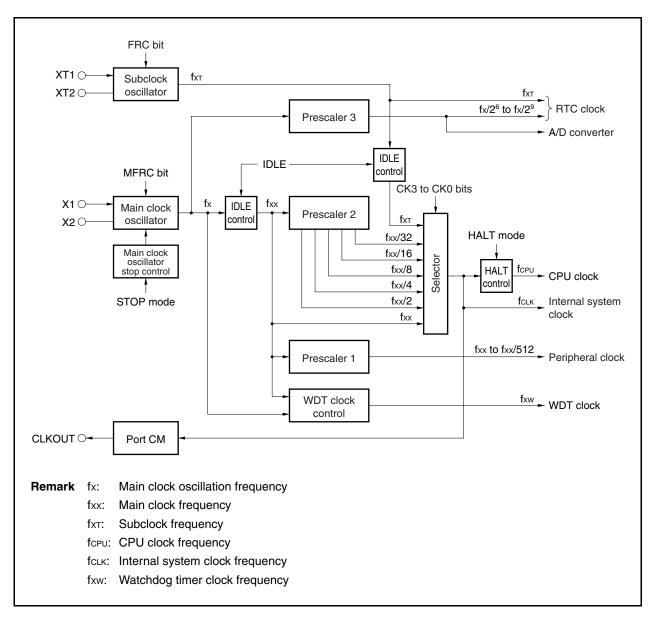

Figure 6-1. Clock Generator

## (1) A/D converter mode register (ADM)

This register sets the conversion time of the analog input signal to be converted into a digital signal as well as conversion start and stop.

The ADM register can be read or written in 8-bit or 1-bit units.

This register is cleared to 00H after reset.

|    |            | _                              |                                             | -                          |                            |            | <u>^</u>     |           |        |              |  |

|----|------------|--------------------------------|---------------------------------------------|----------------------------|----------------------------|------------|--------------|-----------|--------|--------------|--|

|    | 4514       | <7><br>ADCSB <sup>Note 1</sup> | 6<br>0                                      | 5<br>FR3 <sup>Note 2</sup> | 4<br>FB2 <sup>Note 2</sup> | 3          | 2            | 1         | 0      | 1            |  |

|    | ADM        | ADCSBiole                      | 0                                           | FR3 <sup>note 2</sup>      | FR2 <sup>note 2</sup>      | FR1        | FR0          | 0         | 0      | J            |  |

|    |            | ADCSNote 1                     |                                             | A/D conversion control     |                            |            |              |           |        |              |  |

|    |            | 0                              | Stops co                                    | nversion                   |                            |            |              |           |        |              |  |

|    |            | 1                              | Enables                                     | conversion                 |                            |            |              |           |        |              |  |

|    |            |                                |                                             |                            |                            |            |              |           |        | -            |  |

|    |            | FR3 <sup>Note 2</sup>          | FR2 <sup>Note 2</sup>                       |                            | Number of A                | VD conve   | rsion clocks | 6         |        |              |  |

|    |            | 0                              | 0                                           | 19 clocks                  | 6                          |            |              |           |        |              |  |

|    |            | 0                              | 1                                           | Setting p                  | rohibited                  |            |              |           |        |              |  |

|    |            | 1                              | 0                                           | Setting p                  | rohibited                  |            |              |           |        |              |  |

|    |            | 1                              | 1                                           | Setting prohibited         |                            |            |              |           |        |              |  |

|    |            |                                |                                             | 1                          |                            |            |              |           |        | 1            |  |

|    |            | FR1                            | FR0                                         |                            | A/D co                     | onversion  | clock        |           |        |              |  |

|    |            | 0                              | 0                                           | fxx/16                     |                            |            |              |           |        |              |  |

|    |            | 0                              | 1                                           | fxx/8                      |                            |            |              |           |        |              |  |

|    |            | 1                              | 0                                           | fxx/4                      |                            |            |              |           |        |              |  |

|    |            | 1                              | 1                                           | Clock of                   | prescaler 3                | (fbrg)     |              |           |        |              |  |

|    | To use fer | ag output a                    | is the cor                                  | nversion c                 | lock of the                |            |              |           |        | I-time count |  |

|    |            | gister 0 (R <sup>-</sup>       |                                             |                            |                            | out the fe | are clock i  | n the IDI | E mode | To reduce t  |  |

|    |            |                                | -                                           |                            | -                          |            |              |           |        | 6.5.1 (1)) a |  |

|    | -          | -                              |                                             |                            |                            |            |              |           | ,      | , u          |  |

|    |            |                                | I register to 0.<br>FR3 and FR2 bits to 00. |                            |                            |            |              |           |        |              |  |

|    | Be sure to | o clear the                    |                                             |                            |                            |            |              |           |        |              |  |

| 2. |            | o clear the                    |                                             |                            |                            |            |              |           |        |              |  |

#### (7) Receive data noise filter

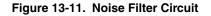

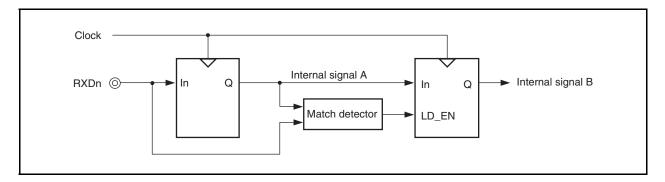

The RXDn signal is sampled at the rising edge of the prescaler output base clock (Clock). If the same sampling value is obtained twice, the match detector output changes, and this output is sampled as input data. Therefore, data not exceeding one clock width is judged to be noise and is not delivered to the internal circuit (see **Figure 13-12**). Refer to **13.6 (1) (a) Base clock (Clock)** regarding the base clock.

Also, since the circuit is configured as shown in Figure 13-11, internal processing during a receive operation is delayed by up to 2 clocks according to the external signal status.

Figure 13-12. Timing of RXDn Signal Judged as Noise

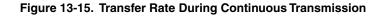

#### (5) Transfer rate during continuous transmission

During continuous transmission, the transfer rate from a stop bit to the next start bit is extended two clocks of the base clock (Clock) longer than normal. However, on the reception side, the transfer result is not affected since the timing is initialized by the detection of the start bit.

Representing the 1-bit data length by FL, the stop bit length by FLstp, and the base clock frequency by fcksr yields the following equation.

FLstp = FL + 2/fcksr

Therefore, the transfer rate during continuous transmission is as follows.

Transfer rate = 11 × FL + 2/fcksr

#### 14.1.2 Switching modes between CSI1 and UART0

CSI1 and UART0 of the V850ES/SA2 and V850ES/SA3 share pins, and therefore these interfaces cannot be used at the same time. Select CSI1 or UART0 in advance by using port mode control register 3 (PMC3) and port function control register 3 (PFC3) (refer to **4.3.3 Port 3**).

# Caution CSI1 or UART0 transmission/reception operations are not guaranteed if the mode is changed during transmission or reception. Be sure to disable the operation of the unit that is not used.

| After res                  | set: 00H | R/W | Address: F | FFFF446H | 4      |           |       |       |

|----------------------------|----------|-----|------------|----------|--------|-----------|-------|-------|

|                            | 7        | 6   | 5          | 4        | 3      | 2         | 1     | 0     |

| PMC3                       | 0        | 0   | 0          | 0        | 0      | PMC32     | PMC31 | PMC30 |

|                            |          |     |            |          |        |           |       |       |

| After res                  | set: 00H | R/W | Address: F | FFFF466H | ł      |           |       |       |

|                            | 7        | 6   | 5          | 4        | 3      | 2         | 1     | 0     |

| PFC3                       | 0        | 0   | 0          | 0        | 0      | 0         | PFC31 | PFC30 |

|                            |          |     |            |          |        |           |       |       |

|                            | PMO      | C3n | PFC3n      |          | Operat | tion mode |       |       |

|                            | C        | )   | ×          | Port I/C | ) mode |           |       |       |

|                            | 1        |     | 0          | CSI1 m   | ode    |           |       | 1     |

|                            | 1        |     | 1          | UART0    | mode   |           |       | 7     |

|                            |          | ÷   |            |          |        |           |       |       |

| <b>Remarks 1.</b> n = 0, 1 | 1        |     |            |          |        |           |       |       |

| <b>2.</b> × = Do           | n't care |     |            |          |        |           |       |       |

|                            |          |     |            |          |        |           |       |       |

Figure 14-2. Selecting CSI1 or UART0 Mode

## 14.2 Configuration

CSIn is controlled by the clocked serial interface mode register (CSIMn). Transmit/receive data can be written to or read from the SIOn register.

#### (1) Clocked serial interface mode register n (CSIMn)

The CSIMn register is an 8-bit register for specifying the operation of CSIn.

#### (2) Clocked serial interface clock selection register n (CSICn)

The CSICn register is an 8-bit register for controlling the transmit operation of CSIn.

#### (3) Serial I/O shift register n (SIOn)

The SIOn register is an 8-bit register for converting between serial data and parallel data. SIOn is used for both transmission and reception.

Data is shifted in (reception) or shifted out (transmission) beginning at either the MSB side or the LSB side. Actual transmit/receive operations are controlled by reading or writing SIOn.

| CKSn2 | CKSn1 | CKSn0 |                     | Baud Rate (bps)     |                       |                     |                    |                    |  |  |  |  |  |

|-------|-------|-------|---------------------|---------------------|-----------------------|---------------------|--------------------|--------------------|--|--|--|--|--|

|       |       |       | 20 MHz<br>Operation | 17 MHz<br>Operation | 13.5 MHz<br>Operation | 10 MHz<br>Operation | 8 MHz<br>Operation | 4 MHz<br>Operation |  |  |  |  |  |

| 0     | 0     | 0     | Setting prohibited  | Setting prohibited  | Setting prohibited    | 5,000,000           | 4,000,000          | 2,000,000          |  |  |  |  |  |

| 0     | 0     | 1     | 5,000,000           | 4,250,000           | 3,375,000             | 2,500,000           | 2,000,000          | 1,000,000          |  |  |  |  |  |

| 0     | 1     | 0     | 2,500,000           | 2,125,000           | 1,687,500             | 1,250,000           | 1,000,000          | 500,000            |  |  |  |  |  |

| 0     | 1     | 1     | 1,250,000           | 1,062,500           | 843,750               | 625,000             | 500,000            | 250,000            |  |  |  |  |  |

| 1     | 0     | 0     | 625,000             | 531,250             | 421,875               | 312,500             | 250,000            | 125,000            |  |  |  |  |  |

| 1     | 0     | 1     | 312,500             | 265,625             | 210,938               | 156,250             | 125,000            | 62,500             |  |  |  |  |  |

## (a) Transfer rate selection example

(2/4)

| WREL                                      | Wait cancellation control                    |                                   |  |  |  |  |  |

|-------------------------------------------|----------------------------------------------|-----------------------------------|--|--|--|--|--|

| 0                                         | Wait not canceled                            |                                   |  |  |  |  |  |

| 1                                         | Wait canceled. This setting is automaticall  | y cleared after wait is canceled. |  |  |  |  |  |

| Condition                                 | n for clearing (WREL = $0$ ) <sup>Note</sup> | Condition for setting (WREL = 1)  |  |  |  |  |  |

| <ul><li>Automa</li><li>After re</li></ul> | tically cleared after execution set          | Set by instruction                |  |  |  |  |  |

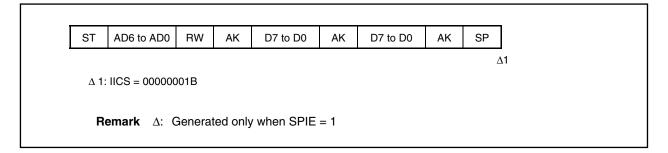

| SPIE                         | Enable/disable generation of interrupt request when stop condition is detected |                                  |  |  |  |  |  |

|------------------------------|--------------------------------------------------------------------------------|----------------------------------|--|--|--|--|--|

| 0                            | Disabled                                                                       |                                  |  |  |  |  |  |

| 1                            | Enabled                                                                        |                                  |  |  |  |  |  |

| Condition                    | n for clearing $(SPIE = 0)^{Note}$                                             | Condition for setting (SPIE = 1) |  |  |  |  |  |

| Cleared                      | d by instruction                                                               | Set by instruction               |  |  |  |  |  |

| <ul> <li>After re</li> </ul> | set                                                                            |                                  |  |  |  |  |  |

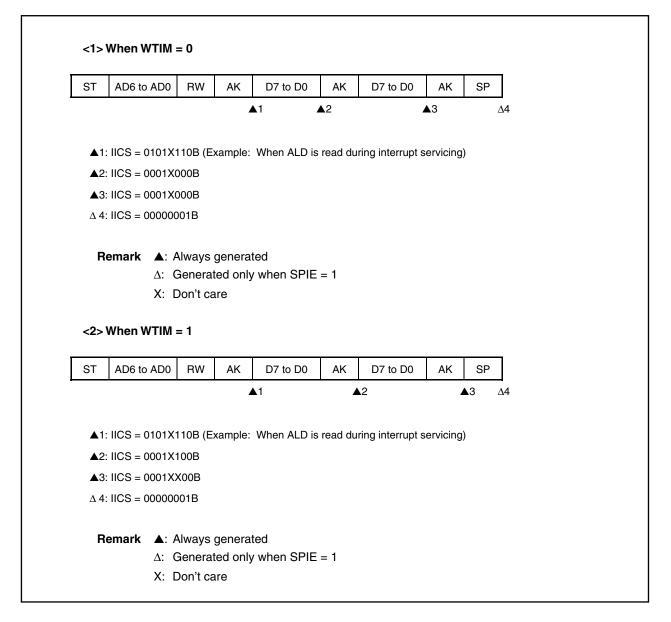

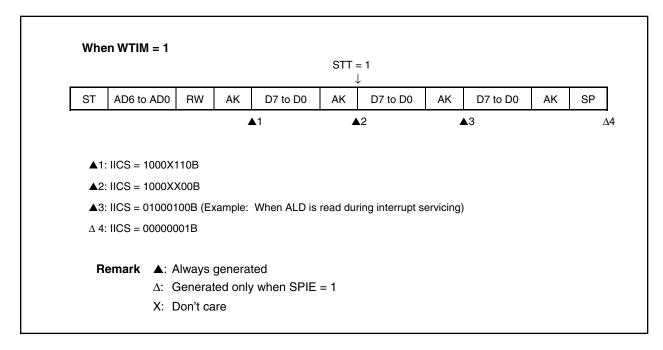

| WTIM                                            | Control of wait and interrupt request generation                                                                                                                                                                                                                                   |                                                                                                                     |                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 0                                               | Interrupt request is generated at the eighth clockÕs falling edge.<br>Master mode: After output of eight clocks, clock output is set to low level and wait is set.<br>Slave mode: After input of eight clocks, the clock is set to low level and wait is set for master            |                                                                                                                     |                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                                                 |                                                                                                                                                                                                                                                                                    | device.                                                                                                             |                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| 1                                               | Interrupt request is generated at the eighth clockÕs falling edge.<br>Master mode: After output of eight clocks, clock output is set to low level and wait is set.<br>Slave mode: After input of eight clocks, the clock is set to low level and wait is set for master<br>device. |                                                                                                                     |                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                                                 |                                                                                                                                                                                                                                                                                    | device.                                                                                                             |                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| master n<br>device th<br>signal is              | node, a wait is ir<br>nat has received                                                                                                                                                                                                                                             | lid during an address tran<br>serted at the falling edge<br>a local address, a wait is<br>he slave device has rece  | nsfer and is valid as the transfer is completed. When in<br>a of the ninth clock during address transfers. For a slave<br>is inserted at the falling edge of the ninth clock after an $\overline{AC}$<br>ived an extension code, a wait is inserted at the falling |  |  |  |  |  |  |

| master n<br>device th<br>signal is<br>edge of t | node, a wait is ir<br>nat has received<br>issued. When t                                                                                                                                                                                                                           | lid during an address tran<br>nserted at the falling edge<br>a local address, a wait is<br>he slave device has rece | e of the ninth clock during address transfers. For a slave s inserted at the falling edge of the ninth clock after an $\overrightarrow{AC}$                                                                                                                        |  |  |  |  |  |  |

**Note** This flag's signal is invalid when IICE = 0.

## (4) IIC function expansion register (IICX)

The IICX register is used to set the function expansion of  $I^2C$  (valid only in high-speed mode). The IICX register can be read or written in 8-bit or 1-bit units. Set the CLX bit in combination with the SMC, CL1, and CL0 bits of the IIC clock selection register (IICCL) (see **Table 15-2 Transfer Clock Setting**). This register is cleared to 00H after reset.

| 7         6         5         4         3         2         1         0           IICX         0         0         0         0         0         0         0         CLX | After res | et: 00H | R/W | Address: F | FFFFD85H | 4 |   |   |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------|-----|------------|----------|---|---|---|-----|

| IICX 0 0 0 0 0 0 0 CLX                                                                                                                                                   |           | 7       | 6   | 5          | 4        | 3 | 2 | 1 | 0   |

|                                                                                                                                                                          | IICX      | IICX 0  |     | 0          | 0        | 0 | 0 | 0 | CLX |

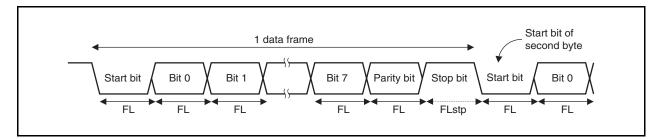

## (5) I<sup>2</sup>C transfer clock setting method

The I<sup>2</sup>C transfer clock frequency (fscL) is calculated using the following expression.

$f_{SCL} = 1/(m \times T + t_R + t_F)$

m = 12, 18, 24, 48, 86, 88, 172 (see Table 15-2 Transfer Clock Setting.)

- T: 1/fxx

- tR: SCL rise time

- tF: SCL fall time

For example, the I<sup>2</sup>C transfer clock frequency (fscL) when fxx = 16 MHz, m = 172,  $t_R = 200$  ns, and  $t_F = 50$  ns is calculated using the following expression.

$f_{SCL} = 1/(172 \times 62.5 \text{ ns} + 200 \text{ ns} + 50 \text{ ns}) \cong 90.9 \text{ kHz}$

#### Figure 15-4. I<sup>2</sup>C Transfer Clock Frequency (fscL)

The transfer clock is set using a combination of the SMC, CL1, and CL0 bits of IIC clock select register (IICCL), the CLX bit of IIC function expansion register (IICX).

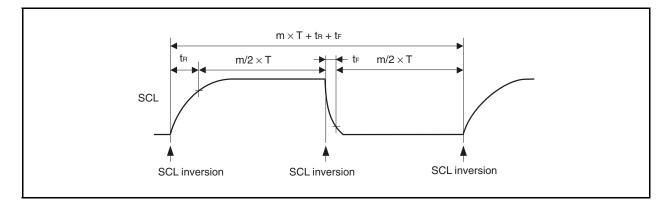

#### (4) Operation without communication

(a) Start ~ Code ~ Data ~ Data ~ Stop

## (5) Arbitration loss operation (operation as slave after arbitration loss)

(a) When arbitration loss occurs during transmission of slave address data

(e) When loss occurs due to stop condition during data transfer

| ST                                            | r ade | 6 to AD0        | RW       | AK | D7 to Dn           | SP  |  |  |

|-----------------------------------------------|-------|-----------------|----------|----|--------------------|-----|--|--|

|                                               | 1     |                 | [        | 1  | ▲1                 | 1   |  |  |

| ▲1: IICS = 1000X110B<br>△ 2: IICS = 01000001B |       |                 |          |    |                    |     |  |  |

| 2                                             |       |                 |          |    |                    |     |  |  |

|                                               | Rema  | r <b>k ≜</b> :/ |          |    | ted<br>/ when SPIE | - 1 |  |  |

|                                               |       |                 | Don't ca |    |                    | - 1 |  |  |

|                                               |       | Dn =            | = D6 to  | D0 |                    |     |  |  |

|                                               |       |                 |          |    |                    |     |  |  |

(f) When arbitration loss occurs due to low-level data when attempting to generate a restart condition

## 15.7 Interrupt Request (INTIIC) Generation Timing and Wait Control

The setting of bit 3 (WTIM) of the IIC control register (IICC) determines the timing by which INTIIC is generated and the corresponding wait control, as shown below.

| WTIM | Durii                   | ng Slave Device Ope | eration             | During Master Device Operation |                |                   |  |

|------|-------------------------|---------------------|---------------------|--------------------------------|----------------|-------------------|--|

|      | Address                 | Data Reception      | Data Transmission   | Address                        | Data Reception | Data Transmission |  |

| 0    | 9 <sup>Notes 1, 2</sup> | 8 <sup>Note 2</sup> | 8 <sup>Note 2</sup> | 9                              | 8              | 8                 |  |

| 1    | 9 <sup>Notes 1, 2</sup> | 9 <sup>Note 2</sup> | 9 <sup>Note 2</sup> | 9                              | 9              | 9                 |  |

#### Table 15-3. INTIIC Signal Generation Timing and Wait Control

Notes 1. The slave device's INTIIC signal and wait period occurs at the falling edge of the ninth clock only when there is a match with the address set to slave address register (SVA).

At this point, ACK is output regardless of the value set to bit 2 (ACKE) of the IICC register. For a slave device that has received an extension code, the INTIIC signal occurs at the falling edge of the eighth clock.

- 2. If the received address does not match the contents of slave address register (SVA), neither the INTIIC signal nor a wait occurs.

- **Remark** The numbers in the table indicate the number of the serial clock's clock signals. Interrupt requests and wait control are both synchronized with the falling edge of these clock signals.

#### (1) During address transmission/reception

- Slave device operation: The interrupt and wait timing are determined regardless of the WTIM bit.

- Master device operation: The interrupt and wait timing occur at the falling edge of the ninth clock regardless

of the WTIM bit.

#### (2) During data reception

• Master/slave device operation: The interrupt and wait timing are determined according to the WTIM bit.

#### (3) During data transmission

• Master/slave device operation: The interrupt and wait timing are determined according to the WTIM bit.

#### (4) Wait cancellation method

The four wait cancellation methods are as follows.

- By setting bit 5 (WREL) of the IIC control register (IICC) to 1

- By writing to the IIC shift register (IIC)

- By start condition setting (bit 1 (STT) of IIC control register (IICC) = 1)

- By stop condition setting (bit 0 (SPT) of IIC control register (IICC) = 1)

When an 8-clock wait has been selected (WTIM = 0), the output level of  $\overline{ACK}$  must be determined prior to wait cancellation.

#### (5) Stop condition detection

INTIIC signal is generated when a stop condition is detected.

#### 16.3.3 DMA byte count registers 0 to 3 (DBC0 to DBC3)

These 16-bit registers are used to set the byte transfer count for DMA channels n (n = 0 to 3). They store the remaining transfer count during DMA transfer.

These registers can be read or written in 16-bit units.

**Remark** If the DBCn register is read during DMA transfer after a terminal count has occurred without the register being overwritten, the value set immediately before the DMA transfer will be read out (0000H will not be read, even if DMA transfer has ended).

|              |                | DBC2 FFFF0C4H, DBC3 FFFF0C6H |                                                                                                                                               |            |      |              |            |     |

|--------------|----------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------|------|--------------|------------|-----|

|              | 15             | 14                           | 13                                                                                                                                            | 12         | 11   | 10           | 9          | 8   |

| DBCn         | BC15           | BC14                         | BC13                                                                                                                                          | BC12       | BC11 | BC10         | BC9        | BC8 |

|              | 7              | 6                            | 5                                                                                                                                             | 4          | 3    | 2            | 1          | 0   |

|              | BC7            | BC6                          | BC5                                                                                                                                           | BC4        | BC3  | BC2          | BC1        | BC0 |

| (n = 0 to 3) |                |                              |                                                                                                                                               |            |      |              |            |     |

|              | BC15 to<br>BC0 |                              | Byte transfer count setting or remaining<br>byte transfer count during DMA transfer<br>Byte transfer count 1 or remaining byte transfer count |            |      |              |            |     |

|              | 0000H          | Byte trar                    |                                                                                                                                               |            |      |              |            |     |

|              | 0001H          | Byte trar                    | Byte transfer count 2 or remaining byte transfer count                                                                                        |            |      |              |            |     |

|              | :              | :                            |                                                                                                                                               |            |      |              |            |     |

|              | FFFFH          | Puto tron                    | ofor count                                                                                                                                    | 65 526 (01 |      | ning byte tr | anofor cou | nt  |

## DC characteristics

## $(T_{A} = -40 \text{ to } +85^{\circ}\text{C}, \text{ V}_{DD} = \text{AV}_{DD} = \text{EV}_{DD} = 2.2 \text{ to } 2.7 \text{ V}, \text{ V}_{SS} = \text{AV}_{SS} = \text{EV}_{SS} = 0 \text{ V})$

(2/3)

| Parameter                          | Symbol |                                   | Conditions              |                       | MIN. | TYP.                       | MAX.             | Unit |

|------------------------------------|--------|-----------------------------------|-------------------------|-----------------------|------|----------------------------|------------------|------|

| Supply current <sup>Note</sup>     | IDD1   | Normal                            | $V_{DD} = 2.2$ to 2.7 V | @2 to 20 MHz          |      | $0.8 \times f_{XX} + 2.5$  | 1.58 × fxx + 6.0 | mA   |

|                                    |        | operation                         |                         | fxx = 2 MHz           |      | 4.1                        | 9.2              | mA   |

| V850ES/SA2                         |        | All peripheral<br>functions       |                         | fxx = 4 MHz           |      | 5.7                        | 12.3             | mA   |

| μPD70F3201,                        |        | operating                         |                         | fxx = 8 MHz           |      | 8.9                        | 18.6             | mA   |

| $\lfloor \mu$ PD70F3201Y $\rfloor$ |        |                                   |                         | fxx = 10 MHz          |      | 10.5                       | 21.8             | mA   |

|                                    |        |                                   |                         | fxx = 12 MHz          |      | 12.1                       | 25.0             | mA   |

| V850ES/SA3                         |        |                                   |                         | fxx = 17 MHz          |      | 16.1                       | 31.9             | mA   |

| (µPD70F3204,                       |        |                                   |                         | fxx = 20 MHz          |      | 18.5                       | 37.6             | mA   |

| <i>µ</i> PD70F3204Y ∫              | IDD2   | HALT mode                         | VDD = 2.2 to 2.7 V      | @2 to 20 MHz          |      | $0.37 \times f_{xx} + 2.0$ | 0.7 × fxx + 3.0  | mA   |

|                                    |        | All peripheral                    |                         | fxx = 2 MHz           |      | 2.7                        | 4.4              | mA   |

|                                    |        | functions                         |                         | fxx = 4 MHz           |      | 3.5                        | 5.8              | mA   |

|                                    |        | operating                         |                         | fxx = 8 MHz           |      | 5.0                        | 8.6              | mA   |

|                                    |        |                                   |                         | fxx = 10 MHz          |      | 6.2                        | 10.0             | mA   |

|                                    |        |                                   |                         | fxx = 12 MHz          |      | 6.9                        | 11.4             | mA   |

|                                    |        |                                   |                         | fxx = 17 MHz          |      | 8.2                        | 14.9             | mA   |

|                                    |        |                                   |                         | fxx = 20 MHz          |      | 9.4                        | 17.0             | mA   |

|                                    | Іррз   | IDLE mode $V_{DD} = 2.2$ to 2.7 V |                         | @2 to 20 MHz          |      | 40 × fxx + 300             | 70 × fxx + 500   | μA   |

|                                    |        | RTC operation                     |                         | fxx = 2 MHz           |      | 380                        | 640              | μA   |

|                                    |        |                                   |                         | fxx = 4 MHz           |      | 460                        | 780              | μA   |

|                                    |        |                                   |                         | fxx = 8 MHz           |      | 620                        | 1060             | μA   |

|                                    |        |                                   |                         | fxx = 10 MHz          |      | 700                        | 1200             | μA   |

|                                    |        |                                   |                         | fxx = 12 MHz          |      | 780                        | 1340             | μA   |

|                                    |        |                                   |                         | fxx = 17 MHz          |      | 980                        | 1690             | μA   |

|                                    |        |                                   |                         | fxx = 20 MHz          |      | 1100                       | 1900             | μA   |

|                                    | DD4    | STOP mode                         | Sub oscillator,         | T <sub>A</sub> = 25°C |      | 4                          | 20               | μA   |

|                                    |        |                                   | Only RTC<br>operates    | T <sub>A</sub> = 85°C |      | -                          | 60               | μA   |

|                                    |        |                                   | Sub oscillator          | T <sub>A</sub> = 25°C |      | 1                          | 10               | μA   |

|                                    |        |                                   | stopped<br>(XT1 = Vss)  | $T_A = 85^{\circ}C$   |      | -                          | 50               | μA   |

|                                    | IDD5   | Subclock operat                   | tion mode (fxr = 3      | 2.768 kHz)            |      | 150                        | 250              | μA   |

|                                    | DD6    | Sub-IDLE mode<br>(fxt = 32.768 kH |                         | $T_A = 25^{\circ}C$   |      | 4                          | 20               | μA   |

|                                    |        | -                                 | d, RTC operates         | $T_A = 85^{\circ}C$   |      | _                          | 60               | μA   |

Note The typical value of VDD is 2.5 V. The value does not include the current consumed at the output buffer.

Remark fxx: Main clock frequency (MHz)

| Symbol        | Name                                         | Unit             | Page |

|---------------|----------------------------------------------|------------------|------|

| DDA1H         | DMA destination address register 1H          | DMAC             | 411  |

| DDA1L         | DMA destination address register 1L          | DMAC             | 411  |

| DDA2H         | DMA destination address register 2H          | DMAC             | 411  |

| DDA2L         | DMA destination address register 2L          | DMAC             | 411  |

| DDA3H         | DMA destination address register 3H          | DMAC             | 411  |

| DDA3L         | DMA destination address register 3L          | DMAC             | 411  |

| DMAIC0        | Interrupt control register                   | INTC             | 441  |

| DMAIC1        | Interrupt control register                   | INTC             | 441  |

| DMAIC2        | Interrupt control register                   | INTC             | 441  |

| DMAIC3        | Interrupt control register                   | INTC             | 441  |

| DSA0H         | DMA source address register 0H               | DMAC             | 410  |

| DSA0L         | DMA source address register 0L               | DMAC             | 410  |

| DSA1H         | DMA source address register 1H               | DMAC             | 410  |

| DSA1L         | DMA source address register 1L               | DMAC             | 410  |

| DSA2H         | DMA source address register 2H               | DMAC             | 410  |

| DSA2L         | DMA source address register 2L               | DMAC             | 410  |

| DSA3H         | DMA source address register 3H               | DMAC             | 410  |

| DSA3L         | DMA source address register 3L               | DMAC             | 410  |

| DTFR0         | DMA trigger factor register 0                | DMAC             | 415  |

| DTFR1         | DMA trigger factor register 1                | DMAC             | 415  |

| DTFR2         | DMA trigger factor register 2                | DMAC             | 415  |

| DTFR3         | DMA trigger factor register 2                | DMAC             | 415  |

| DUFR3<br>DWC0 |                                              | BCU              | -    |

| ECR           | Data wait control register 0                 | CPU              | 188  |

| -             | Interrupt source register                    |                  | 58   |

| EIPC          | Interrupt status saving register             | CPU              | 57   |

|               | Interrupt status saving register             | CPU              | 57   |

| EXIMC         | External bus interface mode control register | BCU              | 180  |

| FEPC          | NMI status saving register                   | CPU              | 58   |

| FEPSW         | NMI status saving register                   | CPU              | 58   |

| HOUR          | Hour count register                          | RTC              | 263  |

| HOURB         | Hour count setting register                  | RTC              | 264  |

| IIC           | IIC shift register                           | I <sup>2</sup> C | 363  |

| IICC          | IIC control register                         | I <sup>2</sup> C | 353  |

| IICCL         | IIC clock select register                    | I <sup>2</sup> C | 361  |

| IICIC         | Interrupt control register                   | INTC             | 441  |

| IICS          | IIC status register                          | l <sup>2</sup> C | 358  |

| IICX          | IIC function expansion register              | l <sup>2</sup> C | 362  |

| MR0           | Interrupt mask register 0                    | INTC             | 442  |

| IMR0H         | Interrupt mask register 0H                   | INTC             | 442  |

| IMR0L         | Interrupt mask register 0L                   | INTC             | 442  |

| MR1           | Interrupt mask register 1                    | INTC             | 442  |

| MR1H          | Interrupt mask register 1H                   | INTC             | 442  |

| MR1L          | Interrupt mask register 1L                   | INTC             | 442  |

| MR2           | Interrupt mask register 2                    | INTC             | 442  |

|        |                                         |       | (7/      |

|--------|-----------------------------------------|-------|----------|

| Symbol | Name                                    | Unit  | Page     |

| TCL5   | Timer clock selection register 5        | Timer | 243      |

| TM0    | Timer 0                                 | Timer | 214      |

| TM1    | Timer 1                                 | Timer | 214      |

| TM2    | Timer counter 2                         | Timer | 241      |

| ТМЗ    | Timer counter 3                         | Timer | 241      |

| TM4    | Timer counter 4                         | Timer | 241      |

| TM5    | Timer counter 5                         | Timer | 241      |

| TMC00  | Timer control register 00               | Timer | 217      |

| TMC01  | Timer control register 01               | Timer | 219      |

| TMC10  | Timer control register 10               | Timer | 217      |

| TMC11  | Timer control register 11               | Timer | 217      |

| TMC2   | Timer mode control register 2           | Timer | 244      |

| ТМС3   | Timer mode control register 3           | Timer | 244      |

| TMC4   | Timer mode control register 4           | Timer | 244      |

| TMC5   | Timer mode control register 5           | Timer | 244      |

| TMIC2  | Interrupt control register              | INTC  | 441      |

| ТМІСЗ  | Interrupt control register              | INTC  | 441      |

| TMIC4  | Interrupt control register              | INTC  | 441      |

| TMIC5  | Interrupt control register              | INTC  | 441      |

| TXB0   | Transmit buffer register 0              | UART  | 309      |

| TXB1   | Transmit buffer register 1              | UART  | 309      |

| VSWC   | System wait control register            | BCU   | 87       |

| WDCS   | Watchdog timer clock selection register | WDT   | 272      |

| WDTIC  | Interrupt control register              | INTC  | 441      |

| WDTM   | Watchdog timer mode register            | WDT   | 273, 444 |

| WEEK   | Week count register                     | RTC   | 265      |

| WEEKB  | Week count setting register             | RTC   | 265      |