# E·XF Renesas Electronics America Inc - UPD78F0752MA-FAA-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Not For New Designs                                                                  |

| Core Processor             | 78K/0                                                                                |

| Core Size                  | 8-Bit                                                                                |

| Speed                      | 10MHz                                                                                |

| Connectivity               | -                                                                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                                   |

| Number of I/O              | 9                                                                                    |

| Program Memory Size        | 16KB (16K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | ·                                                                                    |

| RAM Size                   | 768 x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                          |

| Data Converters            | A/D 5x10b                                                                            |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 16-SSOP (0.173", 4.40mm Width)                                                       |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0752ma-faa-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.3.3 78K0/IB2

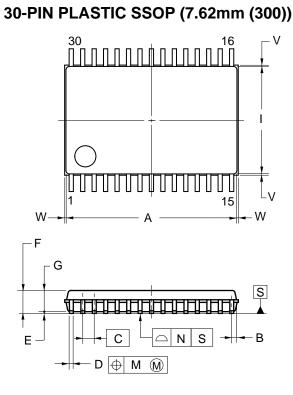

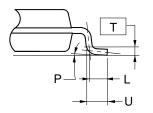

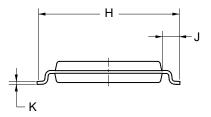

• 30-pin plastic SSOP (7.62 mm (300))

|                                               |                                                  |          |                 | 1               |                            |  |

|-----------------------------------------------|--------------------------------------------------|----------|-----------------|-----------------|----------------------------|--|

|                                               | ANI6/P26/CMPCOM -                                | 1        | 30              |                 |                            |  |

|                                               | ANI5/P25/CMP1+ ○ <del></del> ►                   | 2        | 29              | > ANI7/P27      |                            |  |

|                                               | ANI4/P24/CMP0+ O-                                | 3        | 28              | O AVss          |                            |  |

|                                               | P60/SCLA0/TxD6 ○                                 | 4<br>5   | 27<br>26        |                 |                            |  |

|                                               | P02/SSI11/INTP5                                  | 6        | 20              |                 |                            |  |

|                                               | RESET/P125 O                                     | 7        | 24              |                 |                            |  |

| P1                                            | 22/X2/EXCLK/TOOLD0 O                             | 8        | 23              | ← → O ANI3/P23/ |                            |  |

| P121/X1/TO0                                   | DLC0/ <ti000>/<intp0> ○</intp0></ti000>          | 9        | 22              |                 | /INTP0                     |  |

|                                               | REGC O                                           | 10       | 21              |                 | /TI010                     |  |

|                                               | Vss O                                            | 11       | 20              | ← → P30/TOH1    |                            |  |

|                                               |                                                  | 12       | 19              |                 | 0/INTP2/TOOLC1             |  |

|                                               | P37/SO11 ○ <del></del><br>P36/SI11 ○ <del></del> | 13<br>14 | 18<br>17        |                 | 1/INTP3/TOOLD1             |  |

|                                               | P35/SCK11 0-                                     | 14       | 17              |                 |                            |  |

|                                               |                                                  |          |                 |                 |                            |  |

|                                               |                                                  |          |                 |                 |                            |  |

| AMP- <sup>Note</sup> , AMP+ <sup>Note</sup> : | Amplifier Input                                  |          | REGC :          |                 | Regulator Capacitance      |  |

| AMPOUT <sup>Note</sup> :                      | Amplifier Output                                 |          | RESET :         |                 | Reset                      |  |

| PGAIN <sup>Note</sup> :                       | Programmable Gain                                |          | RxD6 :          |                 | Receive Data               |  |

|                                               | Amplifier Input                                  |          | SCLA0, SCK11    | :               | Serial Clock Input/Output  |  |

| ANI0 to ANI8 :                                | Analog Input                                     |          | SDAA0 :         |                 | Serial Data Input/Output   |  |

| AVREF :                                       | Analog Reference                                 |          | SI11 :          |                 | Serial Data Input          |  |

|                                               | Voltage                                          |          | SO11 :          |                 | Serial Data Output         |  |

| AVss:                                         | Analog Ground                                    |          | SSI11 :         |                 | Serial Interface Chip      |  |

| EXCLK :                                       | External Clock Input                             |          | TI000, TI010, T | 51 :            | Timer Input                |  |

|                                               | (Main System Clock)                              |          | TO00, TOH1 :    |                 | Timer Output               |  |

| CMP0+ to CMP2+ :                              | Comparator Input                                 |          | TOOLCO, TOOI    | _C1 :           | Clock Input for Tool       |  |

| CMPCOM :                                      | Comparator Common Inp                            | out      | TOOLD0, TOOL    | _D1 :           | Data Input/Output for Tool |  |

| INTP0 to INTP5 :                              | External Interrupt Input                         |          | TOX00, TOX01    | , TOX10,        |                            |  |

| P00 to P02 :                                  | Port 0                                           |          | TOX11 :         |                 | Timer Output               |  |

| P20 to P27 :                                  | Port 2                                           |          | TxD6 :          |                 | Transmit Data              |  |

| P30 to P37 :                                  | Port 3                                           |          | VDD:            |                 | Power Supply               |  |

| P60, P61 :                                    | Port 6                                           |          | Vss:            |                 | Ground                     |  |

| P70 :                                         | Port 7                                           |          | X1, X2 :        |                 | Crystal Oscillator         |  |

| P121, P122, P125 :                            | Port 12                                          |          |                 |                 | (Main System Clock)        |  |

Note  $\mu$ PD78F0755, 78F0756 (products with operational amplifier) only

Cautions 1. Connect the REGC pin to Vss via a capacitor (0.47 to 1  $\mu$ F).

- 2. ANI0/P20/AMP-, ANI1/P21/AMPOUT/PGAIN, ANI2/P22/AMP+, ANI3/P23/CMP2+, ANI4/P24/CMP0+, ANI5/P25/CMP1+, ANI6/P26/CMPCOM, ANI7/P27, and ANI8/P70 are set in the analog input mode after release of reset.

- 3. RESET/P125 immediately after release of reset is set in the external reset input.

**Remark** Functions in angle brackets < > can be assigned by setting the input switch control register (MUXSEL).

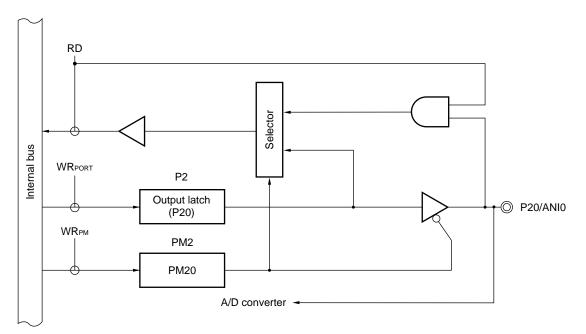

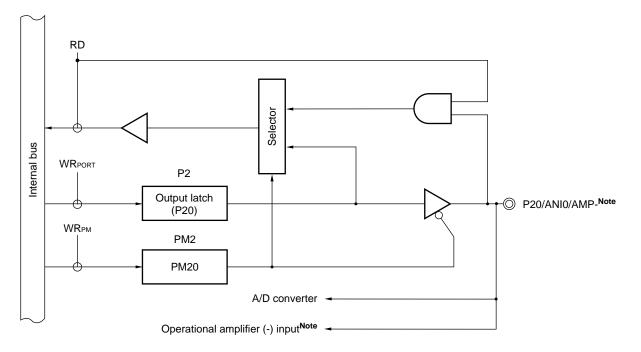

Figure 4-4. Block Diagram of P20

## (1) 78K0/IY2

#### (2) 78K0/IA2, 78K0/IB2

Note Products with operational amplifier only

- P2: Port register 2

- PM2: Port mode register 2

- RD: Read signal

- WR××: Write signal

| Pin Name | Alternate Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PM××   | P××                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|          | Function Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I/O    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |

| P31      | TOX00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Output | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0 |

|          | INTP2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Input  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | × |

|          | TOOLC1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Input  | ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | × |

| P32      | TOX01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Output | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0 |

|          | INTP3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Input  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | × |

|          | TOOLD1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | I/O    | 0<br>1<br>×<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | × |

| P33      | TOX10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Output | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0 |

| P34      | TOX11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Output | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0 |

|          | INTP4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Input  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | × |

| P35      | SCK11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Input  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | × |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Output | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 |

| P36      | SI11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Input  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | × |

| P37      | SO11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Output | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0 |

| P60      | SCLA0 <sup>Notes 1, 2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | I/O    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 |

|          | TxD6 <sup>Note 3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Output | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 |

| P61      | SDAA0 <sup>Notes 1, 2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | I/O    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 |

|          | RxD6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Input  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | × |

| P70      | ANI8 <sup>Note 4</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Input  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | × |

| P121     | X1 <sup>Note 5</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -      | х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | × |

|          | TOOLC0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Input  | 1         ×         0         1         ×         0         1         ×         0         1         1         0         1         0         1         0         0         0         0         0         0         0         0         0         0         0         0         0         1         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         × <td< td=""><td>×</td></td<> | × |

|          | <ti000></ti000>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Input  | ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | × |

|          | <intp0></intp0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Input  | ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | × |

| P122     | TP2         Input           NOLC1         Input           NOLC1         Input           NOL01         Output           TP3         Input           NOLD1         I/O           NOLD1         I/O           NOLD1         I/O           NOLD1         I/O           NOLD1         I/O           NOLD1         Output           NOLD1         Output           NOLD1         Output           NOLD1         Output           NOLD1         Output           NOLD1         Input           NOLD2         Input           NOLD2 | ×      | ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |

|          | EXCLK <sup>Note 5</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Input  | ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | × |

|          | TOOLD0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | I/O    | ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | × |

| P125     | RESET <sup>Note 6</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Input  | ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | × |

| Table 4-15. Settings of Port Mode Register and Output Latch When Using Alternate Function (78K0/IB2 | (30 pins)) (2/2) |

|-----------------------------------------------------------------------------------------------------|------------------|

|                                                                                                     | (00 p            |

**Notes 1.** During I<sup>2</sup>C communication, set SCLA0 and SDAA0 to N-ch open drain output (V<sub>DD</sub> tolerance) mode by using POM6 register (refer to **4.3 (5) Port output mode register 6 (POM6)**).

2. When using an input compliant with the SMBus Specifications in I<sup>2</sup>C communication, select the SMBus input buffer by using PIM6 register (refer to **4.3 (4) Port input mode register 6 (PIM6)**).

- 3. During UART/DALI communication, set TxD6 to normal output (CMOS output) mode by using POM6 register (refer to 4.3 (5) Port output mode register 6 (POM6)).

- 4. The pin function can be selected by using ADPC1 register, PM7 register, and ADS register. Refer to Table

4-12 of 4.2.5 Port 7.

- When using the P121 and P122 pins to connect a resonator for the main system clock (X1, X2) or to input an external clock for the main system clock (EXCLK), the X1 oscillation mode or external clock input mode must be set by using OSCCTL register (for details, refer to 5.3 (1) Clock operation mode select register (OSCCTL)). The reset value of OSCCTL is 00H (both P121 and P122 are input port pins).

- 6. Clear RSTM bit (bit 5 of RSTMASK register) to 0 when using P125 as an external reset input (RESET).

Remark ×: Don't care

PM××: Port mode register

Pxx: Port output latch

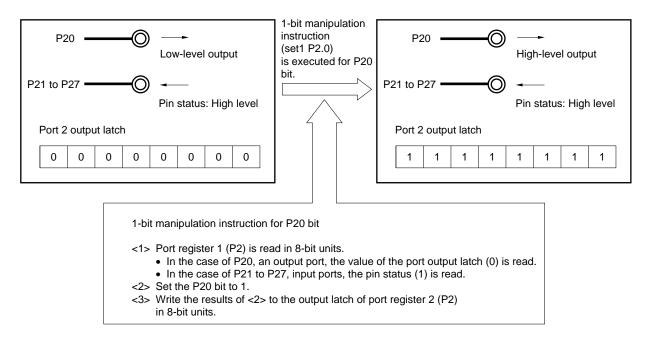

## 4.6 Cautions on 1-Bit Manipulation Instruction for Port Register n (Pn)

When a 1-bit manipulation instruction is executed on a port that provides both input and output functions, the output latch value of an input port that is not subject to manipulation may be written in addition to the targeted bit.

Therefore, it is recommended to rewrite the output latch when switching a port from input mode to output mode.

- <Example> When P20 is an output port, P21 to P27 are input ports (all pin statuses are high level), and the port latch value of port 2 is 00H, if the output of output port P20 is changed from low level to high level via a 1-bit manipulation instruction, the output latch value of port 2 is FFH.

- Explanation: The targets of writing to and reading from the Pn register of a port whose PMnm bit is 1 are the output latch and pin status, respectively.

- A 1-bit manipulation instruction is executed in the following order in the 78K0/lx2 microcontrollers.

- <1> The Pn register is read in 8-bit units.

- <2> The targeted one bit is manipulated.

- <3> The Pn register is written in 8-bit units.

In step <1>, the output latch value (0) of P20, which is an output port, is read, while the pin statuses of P21 to P27, which are input ports, are read. If the pin statuses of P21 to P27 are high level at this time, the read value is FEH.

The value is changed to FFH by the manipulation in <2>.

FFH is written to the output latch by the manipulation in <3>.

Remark The following instructions are 1-bit manipulation instructions.

• MOV1, AND1, OR1, XOR1, SET1, CLR1, NOT11, NOT1

| Address: FF9 | 6H After re                                                                    | eset: 00H R/  | /W                                                             |    |   |   |         |        |

|--------------|--------------------------------------------------------------------------------|---------------|----------------------------------------------------------------|----|---|---|---------|--------|

| Symbol       | 7                                                                              | 6             | 5                                                              | 4  | 3 | 2 | <1>     | <0>    |

| TX1CTL2      | 0                                                                              | 0             | 0                                                              | 0  | 0 | 0 | TX1ADEN | TX1CCS |

|              |                                                                                |               |                                                                |    |   |   |         |        |

|              | TX1ADEN Control of generating A/D conversion synchronization trigger from TMX1 |               |                                                                |    |   |   |         |        |

|              | 0                                                                              | Disables gene | Disables generating A/D conversion synchronization trigger     |    |   |   |         |        |

|              | 1                                                                              | Enables gene  | Enables generating A/D conversion synchronization trigger Note |    |   |   |         |        |

|              |                                                                                |               |                                                                |    |   |   |         |        |

|              | TX1CCS                                                                         |               | TX1CCR0 register operation                                     |    |   |   |         |        |

|              | 0                                                                              | Operates as o | compare registe                                                | er |   |   |         |        |

### Figure 6-11. Format of 16-Bit Timer X1 Operation Control Register 2 (TX1CTL2)

- **Note** When enabling generation of the A/D conversion synchronization trigger (TX1ADEN = 1), set the TX1CCR0 register to operate as a compare register (TX1CCS = 0), because the A/D conversion synchronization trigger is generated upon a match between the counter and the TX1CCR0 register.

- Cautions 1. During the 16-bit timer operation, setting the other bits of TX1CTL2 is prohibited. However, TX1CTL2 can be refreshed (the same value is written).

- 2. The registers used by the A/D converter (ADM0, ADPC0, ADPC1, ADS) can be rewritten while the 16-bit timer X1 is operating.

- A/D conversion synchronization triggers that occur while A/D conversion is stopped (ADCS = 0) are invalid. A/D conversion synchronization triggers that occur after A/D conversion has been enabled (ADCS = 1) are valid.

## (4) 16-bit timer X0 operation control register 3 (TX0CTL3)

1

TX0CTL3 is a register that sets the mode of the interlocking function with comparator 2 and INTP0, and sets the operation when restarting upon comparator output.

TX0CTL3 can be set by a 1-bit or 8-bit memory manipulation instruction.

Operates as capture register

Reset signal generation clears TX0CTL3 to 00H.

| Address: FF9                                                                                                                                 | BH After re                  | eset: 00H R | /W |   |         |                  |            |         |

|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------|----|---|---------|------------------|------------|---------|

| Symbol                                                                                                                                       | 7                            | 6           | 5  | 4 | <3>     | <2>              | <1>        | <0>     |

| TX1IOC0                                                                                                                                      | 0                            | 0           | 0  | 0 | TX1TOC1 | TX1TOC0          | TX1TOL1    | TX1TOL0 |

|                                                                                                                                              |                              |             |    |   |         |                  |            |         |

|                                                                                                                                              | TX1TOC1 TOX11 output control |             |    |   |         |                  |            |         |

| 0Disables timer output (Fixes to low-level output when TX1TOL1 = 0, and fixes to his<br>when TX1TOL1 = 1.)1Enables timer output (PWM output) |                              |             |    |   |         | fixes to high-le | vel output |         |

|                                                                                                                                              |                              |             |    |   |         |                  |            |         |

### Figure 6-16. 16-bit timer X1 output control register 0 (TX1IOC0)

| TX1TOC0 | TOX10 output control                                                                                                 |

|---------|----------------------------------------------------------------------------------------------------------------------|

| 0       | Disables timer output (Fixes to low-level output when TX1TOL0 = 0, and fixes to high-level output when TX1TOL0 = 1.) |

| 1       | Enables timer output (PWM output)                                                                                    |

| TX1TOL1 | Default TOX11 output state setting |

|---------|------------------------------------|

| 0       | Normal output (low level)          |

| 1       | Inverted output (high level)       |

| TX1TOL0 | Default TOX10 output state setting |

|---------|------------------------------------|

| 0       | Normal output (low level)          |

| 1       | Inverted output (high level)       |

- Cautions 1. During the timer operation, setting the other bits of TX1IOC0 is prohibited. However, TX1IOC0 can be refreshed (the same value is written).

- 2. The actual TOX10/P33 and TOX11/P34/INTP4 pin outputs are determined depending on PM33, P33, PM34, and P34 besides TOX10 and TOX11 outputs.

| Register | Bit                       |                                                  |                                                  | Operatio                                         | on mode                                          |         |                       |

|----------|---------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|---------|-----------------------|

|          |                           | TMXn-or<br>(n =                                  | -                                                | Synchronous                                      | s start mode                                     | -       | is start/clear<br>ode |

|          |                           |                                                  | TMX1                                             | Master                                           | Slave                                            | Master  | Slave                 |

|          |                           |                                                  |                                                  | (TMX0)                                           | (TMX1)                                           | (TMX0)  | (TMX1)                |

| TX0CTL4  | TX0CMP1RP                 | Setting                                          |                                                  | Setting                                          |                                                  | -       | -                     |

|          | TX0CMP1RM1,<br>TX0CMP1RM0 | Setting is<br>valid<br>when<br>TX0CMP<br>1RP = 0 | _                                                | Setting is<br>valid<br>when<br>TX0CMP<br>1RP = 0 | _                                                | _       | _                     |

|          | TX0CMP0RP                 | Setting                                          |                                                  | Setting                                          |                                                  | -       | -                     |

|          | TX0CMP0RM1,<br>TX0CMP0RM0 | Setting is<br>valid<br>when<br>TX0CMP<br>0RP = 0 | _                                                | Setting is<br>valid<br>when<br>TX0CMP<br>0RP = 0 | _                                                | _       | _                     |

| TX1CTL4  | TX1CMP1RM1,<br>TX1CMP1RM0 | -                                                | Setting is<br>valid<br>when<br>TX0CMP<br>1RP = 1 | _                                                | Setting is<br>valid<br>when<br>TX0CMP<br>1RP = 1 | _       | -                     |

|          | TX1CMP0RM1,<br>TX1CMP0RM0 | -                                                | Setting is<br>valid<br>when<br>TX0CMP<br>0RP = 1 | _                                                | Setting is<br>valid<br>when<br>TX0CMP<br>0RP = 1 | _       | _                     |

| TX0IOC0  | TX0TOC1                   | Setting                                          | -                                                | Setting                                          | -                                                | Setting | -                     |

|          | ТХ0ТОС0                   | Setting                                          | -                                                | Setting                                          | -                                                | Setting | -                     |

|          | TX0TOL1                   | Setting                                          | -                                                | Setting                                          | -                                                | Setting | -                     |

|          | TX0TOL0                   | Setting                                          | -                                                | Setting                                          | -                                                | Setting | -                     |

| TX1IOC0  | TX1TOC1                   | _                                                | Setting                                          | -                                                | Setting                                          | -       | Setting               |

|          | TX1TOC0                   | _                                                | Setting                                          | -                                                | Setting                                          | -       | Setting               |

|          | TX1TOL1                   | -                                                | Setting                                          | -                                                | Setting                                          | -       | Setting               |

|          | TX1TOL0                   | -                                                | Setting                                          | -                                                | Setting                                          | -       | Setting               |

| Table 6-2. Register Setting Bits Controlling Operation | Mode and 16-bit Timers X0 and X1 (2/2) |

|--------------------------------------------------------|----------------------------------------|

|--------------------------------------------------------|----------------------------------------|

## <R> 6.4 Operation of 16-Bit Timer/Event Counter 00

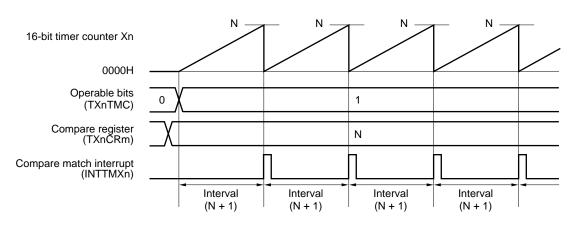

#### (1) Interval timer operation

If bit 7 (TXnTMC) of the 16-bit timer Xn operation control register 0 (TXnCTL0) is set to 1, the count operation is started in synchronization with the count clock.

When the value of the 16-bit timer counter Xn (TMXn) later matches the value of TXnCRm, TMXn is cleared to 0000H and a match interrupt signal (INTTMXn) is generated. This INTTMXn signal enables TMXn to operate as an interval timer.

Remarks 1. For how to enable the INTTMXn interrupt, refer to CHAPTER 17 INTERRUPT FUNCTIONS.

**2.** m = 1, 3

n = 0, 1

#### Figure 6-18. Basic Timing Example of Interval Timer Operation

**Remark** m = 1, 3

n = 0, 1

## CHAPTER 10 WATCHDOG TIMER

#### 10.1 Functions of Watchdog Timer

The watchdog timer is mounted onto all 78K0/Ix2 microcontroller products.

The watchdog timer operates on the internal low-speed oscillation clock.

The watchdog timer is used to detect an inadvertent program loop. If a program loop is detected, an internal reset signal is generated.

Program loop is detected in the following cases.

- If the watchdog timer counter overflows

- If a 1-bit manipulation instruction is executed on the watchdog timer enable register (WDTE)

- If data other than "ACH" is written to WDTE

- If data is written to WDTE during a window close period

- If the instruction is fetched from an area not set by the IMS register (detection of an invalid check while the CPU hangs up)

- If the CPU accesses an area that is not set by the IMS register (excluding FB00H to FFFFH) by executing a read/write instruction (detection of an abnormal access during a CPU program loop)

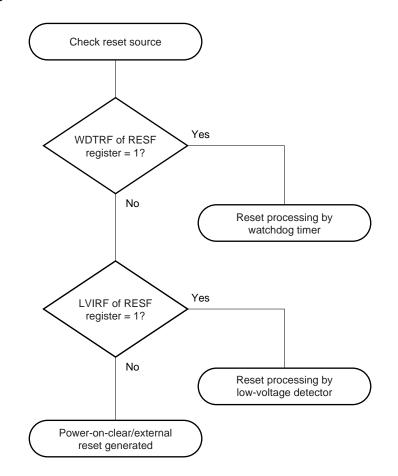

When a reset occurs due to the watchdog timer, bit 4 (WDTRF) of the reset control flag register (RESF) is set to 1. For details of RESF, refer to **CHAPTER 20 RESET FUNCTION**.

- Cautions 1. Set a channel to be used for A/D conversion in the input mode by using port mode registers 2 and 7 (PM2, PM7).

- 2. Set ADS after PGA operation setting when selecting the PGA output signal as analog input. Set ADS after single AMP operation setting when selecting the operational amplifier output signal as analog input.

- 3. To select the internal voltage (1.2 V) as an analog input, set the ADCS bit to 1 when at least 10  $\mu$ s have elapsed after having set the V12SEL bit to 1 while the A/D conversion operation was stopped (ADCS = 0).

- 4. If data is written to ADS, a wait cycle is generated. Do not write data to ADS when the peripheral hardware clock (fPRs) is stopped. For details, refer to CHAPTER 31 CAUTIONS FOR WAIT.

## (4) Port mode register 2 (PM2)

When using AMP-/ANI0/P20, AMPOUT/PGAIN/ANI1/P21, and AMP+/ANI2/P22 pins for the operational amplifier, set PM20 to PM22 to 1.

The output latches of P20 to P22 at this time may be 0 or 1.

If PM20 to PM22 are set to 0, they cannot be used as the operational amplifier pins.

PM2 can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation sets PM2 to FFH.

#### Figure 12-5. Format of Port Mode Register 2 (PM2)

#### (1) 78K0/IY2

| Address: FF | 22H After | reset: FFH | R/W  |      |      |      |   |      |

|-------------|-----------|------------|------|------|------|------|---|------|

| Symbol      | 7         | 6          | 5    | 4    | 3    | 2    | 1 | 0    |

| PM2         | 1         | 1          | PM25 | PM24 | PM23 | PM22 | 1 | PM20 |

Caution Be sure to set bits 1, 6, and 7 of PM2 to 1.

#### (2) 78K0/IA2

| Address: FF | 22H After | reset: FFH | R/W  |      |      |      |      |      |

|-------------|-----------|------------|------|------|------|------|------|------|

| Symbol      | 7         | 6          | 5    | 4    | 3    | 2    | 1    | 0    |

| PM2         | 1         | 1          | PM25 | PM24 | PM23 | PM22 | PM21 | PM20 |

Caution Be sure to set bits 6 and 7 of PM2 to 1.

#### (3) 78K0/IB2

Address: FF22H After reset: FFH R/W

| Symbol | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|--------|------|------|------|------|------|------|------|------|

| PM2    | PM27 | PM26 | PM25 | PM24 | PM23 | PM22 | PM21 | PM20 |

| PM2n | P2n pin I/O mode selection (n = 0 to 7) |

|------|-----------------------------------------|

| 0    | Output mode (output buffer on)          |

| 1    | Input mode (output buffer off)          |

| 5                                                       | <4>    | <3>        | <2>                                                   | <1>                                                                                               | <0>                                                                                               |  |  |  |  |

|---------------------------------------------------------|--------|------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--|--|--|--|

| 0                                                       | C0VRS4 | C0VRS3     | C0VRS2                                                | C0VRS1                                                                                            | C0VRS0                                                                                            |  |  |  |  |

| Internal reference voltage generation operation control |        |            |                                                       |                                                                                                   |                                                                                                   |  |  |  |  |

| Stops operation                                         |        |            |                                                       |                                                                                                   |                                                                                                   |  |  |  |  |

| ion                                                     |        |            |                                                       |                                                                                                   |                                                                                                   |  |  |  |  |

| C0VRS2                                                  | C0VRS1 | C0VRS0     | Peference                                             | voltage level (E                                                                                  | (AO) setting                                                                                      |  |  |  |  |

| 0                                                       | 0      | 0          | 0.05 V (TYP.)                                         | voltage level (E                                                                                  | , to) setting                                                                                     |  |  |  |  |

| 0                                                       | 0      | 1          | 0.03 V (TTP.)                                         |                                                                                                   |                                                                                                   |  |  |  |  |

| 0                                                       | 1      | 0          | 0.15 V (TYP.)                                         |                                                                                                   |                                                                                                   |  |  |  |  |