# E. Renesas Electronics America Inc - UPD78F0753MC-CAA-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0                                                                                |

| Core Size                  | 8-Bit                                                                                |

| Speed                      | 10MHz                                                                                |

| Connectivity               | DALI, I <sup>2</sup> C, LINbus, UART/USART                                           |

| Peripherals                | LVD, POR, PWM, WDT                                                                   |

| Number of I/O              | 13                                                                                   |

| Program Memory Size        | 8KB (8K x 8)                                                                         |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 512 x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                          |

| Data Converters            | A/D 6x10b                                                                            |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                                       |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0753mc-caa-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# (g) SSI11

This is a chip select input pin of serial interface CSI11.

### 2.2.2 P20 to P27 (port 2)

P20 to P27 function as an I/O port. These pins also function as pins for A/D converter analog input, operational amplifier I/O, and PGA input.

| 78K0/IY2                       | 78K0/IA2                                               | 78K0/IB2                                               |

|--------------------------------|--------------------------------------------------------|--------------------------------------------------------|

| 16 Pins                        | 20 Pins                                                | 30 Pins/32 Pins                                        |

| P20/ANI0                       | P20/ANI0/AMP- <sup>Note</sup>                          | P20/ANI0/AMP- <sup>Note</sup>                          |

| P21/ANI1/PGAIN <sup>Note</sup> | P21/ANI1/AMPOUT <sup>Note</sup> /PGAIN <sup>Note</sup> | P21/ANI1/AMPOUT <sup>Note</sup> /PGAIN <sup>Note</sup> |

| _                              | P22/ANI2/AMP+ <sup>Note</sup>                          | P22/ANI2/AMP+ <sup>Note</sup>                          |

| P23/ANI3/CMP2+                 | P23/ANI3/CMP2+                                         | P23/ANI3/CMP2+                                         |

| P24/ANI4/CMP0+                 | P24/ANI4/CMP0+                                         | P24/ANI4/CMP0+                                         |

| P25/ANI5/CMP1+                 | P25/ANI5/CMP1+                                         | P25/ANI5/CMP1+                                         |

| -                              | _                                                      | P26/ANI6/CMPCOM                                        |

| _                              | _                                                      | P27/ANI7                                               |

Note Products with operational amplifier only

The following operation modes can be specified in 1-bit units.

#### (1) Port mode

P20 to P27 function as an I/O port. P20 to P27 can be set to input or output port in 1-bit units using port mode register 2 (PM2).

#### (2) Control mode

P20 to P27 function as A/D converter analog input, operational amplifier I/O, and PGA input.

#### (a) ANI0 to ANI7

These are A/D converter analog input pins. When using these pins as analog input pins, refer to (5) ANI0/P20 to ANI7/P27 and ANI8/P70 in 11.6 Cautions for A/D Converter.

#### (b) AMP+, AMP-

These are operational amplifier input pins.

#### (c) AMPOUT

This is an operational amplifier output pin.

#### (d) PGAIN

This is a PGA (Programmable gain amplifier) input pin.

#### (e) CMP0+ to CMP2+

These are comparator input pins.

#### (7) Oscillation stabilization time select register (OSTS)

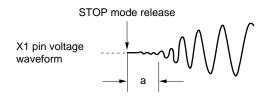

This register is used to select the X1 clock oscillation stabilization wait time when the STOP mode is released. When the X1 clock is selected as the CPU clock, the operation waits for the time set using OSTS after the STOP mode is released.

When the internal high-speed oscillation clock is selected as the CPU clock, confirm with OSTC that the desired oscillation stabilization time has elapsed after the STOP mode is released. The oscillation stabilization time can be checked up to the time set using OSTC.

OSTS can be set by an 8-bit memory manipulation instruction.

Reset signal generation sets OSTS to 05H.

#### Figure 5-8. Format of Oscillation Stabilization Time Select Register (OSTS)

Address: FFA4H After reset: 05H R/W Symbol 5 2 0 7 6 4 3 1 OSTS 0 0 0 0 0 OSTS2 OSTS1 OSTS0

| OSTS2 | OSTS1          | OSTS0 | Oscillation stabilization time selection |                  |  |

|-------|----------------|-------|------------------------------------------|------------------|--|

|       |                |       |                                          | fx = 10 MHz      |  |

| 0     | 0              | 1     | 2 <sup>11</sup> /fx                      | 204.8 μs         |  |

| 0     | 1              | 0     | 2 <sup>13</sup> /fx                      | 819.2 <i>μ</i> s |  |

| 0     | 1              | 1     | 2 <sup>14</sup> /fx                      | 1.64 ms          |  |

| 1     | 0              | 0     | 2 <sup>15</sup> /fx                      | 3.27 ms          |  |

| 1     | 0              | 1     | 2 <sup>16</sup> /fx                      | 6.55 ms          |  |

| 0     | ther than abov | ve    | Setting prohibited                       |                  |  |

| Cautions 1. | To set the STOP mode when the X1 clock is used as the CPU clock, set OSTS before |

|-------------|----------------------------------------------------------------------------------|

|             | executing the STOP instruction.                                                  |

- 2. Do not change the value of the OSTS register during the X1 clock oscillation stabilization time.

- 3. The oscillation stabilization time counter counts up to the oscillation stabilization time set by OSTS. If the STOP mode is entered and then released while the internal high-speed oscillation clock is being used as the CPU clock, set the oscillation stabilization time as follows.

- Desired OSTC oscillation stabilization time ≤ Oscillation stabilization time set by OSTS

Note, therefore, that only the status up to the oscillation stabilization time set by OSTS is set to OSTC after STOP mode is released.

4. The X1 clock oscillation stabilization wait time does not include the time until clock oscillation starts ("a" below).

| Address: FF9 | 6H After re | eset: 00H R/                      | /W                                                                     |   |   |   |         |        |

|--------------|-------------|-----------------------------------|------------------------------------------------------------------------|---|---|---|---------|--------|

| Symbol       | 7           | 6                                 | 5                                                                      | 4 | 3 | 2 | <1>     | <0>    |

| TX1CTL2      | 0           | 0                                 | 0                                                                      | 0 | 0 | 0 | TX1ADEN | TX1CCS |

|              |             |                                   |                                                                        |   |   |   |         |        |

|              | TX1ADEN     |                                   | Control of generating A/D conversion synchronization trigger from TMX1 |   |   |   |         |        |

|              | 0           | Disables gene                     | Disables generating A/D conversion synchronization trigger             |   |   |   |         |        |

|              | 1           | Enables gene                      | Enables generating A/D conversion synchronization trigger Note         |   |   |   |         |        |

|              |             |                                   |                                                                        |   |   |   |         |        |

|              | TX1CCS      |                                   | TX1CCR0 register operation                                             |   |   |   |         |        |

|              | 0           | Operates as compare register Note |                                                                        |   |   |   |         |        |

#### Figure 6-11. Format of 16-Bit Timer X1 Operation Control Register 2 (TX1CTL2)

- **Note** When enabling generation of the A/D conversion synchronization trigger (TX1ADEN = 1), set the TX1CCR0 register to operate as a compare register (TX1CCS = 0), because the A/D conversion synchronization trigger is generated upon a match between the counter and the TX1CCR0 register.

- Cautions 1. During the 16-bit timer operation, setting the other bits of TX1CTL2 is prohibited. However, TX1CTL2 can be refreshed (the same value is written).

- 2. The registers used by the A/D converter (ADM0, ADPC0, ADPC1, ADS) can be rewritten while the 16-bit timer X1 is operating.

- A/D conversion synchronization triggers that occur while A/D conversion is stopped (ADCS = 0) are invalid. A/D conversion synchronization triggers that occur after A/D conversion has been enabled (ADCS = 1) are valid.

### (4) 16-bit timer X0 operation control register 3 (TX0CTL3)

1

TX0CTL3 is a register that sets the mode of the interlocking function with comparator 2 and INTP0, and sets the operation when restarting upon comparator output.

TX0CTL3 can be set by a 1-bit or 8-bit memory manipulation instruction.

Operates as capture register

Reset signal generation clears TX0CTL3 to 00H.

# Figure 7-42. Example of Register Settings for PPG Output Operation (1/2)

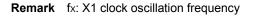

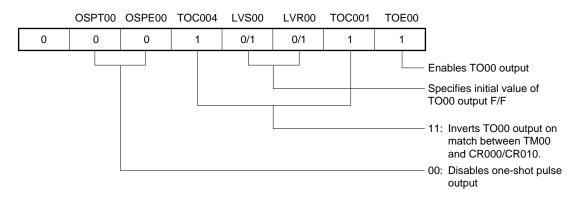

# (a) 16-bit timer mode control register 00 (TMC00)

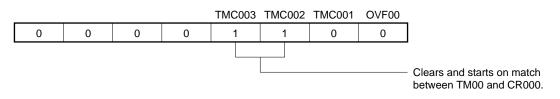

### (b) Capture/compare control register 00 (CRC00)

#### (c) 16-bit timer output control register 00 (TOC00)

#### (d) Prescaler mode register 00 (PRM00)

#### Figure 7-52. Example of Register Settings for Pulse Width Measurement (2/2)

# (e) 16-bit timer counter 00 (TM00)

By reading TM00, the count value can be read.

#### (f) 16-bit capture/compare register 000 (CR000)

This register is used as a capture register. Either the TI000 or TI010 pin is selected as a capture trigger. When a specified edge of the capture trigger is detected, the count value of TM00 is stored in CR000.

#### (g) 16-bit capture/compare register 010 (CR010)

This register is used as a capture register. The signal input to the TI000 pin is used as a capture trigger. When the capture trigger is detected, the count value of TM00 is stored in CR010.

#### (8) 8-bit A/D conversion result register L (ADCRL)

The A/D conversion result is loaded from the successive approximation register to this register each time A/D conversion is completed, and the ADCRH register stores the lower 8 bits of the A/D conversion result.

#### (9) 8-bit A/D conversion result register H (ADCRH)

The A/D conversion result is loaded from the successive approximation register to this register each time A/D conversion is completed, and the ADCRH register stores the higher 8 bits of the A/D conversion result.

#### (10) 10-bit A/D conversion result register for TMXn synchronization (ADCRXn = 0, 1)

If A/D conversion is started with the output of 16-bit timer Xn as the trigger, the conversion result is loaded from the successive approximation register and the A/D conversion result is held in the lower 10 bits (the higher 6 bits are fixed to 0) every time an A/D conversion ends.

#### (11) 8-bit A/D conversion result register L for TMXn synchronization (ADCRXnL = 0, 1)

If A/D conversion is started with the output of 16-bit timer Xn as the trigger, the conversion result is loaded from the successive approximation register and the lower 8 bits of the A/D conversion result are held in ADCRXnL register, every time an A/D conversion ends.

# Caution When data is read from ADCR, ADCRL, ADCRH, ADCRX0, ADCRX1, ADCRX0L, and ADCRX1L, a wait cycle is generated. Do not read data from ADCR, ADCRL, ADCRH, ADCRX0, ADCRX1, ADCRX0L, and ADCRX1L when the peripheral hardware clock (fPRS) is stopped. For details, refer to CHAPTER 31 CAUTIONS FOR WAIT.

#### (12) Controller

This circuit controls the conversion time of an input analog signal that is to be converted into a digital signal, as well as starting and stopping of the conversion operation. When all the specified A/D conversion has been completed, this controller generates an A/D conversion end interrupt request signal (INTAD).

#### (13) AVREF pin

This pin inputs an analog power/reference voltage to the A/D converter. Make this pin the same potential as the  $V_{DD}$  pin when ports 2 and 7 are used as a digital port.

The signal input to ANI0 to ANI8 is converted into a digital signal, based on the voltage applied across AVREF and AVss.

#### (14) AVss pin (78K0/IB2 only)

This is the ground potential pin of the A/D converter. Always use this pin at the same potential as that of the Vss pin even when the A/D converter is not used.

#### (15) Vss pin

This is the ground potential pin. In the 78K0/IY2 and 78K0/IA, Vss functions alternately as the ground potential of the A/D converter. Be sure to connect Vss to a stabilized GND (= 0 V).

- Cautions 1. Set a channel to be used for A/D conversion in the input mode by using port mode registers 2 and 7 (PM2, PM7).

- 2. Set ADS after PGA operation setting when selecting the PGA output signal as analog input. Set ADS after single AMP operation setting when selecting the operational amplifier output signal as analog input.

- 3. To select the internal voltage (1.2 V) as an analog input, set the ADCS bit to 1 when at least 10  $\mu$ s have elapsed after having set the V12SEL bit to 1 while the A/D conversion operation was stopped (ADCS = 0).

- 4. If data is written to ADS, a wait cycle is generated. Do not write data to ADS when the peripheral hardware clock (fPRs) is stopped. For details, refer to CHAPTER 31 CAUTIONS FOR WAIT.

### (4) Port mode register 2 (PM2)

When using AMP-/ANI0/P20, AMPOUT/PGAIN/ANI1/P21, and AMP+/ANI2/P22 pins for the operational amplifier, set PM20 to PM22 to 1.

The output latches of P20 to P22 at this time may be 0 or 1.

If PM20 to PM22 are set to 0, they cannot be used as the operational amplifier pins.

PM2 can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation sets PM2 to FFH.

#### Figure 12-5. Format of Port Mode Register 2 (PM2)

#### (1) 78K0/IY2

| Address: FF | 22H After | reset: FFH | R/W  |      |      |      |   |      |

|-------------|-----------|------------|------|------|------|------|---|------|

| Symbol      | 7         | 6          | 5    | 4    | 3    | 2    | 1 | 0    |

| PM2         | 1         | 1          | PM25 | PM24 | PM23 | PM22 | 1 | PM20 |

Caution Be sure to set bits 1, 6, and 7 of PM2 to 1.

#### (2) 78K0/IA2

| Address: FF | 22H After | reset: FFH | R/W  |      |      |      |      |      |

|-------------|-----------|------------|------|------|------|------|------|------|

| Symbol      | 7         | 6          | 5    | 4    | 3    | 2    | 1    | 0    |

| PM2         | 1         | 1          | PM25 | PM24 | PM23 | PM22 | PM21 | PM20 |

Caution Be sure to set bits 6 and 7 of PM2 to 1.

#### (3) 78K0/IB2

Address: FF22H After reset: FFH R/W

| Symbol | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|--------|------|------|------|------|------|------|------|------|

| PM2    | PM27 | PM26 | PM25 | PM24 | PM23 | PM22 | PM21 | PM20 |

| PM2n | P2n pin I/O mode selection (n = 0 to 7) |

|------|-----------------------------------------|

| 0    | Output mode (output buffer on)          |

| 1    | Input mode (output buffer off)          |

# 13.4 Operation of Comparators

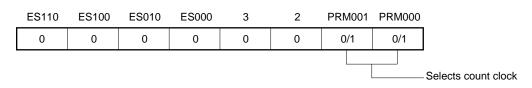

13.4.1 Starting comparator operation (using internal reference voltage for comparator reference voltage)

Figure 13-11. Example of Setting Procedure when Starting Comparator Operation (Using Internal Reference Voltage for Comparator Reference Voltage)

Note Set the CnOE bit to 1 when at least 20  $\mu$  s have elapsed after having set the CVRE register.

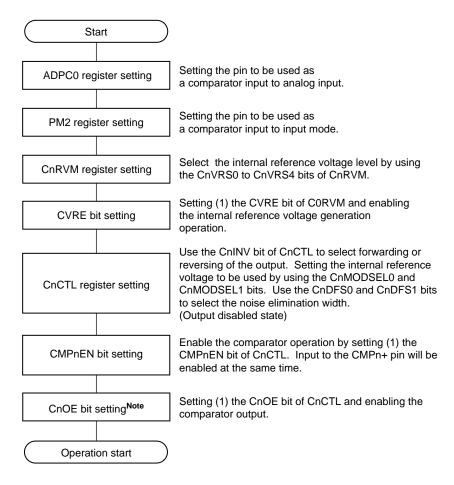

# 14.2 Configuration of Serial Interface UART6/DALI

Serial interface UART6/DALI includes the following hardware.

| Item              | Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Registers         | UART receive buffer register 6 (RXB6)<br>UART/DALI receive shift register 6 (RXS6)<br>DALI receive buffer register (RXBDL)<br>UART/DALI transmit buffer register 6 (TXB6)<br>UART/DALI transmit shift register 6 (TXS6)                                                                                                                                                                                                                                                |

| Control registers | UART/DALI mode control register (UADLCTL)<br>UART/DALI operation mode register 6 (ASIM6)<br>UART/DALI reception error status register 6 (ASIS6)<br>UART transmission status register 6 (ASIF6)<br>Clock selection register 6 (CKSR6)<br>Baud rate generator control register 6 (BRGC6)<br>LIN operation control register 6 (ASICL6)<br>Input switch control register (ISC)<br>Port mode register 6 (PM6)<br>Port register 6 (P6)<br>Port output mode register 6 (POM6) |

| Ļ          |

|------------|

| ₹          |

| 6          |

| T6/I       |

|            |

| 4          |

| 1          |

| _          |

| ខ          |

| ø.         |

| Ľ          |

| Ę          |

| 2          |

| -          |

| ria        |

| P          |

| Ō          |

| ÷          |

| 0          |

| Ε          |

| gran       |

| 5          |

| a          |

| Δ          |

| ×          |

| Ö          |

| <u> </u>   |

| ш          |

|            |

| 4          |

| 4          |

|            |

| e          |

| 5          |

| <u>i</u> g |

| ш          |

|            |

78K0/lx2

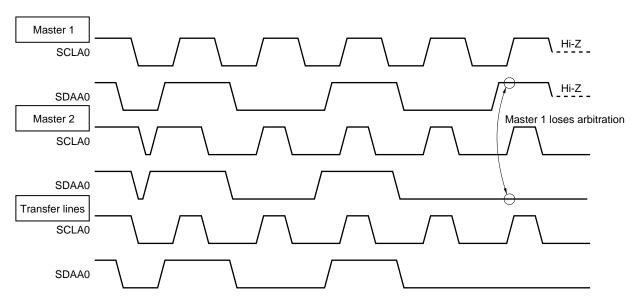

#### 15.5.12 Arbitration

When several master devices simultaneously generate a start condition (when the STT0 bit is set to 1 before the STD0 bit is set to 1), communication among the master devices is performed as the number of clocks are adjusted until the data differs. This kind of operation is called arbitration.

When one of the master devices loses in arbitration, an arbitration loss flag (ALD0) in the IICA status register 0 (IICAS0) is set (1) via the timing by which the arbitration loss occurred, and the SCLA0 and SDAA0 lines are both set to high impedance, which releases the bus.

The arbitration loss is detected based on the timing of the next interrupt request (the eighth or ninth clock, when a stop condition is detected, etc.) and the ALD0 = 1 setting that has been made by software.

For details of interrupt request timing, refer to **15.5.8** Interrupt request (INTIICA0) generation timing and wait control.

Remark STD0: Bit 1 of IICA status register 0 (IICAS0) STT0: Bit 1 of IICA control register 0 (IICACTL0)

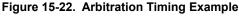

Figure 15-34. Example of Slave to Master Communication (When 8-Clock and 9-Clock Wait Is Selected for Master, 9-Clock Wait Is Selected for Slave) (3/3)

#### (3) Stop condition

Notes 1. To cancel wait, write "FFH" to IICA or set WREL0.

- 2. Write data to IICA, not setting WREL0, in order to cancel a wait state during slave transmission.

- 3. If a wait state during slave transmission is canceled by setting WREL0, TRC0 will be cleared.

#### 18.4.4 Interrupt request hold

There are instructions where, even if an interrupt request is issued for them while another instruction is being executed, request acknowledgment is held pending until the end of execution of the next instruction. These instructions (interrupt request hold instructions) are listed below.

- MOV PSW, #byte

- MOV A, PSW

- MOV PSW, A

- MOV1 PSW. bit, CY

- MOV1 CY, PSW. bit

- AND1 CY, PSW. bit

- OR1 CY, PSW. bit

- XOR1 CY, PSW. bit

- SET1 PSW. bit

- CLR1 PSW. bit

- RETB

- RETI

- PUSH PSW

- POP PSW

- BT PSW. bit, \$addr16

- BF PSW. bit, \$addr16

- BTCLR PSW. bit, \$addr16

- El

- DI

- Manipulation instructions for the IF0L, IF0H, IF1L, IF1H, MK0L, MK0H, MK1L, MK1H, PR0L, PR0H, PR1L, and PR1H registers.

- Caution The BRK instruction is not one of the above-listed interrupt request hold instructions. However, the software interrupt activated by executing the BRK instruction causes the IE flag to be cleared. Therefore, even if a maskable interrupt request is generated during execution of the BRK instruction, the interrupt request is not acknowledged.

Figure 18-18 shows the timing at which interrupt requests are held pending.

### Figure 18-18. Interrupt Request Hold

| CPU processing | Instruction N | Instruction M | PSW and PC saved, jump to interrupt servicing | Interrupt servicing program |

|----------------|---------------|---------------|-----------------------------------------------|-----------------------------|

| ××IF           |               |               |                                               |                             |

Remarks 1. Instruction N: Interrupt request hold instruction

- 2. Instruction M: Instruction other than interrupt request hold instruction

- 3. The xxPR (priority level) values do not affect the operation of xxIF (interrupt request).

| Item                               |                              |        | During Reset Period                                                                                                    |  |  |  |  |

|------------------------------------|------------------------------|--------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| System clock                       |                              |        | Clock supply to the CPU is stopped.                                                                                    |  |  |  |  |

| Main system clock fin              |                              |        | Operation stopped                                                                                                      |  |  |  |  |

|                                    |                              | fx     | Operation stopped (X1 and X2 pins are input port mode)                                                                 |  |  |  |  |

|                                    |                              | fexclk | Clock input invalid (EXCLK pin is input port mode)                                                                     |  |  |  |  |

| fı∟                                |                              |        | Operation stopped                                                                                                      |  |  |  |  |

| CPU                                |                              |        |                                                                                                                        |  |  |  |  |

| Flash memory                       |                              |        |                                                                                                                        |  |  |  |  |

| RAM                                |                              |        | Operation stopped (The value, however, is retained when the voltage is at least the power-on clear detection voltage.) |  |  |  |  |

| Port (latch)                       |                              |        | Operation stopped                                                                                                      |  |  |  |  |

| 16-bit timer                       |                              | X0     |                                                                                                                        |  |  |  |  |

|                                    | ĺ                            | X1     |                                                                                                                        |  |  |  |  |

| 16-bit timer/event c               | ounte                        | er 00  |                                                                                                                        |  |  |  |  |

| 8-bit timer/event co               | 8-bit timer/event counter 51 |        |                                                                                                                        |  |  |  |  |

| 8-bit timer H1                     |                              |        |                                                                                                                        |  |  |  |  |

| Watchdog timer                     |                              |        |                                                                                                                        |  |  |  |  |

| A/D converter                      |                              |        |                                                                                                                        |  |  |  |  |

| Operational amplific<br>(AMP, PGA) | er                           |        |                                                                                                                        |  |  |  |  |

| Comparators 0 to 2                 | 2                            |        |                                                                                                                        |  |  |  |  |

| Serial interface                   | JART                         | 5/DALI |                                                                                                                        |  |  |  |  |

| С                                  | CSI11                        |        |                                                                                                                        |  |  |  |  |

| IICA                               |                              |        |                                                                                                                        |  |  |  |  |

| Multiplier                         |                              |        |                                                                                                                        |  |  |  |  |

| External interrupt                 |                              |        |                                                                                                                        |  |  |  |  |

| Power-on-clear function            |                              |        | Operable                                                                                                               |  |  |  |  |

| Low-voltage detection function     |                              | nction | Operation stopped (however, operation continues at LVI reset)                                                          |  |  |  |  |

| On-chip debug function             |                              |        | Operation stopped                                                                                                      |  |  |  |  |

Remarks 1. fin: Internal I

fexclk: External main system clock,

Internal high-speed oscillation clock, fx: X1 clock

fi∟: Internal low-speed oscillation clock

2. The functions mounted depend on the product. Refer to 1.4 Block Diagram and 1.5 Outline of Functions.

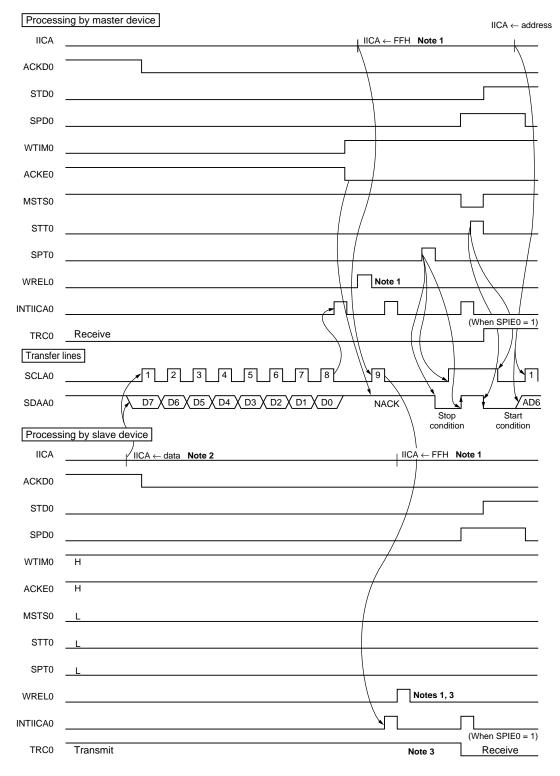

# (2) When LVI default start function enabled is set (LVISTART = 1)

The setting when operation starts and when operation stops is the same as described in **22.4.2 (1)** When LVI default start function stopped is set (LVISTART = 0).

Figure 22-7. Timing of Low-Voltage Detector Interrupt Signal Generation (LVISTART = 1)

**Notes 1.** The LVIMK flag is set to "1" by reset signal generation.

- 2. The interrupt request signal (INTLVI) is generated and the LVIF and LVIIF flags may be set (1).

- 3. If LVI operation is disabled (clears LVION) when the supply voltage (V<sub>DD</sub>) is less than or equal to the detection voltage (V<sub>LVI</sub>), an interrupt request signal (INTLVI) is generated and LVIIF may be set to 1.

- **Remarks 1.** <1> to <8> in Figure 22-7 above correspond to <1> to <8> in the description of "When starting operation" in **22.4.2 (1) When LVI default start function stopped is set (LVISTART = 0).**

- 2. VPOR: POC power supply rise detection voltage VPDR: POC power supply fall detection voltage

# Table 25-9. Processing Time for Each Command When PG-FP5 Is Used (Reference) (2/2)

(3) Products with internal ROMs of the 16 KB:  $\mu$ PD78F0742, 78F0744, 78F0746, 78F0752, 78F0754, 78F0756

| Command of PG-FP5 | Port: UART-Internal-OSC (Internal high-speed oscillation clock (fii: 8 MHz (typ.)),<br>Speed: 500,000 bps |  |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------|--|--|--|--|

|                   |                                                                                                           |  |  |  |  |

| Signature         | 0.5 s (typ.)                                                                                              |  |  |  |  |

| Blankcheck        | 0.5 s (typ.)                                                                                              |  |  |  |  |

| Erase             | 1 s (typ.)                                                                                                |  |  |  |  |

| Program           | 2.5 s (typ.)                                                                                              |  |  |  |  |

| Verify            | 1.5 s (typ.)                                                                                              |  |  |  |  |

| E.P.V             | 2.5 s (typ.)                                                                                              |  |  |  |  |

| Checksum          | 1 s (typ.)                                                                                                |  |  |  |  |

| Security          | 0.5 s (typ.)                                                                                              |  |  |  |  |

Caution When executing boot swapping, do not use the E.P.V. command with the dedicated flash memory programmer.

# Caution The pins mounted depend on the product. Refer to Caution 2 at the beginning of this chapter.

| Parameter                     | Symbol | (                           | Conditions                          | Ratings     | Unit |

|-------------------------------|--------|-----------------------------|-------------------------------------|-------------|------|

| Output current, high          | Іон1   | Per pin                     | P00 to P02, P30 to P37,<br>P60, P61 | -10         | mA   |

|                               |        | Total of all pins<br>–40 mA | P00 to P02                          | –15         | mA   |

|                               |        |                             | P30 to P37, P60, P61                | -25         | mA   |

|                               | Іон2   | Per pin                     | P20 to P27, P70                     | -0.5        | mA   |

|                               |        | Total of all pins           |                                     | -2          | mA   |

| Output current, low           | IOL1   | Per pin                     | P00 to P02, P30 to P37,<br>P60, P61 | 30          | mA   |

|                               |        | Total of all pins<br>120 mA | P00 to P02                          | 45          | mA   |

|                               |        |                             | P30 to P37, P60, P61                | 75          | mA   |

|                               | IOL2   | Per pin                     | P20 to P27, P70                     | 1           | mA   |

|                               |        | Total of all pins           |                                     | 5           | mA   |

| Operating ambient temperature | TA     |                             |                                     | -40 to +105 | °C   |

| Storage temperature           | Tstg   |                             |                                     | –65 to +150 | °C   |

#### Absolute Maximum Ratings (T<sub>A</sub> = 25°C) (2/2)

- Cautions 1. Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

- 2. The value of the current that can be run per pin must satisfy the value of the current per pin and the total value of the currents of all pins.

**Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of port pins.

# Caution The pins mounted depend on the product. Refer to Caution 2 at the beginning of this chapter.

| Parameter            | Symbol           | Conditions                                          |                                                                                                              | MIN.                  | TYP.   | MAX.                 | Unit |

|----------------------|------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------|--------|----------------------|------|

| Input voltage, high  | VIH1             | P37, P121, P122, P125                               |                                                                                                              | 0.7Vdd                |        | VDD                  | V    |

|                      | VIH2             | P20 to P27, P70 AV <sub>REF</sub> = V <sub>DD</sub> |                                                                                                              | 0.7AV <sub>REF</sub>  |        | AVREF                | V    |

|                      | VIH3             | P60, P61 (I/O port mode)                            |                                                                                                              | 0.7Vdd                |        | VDD                  | V    |

|                      | VIH4             | P00 to P02, P30 to P36, R                           | 0.8VDD                                                                                                       |                       | VDD    | V                    |      |

|                      | VIH5             | P60, P61                                            | $3.4~V \le V_{\text{DD}} \le 5.5~V$                                                                          | 0.8VDD                |        |                      | V    |

|                      |                  | (SMBus input mode)                                  | $2.7~V \leq V_{\text{DD}} < 3.4~V$                                                                           | 2.1                   |        |                      | V    |

|                      | VIH6             | X1, X2                                              | Vdd - 0.1                                                                                                    |                       | VDD    | V                    |      |

| Input voltage, low   | VIL1             | P37, P121, P122, P125                               |                                                                                                              | 0                     |        | 0.3Vdd               | V    |

|                      | VIL2             | P20 to P27, P70                                     | AV <sub>REF</sub> = V <sub>DD</sub>                                                                          | 0                     |        | 0.3AV <sub>REF</sub> | V    |

|                      | VIL3             | P60, P61 (I/O port mode)                            | 0                                                                                                            |                       | 0.3VDD | V                    |      |

|                      | VIL4             | P00 to P02, P30 to P36, RESET, EXCLK                |                                                                                                              | 0                     |        | 0.2VDD               | V    |

|                      | VIL5             | P60, P61                                            | $3.4~V \le V_{\text{DD}} \le 5.5~V$                                                                          | 0                     |        | 0.2VDD               | V    |

|                      |                  | (SMBus input mode)                                  | $2.7~V \leq V_{\text{DD}} < 3.4~V$                                                                           | 0                     |        | 0.8                  | V    |

|                      | VIL6             | X1, X2                                              |                                                                                                              | 0                     |        | 0.1                  | V    |

| Output voltage, high | VOH1             | P00 to P02, P30 to P37,<br>P60, P61                 | $\begin{array}{l} 4.0 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \\ I_{\text{OH1}} = -3.0 \ \text{mA} \end{array}$ | $V_{\text{DD}}-0.7$   |        |                      | V    |

|                      |                  |                                                     | $2.7 \text{ V} \le \text{V}_{\text{DD}} < 4.0 \text{ V},$<br>I_OH1 = -2.5 mA                                 | V <sub>DD</sub> - 0.5 |        |                      | V    |

|                      | V <sub>OH2</sub> | P20 to P27, P70                                     | AV <sub>REF</sub> = V <sub>DD</sub> ,<br>I <sub>OH2</sub> = -100 μA                                          | Vdd - 0.5             |        |                      | V    |

# (TA = -40 to +105°C, 2.7 V $\leq$ VDD $\leq$ 5.5 V, AVREF $\leq$ VDD, Vss = AVss = 0 V)

**Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of port pins.

Caution For P122/EXCLK, the value of V<sub>IH</sub> and V<sub>IL</sub> differs according to the input port mode or external clock mode.

Make sure to satisfy the DC characteristics of EXCLK in external clock input mode.

# 28.6 Flash Memory Programming Characteristics

# $(T_{\text{A}} = -40 \text{ to } +105^{\circ}\text{C}, \text{ 2.7 V} \leq V_{\text{DD}} \leq 5.5 \text{ V}, \text{ AV}_{\text{REF}} \leq V_{\text{DD}}, \text{ V}_{\text{SS}} = \text{AV}_{\text{SS}} = 0 \text{ V})$

#### Basic characteristics

| Parameter                      | Symbol | Conditions                                              |                                                               |                                                                                                                                                                                                      |                        | MIN.                       | TYP.                      | MAX.      | Unit    |

|--------------------------------|--------|---------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------------|---------------------------|-----------|---------|

| VDD supply current             | Idd    |                                                         |                                                               |                                                                                                                                                                                                      |                        |                            | 4.5                       | 14        | mA      |

| Number of<br>rewrites per chip | Cerwr  | 1 erase +<br>1 write after<br>erase =<br>1 rewrite<br>1 | In<br>normal<br>power<br>mode<br>(RMC =<br>00H)               | When a flash<br>memory<br>programmer is<br>used, and the self-<br>programming<br>libraries provided<br>by Renesas<br>Electronics are<br>used                                                         | Retention:<br>15 years | 1000                       |                           |           | Times   |

|                                |        |                                                         |                                                               | When the<br>EEPROM<br>emulation libraries<br>(the rewritable<br>ROM size is 4 KB)<br>provided by<br>Renesas<br>Electronics are<br>used                                                               | Retention:<br>5 years  | 10000                      |                           |           | Times   |

|                                |        |                                                         | In low<br>power<br>consump<br>-tion<br>mode<br>(RMC =<br>56H) | When the self-<br>programming<br>libraries <sup>Note 2</sup> , and<br>the EEPROM<br>emulation libraries<br>(the rewritable ROM<br>size is 4 KB)<br>provided by<br>Renesas<br>Electronics are<br>used | Retention:<br>5 years  | 1000                       |                           |           | Times   |

| Operating<br>temperature       |        | When a flash                                            | memory pro                                                    | ogrammer is used: 10                                                                                                                                                                                 | to 40 °C, duri         | ng self-pro                | ogrammin                  | g: –40 to | +105 °C |

| Operating voltage range        |        | In normal power mode<br>(RMC = 00H)                     |                                                               | When a flash memory     2.7       programmer is used                                                                                                                                                 |                        | 2.7 to 5.                  | 2.7 to 5.5 V@8 MHz (MAX.) |           |         |

|                                |        |                                                         |                                                               | During self-programming                                                                                                                                                                              |                        | 2.7 to 5.5 V@20 MHz (MAX.) |                           |           |         |

|                                |        | In low power<br>consumption r<br>(RMC = 56H)            | node                                                          | During self-program                                                                                                                                                                                  | ming                   | 2.7 to 5.                  | 5 V@5 M                   | Hz (MAX.  | )       |

**Notes 1.** When a product is first written after shipment, "erase  $\rightarrow$  write" and "write only" are both taken as one rewrite.

2. Only the data area can be rewritten.

# APPENDIX C REVISION HISTORY

# C.1 Major Revisions in This Edition

| Page          | Description                                                                                                         | Classification |

|---------------|---------------------------------------------------------------------------------------------------------------------|----------------|

| Throughout    |                                                                                                                     |                |

| -             | Update of URL                                                                                                       | -              |

| CHAPTER 6 10  | 6-BIT TIMERS X0 AND X1                                                                                              |                |

| p. 207-215    | Addition of 6.4 Operation of 16-Bit Timer/Event Counter 00                                                          | (c)            |

| p. 216, 218,  | • Duty = (Set value of TXnCR1 <sup>Note1</sup> – Set value of TXnCR0 <sup>Note1</sup> ) / (Set value of TXnCR1 + 1) | (c)            |

| 219, 224, 225 | Addition of Note1                                                                                                   |                |

| p. 218, 220,  | Modification of Figure 6-28, 6-30, 6-32, 6-34 PWM Output Timing                                                     | (c)            |

| 223, 227      |                                                                                                                     |                |

| CHAPTER 11 A  | VD CONVERTER                                                                                                        |                |

| p. 397        | Modification of description in (6) Input impedance of ANI0 to ANI8 pins                                             | (a)            |

| CHAPTER 28 E  | LECTRICAL SPECIFICATIONS                                                                                            | •              |

| p. 710        | Modification of Remarks                                                                                             | (a)            |

(a): Error correction, (b): Addition/change of specifications, (c): Addition/change of description or note,

(d): Addition/change of package, part number, or management division, (e): Addition/change of related documents