# E. Renesas Electronics America Inc - UPD78F0756MC-CAB-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                               |

|----------------------------|--------------------------------------------------------------------------------------|

| Core Processor             | 78K/0                                                                                |

| Core Size                  | 8-Bit                                                                                |

| Speed                      | 10MHz                                                                                |

| Connectivity               | 3-Wire SIO, DALI, I²C, LINbus, UART/USART                                            |

| Peripherals                | LVD, POR, PWM, WDT                                                                   |

| Number of I/O              | 22                                                                                   |

| Program Memory Size        | 16KB (16K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | <u>.</u>                                                                             |

| RAM Size                   | 768 x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                          |

| Data Converters            | A/D 9x10b                                                                            |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 30-LSSOP (0.240", 6.10mm Width)                                                      |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0756mc-cab-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Function Name | I/O   | Function                                                                                                                                                                                                                                                                                                             | After Reset  | Alternate Function                                     |

|---------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------------------------------------------|

| P00           | I/O   | Port 0.<br>3-bit I/O port.                                                                                                                                                                                                                                                                                           | Input port   | TI000/INTP0/ <toh1>/<br/><ti51></ti51></toh1>          |

| P02           |       | Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by a<br>software setting.                                                                                                                                                                                       |              | SSI11/INTP5                                            |

| P20           | I/O   | Port 2.                                                                                                                                                                                                                                                                                                              | Analog input | ANI0/AMP- <sup>Note</sup>                              |

| P21           |       | 8-bit I/O port.<br>Input/output can be specified in 1-bit units.                                                                                                                                                                                                                                                     |              | ANI1/AMPOUT <sup>Note</sup> /<br>PGAIN <sup>Note</sup> |

| P22           |       |                                                                                                                                                                                                                                                                                                                      |              | ANI2/AMP+ <sup>Note</sup>                              |

| P23           |       |                                                                                                                                                                                                                                                                                                                      |              | ANI3/CMP2+                                             |

| P24           |       |                                                                                                                                                                                                                                                                                                                      |              | ANI4/CMP0+                                             |

| P25           |       |                                                                                                                                                                                                                                                                                                                      |              | ANI5/CMP1+                                             |

| P26           |       |                                                                                                                                                                                                                                                                                                                      |              | ANI6/CMPCOM                                            |

| P27           |       |                                                                                                                                                                                                                                                                                                                      |              | ANI7                                                   |

| P31           | I/O   | Port 3.                                                                                                                                                                                                                                                                                                              | Input port   | TOX00/INTP2/TOOLC1                                     |

| P32           |       | 8-bit I/O port.<br>Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by a<br>software setting.                                                                                                                                                                    |              | TOX01/INTP3/TOOLD1                                     |

| P33           |       |                                                                                                                                                                                                                                                                                                                      |              | TOX10                                                  |

| P34           |       |                                                                                                                                                                                                                                                                                                                      |              | TOX11/INTP4/ <toh1>/<br/><ti51></ti51></toh1>          |

| P35           |       |                                                                                                                                                                                                                                                                                                                      |              | SCK11                                                  |

| P36           |       |                                                                                                                                                                                                                                                                                                                      |              | SI11                                                   |

| P37           |       |                                                                                                                                                                                                                                                                                                                      |              | SO11                                                   |

| P60           | I/O   | Port 6.                                                                                                                                                                                                                                                                                                              | Input port   | SCLA0/TxD6                                             |

| P61           |       | <ul> <li>2-bit I/O port.</li> <li>Input/output can be specified in 1-bit units.</li> <li>Input can be set to SMBus input buffer in 1-bit units.</li> <li>Output can be set to N-ch open-drain output (VDD tolerance).</li> <li>Use of an on-chip pull-up resistor can be specified by a software setting.</li> </ul> |              | SDAA0/RxD6                                             |

| P70           | I/O   | Port 7.<br>1-bit I/O port.<br>Input/output can be specified in 1-bit units.                                                                                                                                                                                                                                          | Analog input | ANI8                                                   |

| P121          | Input | Port 12.<br>3-bit input port.                                                                                                                                                                                                                                                                                        | Input port   | X1/TOOLC0/ <ti000>/<br/><intp0></intp0></ti000>        |

| P122          |       | For only P125, use of an on-chip pull-up resistor can be                                                                                                                                                                                                                                                             |              | X2/EXCLK/TOOLD0                                        |

| P125          |       | specified by a software setting.                                                                                                                                                                                                                                                                                     |              | RESET                                                  |

Note µPD78F0755, 78F0756 (products with operational amplifier) only

**Remark** Functions in angle brackets < > can be assigned by setting the input switch control register (MUXSEL).

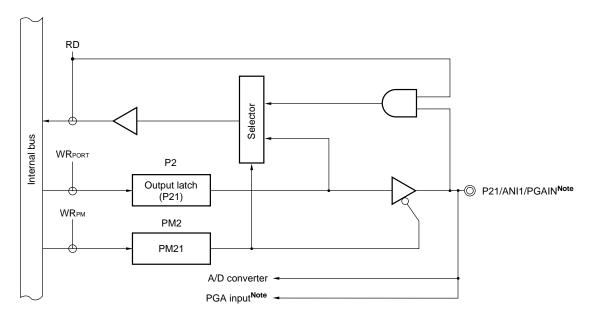

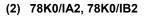

Figure 4-5. Block Diagram of P21

# (1) 78K0/IY2

P2:Port register 2PM2:Port mode register 2AMP0M:Operational amplifier 0 control registerRD:Read signalWR××:Write signal

Note Products with operational amplifier only

Remark PGA: Programmable Gain Amplifier

| Pin Name | Alternate Function                                                                                                                                                                                                                  | PM××   | P×× |   |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|---|

|          | Function Name                                                                                                                                                                                                                       | I/O    |     |   |

| P00      | TI000                                                                                                                                                                                                                               | Input  | 1   | × |

|          | INTP0                                                                                                                                                                                                                               | Input  | 1   | × |

| P01      | TI010                                                                                                                                                                                                                               | Input  | 1   | × |

|          | ТО00                                                                                                                                                                                                                                | Output | 0   | 0 |

| P02      | SSI11                                                                                                                                                                                                                               | Input  | 1   | × |

|          | SSI11       INTP5       ANI0 <sup>Note 1</sup> AMP-Notes 1, 2       ANI1 <sup>Note 3</sup> AMPOUT <sup>Notes 2, 3</sup> PGAIN <sup>Notes 2, 3</sup> ANI2 <sup>Note 1</sup> AMP+Notes 1, 2       AMP+Notes 1, 2       AMP+Notes 1, 2 | Input  | 1   | × |

| P20      | ANI0 <sup>Note 1</sup>                                                                                                                                                                                                              | Input  | 1   | × |

|          | AMP- <sup>Notes 1, 2</sup><br>1 ANI1 <sup>Note 3</sup>                                                                                                                                                                              | Input  | 1   | × |

| P21      | ANI1 <sup>Note 3</sup>                                                                                                                                                                                                              | Input  | 1   | × |

|          | AMPOUT <sup>Notes 2, 3</sup>                                                                                                                                                                                                        | Output | 1   | × |

|          | PGAIN <sup>Notes 2, 3</sup>                                                                                                                                                                                                         | Input  | 1   | × |

| P22      | ANI2 <sup>Note 1</sup>                                                                                                                                                                                                              | Input  | 1   | × |

|          | PGAIN <sup>Notes 2, 3</sup> ANI2 <sup>Note 1</sup> AMP+ <sup>Notes 1, 2</sup>                                                                                                                                                       | Input  | 1   | × |

| P23      | ANI3 Note 4                                                                                                                                                                                                                         | Input  | 1   | × |

|          | CMP2+ <sup>Note 4</sup>                                                                                                                                                                                                             | Input  | 1   | × |

| P24      | ANI4 <sup>Note 4</sup>                                                                                                                                                                                                              | Input  | 1   | × |

|          | CMP0+ <sup>Note 4</sup>                                                                                                                                                                                                             | Input  | 1   | × |

| P25      | ANI5 <sup>Note 4</sup>                                                                                                                                                                                                              | Input  | 1   | × |

|          | CMP1+ <sup>Note 4</sup>                                                                                                                                                                                                             | Input  | 1   | × |

| P26      | ANI6 <sup>Note 5</sup>                                                                                                                                                                                                              | Input  | 1   | × |

|          | CMPCOM <sup>Note 5</sup>                                                                                                                                                                                                            | Input  | 1   | × |

| P27      | ANI7 <sup>Note 6</sup>                                                                                                                                                                                                              | Input  | 1   | × |

| P30      | INTP1                                                                                                                                                                                                                               | Input  | 1   | × |

|          | TI51                                                                                                                                                                                                                                | Input  | 1   | × |

|          | TOH1                                                                                                                                                                                                                                | Output | 0   | 0 |

| Table 4-15. Settings of Port Mode Register and Output Latch When Using Alternate Function (78K0/IB2 (30 pin | s)) (1/2) |

|-------------------------------------------------------------------------------------------------------------|-----------|

|                                                                                                             | -,, ( = , |

**Notes 1.** The pin function can be selected by using ADPC0 register, PM2 register, ADS register, and OPAMP0E bit. Refer to **Table 4-7** in **4.2.2 Port 2**.

- 2. μPD 78F0755, 78F0756 (products with operational amplifier) only

- **3.** The pin function can be selected by using ADPC0 register, PM2 register, ADS register, OPAMP0E bit, and PGAEN bit. Refer to **Table 4-8** in **4.2.2 Port 2**.

- The pin function can be selected by using ADPC0 register, PM2 register, ADS register, and CMPmEN (m = 0-2) bit. Refer to Table 4-9 in 4.2.2 Port 2.

- The pin function can be selected by using ADPC0 register, PM2 register, ADS register, and CmMODSEL1, CmMODSEL0 (m = 0-2) bit. Refer to Table 4-10 in 4.2.2 Port 2.

- The pin function can be selected by using ADPC0 register, PM2 register, and ADS register. Refer to Table

4-11 in 4.2.2 Port 2.

- Remark ×: Don't care

- PM××: Port mode register

- Pxx: Port output latch

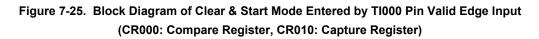

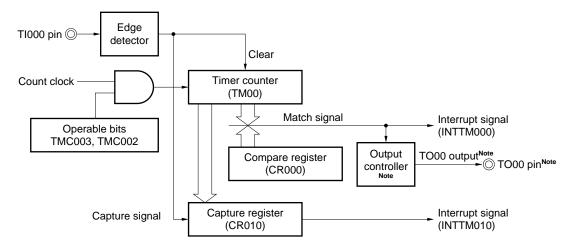

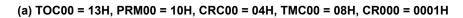

# (2) Operation in clear & start mode entered by TI000 pin valid edge input (CR000: compare register, CR010: capture register)

Note 78K0/IB2 (30 pins) only

# Figure 7-26. Timing Example of Clear & Start Mode Entered by TI000 Pin Valid Edge Input (CR000: Compare Register, CR010: Capture Register) (1/2)

This is an application example where the TO00 output level is inverted when the count value has been captured & cleared.

The count value is captured to CR010 and TM00 is cleared (to 0000H) when the valid edge of the TI000 pin is detected. When the count value of TM00 is 0001H, a compare match interrupt signal (INTTM000) is generated, and the TO00 output level is inverted.

#### Figure 9-4. Format of 8-Bit Timer H Mode Register 1 (TMHMD1)

Address: FF6CH After reset: 00H R/W

TMHMD1

| _ | <7>   | 6     | 5     | 4     | 3      | 2      | <1>    | <0>   |

|---|-------|-------|-------|-------|--------|--------|--------|-------|

|   | TMHE1 | CKS12 | CKS11 | CKS10 | TMMD11 | TMMD10 | TOLEV1 | TOEN1 |

| TMHE1 | Timer operation enable                                                     |

|-------|----------------------------------------------------------------------------|

| 0     | Stops timer count operation (counter is cleared to 0)                      |

| 1     | Enables timer count operation (count operation started by inputting clock) |

| CKS12 | CKS11 | CKS10 |                                    | Co                          | ount clock s                | election                     |                                                  |

|-------|-------|-------|------------------------------------|-----------------------------|-----------------------------|------------------------------|--------------------------------------------------|

|       |       |       |                                    | f <sub>PRS</sub> =<br>2 MHz | f <sub>PRS</sub> =<br>5 MHz | f <sub>PRS</sub> =<br>10 MHz | f <sub>PRS</sub> = 20<br>MHz (when<br>using PLL) |

| 0     | 0     | 0     | fprs                               | 2 MHz                       | 5 MHz                       | 10 MHz                       | 20 MHz                                           |

| 0     | 0     | 1     | fprs/2 <sup>2</sup>                | 500 kHz                     | 1.25 MHz                    | 2.5 MHz                      | 5 MHz                                            |

| 0     | 1     | 0     | fprs/24                            | 125 kHz                     | 312.5 kHz                   | 625 kHz                      | 1.25 MHz                                         |

| 0     | 1     | 1     | fprs/2 <sup>6</sup>                | 31.25 kHz                   | 78.13 kHz                   | 156.25 kHz                   | 312.5 kHz                                        |

| 1     | 0     | 0     | fprs/212                           | 0.49 kHz                    | 1.22 kHz                    | 2.44 kHz                     | 4.88 kHz                                         |

| 1     | 0     | 1     | fiu/2 <sup>6</sup> 0.47 kHz (TYP.) |                             |                             |                              |                                                  |

| 1     | 1     | 0     | fil/2 <sup>15</sup> 0.92 Hz (TYP.) |                             |                             |                              |                                                  |

| 1     | 1     | 1     | fı∟                                | 30 kHz (T                   | YP.)                        |                              |                                                  |

| TMMD11 | TMMD10 | Timer operation mode   |  |  |  |

|--------|--------|------------------------|--|--|--|

| 0      | 0      | terval timer mode      |  |  |  |

| 0      | 1      | Carrier generator mode |  |  |  |

| 1      | 0      | PWM output mode        |  |  |  |

| 1      | 1      | Setting prohibited     |  |  |  |

| TOLEV1 | Timer output level control (in default mode) |

|--------|----------------------------------------------|

| 0      | Low level                                    |

| 1      | High level                                   |

| TOEN1 | Timer output control |

|-------|----------------------|

| 0     | Disables output      |

| 1     | Enables output       |

- Cautions 1. When TMHE1 = 1, setting the other bits of TMHMD1 is prohibited. However, TMHMD1 can be refreshed (the same value is written).

- In the PWM output mode and carrier generator mode, be sure to set the 8-bit timer H compare register 11 (CMP11) when starting the timer count operation (TMHE1 = 1) after the timer count operation was stopped (TMHE1 = 0) (be sure to set again even if setting the same value to CMP11).

- 3. When the carrier generator mode is used, set so that the count clock frequency of TMH1 becomes more than 6 times the count clock frequency of TM51.

When using P20/AMP-/ANI0 to P27/ANI7, and P70/ANI8, set the registers according to the pin function to be used (refer to **Tables 11-3** to **11-8**).

| ADPC0<br>Register | PM2 Register | OPAMP0E<br>bit <sup>Note</sup> | ADS Register<br>(n = 0, 2) | P20/ANI0/AMP-,<br>P22/ANI2/AMP+ Pins                                                |

|-------------------|--------------|--------------------------------|----------------------------|-------------------------------------------------------------------------------------|

| Digital I/O       | Input mode   | _                              | Selects ANIn.              | Setting prohibited                                                                  |

| selection         |              |                                | Does not select ANIn.      | Digital input                                                                       |

|                   | Output mode  | _                              | Selects ANIn.              | Setting prohibited                                                                  |

|                   |              |                                | Does not select ANIn.      | Digital output                                                                      |

| Analog input      | Input mode   | 0                              | Selects ANIn.              | Analog input (to be converted into digital signal)                                  |

| selection         |              |                                | Does not select ANIn.      | Analog input (not to be converted into digital signal)                              |

|                   |              |                                | Selects ANIn.              | Analog input (to be converted into digital signal), and operational amplifier input |

|                   |              |                                | Does not select ANIn.      | Operational amplifier input                                                         |

|                   | Output mode  | -                              | _                          | Setting prohibited                                                                  |

## Note 78K0/IA2, 78K0/IB2 only

| Remark | ADPC0:   | A/D port configuration register 0                         |

|--------|----------|-----------------------------------------------------------|

|        | PM2:     | Port mode register 2                                      |

|        | OPAMP0E: | Bit 7 of operational amplifier 0 control register (AMP0M) |

|        | ADS:     | Analog input channel specification register               |

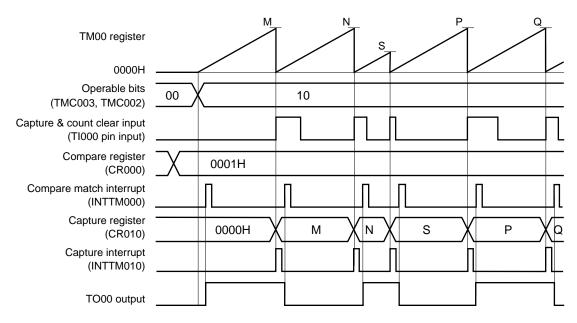

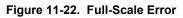

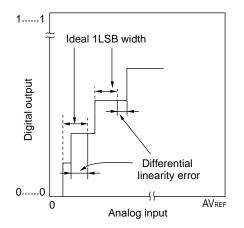

## (5) Full-scale error

This shows the difference between the actual measurement value of the analog input voltage and the theoretical value (Full-scale -3/2LSB) when the digital output changes from 1.....110 to 1.....111.

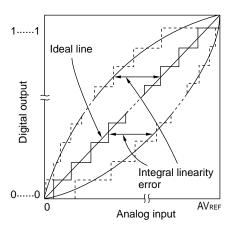

## (6) Integral linearity error

This shows the degree to which the conversion characteristics deviate from the ideal linear relationship. It expresses the maximum value of the difference between the actual measurement value and the ideal straight line when the zero-scale error and full-scale error are 0.

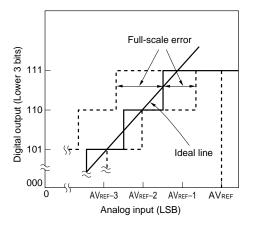

### (7) Differential linearity error

While the ideal width of code output is 1LSB, this indicates the difference between the actual measurement value and the ideal value.

Figure 11-23. Integral Linearity Error

Figure 11-24. Differential Linearity Error

#### (8) Conversion time

This expresses the time from the start of sampling to when the digital output is obtained. The sampling time is included in the conversion time in the characteristics table.

#### (9) Sampling time

This is the time the analog switch is turned on for the analog voltage to be sampled by the sample & hold circuit.

# CHAPTER 12 OPERATIONAL AMPLIFIER

| Item                                                             | 78K0/IY2                | 78K0/IA2             | 78K0             | /IB2    |

|------------------------------------------------------------------|-------------------------|----------------------|------------------|---------|

|                                                                  | 16 Pins                 | 20 Pins              | 30 Pins          | 32 Pins |

| Operational amplifier (products with operational amplifier only) | 1 ch (PGA mode<br>only) | 1 ch (Single AMP mod | le and PGA mode) |         |

# 12.1 Function of Operational Amplifier

Operational amplifier is mounted onto products with operational amplifier of the 78K0/lx2 microcontrollers. The operational amplifier has the following modes.

# Single AMP mode<sup>Note </sup>

Operational amplifier has two input pins (the AMP- pin and the AMP+ pin) and one output pin (the AMPOUT pin), and can be used as single-power supply amplifier that can be externally connected.

The amplified voltage can be used as an analog input of the A/D converter, because the AMPOUT pin is alternatively used with analog input pin of the A/D converter.

Note Products with operational amplifier of the 78K0/IA2, 78K0/IB2 only.

#### • PGA (Programmable gain amplifier) mode

In this mode, the analog voltage input from the PGAIN pin is amplified within the microcontroller. The gain can be selected from four types ( $\times$ 4,  $\times$ 8,  $\times$ 16,  $\times$ 32).

The amplified voltage can be used as an analog input of the A/D converter.

The relationship between the register settings and pins is shown below.

| POWER | TXE6 | RXE6 | PM60  | P60               | PM61              | P61               | POM60 | POM61 | UART6                      | Pin Fu                 | inction                |

|-------|------|------|-------|-------------------|-------------------|-------------------|-------|-------|----------------------------|------------------------|------------------------|

| 6     |      |      |       |                   |                   |                   |       |       | Operation                  | TxD6/<br>SCLA0/<br>P60 | RxD6/<br>SDAA0/<br>P61 |

| 0     | 0    | 0    | ×Note | × <sup>Note</sup> | × <sup>Note</sup> | × <sup>Note</sup> | ×Note | ×Note | Stop                       | P60                    | P61                    |

|       |      |      | 0     | 1                 | 0                 | 1                 | 1     | 1     |                            | SCLA0                  | SDAA0                  |

| 1     | 0    | 1    | ×Note | ×Note             | 1                 | ×                 | ×Note | ×     | Reception                  | P60                    | RxD6                   |

|       | 1    | 0    | 0     | 1                 | ×Note             | ×Note             | 0     | ×Note | Transmission               | TxD6                   | P61                    |

|       | 1    | 1    | 0     | 1                 | 1                 | ×                 | 0     | ×     | Transmission/<br>reception | TxD6                   | RxD6                   |

Table 14-2.

Relationship Between Register Settings and Pins

**Note** Can be set as port function.

| Remark | ×:            | don't care                                           |

|--------|---------------|------------------------------------------------------|

|        | POWER6:       | Bit 7 of UART/DALI operation mode register 6 (ASIM6) |

|        | TXE6:         | Bit 6 of ASIM6                                       |

|        | RXE6:         | Bit 5 of ASIM6                                       |

|        | PM6×:         | Port mode register                                   |

|        | P6×:          | Port output latch                                    |

|        | POM60, POM61: | Bits 0 and 1 of Port output mode register 6 (POM6)   |

Example: Frequency of base clock = 10 MHz = 10,000,000 Hz Set value of MDL67 to MDL60 bits of BRGC6 register = 00100001B (k = 33) Target baud rate = 153600 bps

> Baud rate (UART) =  $10 \text{ M} / (2 \times 33)$ = 10000000 / (2 × 33) = 151,515 [bps]

Error = (151515/153600 - 1) × 100 = -1.357 [%]

## (3) Example of setting baud rate

| Baud<br>Rate | f      | PRS = | = 2.0 MHz  |       | f      | PRS = | 5.0 MHz    |       | f <sub>PRS</sub> = 10.0 MHz |    |            |       | f <sub>PRS</sub> = 20.0 MHz<br>(when using PLL) |    |            |       |

|--------------|--------|-------|------------|-------|--------|-------|------------|-------|-----------------------------|----|------------|-------|-------------------------------------------------|----|------------|-------|

| [bps]        | TPS63- | k     | Calculated | ERR   | TPS63- | k     | Calculated | ERR   | TPS63-                      | k  | Calculated | ERR   | TPS63-                                          | k  | Calculated | ERR   |

|              | TPS60  |       | Value      | [%]   | TPS60  |       | Value      | [%]   | TPS60                       |    | Value      | [%]   | TPS60                                           |    | Value      | [%]   |

| 300          | 8H     | 13    | 301        | 0.16  | 7H     | 65    | 301        | 0.16  | 8H                          | 65 | 301        | 0.16  | 9H                                              | 65 | 301        | 0.16  |

| 600          | 7H     | 13    | 601        | 0.16  | 6H     | 65    | 601        | 0.16  | 7H                          | 65 | 601        | 0.16  | 8H                                              | 65 | 601        | 0.16  |

| 1200         | 6H     | 13    | 1202       | 0.16  | 5H     | 65    | 1202       | 0.16  | 6H                          | 65 | 1202       | 0.16  | 7H                                              | 65 | 1202       | 0.16  |

| 2400         | 5H     | 13    | 2404       | 0.16  | 4H     | 65    | 2404       | 0.16  | 5H                          | 65 | 2404       | 0.16  | 6H                                              | 65 | 2404       | 0.16  |

| 4800         | 4H     | 13    | 4808       | 0.16  | 3H     | 65    | 4808       | 0.16  | 4H                          | 65 | 4808       | 0.16  | 5H                                              | 65 | 4808       | 0.16  |

| 9600         | 3H     | 13    | 9615       | 0.16  | 2H     | 65    | 9615       | 0.16  | 3H                          | 65 | 9615       | 0.16  | 4H                                              | 65 | 9615       | 0.16  |

| 19200        | 2H     | 13    | 19231      | 0.16  | 1H     | 65    | 19231      | 0.16  | 2H                          | 65 | 19231      | 0.16  | ЗH                                              | 65 | 19231      | 0.16  |

| 24000        | 1H     | 21    | 23810      | -0.79 | 3H     | 13    | 24038      | 0.16  | 4H                          | 13 | 24038      | 0.16  | 5H                                              | 13 | 24038      | 0.16  |

| 31250        | 1H     | 16    | 31250      | 0     | 4H     | 5     | 31250      | 0     | 5H                          | 5  | 31250      | 0     | 6H                                              | 5  | 31250      | 0     |

| 38400        | 1H     | 13    | 38462      | 0.16  | 0H     | 65    | 38462      | 0.16  | 1H                          | 65 | 38462      | 0.16  | 2H                                              | 65 | 38462      | 0.16  |

| 48000        | 0H     | 21    | 47619      | -0.79 | 2H     | 13    | 48077      | 0.16  | 3H                          | 13 | 48077      | 0.16  | 4H                                              | 13 | 48077      | 0.16  |

| 76800        | 0H     | 13    | 76923      | 0.16  | 0H     | 33    | 75758      | -1.36 | 0H                          | 65 | 76923      | 0.16  | 1H                                              | 65 | 76923      | 0.16  |

| 115200       | 0H     | 9     | 111111     | -3.55 | 1H     | 11    | 113636     | -1.36 | 0H                          | 43 | 116279     | 0.94  | 0H                                              | 87 | 116279     | -0.22 |

| 153600       | -      | -     | _          | I     | 1H     | 8     | 156250     | 1.73  | 0H                          | 33 | 151515     | -1.36 | 1H                                              | 33 | 151515     | -1.36 |

| 312500       | -      |       | _          | -     | 0H     | 8     | 312500     | 0     | 1H                          | 8  | 312500     | 0     | 2H                                              | 8  | 312500     | 0     |

| 625000       | I      | I     | -          | I     | 0H     | 4     | 625000     | 0     | 1H                          | 4  | 625000     | 0     | 2H                                              | 4  | 625000     | 0     |

#### Table 14-6. Set Data of Baud Rate Generator

Remark TPS63 to TPS60: Bits 3 to 0 of clock selection register 6 (CKSR6) (setting of base clock (fxcLk6))

k:

Value set by MDL67 to MDL60 bits of baud rate generator control register 6 (BRGC6) (k = 4, 5, 6, ..., 255)

fprs: ERR:

Baud rate error

Peripheral hardware clock frequency

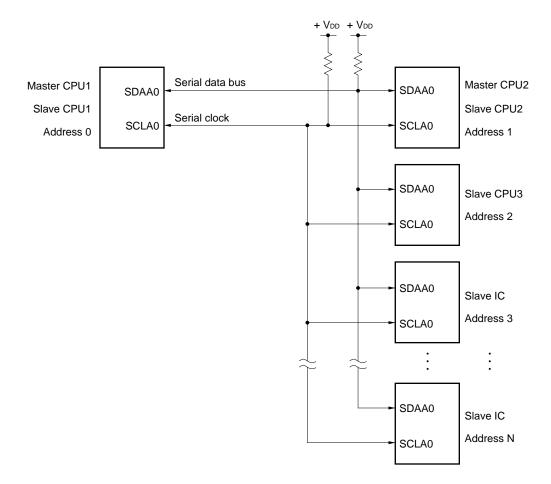

Figure 15-2 shows a serial bus configuration example.

Figure 15-2. Serial Bus Configuration Example Using I<sup>2</sup>C Bus

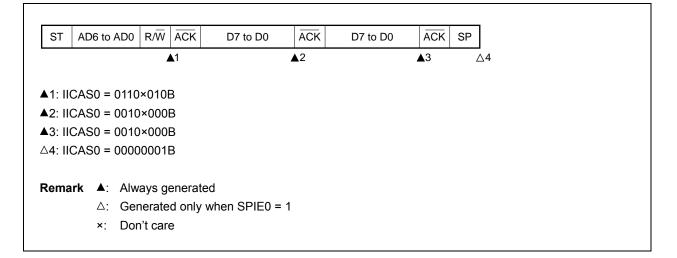

# (ii) When WTIM0 = 1

| ST A     | D6 to AD0          | R/W     | ACK      | D7 to D0     | ACK | D7 to D0 | ĀCK | SP         |

|----------|--------------------|---------|----------|--------------|-----|----------|-----|------------|

|          |                    |         | ▲1       |              | ▲2  |          |     | 3 <u>/</u> |

|          |                    |         |          |              |     |          |     |            |

| 1: IICA  | $S0 = 010^{\circ}$ | 1×110   | В        |              |     |          |     |            |

| 2: IICA  | S0 = 000           | 1×100   | В        |              |     |          |     |            |

| 3: IICA  | S0 = 000           | 1××00   | В        |              |     |          |     |            |

| ∆4: IICA | S0 = 0000          | 00001   | В        |              |     |          |     |            |

|          |                    |         |          |              |     |          |     |            |

| Remark   | ▲: Alw             | /ays g  | enerated | d            |     |          |     |            |

|          | ∆: Ge              | nerate  | d only w | when SPIE0 = | 1   |          |     |            |

|          | ×: Do              | n't can | <u>م</u> |              |     |          |     |            |

# (b) When arbitration loss occurs during transmission of extension code

## (i) When WTIM0 = 0

## **18.4 Interrupt Servicing Operations**

#### 18.4.1 Maskable interrupt acknowledgment

A maskable interrupt becomes acknowledgeable when the interrupt request flag is set to 1 and the mask (MK) flag corresponding to that interrupt request is cleared to 0. A vectored interrupt request is acknowledged if interrupts are in the interrupt enabled state (when the IE flag is set to 1). However, a low-priority interrupt request is not acknowledged during servicing of a higher priority interrupt request (when the ISP flag is reset to 0).

The times from generation of a maskable interrupt request until vectored interrupt servicing is performed are listed in Table 18-4 below.

For the interrupt request acknowledgment timing, refer to Figures 18-15 and 18-16.

Table 18-4. Time from Generation of Maskable Interrupt Request Until Servicing

|               | Minimum Time | Maximum Time <sup>Note</sup> |

|---------------|--------------|------------------------------|

| When ××PR = 0 | 7 clocks     | 32 clocks                    |

| When ××PR = 1 | 8 clocks     | 33 clocks                    |

Note If an interrupt request is generated just before a divide instruction, the wait time becomes longer.

Remark 1 clock: 1/fcpu (fcpu: CPU clock)

If two or more maskable interrupt requests are generated simultaneously, the request with a higher priority level specified in the priority specification flag is acknowledged first. If two or more interrupts requests have the same priority level, the request with the highest default priority is acknowledged first.

An interrupt request that is held pending is acknowledged when it becomes acknowledgeable.

Figure 18-14 shows the interrupt request acknowledgment algorithm.

If a maskable interrupt request is acknowledged, the contents are saved into the stacks in the order of PSW, then PC, the IE flag is reset (0), and the contents of the priority specification flag corresponding to the acknowledged interrupt are transferred to the ISP flag. The vector table data determined for each interrupt request is the loaded into the PC and branched.

Restoring from an interrupt is possible by using the RETI instruction.

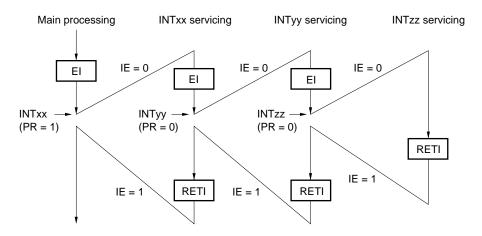

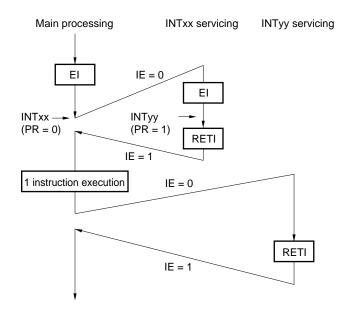

## Figure 18-17. Examples of Multiple Interrupt Servicing (1/2)

#### Example 1. Multiple interrupt servicing occurs twice

During servicing of interrupt INTxx, two interrupt requests, INTyy and INTzz, are acknowledged, and multiple interrupt servicing takes place. Before each interrupt request is acknowledged, the EI instruction must always be issued to enable interrupt request acknowledgment.

#### Example 2. Multiple interrupt servicing does not occur due to priority control

Interrupt request INTyy issued during servicing of interrupt INTxx is not acknowledged because its priority is lower than that of INTxx, and multiple interrupt servicing does not take place. The INTyy interrupt request is held pending, and is acknowledged following execution of one main processing instruction.

- PR = 0: Higher priority level

- PR = 1: Lower priority level

- IE = 0: Interrupt request acknowledgment disabled

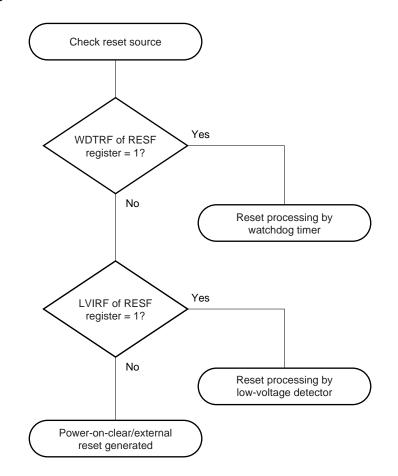

Figure 21-3. Example of Software Processing After Reset Release (2/2)

Checking reset source

## 25.4.2 RESET pin

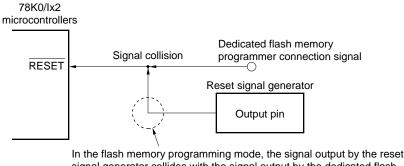

If the reset signal of the dedicated flash memory programmer is connected to the RESET pin that is connected to the reset signal generator on the board, signal collision takes place. To prevent this collision, isolate the connection with the reset signal generator.

If the reset signal is input from the user system while the flash memory programming mode is set, the flash memory will not be correctly programmed. Do not input any signal other than the reset signal of the dedicated flash memory programmer.

Figure 25-4. Signal Collision (RESET Pin)

signal generator collides with the signal output by the reset signal memory programmer. Therefore, isolate the signal of the reset signal generator.

## 25.4.3 Port pins

When the flash memory programming mode is set, all the pins not used for flash memory programming enter the same status as that immediately after reset. If external devices connected to the ports do not recognize the port status immediately after reset, the port pin must be connected to V<sub>DD</sub> or V<sub>SS</sub> via a resistor.

## 25.4.4 REGC pin

Connect the REGC pin to V<sub>DD</sub> via a capacitor (0.47 to 1  $\mu$ F) in the same manner as during normal operation. However, when using the STOP mode that has been entered since operation of the internal high-speed oscillation clock and external main system clock, 0.47  $\mu$ F is recommended. Also, use a capacitor with good characteristics, since it is used to stabilize internal voltage.

#### 25.4.5 Other signal pins

Connect X1 and X2 in the same status as in the normal operation mode.

Remark In the flash memory programming mode, the internal high-speed oscillation clock (fiH) is used.

#### 25.4.6 Power supply

To use the supply voltage output of the flash memory programmer, connect the V<sub>DD</sub> pin to V<sub>DD</sub> of the flash memory programmer, and the V<sub>SS</sub> pin to GND of the flash memory programmer.

To use the on-board supply voltage, connect in compliance with the normal operation mode.

However, be sure to connect the V<sub>DD</sub> and V<sub>SS</sub> pins to V<sub>DD</sub> and GND of the flash memory programmer to use the power monitor function with the flash memory programmer, even when using the on-board supply voltage.

Supply the same other power supplies (AVREF and AVss) as those in the normal operation mode.

| Instruction | Masaasia | Onerende       | Durfees        | Clo    | ocks   | Operation                                    |   | Flag  |

|-------------|----------|----------------|----------------|--------|--------|----------------------------------------------|---|-------|

| Group       | Mnemonic | Operands       | Bytes          | Note 1 | Note 2 | Operation                                    | Z | AC CY |

| 8-bit       | OR       | A, #byte       | 2              | 4      | -      | $A \leftarrow A \lor byte$                   | × |       |

| operation   |          | saddr, #byte   | 3              | 6      | 8      | $(saddr) \leftarrow (saddr) \lor byte$       | × |       |

|             |          | A, r Note      | <sup>3</sup> 2 | 4      | -      | $A \leftarrow A \lor r$                      | × |       |

|             |          | r, A           | 2              | 4      | -      | $r \leftarrow r \lor A$                      | × |       |

|             |          | A, saddr       | 2              | 4      | 5      | $A \leftarrow A \lor (saddr)$                | × |       |

|             |          | A, !addr16     | 3              | 8      | 9      | $A \leftarrow A \lor (addr16)$               | × |       |

|             |          | A, [HL]        | 1              | 4      | 5      | $A \leftarrow A \lor (HL)$                   | × |       |

|             |          | A, [HL + byte] | 2              | 8      | 9      | $A \leftarrow A \lor (HL + byte)$            | × |       |

|             |          | A, [HL + B]    | 2              | 8      | 9      | $A \leftarrow A \lor (HL + B)$               | × |       |

|             |          | A, [HL + C]    | 2              | 8      | 9      | $A \leftarrow A \lor (HL + C)$               | × |       |

|             | XOR      | A, #byte       | 2              | 4      | -      | $A \leftarrow A + byte$                      | × |       |

|             |          | saddr, #byte   | 3              | 6      | 8      | $(saddr) \leftarrow (saddr) + byte$          | × |       |

|             |          | A, r           | <sup>3</sup> 2 | 4      | -      | $A \leftarrow A \nleftrightarrow r$          | × |       |

|             |          | r, A           | 2              | 4      | -      | $r \leftarrow r \nleftrightarrow A$          | × |       |

|             |          | A, saddr       | 2              | 4      | 5      | $A \leftarrow A \leftrightarrow (saddr)$     | × |       |

|             |          | A, !addr16     | 3              | 8      | 9      | $A \leftarrow A \leftrightarrow$ (addr16)    | × |       |

|             |          | A, [HL]        | 1              | 4      | 5      | $A \leftarrow A \nleftrightarrow (HL)$       | × |       |

|             |          | A, [HL + byte] | 2              | 8      | 9      | $A \leftarrow A \leftrightarrow (HL + byte)$ | × |       |

|             |          | A, [HL + B]    | 2              | 8      | 9      | $A \leftarrow A \leftrightarrow (HL + B)$    | × |       |

|             |          | A, [HL + C]    | 2              | 8      | 9      | $A \leftarrow A \leftrightarrow (HL + C)$    | × |       |

|             | СМР      | A, #byte       | 2              | 4      | -      | A – byte                                     | × | × ×   |

|             |          | saddr, #byte   | 3              | 6      | 8      | (saddr) – byte                               | × | x x   |

|             |          | A, r Note      | <sup>3</sup> 2 | 4      | -      | A – r                                        | × | × ×   |

|             |          | r, A           | 2              | 4      | -      | r – A                                        | × | × ×   |

|             |          | A, saddr       | 2              | 4      | 5      | A – (saddr)                                  | × | × ×   |

|             |          | A, !addr16     | 3              | 8      | 9      | A – (addr16)                                 | × | × ×   |

|             |          | A, [HL]        | 1              | 4      | 5      | A – (HL)                                     | × | × ×   |

|             |          | A, [HL + byte] | 2              | 8      | 9      | A – (HL + byte)                              | × | × ×   |

|             |          | A, [HL + B]    | 2              | 8      | 9      | A – (HL + B)                                 | × | × ×   |

|             |          | A, [HL + C]    | 2              | 8      | 9      | A – (HL + C)                                 | × | × ×   |

Notes 1. When the internal high-speed RAM area is accessed or for an instruction with no data access

- 2. When an area except the internal high-speed RAM area is accessed

- 3. Except "r = A"

- **Remarks 1.** One instruction clock cycle is one cycle of the CPU clock (fcPu) selected by the processor clock control register (PCC).

- 2. This clock cycle applies to the internal ROM program.

## Caution The pins mounted depend on the product. Refer to Caution 2 at the beginning of this chapter.

| Parameter            | Symbol           | Condi                                               | tions                                                                                                        | MIN.                  | TYP.   | MAX.                 | Unit |

|----------------------|------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------|--------|----------------------|------|

| Input voltage, high  | VIH1             | P37, P121, P122, P125                               |                                                                                                              | 0.7Vdd                |        | VDD                  | V    |

|                      | VIH2             | P20 to P27, P70 AV <sub>REF</sub> = V <sub>DD</sub> |                                                                                                              | 0.7AV <sub>REF</sub>  |        | AVREF                | V    |

|                      | VIH3             | P60, P61 (I/O port mode)                            |                                                                                                              | 0.7Vdd                |        | VDD                  | V    |

|                      | VIH4             | P00 to P02, P30 to P36, R                           | ESET, EXCLK                                                                                                  | 0.8VDD                |        | VDD                  | V    |

|                      | VIH5             | P60, P61                                            | $3.4~V \le V_{\text{DD}} \le 5.5~V$                                                                          | 0.8VDD                |        |                      | V    |

|                      |                  | (SMBus input mode)                                  | $2.7~V \leq V_{\text{DD}} < 3.4~V$                                                                           | 2.1                   |        |                      | V    |

|                      | VIH6             | X1, X2                                              | Vdd - 0.1                                                                                                    |                       | VDD    | V                    |      |

| Input voltage, low   | VIL1             | P37, P121, P122, P125                               |                                                                                                              | 0                     |        | 0.3Vdd               | V    |

|                      | VIL2             | P20 to P27, P70                                     | AV <sub>REF</sub> = V <sub>DD</sub>                                                                          | 0                     |        | 0.3AV <sub>REF</sub> | V    |

|                      | VIL3             | P60, P61 (I/O port mode)                            | 0                                                                                                            |                       | 0.3VDD | V                    |      |

|                      | VIL4             | P00 to P02, P30 to P36, R                           | 0                                                                                                            |                       | 0.2VDD | V                    |      |

|                      | VIL5             | P60, P61                                            | $3.4~V \le V_{\text{DD}} \le 5.5~V$                                                                          | 0                     |        | 0.2VDD               | V    |

|                      |                  | (SMBus input mode)                                  | $2.7~V \leq V_{\text{DD}} < 3.4~V$                                                                           | 0                     |        | 0.8                  | V    |

|                      | VIL6             | X1, X2                                              |                                                                                                              | 0                     |        | 0.1                  | V    |

| Output voltage, high | VOH1             | P00 to P02, P30 to P37,<br>P60, P61                 | $\begin{array}{l} 4.0 \ V \leq V_{\text{DD}} \leq 5.5 \ V, \\ I_{\text{OH1}} = -3.0 \ \text{mA} \end{array}$ | $V_{\text{DD}}-0.7$   |        |                      | V    |

|                      |                  |                                                     | $2.7 \text{ V} \le \text{V}_{\text{DD}} < 4.0 \text{ V},$<br>I_OH1 = -2.5 mA                                 | V <sub>DD</sub> - 0.5 |        |                      | V    |

|                      | V <sub>OH2</sub> | P20 to P27, P70                                     | AV <sub>REF</sub> = V <sub>DD</sub> ,<br>I <sub>OH2</sub> = -100 μA                                          | Vdd - 0.5             |        |                      | V    |

# (TA = -40 to +105°C, 2.7 V $\leq$ VDD $\leq$ 5.5 V, AVREF $\leq$ VDD, Vss = AVss = 0 V)

**Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of port pins.

Caution For P122/EXCLK, the value of V<sub>IH</sub> and V<sub>IL</sub> differs according to the input port mode or external clock mode.

Make sure to satisfy the DC characteristics of EXCLK in external clock input mode.

| Edition     | Description                                                                                                                              | Chapter                                              |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--|--|

| 3rd Edition | Modification of (4) 0083H/1083H in 24.1 Functions of Option Bytes                                                                        | CHAPTER 24 OPTION                                    |  |  |

|             | Modification of Figure 24-1. Format of Option Byte (3/3)                                                                                 | BYTE                                                 |  |  |

|             | Modification of Figure 25-2 Environment for Writing Program to Flash Memory                                                              | CHAPTER 25 FLASH                                     |  |  |

|             | Modification of Table 25-2 Pin Connection                                                                                                | MEMORY                                               |  |  |

|             | Modification of 25.4.1 TOOL pins                                                                                                         |                                                      |  |  |

|             | Addition of 25.4.7 On-board writing when connecting crystal/ceramic resonator                                                            |                                                      |  |  |

|             | Modification of 25.5.2 Flash memory programming mode                                                                                     |                                                      |  |  |

|             | Addition of 25.7 Processing Time for Each Command When PG-FP5 Is Used (Reference)                                                        |                                                      |  |  |

|             | Modification of Cautions 2 to 4 and Remark in 25.8 Flash Memory Programming by Self Programming                                          | -                                                    |  |  |

|             | Addition of <b>25.8.1 Register controlling self programming mode</b> and <b>25.8.2 Flow of self programming (Rewriting Flash Memory)</b> |                                                      |  |  |

|             | Modification of Caution in 25.8.3 Boot swap function                                                                                     |                                                      |  |  |

|             | Addition of 25.9 Creating ROM Code to Place Order for Previously Written Product                                                         | ]                                                    |  |  |

|             | Addition of Caution 2 to 26.1 Connecting QB-MINI2 to 78K0/Ix2 Microcontrollers                                                           | CHAPTER 26 ON-CHI                                    |  |  |

|             | Modification of Figure 26-1 Connection Example of QB-MINI2 and 78K0/lx2<br>Microcontrollers                                              | DEBUG FUNCTION                                       |  |  |

|             | Modification of 26.2 On-Chip Debug Security ID                                                                                           |                                                      |  |  |

|             | Addition of 26.3 Securing of User Resources                                                                                              |                                                      |  |  |

|             | Revision of chapter                                                                                                                      | CHAPTER 28<br>ELECTRICAL<br>SPECIFICATIONS           |  |  |

|             | Modification of Table 30-1 Surface Mounting Type Soldering Conditions                                                                    | CHAPTER 30<br>RECOMMENDED<br>SOLDERING<br>CONDITIONS |  |  |

|             | Modification of Table 31-1. Registers That Generate Wait and Number of CPU Wait Clocks (2/2)                                             | CHAPTER 31<br>CAUTIONS FOR WAI                       |  |  |

|             | Modification of Notes 3 and 4 in Figure A-1 Development Tool Configuration (1/2)                                                         | APPENDIX A                                           |  |  |

|             | Modification of Note 5 in Figure A-1 Development Tool Configuration (2/2)                                                                | DEVELOPMENT TOOL                                     |  |  |

|             | Addition of Note 1 to A.3.1 When using flash memory programmer PG-FP5 and FL-<br>PR5                                                     |                                                      |  |  |

|             | Addition of the product name of system simulator to A.5 Debugging Tools (Software)                                                       | ]                                                    |  |  |

|             | Addition of chapter                                                                                                                      | APPENDIX B<br>REGISTER INDEX                         |  |  |

|             | Addition of C.2 Revision History of Preceding Editions                                                                                   | APPENDIX C REVISIO<br>HISTORY                        |  |  |

| 4th Edition | Addition of 32-pin products to 78K0/IB2                                                                                                  | Throughout                                           |  |  |

|             | Change URL of Renesas Electronics website                                                                                                |                                                      |  |  |

|             | Deletion of "(To be prepared)" and change of document no. of related documents                                                           | How to Use This<br>Manual                            |  |  |

|             | Addition of 20-pin plastic SOP (7.62 mm (300)) and 32-pin plastic WQFN (fine pitch) (5 x 5) to <b>1.2 Ordering Information</b>           | CHAPTER 1 OUTLIN                                     |  |  |

|             | Addition of 20-pin plastic SOP (7.62 mm (300)) and 32-pin plastic WQFN (fine pitch) (5 x 5) to <b>1.3 Pin Configuration (Top View)</b>   |                                                      |  |  |

|             | Change of Port 12 of 30-pin plastic SSOP (7.62 mm (300))                                                                                 |                                                      |  |  |

78K0/lx2