Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | Coldfire V1                                                             |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 50MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, SCI, SPI                                      |

| Peripherals                | LVD, PWM, WDT                                                           |

| Number of I/O              | 69                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 32K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 24x12b                                                              |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 80-LQFP                                                                 |

| Supplier Device Package    | 80-LQFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcf51ac256aclke |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1   | MCF    | 51AC256 Family Configurations                                                         |

|-----|--------|---------------------------------------------------------------------------------------|

|     | 1.1    | Device Comparison3                                                                    |

|     | 1.2    | Block Diagram4                                                                        |

|     | 1.3    | Features                                                                              |

|     |        | 1.3.1 Feature List                                                                    |

|     | 1.4    | Part Numbers                                                                          |

|     | 1.5    | Pinouts and Packaging                                                                 |

| 2   | Elect  | rical Characteristics                                                                 |

|     | 2.1    | Parameter Classification                                                              |

|     | 2.2    | Absolute Maximum Ratings                                                              |

|     | 2.3    | Thermal Characteristics                                                               |

|     | 2.4    | Electrostatic Discharge (ESD) Protection Characteristics<br>19                        |

|     | 2.5    | DC Characteristics                                                                    |

|     | 2.6    | Supply Current Characteristics                                                        |

|     | 2.7    | Analog Comparator (ACMP) Electricals                                                  |

|     | 2.8    | ADC Characteristics                                                                   |

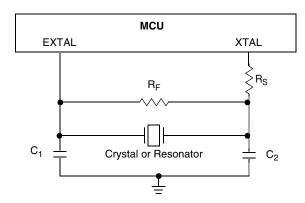

|     | 2.9    | External Oscillator (XOSC) Characteristics                                            |

|     | 2.10   | MCG Specifications32                                                                  |

|     | 2.11   | AC Characteristics                                                                    |

|     |        | 2.11.1 Control Timing                                                                 |

|     |        | 2.11.2 Timer (TPM/FTM) Module Timing                                                  |

|     |        | 2.11.3 MSCAN                                                                          |

|     | 2.12   | SPI Characteristics                                                                   |

|     | 2.13   | Flash Specifications                                                                  |

|     | 2.14   | EMC Performance                                                                       |

|     |        | 2.14.1 Radiated Emissions39                                                           |

| 3   |        | anical Outline Drawings                                                               |

| 4   | Revis  | sion History                                                                          |

|     |        |                                                                                       |

| Lis | st of  | Figures                                                                               |

|     |        | .MCF51AC256 Series Block Diagram 5                                                    |

| Fig | gure 2 | .MCF51AC256 Series ColdFire Microcontroller                                           |

|     |        | 80-Pin LQFP                                                                           |

| Fig | gure 3 | .MCF51AC256 Series ColdFire Microcontroller                                           |

|     |        | 64-Pin QFP/LQFP                                                                       |

| Fig | gure 4 | .MCF51AC256 Series ColdFire Microcontroller                                           |

|     |        | 44-Pin LQFP                                                                           |

| Fig | gure 5 | Typical I <sub>OH</sub> vs. V <sub>DD</sub> -V <sub>OH</sub> at V <sub>DD</sub> = 3 V |

|     |        | (Low Drive, PTxDSn = 0)                                                               |

| Fig | gure 6 | Typical $I_{OH}$ vs. $V_{DD}-V_{OH}$ at $V_{DD}=3$ V                                  |

|     |        | (High Drive, PTxDSn = 1)                                                              |

| Fig | gure 7 | Typical $I_{OH}$ vs. $V_{DD}-V_{OH}$ at $V_{DD}=5$ V                                  |

|     |        | (Low Drive, PTxDSn = 0)                                                               |

| Figure 8. Typical $I_{OH}$ vs. $V_{DD}$ – $V_{OH}$ at $V_{DD}$ = 5 V |

|----------------------------------------------------------------------|

| (High Drive, PTxDSn = 1)                                             |

| Figure 9. Typical Run IDD vs. System Clock Freq.                     |

| for FEI and FBE Modes                                                |

| Figure 10.ADC Input Impedance Equivalency Diagram 29                 |

| Figure 11.Reset Timing                                               |

| Figure 12.IRQ/KBIPx Timing                                           |

| Figure 13.Timer External Clock                                       |

| Figure 14.Timer Input Capture Pulse                                  |

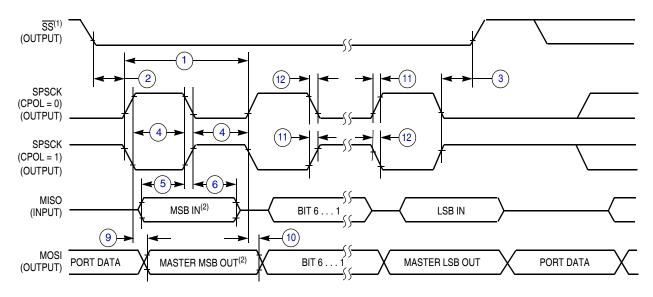

| Figure 15.SPI Master Timing (CPHA = 0)                               |

| Figure 16.SPI Master Timing (CPHA =1)                                |

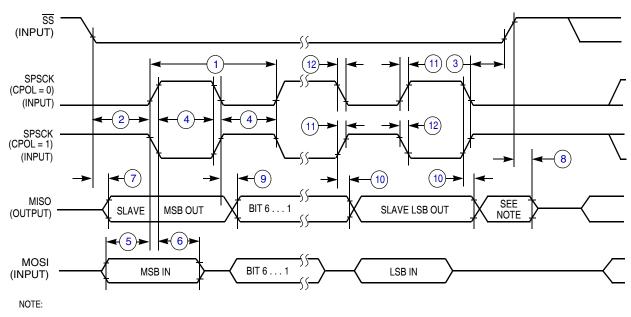

| Figure 17.SPI Slave Timing (CPHA = 0)                                |

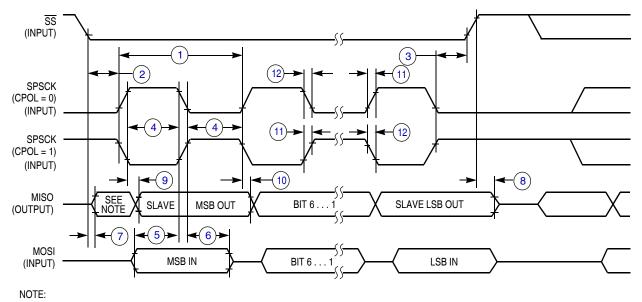

| Figure 18.SPI Slave Timing (CPHA = 1)                                |

| List of Tables                                                       |

| Table 1. MCF51AC256 Series Device Comparison                         |

| Table 2. MCF51AC256 Series Functional Units 6                        |

| Table 3. Orderable Part Number Summary                               |

| Table 4. Pin Availability by Package Pin-Count                       |

| Table 5. Parameter Classifications                                   |

| Table 6. Absolute Maximum Ratings                                    |

| Table 7. Thermal Characteristics                                     |

| Table 8. ESD and Latch-up Test Conditions 20                         |

| Table 9. ESD and Latch-Up Protection Characteristics 20              |

| Table 10.DC Characteristics                                          |

| Table 11. Supply Current Characteristics                             |

| Table 12. Analog Comparator Electrical Specifications 27             |

| Table 13.5 Volt 12-bit ADC Operating Conditions 28                   |

| Table 14.5 Volt 12-bit ADC Characteristics                           |

| $(V_{REFH} = V_{DDA}, V_{REFL} = V_{SSA}) \dots 29$                  |

| Table 15. Oscillator Electrical Specifications                       |

| (Temperature Range = -40 to 105 °C Ambient) 31                       |

| Table 16.MCG Frequency Specifications                                |

| (Temperature Range = -40 to 105 °C Ambient) 32                       |

| Table 17. Control Timing                                             |

| Table 18.TPM/FTM Input Timing                                        |

| Table 19.MSCAN Wake-Up Pulse Characteristics                         |

| Table 20.SPI Timing                                                  |

| Table 21.Flash Characteristics                                       |

| Table 22.Package Information                                         |

| Table 23.Revision History                                            |

|                                                                      |

|                                                                      |

# 1.1 Device Comparison

The MCF51AC256 series is summarized in Table 1.

Table 1. MCF51AC256 Series Device Comparison

| Factoria                                            | MCF51  | AC256A | МС     | F51AC2 | 56B    | MCF51  | AC128A | МС                    | F51AC12 | 28C    |

|-----------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|-----------------------|---------|--------|

| Feature                                             | 80-pin | 64-pin | 80-pin | 64-pin | 44-pin | 80-pin | 64-pin | 80-pin                | 64-pin  | 44-pin |

| Flash memory size (Kbytes)                          |        |        | 256    | •      |        |        |        | 128                   |         |        |

| RAM size (Kbytes)                                   |        |        | 32     |        |        |        |        | 32 or 16 <sup>1</sup> |         |        |

| V1 ColdFire core with BDM (background debug module) |        |        |        |        | ١      | ⁄es    |        |                       |         |        |

| ACMP1 (analog comparator)                           |        |        |        |        | ١      | ⁄es    |        |                       |         |        |

| ACMP2 (analog comparator)                           | Ye     | es     | Ye     | es     | No     |        | Y      | es                    |         | No     |

| ADC (analog-to-digital converter) channels (12-bit) | 24     | 20     | 24     | 20     | 9      | 24     | 20     | 24                    | 20      | 9      |

| CAN (controller area network)                       | Ye     | es     |        | No     |        | Ye     | es     |                       | No      |        |

| COP (computer operating properly)                   |        |        |        |        | ١      | ⁄es    |        |                       |         |        |

| CRC (cyclic redundancy check)                       | Yes    |        |        |        |        |        |        |                       |         |        |

| RTI                                                 | Yes    |        |        |        |        |        |        |                       |         |        |

| DBG (debug)                                         | Yes    |        |        |        |        |        |        |                       |         |        |

| IIC1 (inter-integrated circuit)                     |        |        |        |        | Υ      | ⁄es    |        |                       |         |        |

| IRQ (interrupt request input)                       |        |        |        |        | ١      | ⁄es    |        |                       |         |        |

| INTC (interrupt controller)                         |        |        |        |        | ١      | ⁄es    |        |                       |         |        |

| KBI (keyboard interrupts)                           | Yes    |        |        |        |        |        |        |                       |         |        |

| LVD (low-voltage detector)                          | Yes    |        |        |        |        |        |        |                       |         |        |

| MCG (multipurpose clock generator)                  |        |        |        |        | ١      | ⁄es    |        |                       |         |        |

| OSC (crystal oscillator)                            |        |        |        |        | ١      | ⁄es    |        |                       |         |        |

| Port I/O <sup>2</sup>                               | 69     | 54     | 69     | 54     | 36     | 69     | 54     | 69                    | 54      | 36     |

| RGPIO (rapid general-purpose I/O)                   |        | 1      | 6      | •      | 12     |        | 1      | 6                     |         | 12     |

| SCI1, SCI2 (serial communications interfaces)       |        |        |        |        | ١      | es/es  |        |                       |         |        |

| SPI1 (serial peripheral interface)                  |        |        |        |        | ١      | ⁄es    |        |                       |         |        |

| SPI2 (serial peripheral interface)                  | Yes    | No     | Yes    | ٨      | lo     | Yes    | No     | Yes                   | N       | 0      |

| FTM1 (flexible timer module) channels               |        | 6      | 6      |        | 4      |        | . (    | 6                     |         | 4      |

| FTM2 channels                                       | 6      | 2      | 6      | 2      | 2      | 6      | 2      | 6                     | 2       | 2      |

- Trimmable internal reference allows 0.2% resolution and 2% deviation

- Analog-to-digital converter (ADC)

- 24 analog inputs with 12 bits resolution

- Output formatted in 12-, 10- or 8-bit right-justified format

- Single or continuous conversion (automatic return to idle after single conversion)

- Operation in low-power modes for lower noise operation

- Asynchronous clock source for lower noise operation

- Automatic compare with interrupt for less-than, or greater-than or equal-to, programmable value

- On-chip temperature sensor

- Flexible timer/pulse-width modulators (FTM)

- 16-bit Free-running counter or a counter with initial and final value. The counting can be up and unsigned, up and signed, or up-down and unsigned

- Up to 6 channels, and each channel can be configured for input capture, output compare or edge-aligned PWM mode, all channels can be configured for center-aligned PWM mode

- Channels can operate as pairs with equal outputs, pairs with complimentary outputs or independent channels (with independent outputs)

- Each pair of channels can be combined to generate a PWM signal (with independent control of both edges of PWM signal)

- Deadtime insertion is available for each complementary pair

- The load of the FTM registers which have write buffer can be synchronized; write protection for critical registers

- Generation of the triggers to ADC (hardware trigger)

- A fault input for global fault control

- Backwards compatible with TPM

- Timer/pulse width modulator (TPM)

- 16-bit free-running or modulo up/down count operation

- Two channels, each channel may be input capture, output compare, or edge-aligned PWM

- One interrupt per channel plus terminal count interrupt

- Cyclic redundancy check (CRC) generator

- High speed hardware CRC generator circuit using 16-bit shift register

- CRC16-CCITT compliancy with  $x^{16} + x^{12} + x^5 + 1$  polynomial

- Error detection for all single, double, odd, and most multi-bit errors

- Programmable initial seed value

- Analog comparators (ACMP)

- Full rail to rail supply operation

- Selectable interrupt on rising edge, falling edge, or either rising or falling edges of comparator output

- Option to compare to fixed internal bandgap reference voltage

- Option to allow comparator output to be visible on a pin, ACMPxO

## **Table 3. Orderable Part Number Summary**

| MCF51AC256ACPUE | MCF51AC256 ColdFire Microcontroller with CAN    | 256 / 32 | 64 LQFP | –40°C to 85°C  |

|-----------------|-------------------------------------------------|----------|---------|----------------|

| MCF51AC256BCPUE | MCF51AC256 ColdFire Microcontroller without CAN | 256 / 32 | 64 LQFP | –40°C to 85°C  |

| MCF51AC256BCFGE | MCF51AC256 ColdFire Microcontroller without CAN | 256/32   | 44 LQFP | –40°C to 85°C  |

| MCF51AC128ACFUE | MCF51AC128 ColdFire Microcontroller with CAN    | 128 / 32 | 64 QFP  | –40°C to 85°C  |

| MCF51AC128CCFUE | MCF51AC128 ColdFire Microcontroller without CAN | 128 / 16 | 64 QFP  | –40°C to 85°C  |

| MCF51AC128ACLKE | MCF51AC128 ColdFire Microcontroller with CAN    | 128 / 32 | 80 LQFP | –40°C to 85°C  |

| MCF51AC128CCLKE | MCF51AC128 ColdFire Microcontroller without CAN | 128 / 16 | 80 LQFP | –40°C to 85°CC |

| MCF51AC128ACPUE | MCF51AC128 ColdFire Microcontroller with CAN    | 128 / 32 | 64 LQFP | –40°C to 85°C  |

| MCF51AC128CCPUE | MCF51AC128 ColdFire Microcontroller without CAN | 128 / 16 | 64 LQFP | –40°C to 85°C  |

| MCF51AC128CCFGE | MCF51AC128 ColdFire Microcontroller without CAN | 128 / 16 | 44 LQFP | –40°C to 85°C  |

## 1.5 Pinouts and Packaging

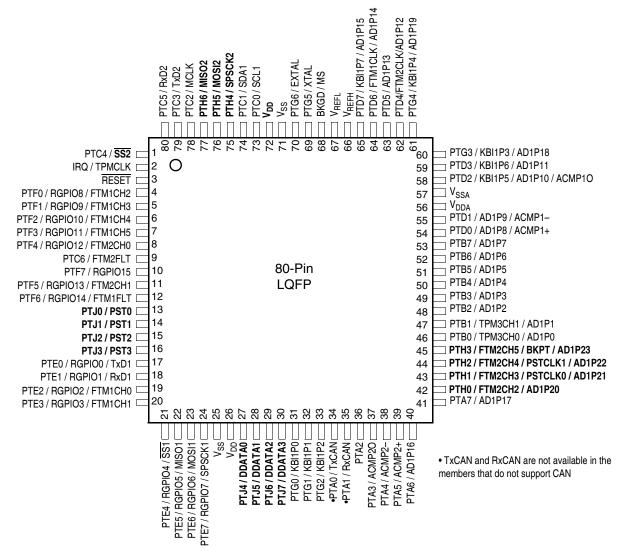

Figure 2 shows the pinout of the 80-pin LQFP.

Figure 2. MCF51AC256 Series ColdFire Microcontroller 80-Pin LQFP

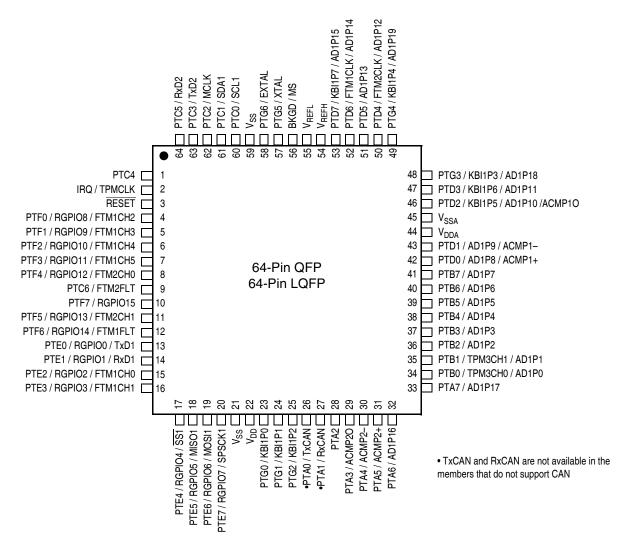

Figure 3 shows the pinout of the 64-pin LQFP and QFP.

Figure 3. MCF51AC256 Series ColdFire Microcontroller 64-Pin QFP/LQFP

Figure 4 shows the pinout of the 44-pin LQFP.

Table 4. Pin Availability by Package Pin-Count (continued)

| Pir | n Num | ber | Lowe              | Lowest < Priority> Highes |         |        |

|-----|-------|-----|-------------------|---------------------------|---------|--------|

| 80  | 64    | 44  | Port Pin          | Alt 1                     | Alt 2   | Alt 3  |

| 8   | 8     | 6   | PTF4              | RGPIO12                   | FTM2CH0 |        |

| 9   | 9     | _   | PTC6              | FTM2FLT                   |         |        |

| 10  | 10    | _   | PTF7              | RGPIO15                   |         |        |

| 11  | 11    | 7   | PTF5              | RGPIO13                   | FTM2CH1 |        |

| 12  | 12    | _   | PTF6              | RGPIO14                   | FTM1FLT |        |

| 13  |       | _   | PTJ0              | PST0                      |         |        |

| 14  |       | _   | PTJ1              | PST1                      |         |        |

| 15  |       | _   | PTJ2              | PST2                      |         |        |

| 16  |       | _   | PTJ3              | PST3                      |         |        |

| 17  | 13    | 8   | PTE0              | RGPIO0                    | TxD1    |        |

| 18  | 14    | 9   | PTE1              | RGPIO1                    | RxD1    |        |

| 19  | 15    | 10  | PTE2              | RGPIO2                    | FTM1CH0 |        |

| 20  | 16    | 11  | PTE3              | RGPIO3                    | FTM1CH1 |        |

| 21  | 17    | 12  | PTE4              | RGPIO4                    | SS1     |        |

| 22  | 18    | 13  | PTE5              | RGPIO5                    | MISO1   |        |

| 23  | 19    | 14  | PTE6              | RGPIO6                    | MOSI1   |        |

| 24  | 20    | 15  | PTE7              | RGPI07                    | SPSCK1  |        |

| 25  | 21    | 16  | $V_{SS}$          |                           |         |        |

| 26  | 22    | 17  | $V_{\mathrm{DD}}$ |                           |         |        |

| 27  | _     | _   | PTJ4              | DDATA0                    |         |        |

| 28  | _     | _   | PTJ5              | DDATA1                    |         |        |

| 29  | _     | _   | PTJ6              | DDATA2                    |         |        |

| 30  | _     | _   | PTJ7              | DDATA3                    |         |        |

| 31  | 23    | 18  | PTG0              | KBI1P0                    |         |        |

| 32  | 24    | 19  | PTG1              | KBI1P1                    |         |        |

| 33  | 25    | 20  | PTG2              | KBI1P2                    |         |        |

| 34  | 26    | 21  | PTA0              | TxCAN <sup>2</sup>        |         |        |

| 35  | 27    | 22  | PTA1              | RxCAN <sup>3</sup>        |         |        |

| 36  | 28    | _   | PTA2              |                           |         |        |

| 37  | 29    | _   | PTA3              | ACMP2O                    |         |        |

| 38  | 30    | _   | PTA4              | ACMP2-                    |         |        |

| 39  | 31    | _   | PTA5              | ACMP2+                    |         |        |

| 40  | 32    | _   | PTA6              | AD1P16                    |         |        |

| 41  | 33    | _   | PTA7              | AD1P17                    |         |        |

| 42  | _     | _   | PTH0              | FTM2CH2                   | AD1P20  |        |

| 43  | _     | _   | PTH1              | FTM2CH3                   | PSTCLK0 | AD1P21 |

| 44  | _     | _   | PTH2              | FTM2CH4                   | PSTCLK1 | AD1P22 |

| 45  | _     | _   | PTH3              | FTM2CH5                   | BKPT    | AD1P23 |

| 46  | 34    | 23  | PTB0              | TPM3CH0                   | AD1P0   |        |

| 47  | 35    | 24  | PTB1              | TPM3CH1                   | AD1P1   |        |

| 48  | 36    | 25  | PTB2              | AD1P2                     |         |        |

MCF51AC256 ColdFire Microcontroller Data Sheet, Rev.7

**Table 6. Absolute Maximum Ratings**

| Rating                                                                                                               | Symbol           | Value                          | Unit |

|----------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------|------|

| Supply voltage                                                                                                       | $V_{DD}$         | -0.3 to 5.8                    | V    |

| Input voltage                                                                                                        | V <sub>In</sub>  | $-0.3 \text{ to V}_{DD} + 0.3$ | V    |

| Instantaneous maximum current Single pin limit (applies to all port pins) <sup>1</sup> , <sup>2</sup> , <sup>3</sup> | I <sub>D</sub>   | ±25                            | mA   |

| Maximum current into V <sub>DD</sub>                                                                                 | I <sub>DD</sub>  | 120                            | mA   |

| Storage temperature                                                                                                  | T <sub>stg</sub> | -55 to 150                     | °C   |

Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive (V<sub>DD</sub>) and negative (V<sub>SS</sub>) clamp voltages, then use the larger of the two resistance values.

### 2.3 Thermal Characteristics

This section provides information about operating temperature range, power dissipation, and package thermal resistance. Power dissipation on I/O pins is usually small compared to the power dissipation in on-chip logic and it is user-determined rather than being controlled by the MCU design. In order to take  $P_{I/O}$  into account in power calculations, determine the difference between actual pin voltage and  $V_{SS}$  or  $V_{DD}$  and multiply by the pin current for each I/O pin. Except in cases of unusually high pin current (heavy loads), the difference between pin voltage and  $V_{SS}$  or  $V_{DD}$  will be very small.

**Table 7. Thermal Characteristics**

| Rating                                 |            | Symbol            | Value      | Unit |

|----------------------------------------|------------|-------------------|------------|------|

| Operating temperature range (packaged) |            | T <sub>A</sub>    | -40 to 105 | °C   |

| Maximum junction temperature           |            | TJ                | 150        | °C   |

| Thermal resistance 1,2,3,4             |            |                   |            |      |

| 80-pin LQFP                            | 1s         |                   | 51         |      |

| 64-pin LQFP                            | 2s2p       |                   | 38<br>59   |      |

| 64-pin QFP                             | 2s2p       | $\theta_{\sf JA}$ | 41<br>50   | °C/W |

| 44 pin LOED                            | 1s<br>2s2p |                   | 36         |      |

| 44-pin LQFP                            | 1s<br>2s2p |                   | 67<br>45   |      |

MCF51AC256 ColdFire Microcontroller Data Sheet, Rev.7

$<sup>^{2}</sup>$  All functional non-supply pins are internally clamped to  $V_{SS}$  and  $V_{DD}$ .

Power supply must maintain regulation within operating V<sub>DD</sub> range during instantaneous and operating maximum current conditions. If positive injection current (V<sub>In</sub> > V<sub>DD</sub>) is greater than I<sub>DD</sub>, the injection current may flow out of V<sub>DD</sub> and could result in external power supply going out of regulation. Ensure external V<sub>DD</sub> load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if the clock rate is very low which would reduce overall power consumption.

- Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance

- <sup>2</sup> Junction to Ambient Natural Convection

- <sup>3</sup> 1s Single layer board, one signal layer

- <sup>4</sup> 2s2p Four layer board, 2 signal and 2 power layers

The average chip-junction temperature  $(T_I)$  in  ${}^{\circ}C$  can be obtained from:

$$T_{J} = T_{A} + (P_{D} \times \theta_{JA})$$

Eqn. 1

where:

$T_A = Ambient temperature, °C$

$\theta_{\rm JA}$  = Package thermal resistance, junction-to-ambient, °C/W

$$P_{D} = P_{int} + P_{I/O}$$

$P_{int} = I_{DD} \times V_{DD}$ , Watts — chip internal power

$P_{I/O}$  = Power dissipation on input and output pins — user determined

For most applications,  $P_{I/O} \ll P_{int}$  and can be neglected. An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is:

$$P_D = K \div (T_A + 273^{\circ}C)$$

Eqn. 2

Solving Equation 1 and Equation 2 for K gives:

$$K = P_D \times (T_A + 273^{\circ}C) + \theta_{JA} \times (P_D)^2$$

Eqn. 3

where K is a constant pertaining to the particular part. K can be determined from Equation 3 by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K, the values of  $P_D$  and  $T_J$  can be obtained by solving Equation 1 and Equation 2 iteratively for any value of  $T_A$ .

## 2.4 Electrostatic Discharge (ESD) Protection Characteristics

Although damage from static discharge is much less common on these devices than on early CMOS circuits, normal handling precautions should be used to avoid exposure to static discharge. Qualification tests are performed to ensure that these devices can withstand exposure to reasonable levels of static without suffering any permanent damage.

All ESD testing is in conformity with CDF-AEC-Q00 Stress Test Qualification for Automotive Grade Integrated Circuits. (http://www.aecouncil.com/) This device was qualified to AEC-Q100 Rev E.

A device is considered to have failed if, after exposure to ESD pulses, the device no longer meets the device specification requirements. Complete dc parametric and functional testing is performed per the

applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

**Table 8. ESD and Latch-up Test Conditions**

| Model         | Description                 | Symbol | Value                                     | Unit                               |

|---------------|-----------------------------|--------|-------------------------------------------|------------------------------------|

| Human body    | Series resistance           | R1     | 1500                                      | Ω                                  |

|               | Storage capacitance         | ,      |                                           |                                    |

|               | Number of pulse per pin     | _      | 3                                         | 500 Ω 100 pF 3 0 Ω 0 pF 3 — -2.5 V |

| Charge device | Series resistance           | R1     | 0                                         | Ω                                  |

| model         | Storage capacitance         | С      | 0                                         | pF                                 |

|               | Number of pulse per pin     | _      | 1500 Ω 100 pF 3 0 Ω 0 pF 3 — -2.5 V       | _                                  |

| Latch-up      | Minimum input voltage limit | _      | -2.5                                      | V                                  |

|               | Maximum input voltage limit | _      | R1 1500 C 100 — 3 R1 0 C 0 — 3 — 3 — -2.5 | ٧                                  |

Table 9. ESD and Latch-Up Protection Characteristics

| Num | Rating                                     | Symbol           | Min   | Max | Unit |

|-----|--------------------------------------------|------------------|-------|-----|------|

| 1   | Human body model (HBM)                     | $V_{HBM}$        | ±2000 |     | V    |

| 2   | Charge device model (CDM)                  | V <sub>CDM</sub> | ±500  | _   | V    |

| 3   | Latch-up current at T <sub>A</sub> = 85 °C | I <sub>LAT</sub> | ±100  |     | mA   |

## 2.5 DC Characteristics

This section includes information about power supply requirements, I/O pin characteristics, and power supply current in various operating modes.

**Table 10. DC Characteristics**

| Num | С | Parameter                                     | Symbol          | Min                   | Typical <sup>1</sup> | Max              | Unit |

|-----|---|-----------------------------------------------|-----------------|-----------------------|----------------------|------------------|------|

| 1   | — | Operating voltage                             |                 | 2.7                   | _                    | 5.5              | V    |

|     |   | Output high voltage — Low drive (PTxDSn = 0)  |                 |                       |                      |                  |      |

|     |   | 5 V, $I_{Load} = -4 \text{ mA}$               |                 | V <sub>DD</sub> – 1.5 | _                    | _                |      |

|     |   | 3 V, $I_{Load} = -2 \text{ mA}$               |                 | V <sub>DD</sub> – 1.5 | _                    | _                |      |

|     |   | 5 V, $I_{Load} = -2 \text{ mA}$               |                 | $V_{DD} - 0.8$        |                      | _                |      |

| 2   | Р | 3 V, $I_{Load} = -1 \text{ mA}$               | V               | $V_{DD} - 0.8$        | _                    | _                | V    |

|     | ' | Output high voltage — High drive (PTxDSn = 1) | V <sub>OH</sub> |                       |                      |                  | V    |

|     |   | 5 V, $I_{Load} = -15 \text{ mA}$              |                 | V <sub>DD</sub> – 1.5 | _                    | _                |      |

|     |   | 3 V, $I_{Load} = -8 \text{ mA}$               |                 | V <sub>DD</sub> – 1.5 |                      | _                |      |

|     |   | 5 V, $I_{Load} = -8 \text{ mA}$               |                 | $V_{DD} - 0.8$        | _                    | _<br>_<br>_<br>_ |      |

|     |   | 3 V, $I_{Load} = -4 \text{ mA}$               |                 | $V_{DD}^{-1} - 0.8$   | _                    | _                |      |

### **Table 10. DC Characteristics (continued)**

| Num | С | Parameter                                                                                                                      | Symbol          | Min    | Typical <sup>1</sup> | Max       | Unit |

|-----|---|--------------------------------------------------------------------------------------------------------------------------------|-----------------|--------|----------------------|-----------|------|

|     |   | DC injection current <sup>5 6 7 8</sup> (single pin limit)  V <sub>IN</sub> >V <sub>DD</sub> V <sub>IN</sub> <v<sub>SS</v<sub> | . ⊢             | 0<br>0 | _                    | 2<br>-0.2 | mA   |

| 22  |   | DC injection current (Total MCU limit, includes sum of all stressed pins) $ \frac{V_{IN}>V_{DD}}{V_{IN}< V_{SS}} $             | I <sub>IC</sub> | 0<br>0 |                      | 2         | mA   |

Typical values are based on characterization data at 25°C unless otherwise stated.

- $^{6}\,$  All functional non-supply pins are internally clamped to  $V_{SS}$  and  $V_{DD}$ .

- Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive and negative clamp voltages, then use the larger of the two values.

- <sup>8</sup> The  $\overline{\text{RESET}}$  pin does not have a clamp diode to  $V_{DD}$ . Do not drive this pin above  $V_{DD}$ .

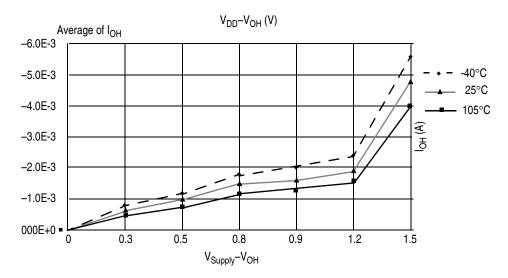

Figure 5. Typical I<sub>OH</sub> vs. V<sub>DD</sub>-V<sub>OH</sub> at V<sub>DD</sub> = 3 V (Low Drive, PTxDSn = 0)

<sup>&</sup>lt;sup>2</sup> Measured with  $V_{In} = V_{DD}$  or  $V_{SS}$ .

$<sup>^{3}</sup>$  Measured with  $V_{In} = V_{SS}$ .

<sup>&</sup>lt;sup>4</sup> Measured with  $V_{In} = V_{DD}$ .

Power supply must maintain regulation within operating V<sub>DD</sub> range during instantaneous and operating maximum current conditions. If positive injection current (V<sub>In</sub> > V<sub>DD</sub>) is greater than I<sub>DD</sub>, the injection current may flow out of V<sub>DD</sub> and could result in external power supply going out of regulation. Ensure external V<sub>DD</sub> load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if clock rate is very low (which would reduce overall power consumption).

**Table 11. Supply Current Characteristics (continued)**

| Num | С | Parameter                                                                        | Symbol                | V <sub>DD</sub> (V) | Typical <sup>1</sup> | Max <sup>2</sup>  | Unit   |

|-----|---|----------------------------------------------------------------------------------|-----------------------|---------------------|----------------------|-------------------|--------|

| 5   | С | Wait mode supply <sup>3</sup> current measured at                                |                       | 5                   | 1.3                  | 2                 | - mA   |

| 3   |   | (CPU clock = 2 MHz, f <sub>Bus</sub> = 1 MHz)                                    |                       | 3                   | 1.29                 | 2                 | ША     |

| 6   | С | Wait mode supply <sup>3</sup> current measured at                                | WI <sub>DD</sub>      | 5                   | 5.11                 | 8                 | mA     |

|     |   | (CPU clock = 16 MHz, f <sub>Bus</sub> = 8 MHz)                                   |                       | 3                   | 5.1                  | 8                 | 1117   |

| 7   | С | Wait mode supply <sup>3</sup> current measured at                                |                       | 5                   | 15.24                | 25                | mA     |

| ,   |   | (CPU clock = 50 MHz, f <sub>Bus</sub> = 25 MHz)                                  |                       | 3                   | 15.2                 | 25                | 1117 ( |

| 8   | С | Stop2 mode supply current  -40 °C  25 °C  120 °C                                 | S2I <sub>DD</sub>     | 5                   | 1.40                 | 2.5<br>2.5<br>200 | μА     |

| ŭ   |   | –40 °C<br>25 °C<br>120 °C                                                        | OZ. DD                | 3                   | 1.16                 | 2.5<br>2.5<br>200 | μА     |

| 9   | С | Stop3 mode supply current  -40 °C 25 °C 120 °C                                   | S3I <sub>DD</sub>     | 5                   | 1.60                 | 2.5<br>2.5<br>220 | μА     |

|     |   | –40 °C<br>25 °C<br>120 °C                                                        | DD                    | 3                   | 1.35                 | 2.5<br>2.5<br>220 | μΑ     |

| 10  | С | RTI adder to stop2 or stop3 <sup>3</sup> , 25 °C                                 | S23I <sub>DDRTI</sub> | 5                   | 300                  |                   | nA     |

|     |   | n i addel to stope of stope , 25 C                                               | OZOIDDRTI             | 3                   | 300                  |                   | nA     |

| 11  | С | Adder to stop3 for oscillator enabled <sup>4</sup> (ERCLKEN =1 and EREFSTEN = 1) | S3I <sub>DDOSC</sub>  | 5, 3                | 5                    |                   | μА     |

<sup>&</sup>lt;sup>1</sup> Typicals are measured at 25 °C.

<sup>&</sup>lt;sup>2</sup> Values given here are preliminary estimates prior to completing characterization.

Most customers are expected to find that auto-wakeup from stop2 or stop3 can be used instead of the higher current wait mode

<sup>&</sup>lt;sup>4</sup> Values given under the following conditions: low range operation (RANGE = 0), low power mode (HGO = 0).

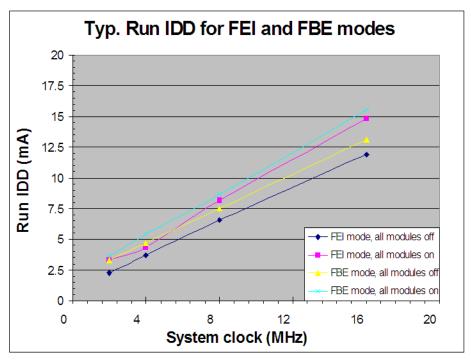

Figure 9. Typical Run  $\rm I_{DD}$  vs. System Clock Freq. for FEI and FBE Modes

## 2.7 Analog Comparator (ACMP) Electricals

**Table 12. Analog Comparator Electrical Specifications**

| Num | С | Rating                                                                                  | Symbol             | Min            | Typical | Max      | Unit |

|-----|---|-----------------------------------------------------------------------------------------|--------------------|----------------|---------|----------|------|

| 1   | _ | Supply voltage                                                                          | $V_{DD}$           | 2.7            | _       | 5.5      | V    |

| 2   | Т | Supply current (active)                                                                 | I <sub>DDAC</sub>  | _              | 20      | 35       | μА   |

| 3   | D | Analog input voltage                                                                    | V <sub>AIN</sub>   | $V_{SS} - 0.3$ | _       | $V_{DD}$ | V    |

| 4   | D | Analog input offset voltage                                                             | $V_{AIO}$          | _              | 20      | 40       | mV   |

| 5   | D | Analog comparator hysteresis                                                            | V <sub>H</sub>     | 3.0            | 6.0     | 20.0     | mV   |

| 6   | D | Analog input leakage current                                                            | I <sub>ALKG</sub>  | _              | _       | 1.0      | μА   |

| 7   | D | Analog comparator initialization delay                                                  | t <sub>AINIT</sub> | _              | _       | 1.0      | μS   |

| 8   | Р | Bandgap voltage reference factory trimmed at $V_{DD} = 5.3248 \text{ V}$ , Temp = 25 °C | $V_{BG}$           | 1.18           | 1.20    | 1.21     | V    |

# 2.10 MCG Specifications

Table 16. MCG Frequency Specifications (Temperature Range = -40 to 105 °C Ambient)

| Num | С | Rati                                                                     | ing                              | Symbol                        | Min    | Typical <sup>1</sup> | Max     | Unit              |

|-----|---|--------------------------------------------------------------------------|----------------------------------|-------------------------------|--------|----------------------|---------|-------------------|

| 1   | С | Internal reference frequency $V_{DD} = 5 \text{ V}$ and temperature      | f <sub>int_ft</sub>              | _                             | 32.768 | _                    | kHz     |                   |

| 2   | С | Average internal reference                                               | frequency — untrimmed            | f <sub>int_ut</sub>           | 31.25  | _                    | 39.0625 | kHz               |

| 3   | Т | Internal reference startup ti                                            | me                               | t <sub>irefst</sub>           |        | 60                   | 100     | μS                |

|     | С | DCO output fraguancy                                                     | Low range (DRS=00)               |                               | 16     | _                    | 20      |                   |

| 4   | С | DCO output frequency range — untrimmed <sup>2</sup>                      | Mid range (DRS=01)               | f <sub>dco_ut</sub>           | 32     | _                    | 40      | MHz               |

|     | С | rango anammoa                                                            | High range (DRS=10)              |                               | 48     | _                    | 60      | ,                 |

|     | Р | DCO output frequency <sup>2</sup>                                        | Low range (DRS=00)               | f <sub>dco_DMX32</sub>        |        | 16.82                | _       | MHz               |

| 5   | Р | reference =32768Hz                                                       | Mid range (DRS=01)               |                               |        | 33.69                | _       |                   |

|     | Р |                                                                          | High range (DRS=10)              |                               | _      | 50.48                | _       |                   |

| 6   | D | Resolution of trimmed DCC voltage and temperature (u                     |                                  | $\Delta f_{dco\_res\_t}$      | _      | ±0.1                 | ±0.2    | %f <sub>dco</sub> |

| 7   | D | Resolution of trimmed DCC voltage and temperature (n                     |                                  | $\Delta f_{dco\_res\_t}$      | _      | ±0.2                 | ±0.4    | %f <sub>dco</sub> |

| 8   | D | Total deviation of trimmed D<br>voltage and temperature                  | CO output frequency over         | $\Delta f_{dco\_t}$           | _      | 0.5<br>-1.0          | ±2      | %f <sub>dco</sub> |

| 9   | D | Total deviation of trimmed Difference to the fixed voltage and temperate |                                  | $\Delta f_{dco\_t}$           | _      | ±0.5                 | ±1      | %f <sub>dco</sub> |

| 10  | D | FLL acquisition time <sup>3</sup>                                        |                                  | t <sub>fll_acquire</sub>      | _      | _                    | 1       | ms                |

| 11  | D | PLL acquisition time <sup>4</sup>                                        |                                  | t <sub>pll_acquire</sub>      | _      | _                    | 1       | ms                |

| 12  | D | Long term jitter of DCO out 2ms interval) <sup>5</sup>                   | put clock (averaged over         | C <sub>Jitter</sub>           | _      | 0.02                 | 0.2     | %f <sub>dco</sub> |

| 13  | D | VCO operating frequency                                                  |                                  | f <sub>vco</sub>              | 7.0    | _                    | 55.0    | MHz               |

| 16  | D | Jitter of PLL output clock m                                             | easured over 625 ns <sup>6</sup> | f <sub>pll_jitter_625ns</sub> | _      | 0.566 <sup>6</sup>   | _       | %f <sub>pll</sub> |

| 17  | D | Lock entry frequency tolera                                              | ince <sup>7</sup>                | D <sub>lock</sub>             | ±1.49  | _                    | ±2.98   | %                 |

| Num | С | Rating                                               | Symbol                | Min                      | Typical <sup>1</sup> | Max                                                        | Unit |

|-----|---|------------------------------------------------------|-----------------------|--------------------------|----------------------|------------------------------------------------------------|------|

| 18  | D | Lock exit frequency tolerance 8                      | D <sub>unl</sub>      | ±4.47                    | _                    | ±5.97                                                      | %    |

| 19  | D | Lock time — FLL                                      | t <sub>fll_lock</sub> | _                        |                      | t <sub>fll_acquire+</sub><br>1075(1/ <sup>f</sup> int_t)   | S    |

| 20  | D | Lock time — PLL                                      | t <sub>pll_lock</sub> | _                        | _                    | t <sub>pll_acquire+</sub><br>1075(1/ <sup>f</sup> pll_ref) | s    |

| 21  | D | Loss of external clock minimum frequency — RANGE = 0 | f <sub>loc_low</sub>  | (3/5) × f <sub>int</sub> | _                    | _                                                          | kHz  |

<sup>&</sup>lt;sup>1</sup> Data in Typical column was characterized at 5.0 V, 25 °C or is typical recommended value.

- <sup>4</sup> This specification applies when the PLL VCO divider or reference divider is changed, or changing from PLL disabled (BLPE, BLPI) to PLL enabled (PBE, PEE). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

- Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum f<sub>BUS</sub>. Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise injected into the FLL circuitry via V<sub>DD</sub> and V<sub>SS</sub> and variation in crystal oscillator frequency increase the C<sub>Jitter</sub> percentage for a given interval.

- 625 ns represents 5 time quanta for CAN applications, under worst case conditions of 8 MHz CAN bus clock, 1 Mbps CAN bus speed, and 8 time quanta per bit for bit time settings. 5 time quanta is the minimum time between a synchronization edge and the sample point of a bit using 8 time quanta per bit.

- Below D<sub>lock</sub> minimum, the MCG enters lock. Above D<sub>lock</sub> maximum, the MCG will not enter lock. But if the MCG is already in lock, then the MCG may stay in lock.

- Below D<sub>unl</sub> minimum, the MCG will not exit lock if already in lock. Above D<sub>unl</sub> maximum, the MCG is guaranteed to exit lock.

## 2.11 AC Characteristics

This section describes ac timing characteristics for each peripheral system.

<sup>&</sup>lt;sup>2</sup> The resulting bus clock frequency must not exceed the maximum specified bus clock frequency of the device.

This specification applies when the FLL reference source or reference divider is changed, trim value changed or changing from FLL disabled (BLPE, BLPI) to FLL enabled (FEI, FEE, FBE, FBI). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

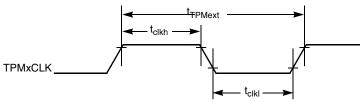

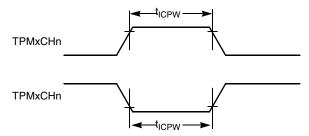

## 2.11.2 Timer (TPM/FTM) Module Timing

Synchronizer circuits determine the shortest input pulses that can be recognized or the fastest clock that can be used as the optional external source to the timer counter. These synchronizers operate from the current bus rate clock.

| NUM | С | Function                  | Symbol              | Min | Max                 | Unit             |

|-----|---|---------------------------|---------------------|-----|---------------------|------------------|

| 1   | _ | External clock frequency  | f <sub>TPMext</sub> | DC  | f <sub>Bus</sub> /4 | MHz              |

| 2   | _ | External clock period     | t <sub>TPMext</sub> | 4   | _                   | t <sub>cyc</sub> |

| 3   | D | External clock high time  | t <sub>clkh</sub>   | 1.5 | _                   | t <sub>cyc</sub> |

| 4   | D | External clock low time   | t <sub>clkl</sub>   | 1.5 | _                   | t <sub>cyc</sub> |

| 5   | D | Input capture pulse width | t <sub>ICPW</sub>   | 1.5 | _                   | t <sub>cyc</sub> |

Table 18. TPM/FTM Input Timing

Figure 13. Timer External Clock

Figure 14. Timer Input Capture Pulse

### 2.11.3 MSCAN

Table 19. MSCAN Wake-Up Pulse Characteristics

| Num | С | Parameter                             | Symbol           | Min | Typical <sup>1</sup> | Max | Unit |

|-----|---|---------------------------------------|------------------|-----|----------------------|-----|------|

| 1   | D | MSCAN wake-up dominant pulse filtered | t <sub>WUP</sub> | _   | _                    | 2   | μS   |

| 2   | D | MSCAN wake-up dominant pulse pass     | t <sub>WUP</sub> | 5   | _                    | 5   | μS   |

<sup>&</sup>lt;sup>1</sup> Typical values are based on characterization data at  $V_{DD}$  = 5.0 V, 25 °C unless otherwise stated.

Freescale Semiconductor 35

MCF51AC256 ColdFire Microcontroller Data Sheet, Rev.7

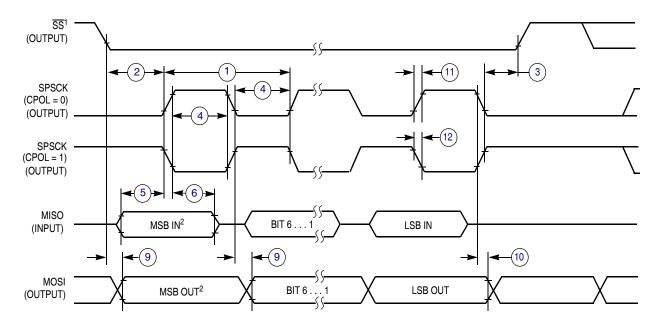

### NOTES:

- 1.  $\overline{SS}$  output mode (DDS7 = 1, SSOE = 1).

- 2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

Figure 15. SPI Master Timing (CPHA = 0)

### NOTES:

- 1.  $\overline{SS}$  output mode (DDS7 = 1, SSOE = 1).

- 2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

Figure 16. SPI Master Timing (CPHA =1)

1. Not defined but normally MSB of character just received

Figure 17. SPI Slave Timing (CPHA = 0)

1. Not defined but normally LSB of character just received

Figure 18. SPI Slave Timing (CPHA = 1)

## 2.13 Flash Specifications

This section provides details about program/erase times and program-erase endurance for the Flash memory.

Program and erase operations do not require any special power sources other than the normal  $V_{DD}$  supply. For more detailed information about program/erase operations, see Chapter 4, "Memory."

| Num | С | Characteristic                                                                     | Symbol                  | Min         | Typical <sup>1</sup> | Max  | Unit              |

|-----|---|------------------------------------------------------------------------------------|-------------------------|-------------|----------------------|------|-------------------|

| 1   | _ | Supply voltage for program/erase                                                   | V <sub>prog/erase</sub> | 2.7 — 5.5   |                      | V    |                   |

| 2   | _ | Supply voltage for read operation                                                  | V <sub>Read</sub>       | 2.7         | _                    | 5.5  | V                 |

| 3   |   | Internal FCLK frequency <sup>2</sup>                                               | f <sub>FCLK</sub>       | 150         | _                    | 200  | kHz               |

| 4   |   | Internal FCLK period (1/FCLK)                                                      | t <sub>Fcyc</sub>       | 5           | _                    | 6.67 | μS                |

| 5   |   | Byte program time (random location) <sup>2</sup>                                   | t <sub>prog</sub>       | 9           |                      |      | t <sub>Fcyc</sub> |

| 6   |   | Byte program time (burst mode) <sup>2</sup>                                        | t <sub>Burst</sub>      | 4           |                      |      | t <sub>Fcyc</sub> |

| 7   |   | Page erase time <sup>3</sup>                                                       | t <sub>Page</sub>       | 4000        |                      |      | t <sub>Fcyc</sub> |

| 8   |   | Mass erase time <sup>2</sup>                                                       | t <sub>Mass</sub>       | 20,000      |                      |      | t <sub>Fcyc</sub> |

| 9   | О | Program/erase endurance <sup>4</sup> $T_L$ to $T_H = -40$ °C to 105 °C $T = 25$ °C | _                       | 10,000<br>— | <br>100,000          |      | cycles            |

| 10  | С | Data retention <sup>5</sup>                                                        | t <sub>D_ret</sub>      | 15          | 100                  | _    | years             |

**Table 21. Flash Characteristics**

### 2.14 EMC Performance

Electromagnetic compatibility (EMC) performance is highly dependant on the environment in which the MCU resides. Board design and layout, circuit topology choices, location and characteristics of external components as well as MCU software operation all play a significant role in EMC performance. The system designer should consult Freescale applications notes such as AN2321, AN1050, AN1263, AN2764, and AN1259 for advice and guidance specifically targeted at optimizing EMC performance.

### 2.14.1 Radiated Emissions

Microcontroller radiated RF emissions are measured from 150 kHz to 1 GHz using the TEM/GTEM Cell method in accordance with the IEC 61967-2 and SAE J1752/3 standards. The measurement is performed with the microcontroller installed on a custom EMC evaluation board while running specialized EMC test software. The radiated emissions from the microcontroller are measured in a TEM cell in two package orientations (North and East). For more detailed information concerning the evaluation results, conditions and setup, please refer to the EMC Evaluation Report for this device.

<sup>&</sup>lt;sup>1</sup> Typical values are based on characterization data at V<sub>DD</sub> = 5.0 V, 25 °C unless otherwise stated.

<sup>&</sup>lt;sup>2</sup> The frequency of this clock is controlled by a software setting.

These values are hardware state machine controlled. User code does not need to count cycles. This information supplied for calculating approximate time to program and erase.

Typical endurance for flash was evaluated for this product family on the 9S12Dx64. For additional information on how Freescale Semiconductor defines typical endurance, please refer to Engineering Bulletin EB619/D, Typical Endurance for Nonvolatile Memory.

Typical data retention values are based on intrinsic capability of the technology measured at high temperature and de-rated to 25°C using the Arrhenius equation. For additional information on how Freescale Semiconductor defines typical data retention, please refer to Engineering Bulletin EB618/D, Typical Data Retention for Nonvolatile Memory.

# 4 Revision History

## **Table 23. Revision History**

| Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | Initial published                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2        | Updated ADC channels, Item 1, 4-5 on Table 2.10                                                                                                                                                                                                                                                                                                                                                                                   |

| 3        | Completed all the TBDs. Changed RTC to RTI in Figure 1. Corrected the block diagram. Changed $V_{DDAD}$ to $V_{DDA}$ , $V_{SSAD}$ to $V_{SSA}$ . Added charge device model data and removed machine data in Table 8. Updated the specifications of $V_{LVDH}$ , $V_{LVDL}$ , $V_{LVWH}$ and $V_{LVWL}$ in Table 10. Updated $S2I_{DD}$ , $S3I_{DD}$ in Table 11. Added C column in Table 14. Updated $f_{dco_DMX32}$ in Table 16. |

| 4        | Corrected the expansion of SPI to serial peripheral interface.                                                                                                                                                                                                                                                                                                                                                                    |

| 5        | Updated V <sub>LVDL</sub> in the Table 10.<br>Updated RI <sub>DD</sub> in the Table 11.                                                                                                                                                                                                                                                                                                                                           |

| 6        | Updated V <sub>LVDH</sub> , V <sub>LVDL</sub> , V <sub>LVWH</sub> and V <sub>LVWL</sub> in the Table 10.<br>Added LPO on the Figure 1 and LPO features in the Section 1.3, "Features."                                                                                                                                                                                                                                            |

| 7        | Added 44-pin LQFP package information for AC256 and AC128.                                                                                                                                                                                                                                                                                                                                                                        |