Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | Coldfire V1                                                             |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 50MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                              |

| Peripherals                | LVD, PWM, WDT                                                           |

| Number of I/O              | 69                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 32K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 24x12b                                                              |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 80-LQFP                                                                 |

| Supplier Device Package    | 80-LQFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcf51ac256bclke |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.3.1 Feature List

- 32-bit Version 1 ColdFire® central processor unit (CPU)

- Up to 50.33 MHz at 2.7 V 5.5 V

- Provide 0.94 Dhrystone 2.1 DMIPS per MHz performance when running from internal RAM (0.76 DMIPS per MHz when running from flash)

- Implements instruction set revision C (ISA\_C)

- On-chip memory

- Up to 256 KB flash memory read/program/erase over full operating voltage and temperature

- Up to 32 KB static random access memory (SRAM)

- Security circuitry to prevent unauthorized access to SRAM and flash contents

- Power-Saving Modes

- Three low-power stop plus wait modes

- Peripheral clock enable register can disable clocks to unused modules, reducing currents; allows clocks to remain enabled to specific peripherals in stop3 mode

- System protection features

- Watchdog computer operating properly (COP) reset with options to run from independent LPO clock or bus clock

- Low-voltage detection with reset or interrupt

- Illegal opcode and illegal address detection with programmable reset or exception response

- Flash block protection

- Debug support

- Single-wire background debug interface

- Real-time debug support, with 6 hardware breakpoints (4 PC, 1 address pair and 1 data) that can be configured into a 1- or 2-level trigger

- On-chip trace buffer provides programmable start/stop recording conditions plus support for continuous or PC-profiling modes

- Support for real-time program (and optional partial data) trace using the debug visibility bus

- V1 ColdFire interrupt controller (CF1\_INTC)

- Support of 40 peripheral I/O interrupt requests plus seven software (one per level) interrupt requests

- Fixed association between interrupt request source and level plus priority, up to two requests can be remapped to the highest maskable level + priority

- Unique vector number for each interrupt source

- Support for service routine interrupt acknowledge (software IACK) read cycles for improved system performance

- Multipurpose clock generator (MCG)

- Oscillator (XOSC); loop-control Pierce oscillator; crystal or ceramic resonator range of 31.25 kHz to 38.4 kHz or 1 MHz to 16 MHz

- LPO clock as an optional independent clock source for COP and RTI

- FLL/PLL controlled by internal or external reference

- Trimmable internal reference allows 0.2% resolution and 2% deviation

- Analog-to-digital converter (ADC)

- 24 analog inputs with 12 bits resolution

- Output formatted in 12-, 10- or 8-bit right-justified format

- Single or continuous conversion (automatic return to idle after single conversion)

- Operation in low-power modes for lower noise operation

- Asynchronous clock source for lower noise operation

- Automatic compare with interrupt for less-than, or greater-than or equal-to, programmable value

- On-chip temperature sensor

- Flexible timer/pulse-width modulators (FTM)

- 16-bit Free-running counter or a counter with initial and final value. The counting can be up and unsigned, up and signed, or up-down and unsigned

- Up to 6 channels, and each channel can be configured for input capture, output compare or edge-aligned PWM mode, all channels can be configured for center-aligned PWM mode

- Channels can operate as pairs with equal outputs, pairs with complimentary outputs or independent channels (with independent outputs)

- Each pair of channels can be combined to generate a PWM signal (with independent control of both edges of PWM signal)

- Deadtime insertion is available for each complementary pair

- The load of the FTM registers which have write buffer can be synchronized; write protection for critical registers

- Generation of the triggers to ADC (hardware trigger)

- A fault input for global fault control

- Backwards compatible with TPM

- Timer/pulse width modulator (TPM)

- 16-bit free-running or modulo up/down count operation

- Two channels, each channel may be input capture, output compare, or edge-aligned PWM

- One interrupt per channel plus terminal count interrupt

- Cyclic redundancy check (CRC) generator

- High speed hardware CRC generator circuit using 16-bit shift register

- CRC16-CCITT compliancy with  $x^{16} + x^{12} + x^5 + 1$  polynomial

- Error detection for all single, double, odd, and most multi-bit errors

- Programmable initial seed value

- Analog comparators (ACMP)

- Full rail to rail supply operation

- Selectable interrupt on rising edge, falling edge, or either rising or falling edges of comparator output

- Option to compare to fixed internal bandgap reference voltage

- Option to allow comparator output to be visible on a pin, ACMPxO

- Inter-integrated circuit (IIC)

- Compatible with IIC bus standard

- Multi-master operation

- Software programmable for one of 64 different serial clock frequencies

- Interrupt driven byte-by-byte data transfer

- Arbitration lost interrupt with automatic mode switching from master to slave

- Calling address identification interrupt

- Bus busy detection

- 10-bit address extension

- Controller area network (CAN)

- Implementation of the CAN protocol Version 2.0A/B

- Standard and extended data frames

- Zero to eight bytes data length

- Programmable bit rate up to 1 Mbps

- Support for remote frames

- Five receive buffers with FIFO storage scheme

- Three transmit buffers with internal prioritization using a "local priority" concept

- Flexible maskable identifier filter supports two full-size (32-bit) extended identifier filters, four 16-bit filters, or eight 8-bit filters

- Programmable wakeup functionality with integrated low-pass filter

- Programmable loopback mode supports self-test operation

- Programmable listen-only mode for monitoring of CAN bus

- Programmable bus-off recovery functionality

- Separate signalling and interrupt capabilities for all CAN receiver and transmitter error states (warning, error passive, bus-off)

- Internal timer for time-stamping of received and transmitted messages

- Serial communications interfaces (SCI)

- Full-duplex, standard non-return-to-zero (NRZ) format

- Double-buffered transmitter and receiver with separate enables

- Programmable baud rates (13-bit modulo divider)

- Interrupt-driven or polled operation

- Hardware parity generation and checking

- Programmable 8-bit or 9-bit character length

- Receiver wakeup by idle-line or address-mark

- Optional 13-bit break character generation / 11-bit break character detection

- Selectable transmitter output polarity

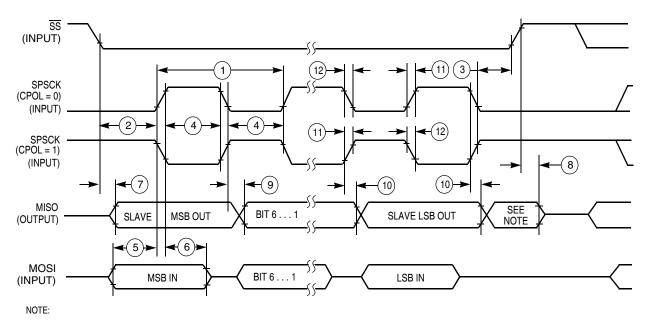

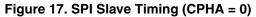

- Serial peripheral interfaces (SPI)

- Master or slave mode operation

- Full-duplex or single-wire bidirectional option

- Programmable transmit bit rate

- Double-buffered transmit and receive

- Serial clock phase and polarity options

- Slave select output

- Selectable MSB-first or LSB-first shifting

- 16-bit and FIFO operations in SPI2

- Input/Output

- 69 GPIOs

- 8 keyboard interrupt pins with selectable polarity

- Hysteresis and configurable pull-up device on all input pins; Configurable slew rate and drive strength on all output pins

- 16-bits Rapid GPIO pins connected to the processor's local 32-bit platform bus with set, clear, and faster toggle functionality

### 1.4 Part Numbers

Table 3. Orderable Part Number Summary

| Freescale Part Number | Description                                     | Flash / SRAM<br>(Kbytes) | Package | Temperature    |

|-----------------------|-------------------------------------------------|--------------------------|---------|----------------|

| MCF51AC256AVFUE       | MCF51AC256 ColdFire Microcontroller with CAN    | 256 / 32                 | 64 QFP  | –40°C to 105°C |

| MCF51AC256BVFUE       | MCF51AC256 ColdFire Microcontroller without CAN | 256 / 32                 | 64 QFP  | –40°C to 105°C |

| MCF51AC256AVLKE       | MCF51AC256 ColdFire Microcontroller with CAN    | 256 / 32                 | 80 LQFP | –40°C to 105°C |

| MCF51AC256BVLKE       | MCF51AC256 ColdFire Microcontroller without CAN | 256 / 32                 | 80 LQFP | –40°C to 105°C |

| MCF51AC256AVPUE       | MCF51AC256 ColdFire Microcontroller with CAN    | 256 / 32                 | 64 LQFP | –40°C to 105°C |

| MCF51AC256BVPUE       | MCF51AC256 ColdFire Microcontroller without CAN | 256 / 32                 | 64 LQFP | –40°C to 105°C |

| MCF51AC128AVFUE       | MCF51AC128 ColdFire Microcontroller with CAN    | 128 / 32                 | 64 QFP  | –40°C to 105°C |

| MCF51AC128CVFUE       | MCF51AC128 ColdFire Microcontroller without CAN | 128 / 16                 | 64 QFP  | –40°C to 105°C |

| MCF51AC128AVLKE       | MCF51AC128 ColdFire Microcontroller with CAN    | 128 / 32                 | 80 LQFP | –40°C to 105°C |

| MCF51AC128CVLKE       | MCF51AC128 ColdFire Microcontroller without CAN | 128 / 16                 | 80 LQFP | –40°C to 105°C |

| MCF51AC128AVPUE       | MCF51AC128 ColdFire Microcontroller with CAN    | 128 / 32                 | 64 LQFP | –40°C to 105°C |

| MCF51AC128CVPUE       | MCF51AC128 ColdFire Microcontroller without CAN | 128 / 16                 | 64 LQFP | –40°C to 105°C |

| MCF51AC256ACFUE       | MCF51AC256 ColdFire Microcontroller with CAN    | 256 / 32                 | 64 QFP  | –40°C to 85°C  |

| MCF51AC256BCFUE       | MCF51AC256 ColdFire Microcontroller without CAN | 256 / 32                 | 64 QFP  | –40°C to 85°C  |

| MCF51AC256ACLKE       | MCF51AC256 ColdFire Microcontroller with CAN    | 256 / 32                 | 80 LQFP | –40°C to 85°C  |

| MCF51AC256BCLKE       | MCF51AC256 ColdFire Microcontroller without CAN | 256 / 32                 | 80 LQFP | –40°C to 85°C  |

| MCF51AC256ACPUE | MCF51AC256 ColdFire Microcontroller with CAN    | 256 / 32 | 64 LQFP | –40°C to 85°C  |

|-----------------|-------------------------------------------------|----------|---------|----------------|

| MCF51AC256BCPUE | MCF51AC256 ColdFire Microcontroller without CAN | 256 / 32 | 64 LQFP | –40°C to 85°C  |

| MCF51AC256BCFGE | MCF51AC256 ColdFire Microcontroller without CAN | 256/32   | 44 LQFP | –40°C to 85°C  |

| MCF51AC128ACFUE | MCF51AC128 ColdFire Microcontroller with CAN    | 128 / 32 | 64 QFP  | –40°C to 85°C  |

| MCF51AC128CCFUE | MCF51AC128 ColdFire Microcontroller without CAN | 128 / 16 | 64 QFP  | –40°C to 85°C  |

| MCF51AC128ACLKE | MCF51AC128 ColdFire Microcontroller with CAN    | 128 / 32 | 80 LQFP | –40°C to 85°C  |

| MCF51AC128CCLKE | MCF51AC128 ColdFire Microcontroller without CAN | 128 / 16 | 80 LQFP | –40°C to 85°CC |

| MCF51AC128ACPUE | MCF51AC128 ColdFire Microcontroller with CAN    | 128 / 32 | 64 LQFP | –40°C to 85°C  |

| MCF51AC128CCPUE | MCF51AC128 ColdFire Microcontroller without CAN | 128 / 16 | 64 LQFP | –40°C to 85°C  |

| MCF51AC128CCFGE | MCF51AC128 ColdFire Microcontroller without CAN | 128 / 16 | 44 LQFP | –40°C to 85°C  |

### Table 3. Orderable Part Number Summary

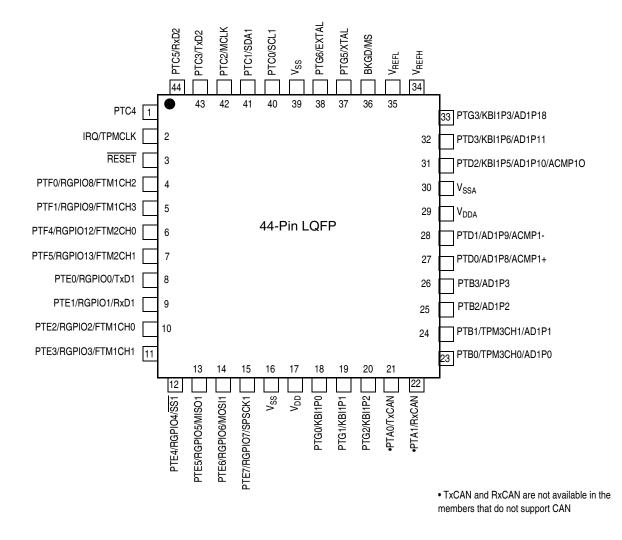

Figure 4. MCF51AC256 Series ColdFire Microcontroller 44-Pin LQFP

Table 4 shows the package pin assignments.

| Pin Number |    |    | Lowest < Priority> Highest |                     |         |       |  |

|------------|----|----|----------------------------|---------------------|---------|-------|--|

| 80         | 64 | 44 | Port Pin                   | Alt 1               | Alt 2   | Alt 3 |  |

| 1          | 1  | 1  | PTC4                       | SS2                 |         |       |  |

| 2          | 2  | 2  | IRQ                        | TPMCLK <sup>1</sup> |         |       |  |

| 3          | 3  | 3  | RESET                      |                     |         |       |  |

| 4          | 4  | 4  | PTF0                       | RGPIO8              | FTM1CH2 |       |  |

| 5          | 5  | 5  | PTF1                       | RGPIO9              | FTM1CH3 |       |  |

| 6          | 6  | _  | PTF2                       | RGPIO10             | FTM1CH4 |       |  |

| 7          | 7  |    | PTF3                       | RGPI011             | FTM1CH5 |       |  |

Table 4. Pin Availability by Package Pin-Count

This section contains electrical specification tables and reference timing diagrams for the MCF51AC256 microcontroller, including detailed information on power considerations, DC/AC electrical characteristics, and AC timing specifications.

The electrical specifications are preliminary and are from previous designs or design simulations. These specifications may not be fully tested or guaranteed at this early stage of the product life cycle. These specifications will, however, be met for production silicon. Finalized specifications will be published after complete characterization and device qualifications have been completed.

### NOTE

The parameters specified in this data sheet supersede any values found in the module specifications.

## 2.1 Parameter Classification

The electrical parameters shown in this supplement are guaranteed by various methods. To give the customer a better understanding the following classification is used and the parameters are tagged accordingly in the tables where appropriate:

### Table 5. Parameter Classifications

| Р | Those parameters are guaranteed during production testing on each individual device.                                                                                                                                   |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| с | Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations.                                                                              |

| т | Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category. |

| D | Those parameters are derived mainly from simulations.                                                                                                                                                                  |

### NOTE

The classification is shown in the column labeled "C" in the parameter tables where appropriate.

## 2.2 Absolute Maximum Ratings

Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the limits specified in Table 6 may affect device reliability or cause permanent damage to the device. For functional operating conditions, refer to the remaining tables in this section.

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for instance, either  $V_{SS}$  or  $V_{DD}$ ).

| Rating                                                                                                                  | Symbol           | Value                         | Unit |

|-------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------|------|

| Supply voltage                                                                                                          | V <sub>DD</sub>  | -0.3 to 5.8                   | V    |

| Input voltage                                                                                                           | V <sub>In</sub>  | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Instantaneous maximum current<br>Single pin limit (applies to all port pins) <sup>1</sup> , <sup>2</sup> , <sup>3</sup> | ۱ <sub>D</sub>   | ±25                           | mA   |

| Maximum current into V <sub>DD</sub>                                                                                    | I <sub>DD</sub>  | 120                           | mA   |

| Storage temperature                                                                                                     | T <sub>stg</sub> | -55 to 150                    | °C   |

#### Table 6. Absolute Maximum Ratings

<sup>1</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive (V<sub>DD</sub>) and negative (V<sub>SS</sub>) clamp voltages, then use the larger of the two resistance values.

$^2~$  All functional non-supply pins are internally clamped to  $V_{SS}$  and  $V_{DD}$

<sup>3</sup> Power supply must maintain regulation within operating V<sub>DD</sub> range during instantaneous and operating maximum current conditions. If positive injection current (V<sub>In</sub> > V<sub>DD</sub>) is greater than I<sub>DD</sub>, the injection current may flow out of V<sub>DD</sub> and could result in external power supply going out of regulation. Ensure external V<sub>DD</sub> load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if the clock rate is very low which would reduce overall power consumption.

## 2.3 Thermal Characteristics

This section provides information about operating temperature range, power dissipation, and package thermal resistance. Power dissipation on I/O pins is usually small compared to the power dissipation in on-chip logic and it is user-determined rather than being controlled by the MCU design. In order to take  $P_{I/O}$  into account in power calculations, determine the difference between actual pin voltage and  $V_{SS}$  or  $V_{DD}$  and multiply by the pin current for each I/O pin. Except in cases of unusually high pin current (heavy loads), the difference between pin voltage and  $V_{SS}$  or  $V_{DD}$  will be very small.

| Rating                                   |                          | Symbol         | Value                | Unit |

|------------------------------------------|--------------------------|----------------|----------------------|------|

| Operating temperature range (packaged)   |                          | T <sub>A</sub> | -40 to 105           | °C   |

| Maximum junction temperature             |                          | Т <sub>Ј</sub> | 150                  | °C   |

| Thermal resistance 1,2,3,4               |                          |                |                      |      |

| 80-pin LQFP<br>64-pin LQFP<br>64-pin QFP | 1s<br>2s2p<br>1s<br>2s2p | θյΑ            | 51<br>38<br>59<br>41 | °C/W |

| 44-pin LQFP                              | 1s<br>2s2p<br>1s<br>2s2p |                | 50<br>36<br>67<br>45 |      |

**Table 7. Thermal Characteristics**

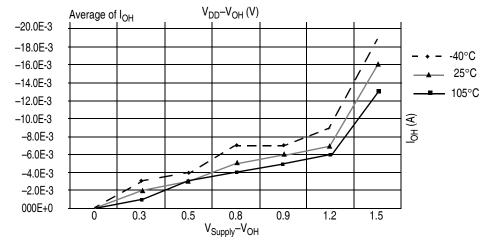

Figure 6. Typical  $I_{OH}$  vs.  $V_{DD}$ - $V_{OH}$  at  $V_{DD}$  = 3 V (High Drive, PTxDSn = 1)

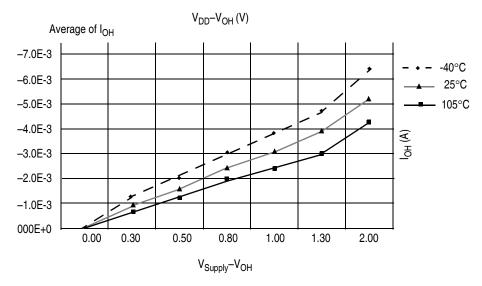

Figure 7. Typical  $I_{OH}$  vs.  $V_{DD}$ - $V_{OH}$  at  $V_{DD}$  = 5 V (Low Drive, PTxDSn = 0)

Figure 9. Typical Run  $I_{\text{DD}}$  vs. System Clock Freq. for FEI and FBE Modes

## 2.7 Analog Comparator (ACMP) Electricals

### Table 12. Analog Comparator Electrical Specifications

| Num | С | Rating                                                                         | Symbol             | Min                   | Typical | Max             | Unit |

|-----|---|--------------------------------------------------------------------------------|--------------------|-----------------------|---------|-----------------|------|

| 1   |   | Supply voltage                                                                 | V <sub>DD</sub>    | 2.7                   |         | 5.5             | V    |

| 2   | Т | Supply current (active)                                                        | I <sub>DDAC</sub>  | —                     | 20      | 35              | μA   |

| 3   | D | Analog input voltage                                                           | V <sub>AIN</sub>   | V <sub>SS</sub> – 0.3 | _       | V <sub>DD</sub> | V    |

| 4   | D | Analog input offset voltage                                                    | V <sub>AIO</sub>   | —                     | 20      | 40              | mV   |

| 5   | D | Analog comparator hysteresis                                                   | V <sub>H</sub>     | 3.0                   | 6.0     | 20.0            | mV   |

| 6   | D | Analog input leakage current                                                   | I <sub>ALKG</sub>  | _                     | _       | 1.0             | μA   |

| 7   | D | Analog comparator initialization delay                                         | t <sub>AINIT</sub> | —                     | _       | 1.0             | μs   |

| 8   | Ρ | Bandgap voltage reference factory trimmed at $V_{DD}$ = 5.3248 V, Temp = 25 °C | V <sub>BG</sub>    | 1.18                  | 1.20    | 1.21            | V    |

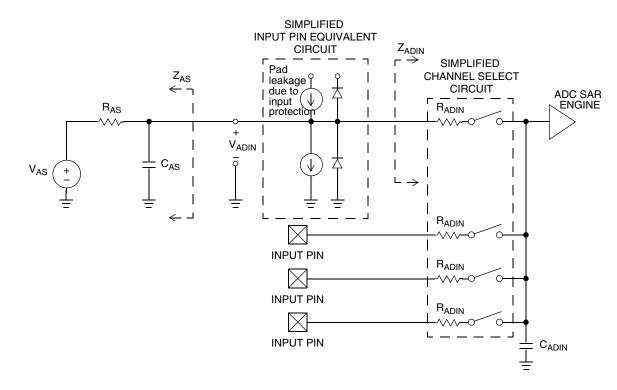

## 2.8 ADC Characteristics

| Num | С                | Characteristic                                                                 | Conditions                                                                     | Symb              | Min               | Typical <sup>1</sup> | Max              | Unit | Comment            |

|-----|------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------------------|-------------------|----------------------|------------------|------|--------------------|

|     | D                |                                                                                | Absolute                                                                       | V <sub>DDA</sub>  | 2.7               |                      | 5.5              | V    |                    |

| 1   | D Supply voltage | Delta to V <sub>DD</sub><br>(V <sub>DD</sub> – V <sub>DDA</sub> ) <sup>2</sup> | $\Delta V_{DDA}$                                                               | -100              | 0                 | 100                  | mV               |      |                    |

| 2   | D                | Ground voltage                                                                 | Delta to V <sub>SS</sub><br>(V <sub>SS</sub> – V <sub>SSA</sub> ) <sup>2</sup> | $\Delta V_{SSA}$  | -100              | 0                    | 100              | mV   |                    |

| 3   | D                | Reference<br>voltage high                                                      |                                                                                | V <sub>REFH</sub> | 2.7               | V <sub>DDA</sub>     | V <sub>DDA</sub> | v    |                    |

| 4   | D                | Reference<br>voltage low                                                       |                                                                                | V <sub>REFL</sub> | V <sub>SSA</sub>  | V <sub>SSA</sub>     | V <sub>SSA</sub> | v    |                    |

| 5   | D                | Input voltage                                                                  |                                                                                | V <sub>ADIN</sub> | V <sub>REFL</sub> | _                    | $V_{REFH}$       | V    |                    |

| 6   | С                | Input<br>capacitance                                                           |                                                                                | C <sub>ADIN</sub> | _                 | 4.5                  | 5.5              | pF   |                    |

| 7   | С                | Input<br>resistance                                                            |                                                                                | R <sub>ADIN</sub> | _                 | 3                    | 5                | kΩ   |                    |

|     | С                |                                                                                | 12-bit mode<br>f <sub>ADCK</sub> > 4MHz<br>f <sub>ADCK</sub> < 4MHz            |                   | _                 |                      | 2<br>5           |      |                    |

| 8   | С                | Analog source resistance                                                       | 10-bit mode<br>f <sub>ADCK</sub> > 4MHz<br>f <sub>ADCK</sub> < 4MHz            | R <sub>AS</sub>   | _                 |                      | 5<br>10          | kΩ   | External<br>to MCU |

|     | С                |                                                                                | 8-bit mode (all valid<br>f <sub>ADCK</sub> )                                   |                   | _                 | _                    | 10               |      |                    |

| 9   | D                | ADC conversion                                                                 | High speed<br>(ADLPC = 0)                                                      | f                 | 0.4               | _                    | 8.0              | MHz  |                    |

| 5   | D                | clock<br>frequency                                                             | Low power<br>(ADLPC = 1)                                                       | f <sub>adck</sub> | 0.4               | _                    | 4.0              |      |                    |

<sup>1</sup> Typical values assume V<sub>DDA</sub> = 5.0 V, Temp = 25 °C, f<sub>ADCK</sub> = 1.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

<sup>2</sup> DC potential difference.

Figure 10. ADC Input Impedance Equivalency Diagram

| Num | С | Characteristic                                        | Conditions              | Symb               | Min  | Typical <sup>1</sup> | Max | Unit | Comment              |

|-----|---|-------------------------------------------------------|-------------------------|--------------------|------|----------------------|-----|------|----------------------|

| 1   | т | Supply current<br>ADLPC = 1<br>ADLSMP = 1<br>ADCO = 1 |                         | I <sub>DDA</sub>   | _    | 133                  | _   | μA   |                      |

| 2   | т | Supply current<br>ADLPC = 1<br>ADLSM = 0<br>ADCO = 1  |                         | I <sub>DDA</sub>   | _    | 218                  | _   | μA   |                      |

| 3   | Т | Supply current<br>ADLPC = 0<br>ADLSMP = 1<br>ADCO = 1 |                         | I <sub>DDA</sub>   | _    | 327                  |     | μA   |                      |

| 4   | D | Supply current<br>ADLPC = 0<br>ADLSMP = 0<br>ADCO = 1 |                         | I <sub>DDA</sub>   | _    | 0.582                | 1   | mA   |                      |

| 5   | Т | Supply current                                        | Stop, reset, module off | I <sub>DDA</sub>   | _    | 0.011                | 1   | μA   |                      |

|     |   | ADC                                                   | High speed (ADLPC = 0)  | f <sub>ADACK</sub> | 2    | 3.3                  | 5   |      | t <sub>ADACK</sub> = |

| 6   | P | asynchronous<br>clock source                          | Low power (ADLPC = 1)   |                    | 1.25 | 2                    | 3.3 | MHz  | 1/f <sub>ADACK</sub> |

Table 14. 5 Volt 12-bit ADC Characteristics ( $V_{REFH} = V_{DDA}$ ,  $V_{REFL} = V_{SSA}$ )

| Num | С   | Characteristic                  | Conditions                | Symb                | Min  | Typical <sup>1</sup> | Max  | Unit             | Comment                                 |

|-----|-----|---------------------------------|---------------------------|---------------------|------|----------------------|------|------------------|-----------------------------------------|

|     | _   | Conversion                      | Short sample (ADLSMP = 0) |                     | _    | 20                   |      | ADCK             | See                                     |

| 7   | Р   | time (including<br>sample time) | Long sample (ADLSMP = 1)  | t <sub>ADC</sub>    | _    | 40                   | _    | cycles           | Table 10<br>for                         |

|     | Ŧ   |                                 | Short sample (ADLSMP = 0) |                     | _    | 3.5                  | _    | ADCK             | conversion<br>time                      |

| 8   | Т   | Sample time                     | Long sample (ADLSMP = 1)  | t <sub>ADS</sub>    | _    | 23.5                 | _    | cycles           | variances                               |

|     | Т   | Total                           | 12-bit mode               |                     | _    | ±3.0                 | _    |                  | Includes                                |

| 9   | Р   | unadjusted                      | 10-bit mode               | E <sub>TUE</sub>    |      | ±1                   | ±2.5 | LSB <sup>2</sup> | quantizatio                             |

|     | Т   | error                           | 8-bit mode                |                     | _    | ±0.5                 | ±1.0 |                  | n                                       |

|     | Т   |                                 | 12-bit mode               |                     |      | ±1.75                |      |                  |                                         |

| 10  | Р   | Differential non-linearity      | 10-bit mode <sup>3</sup>  | DNL                 |      | ±0.5                 | ±1.0 | LSB <sup>2</sup> |                                         |

|     | Т   |                                 | 8-bit mode <sup>3</sup>   | •                   |      | ±0.3                 | ±0.5 |                  |                                         |

|     | Т   |                                 | 12-bit mode               |                     |      | ±1.5                 |      |                  |                                         |

| 11  | Т   | Integral<br>non-linearity       | 10-bit mode               | INL                 |      | ±0.5                 | ±1.0 | LSB <sup>2</sup> |                                         |

|     | Т   |                                 | 8-bit mode                | — ±0.3              | ±0.5 |                      |      |                  |                                         |

|     | Т   |                                 | 12-bit mode               | E <sub>ZS</sub>     |      | ±1.5                 |      |                  |                                         |

| 12  | Р   | Zero-scale<br>error             | 10-bit mode               |                     |      | ±0.5                 | ±1.5 | LSB <sup>2</sup> | V <sub>ADIN</sub> =<br>V <sub>SSA</sub> |

|     | Т   |                                 | 8-bit mode                |                     |      | ±0.5                 | ±0.5 |                  | 334                                     |

|     | Т   |                                 | 12-bit mode               |                     |      | ±1                   |      |                  |                                         |

| 13  | Ρ   | Full-scale error                | 10-bit mode               | E <sub>FS</sub>     |      | ±0.5                 | ±1   | LSB <sup>2</sup> | V <sub>ADIN</sub> =<br>V <sub>DDA</sub> |

|     | Т   |                                 | 8-bit mode                |                     |      | ±0.5                 | ±0.5 |                  | DDA                                     |

|     |     |                                 | 12-bit mode               |                     | _    | -1 to 0              | _    |                  |                                         |

| 14  | D   | Quantization<br>error           | 10-bit mode               | EQ                  | _    | —                    | ±0.5 | LSB <sup>2</sup> |                                         |

|     |     |                                 | 8-bit mode                |                     |      | —                    | ±0.5 |                  |                                         |

|     |     |                                 | 12-bit mode               |                     |      | ±1                   |      |                  | Pad                                     |

| 15  | D   | Input leakage<br>error          | 10-bit mode               | EIL                 |      | ±0.2                 | ±2.5 | LSB <sup>2</sup> | leakage <sup>4</sup> *                  |

|     |     |                                 | 8-bit mode                |                     |      | ±0.1                 | ±1   |                  | R <sub>AS</sub>                         |

| 16  | D   | Temp sensor<br>voltage          | 25°C                      | V <sub>TEMP25</sub> | _    | 1.396                | _    | V                |                                         |

| 17  | D   | Temp sensor                     | –40 °C–25 °C              | ~                   | —    | 3.266                | —    | mV/°C            |                                         |

| 17  | ע ו | slope                           | 25 °C–85 °C               | m                   |      | 3.638                |      |                  |                                         |

### Table 14. 5 Volt 12-bit ADC Characteristics ( $V_{REFH} = V_{DDA}$ , $V_{REFL} = V_{SSA}$ ) (continued)

<sup>1</sup> Typical values assume V<sub>DDA</sub> = 5.0 V, Temp = 25 °C, f<sub>ADCK</sub> = 1.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

<sup>2</sup> 1 LSB =  $(V_{\text{REFH}} - V_{\text{REFL}})/2^{\text{N}}$ .

<sup>3</sup> Monotonicity and No-Missing-Codes guaranteed in 10-bit and 8-bit modes

<sup>4</sup> Based on input pad leakage current. Refer to pad electricals.

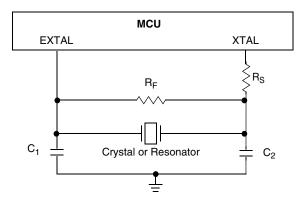

## 2.9 External Oscillator (XOSC) Characteristics

### Table 15. Oscillator Electrical Specifications (Temperature Range = -40 to 105 °C Ambient)

| Num | С | Rating                                                                                                                                                                                                                                                                                    | Symbol                                                                                                     | Min                    | Typical <sup>1</sup>         | Мах                                                | Unit                                   |  |

|-----|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------|------------------------------|----------------------------------------------------|----------------------------------------|--|

| 1   | С | Oscillator crystal or resonator (EREFS = 1, ERCLKEN = 1)<br>Low range (RANGE = 0)<br>High range (RANGE = 1) FEE or FBE mode <sup>2</sup><br>High range (RANGE = 1) PEE or PBE mode <sup>3</sup><br>High range (RANGE = 1, HGO = 1) BLPE mode<br>High range (RANGE = 1, HGO = 0) BLPE mode | f <sub>lo</sub><br>f <sub>hi-fll</sub><br>f <sub>hi-pll</sub><br>f <sub>hi-hgo</sub><br>f <sub>hi-lp</sub> | 32<br>1<br>1<br>1<br>1 |                              | 38.4<br>5<br>16<br>16<br>8                         | kHz<br>MHz<br>MHz<br>MHz<br>MHz<br>MHz |  |

| 2   |   | Load capacitors                                                                                                                                                                                                                                                                           | C <sub>1</sub><br>C <sub>2</sub>                                                                           |                        | •                            | e crystal or resonator<br>cturer's recommendation. |                                        |  |

| 3   |   | Feedback resistor<br>Low range (32 kHz to 38.4 kHz)<br>High range (1 MHz to 16 MHz)                                                                                                                                                                                                       | R <sub>F</sub>                                                                                             |                        | 10<br>1                      |                                                    | MΩ                                     |  |

| 4   |   | Series resistor<br>Low range, low gain (RANGE = 0, HGO = 0)<br>Low range, high gain (RANGE = 0, HGO = 1)<br>High range, low gain (RANGE = 1, HGO = 0)<br>High range, high gain (RANGE = 1, HGO = 1)<br>≥ 8 MHz<br>4 MHz<br>1 MHz                                                          | R <sub>S</sub>                                                                                             |                        | 0<br>100<br>0<br>0<br>0<br>0 | <br><br>10<br>20                                   | kΩ                                     |  |

| 5   | т | Crystal start-up time <sup>4</sup><br>Low range, low gain (RANGE = 0, HGO = 0)<br>Low range, high gain (RANGE = 0, HGO = 1)<br>High range, low gain (RANGE = 1, HGO = 0) <sup>5</sup><br>High range, high gain (RANGE = 1, HGO = 1) <sup>5</sup>                                          | t<br>CSTL-LP<br>ÇSTL-HGO<br>CSTH-LP<br>t<br>CSTH-HGO                                                       |                        | 200<br>400<br>5<br>15        | <br><br>                                           | ms                                     |  |

| 6   | т | Square wave input clock frequency (EREFS = 0, ERCLKEN =<br>1)<br>FEE or FBE mode <sup>2</sup><br>PEE or PBE mode <sup>3</sup><br>BLPE mode                                                                                                                                                | f <sub>extal</sub>                                                                                         | 0.03125<br>1<br>0      |                              | 5<br>16<br>40                                      | MHz                                    |  |

<sup>1</sup> Data in Typical column was characterized at 5.0 V, 25 °C or is typical recommended value.

<sup>2</sup> When MCG is configured for FEE or FBE mode, input clock source must be divisible using RDIV to within the range of 31.25 kHz to 39.0625 kHz.

<sup>3</sup> When MCG is configured for PEE or PBE mode, input clock source must be divisible using RDIV to within the range of 1 MHz to 2 MHz.

<sup>4</sup> This parameter is characterized and not tested on each device. Proper PC board layout procedures must be followed to achieve specifications.

<sup>5</sup> 4 MHz crystal

## 2.10 MCG Specifications

### Table 16. MCG Frequency Specifications (Temperature Range = -40 to 105 °C Ambient)

| Num | С | Rat                                                                                                                                               | ing                   | Symbol                        | Min   | Typical <sup>1</sup> | Max     | Unit              |

|-----|---|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------------------|-------|----------------------|---------|-------------------|

| 1   | С | $\frac{1}{2} \frac{\text{Internal reference frequency} - \text{factory trimmed at}}{V_{\text{DD}} = 5 \text{ V and temperature} = 25 \text{ °C}}$ |                       | f <sub>int_ft</sub>           | _     | 32.768               | _       | kHz               |

| 2   | С | Average internal reference                                                                                                                        | frequency — untrimmed | f <sub>int_ut</sub>           | 31.25 | —                    | 39.0625 | kHz               |

| 3   | Т | Internal reference startup ti                                                                                                                     | me                    | t <sub>irefst</sub>           | _     | 60                   | 100     | μs                |

|     | С | DCO output frequency range — untrimmed <sup>2</sup>                                                                                               | Low range (DRS=00)    |                               | 16    | —                    | 20      | MHz               |

| 4   | С |                                                                                                                                                   | Mid range (DRS=01)    | f <sub>dco_ut</sub>           | 32    | —                    | 40      |                   |

|     | С | ango antininoa                                                                                                                                    | High range (DRS=10)   |                               | 48    | —                    | 60      |                   |

|     | Ρ | DCO output frequency <sup>2</sup><br>reference =32768Hz<br>and DMX32 = 1                                                                          | Low range (DRS=00)    | f <sub>dco_DMX32</sub>        | _     | 16.82                | _       | MHz               |

| 5   | Ρ |                                                                                                                                                   | Mid range (DRS=01)    |                               | _     | 33.69                | _       |                   |

|     | Ρ |                                                                                                                                                   | High range (DRS=10)   |                               | _     | 50.48                | _       |                   |

| 6   | D | Resolution of trimmed DCO output frequency at fixed voltage and temperature (using FTRIM)                                                         |                       | $\Delta f_{dco\_res\_t}$      | _     | ±0.1                 | ±0.2    | %f <sub>dco</sub> |

| 7   | D | Resolution of trimmed DCO output frequency at fixed voltage and temperature (not using FTRIM)                                                     |                       | $\Delta f_{dco\_res\_t}$      | _     | ±0.2                 | ±0.4    | %f <sub>dco</sub> |

| 8   | D | Total deviation of trimmed DCO output frequency over voltage and temperature                                                                      |                       | $\Delta f_{dco_t}$            | _     | 0.5<br>-1.0          | ±2      | %f <sub>dco</sub> |

| 9   | D | Total deviation of trimmed DCO output frequency over fixed voltage and temperature range of $0-70$ °C                                             |                       | $\Delta f_{dco_t}$            |       | ±0.5                 | ±1      | %f <sub>dco</sub> |

| 10  | D | FLL acquisition time <sup>3</sup>                                                                                                                 |                       | t <sub>fll_acquire</sub>      | _     | —                    | 1       | ms                |

| 11  | D | PLL acquisition time <sup>4</sup>                                                                                                                 |                       | t <sub>pll_acquire</sub>      | _     | —                    | 1       | ms                |

| 12  | D | Long term jitter of DCO output clock (averaged over 2ms interval) <sup>5</sup>                                                                    |                       | C <sub>Jitter</sub>           | _     | 0.02                 | 0.2     | %f <sub>dco</sub> |

| 13  | D | VCO operating frequency                                                                                                                           |                       | f <sub>vco</sub>              | 7.0   | —                    | 55.0    | MHz               |

| 16  | D | Jitter of PLL output clock measured over 625 ns <sup>6</sup>                                                                                      |                       | f <sub>pll_jitter_625ns</sub> | _     | 0.566 <sup>6</sup>   | —       | %f <sub>pll</sub> |

| 17  | D | Lock entry frequency tolerance <sup>7</sup>                                                                                                       |                       | D <sub>lock</sub>             | ±1.49 | —                    | ±2.98   | %                 |

#### Table 16. MCG Frequency Specifications (continued)(Temperature Range = -40 to 105 °C Ambient)

| Num | С | Rating                                                  | Symbol                | Min                    | Typical <sup>1</sup> | Max                                                        | Unit |

|-----|---|---------------------------------------------------------|-----------------------|------------------------|----------------------|------------------------------------------------------------|------|

| 18  | D | Lock exit frequency tolerance <sup>8</sup>              | D <sub>unl</sub>      | ±4.47                  | _                    | ±5.97                                                      | %    |

| 19  | D | Lock time — FLL                                         | t <sub>fll_lock</sub> | _                      |                      | t <sub>fll_acquire+</sub><br>1075(1/ <sup>f</sup> int_t)   | s    |

| 20  | D | Lock time — PLL                                         | t <sub>pll_lock</sub> | _                      | _                    | t <sub>pll_acquire+</sub><br>1075(1/ <sup>f</sup> pll_ref) | s    |

| 21  | D | Loss of external clock minimum frequency —<br>RANGE = 0 | f <sub>loc_low</sub>  | $(3/5) \times f_{int}$ | _                    | _                                                          | kHz  |

<sup>1</sup> Data in Typical column was characterized at 5.0 V, 25 °C or is typical recommended value.

<sup>2</sup> The resulting bus clock frequency must not exceed the maximum specified bus clock frequency of the device.

<sup>3</sup> This specification applies when the FLL reference source or reference divider is changed, trim value changed or changing from FLL disabled (BLPE, BLPI) to FLL enabled (FEI, FEE, FBE, FBI). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

<sup>4</sup> This specification applies when the PLL VCO divider or reference divider is changed, or changing from PLL disabled (BLPE, BLPI) to PLL enabled (PBE, PEE). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

<sup>5</sup> Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum f<sub>BUS</sub>. Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise injected into the FLL circuitry via V<sub>DD</sub> and V<sub>SS</sub> and variation in crystal oscillator frequency increase the C<sub>Jitter</sub> percentage for a given interval.

<sup>6</sup> 625 ns represents 5 time quanta for CAN applications, under worst case conditions of 8 MHz CAN bus clock, 1 Mbps CAN bus speed, and 8 time quanta per bit for bit time settings. 5 time quanta is the minimum time between a synchronization edge and the sample point of a bit using 8 time quanta per bit.

<sup>7</sup> Below D<sub>lock</sub> minimum, the MCG enters lock. Above D<sub>lock</sub> maximum, the MCG will not enter lock. But if the MCG is already in lock, then the MCG may stay in lock.

<sup>8</sup> Below D<sub>unl</sub> minimum, the MCG will not exit lock if already in lock. Above D<sub>unl</sub> maximum, the MCG is guaranteed to exit lock.

## 2.11 AC Characteristics

This section describes ac timing characteristics for each peripheral system.

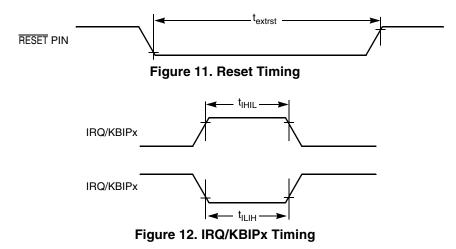

## 2.11.1 Control Timing

| Num | С | Parameter                                                                                                                                                                                                                                                            | Symbol                                | Min                           | Typical <sup>1</sup> | Max  | Unit |

|-----|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------|----------------------|------|------|

| 1   | D | Bus frequency (t <sub>cyc</sub> = 1/f <sub>Bus</sub> )                                                                                                                                                                                                               | f <sub>Bus</sub>                      | dc                            | _                    | 24   | MHz  |

| 2   | D | Internal low-power oscillator period                                                                                                                                                                                                                                 | t <sub>LPO</sub>                      | 800                           | —                    | 1500 | μs   |

| 3   | D | External reset pulse width <sup>2</sup><br>( $t_{cyc} = 1/f_{Self\_reset}$ )                                                                                                                                                                                         | t <sub>extrst</sub>                   | 100                           | _                    | _    | ns   |

| 4   | D | Reset low drive                                                                                                                                                                                                                                                      | t <sub>rstdrv</sub>                   | $66 	imes t_{cyc}$            | —                    | _    | ns   |

| 5   | D | Active background debug mode latch setup time                                                                                                                                                                                                                        | t <sub>MSSU</sub>                     | 500                           | —                    | _    | ns   |

| 6   | D | Active background debug mode latch hold time                                                                                                                                                                                                                         | t <sub>MSH</sub>                      | 100                           | —                    | _    | ns   |

| 7   | D | IRQ pulse width<br>Asynchronous path <sup>2</sup><br>Synchronous path <sup>3</sup>                                                                                                                                                                                   | t <sub>ILIH,</sub> t <sub>IHIL</sub>  | 100<br>1.5 × t <sub>cyc</sub> | _                    | _    | ns   |

| 8   | D | KBIPx pulse width<br>Asynchronous path <sup>2</sup><br>Synchronous path <sup>3</sup>                                                                                                                                                                                 | t <sub>ILIH,</sub> t <sub>IHIL</sub>  | 100<br>1.5 × t <sub>cyc</sub> | _                    | _    | ns   |

| 9   | D | Port rise and fall time $(load = 50 \text{ pF})^4$<br>Slew rate control disabled (PTxSE = 0), Low Drive<br>Slew rate control enabled (PTxSE = 1), Low Drive<br>Slew rate control disabled (PTxSE = 0), Low Drive<br>Slew rate control enabled (PTxSE = 1), Low Drive | t <sub>Rise</sub> , t <sub>Fall</sub> | <br>                          | 11<br>35<br>40<br>75 | _    | ns   |

Table 17. Control Timing

<sup>1</sup> Typical values are based on characterization data at  $V_{DD}$  = 5.0 V, 25 °C unless otherwise stated.

<sup>2</sup> This is the shortest pulse that is guaranteed to be recognized as a reset pin request. Shorter pulses are not guaranteed to override reset requests from internal sources.

<sup>3</sup> This is the minimum pulse width that is guaranteed to pass through the pin synchronization circuitry. Shorter pulses may or may not be recognized. In stop mode, the synchronizer is bypassed so shorter pulses can be recognized in that case.

$^4$   $\,$  Timing is shown with respect to 20%  $V_{DD}$  and 80%  $V_{DD}$  levels. Temperature range –40 °C to 105 °C.

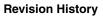

1. Not defined but normally MSB of character just received

Figure 18. SPI Slave Timing (CPHA = 1)

## 2.13 Flash Specifications

This section provides details about program/erase times and program-erase endurance for the Flash memory.

Program and erase operations do not require any special power sources other than the normal  $V_{DD}$  supply. For more detailed information about program/erase operations, see Chapter 4, "Memory."

**Mechanical Outline Drawings**

# 3 Mechanical Outline Drawings

Table 22 provides the available package types and their document numbers. The latest package outline/mechanical drawings are available on the MCF51AC256 Series Product Summary pages at http://www.freescale.com.

To view the latest drawing, either:

- Click on the appropriate link in Table 22, or

- Open a browser to the FreescaleÆ website (http://www.freescale.com), and enter the appropriate document number (from Table 22) in the "Enter Keyword" search box at the top of the page.

| Pin Count | Туре | Document No. |

|-----------|------|--------------|

| 80        | LQFP | 98ARL10530D  |

| 64        | LQFP | 98ASS23234W  |

| 64        | QFP  | 98ASB42844B  |

| 44        | LQFP | 98ASS23225W  |

### Table 22. Package Information

# 4 Revision History

\_\_\_\_

### Table 23. Revision History

| Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | Initial published                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2        | Updated ADC channels, Item 1, 4-5 on Table 2.10                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3        | Completed all theTBDs.<br>Changed RTC to RTI in Figure 1.<br>Corrected the block diagram.<br>Changed $V_{DDAD}$ to $V_{DDA}$ , $V_{SSAD}$ to $V_{SSA}$ .<br>Added charge device model data and removed machine data in Table 8.<br>Updated the specifications of $V_{LVDH}$ , $V_{LVDL}$ , $V_{LVWH}$ and $V_{LVWL}$ in Table 10.<br>Updated S2I <sub>DD</sub> , S3I <sub>DD</sub> in Table 11.<br>Added C column in Table 14.<br>Updated f <sub>dco_DMX32</sub> in Table 16. |

| 4        | Corrected the expansion of SPI to serial peripheral interface.                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5        | Updated V <sub>LVDL</sub> in the Table 10.<br>Updated RI <sub>DD</sub> in the Table 11.                                                                                                                                                                                                                                                                                                                                                                                       |

| 6        | Updated $V_{LVDH}$ , $V_{LVDL}$ , $V_{LVWH}$ and $V_{LVWL}$ in the Table 10.<br>Added LPO on the Figure 1 and LPO features in the Section 1.3, "Features."                                                                                                                                                                                                                                                                                                                    |

| 7        | Added 44-pin LQFP package information for AC256 and AC128.                                                                                                                                                                                                                                                                                                                                                                                                                    |