Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | M210                                                                   |

| Core Size                  | 16/32-Bit                                                              |

| Speed                      | 33MHz                                                                  |

| Connectivity               | EBI/EMI, SCI, SPI                                                      |

| Peripherals                | POR, PWM, WDT                                                          |

| Number of I/O              | 72                                                                     |

| Program Memory Size        | 128KB (128K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 8K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                            |

| Data Converters            | A/D 8x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 144-LQFP                                                               |

| Supplier Device Package    | 144-LQFP (20x20)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mmc2107cfcpv33 |

**Table of Contents**

| 11.4.2.3Port Pin Data/Set Data Registers.25311.4.2.4Port Clear Output Data Registers.25411.4.2.5Port C/D Pin Assignment Register.25511.4.2.6Port E Pin Assignment Register.25611.5Functional Description.25711.5.1Pin Functions.25811.5.2Port Digital I/O Timing.258 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11.6 Interrupts                                                                                                                                                                                                                                                      |

| Section 12. Edge Port Module (EPORT)                                                                                                                                                                                                                                 |

| 12.1 Contents                                                                                                                                                                                                                                                        |

| 12.2 Introduction                                                                                                                                                                                                                                                    |

| 12.3 Low-Power Mode Operation                                                                                                                                                                                                                                        |

| 12.3.1 Wait and Doze Modes                                                                                                                                                                                                                                           |

| 12.3.2 Stop Mode                                                                                                                                                                                                                                                     |

| 12.4 Interrupt/General-Purpose I/O Pin Descriptions                                                                                                                                                                                                                  |

| 12.5 Memory Map and Registers                                                                                                                                                                                                                                        |

| 12.5.1 Memory Map                                                                                                                                                                                                                                                    |

| 12.5.2 Registers                                                                                                                                                                                                                                                     |

| 12.5.2.2 EPORT Data Direction Register                                                                                                                                                                                                                               |

| 12.5.2.3 Edge Port Interrupt Enable Register                                                                                                                                                                                                                         |

| 12.5.2.4 Edge Port Data Register                                                                                                                                                                                                                                     |

| 12.5.2.5 Edge Port Pin Data Register                                                                                                                                                                                                                                 |

| 12.5.2.6 Edge Port Flag Register269                                                                                                                                                                                                                                  |

| Section 13. Watchdog Timer Module                                                                                                                                                                                                                                    |

| 13.1 Contents                                                                                                                                                                                                                                                        |

| 13.2 Introduction                                                                                                                                                                                                                                                    |

| 13.3 Modes of Operation                                                                                                                                                                                                                                              |

| 13.3.1 Wait Mode                                                                                                                                                                                                                                                     |

| 13.3.2 Doze Mode                                                                                                                                                                                                                                                     |

| 13.3.3 Stop Mode                                                                                                                                                                                                                                                     |

| 13.3.4 Debug Mode272                                                                                                                                                                                                                                                 |

# **Table of Contents**

| 21.13 Signal Descriptions                                 | 555 |

|-----------------------------------------------------------|-----|

| 21.13.1 Debug Serial Input (TDI)                          | 555 |

| 21.13.2 Debug Serial Clock (TCLK)                         |     |

| 21.13.3 Debug Serial Output (TDO)                         | 555 |

| 21.13.4 Debug Mode Select (TMS)                           | 556 |

| 21.13.5 Test Reset (TRST)                                 | 556 |

| 21.13.6 Debug Event (DE)                                  |     |

| 21.14 Functional Description                              | 556 |

| 21.14.1 Operation                                         | 557 |

| 21.14.2 OnCE Controller and Serial Interface              | 558 |

| 21.14.3 OnCE Interface Signals                            | 559 |

| 21.14.3.1 Internal Debug Request Input (IDR)              |     |

| 21.14.3.2 CPU Debug Request (DBGRQ)                       |     |

| 21.14.3.3 CPU Debug Acknowledge (DBGACK)                  | 560 |

| 21.14.3.4 CPU Breakpoint Request (BRKRQ)                  | 560 |

| 21.14.3.5 CPU Address, Attributes (ADDR, ATTR)            | 560 |

| 21.14.3.6 CPU Status (PSTAT)                              | 560 |

| 21.14.3.7 OnCE Debug Output (DEBUG)                       | 560 |

| 21.14.4 OnCE Controller Registers                         | 561 |

| 21.14.4.1 OnCE Command Register                           | 561 |

| 21.14.4.2 OnCE Control Register                           | 564 |

| 21.14.4.3 OnCE Status Register                            | 568 |

| 21.14.5 OnCE Decoder (ODEC)                               | 570 |

| 21.14.6 Memory Breakpoint Logic                           | 570 |

| 21.14.6.1 Memory Address Latch (MAL)                      | 571 |

| 21.14.6.2 Breakpoint Address Base Registers               | 571 |

| 21.14.7 Breakpoint Address Mask Registers                 | 571 |

| 21.14.7.1 Breakpoint Address Comparators                  |     |

| 21.14.7.2 Memory Breakpoint Counters                      | 572 |

| 21.14.8 OnCE Trace Logic                                  |     |

| 21.14.8.1 OnCE Trace Counter                              |     |

| 21.14.8.2 Trace Operation                                 |     |

| 21.14.9 Methods of Entering Debug Mode                    |     |

| 21.14.9.1 Debug Request During RESET                      |     |

| 21.14.9.2 Debug Request During Normal Activity            |     |

| 21.14.9.3 Debug Request During Stop, Doze, or Wait Mode . |     |

| 21.14.9.4 Software Request During Normal Activity         | 575 |

# **System Memory Map**

| Address                    | Register Name                                             | Bit Number                                                                                            |        |             |              |              |               |               |               |            |

|----------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------|-------------|--------------|--------------|---------------|---------------|---------------|------------|

| Edge Port (EPO             | RT)                                                       |                                                                                                       |        |             |              |              |               |               |               |            |

|                            |                                                           |                                                                                                       | Bit 15 | 14          | 13           | 12           | 11            | 10            | 9             | Bit 8      |

| 0x00c6_0000<br>0x00c6_0001 | EPORT Pin Assignment<br>Register (EPPAR)<br>See page 264. | Read:<br>Write:                                                                                       | EPPA7  |             | EPPA6        |              | EPPA5         |               | EPPA4         |            |

|                            | See page 204.                                             | Reset:                                                                                                | 0      | 0           | 0            | 0            | 0             | 0             | 0             | 0          |

|                            |                                                           |                                                                                                       | Bit 7  | 6           | 5            | 4            | 3             | 2             | 1             | Bit 0      |

|                            |                                                           | Read:<br>Write:                                                                                       | EPI    | PA3         | EPPA2        |              | EPPA1         |               | EPPA0         |            |

|                            |                                                           | Reset:                                                                                                | 0      | 0           | 0            | 0            | 0             | 0             | 0             | 0          |

|                            |                                                           |                                                                                                       | Bit 7  | 6           | 5            | 4            | 3             | 2             | 1             | Bit 0      |

| 0x00c6_0002                | EPORT Data Direction<br>Register (EPDDR)                  | Read:<br>Write:                                                                                       | EPDD7  | EPDD6       | EPDD5        | EPDD4        | EPDD3         | EPDD2         | EPDD1         | EPDD0      |

|                            | See page 266.                                             | Reset:                                                                                                | 0      | 0           | 0            | 0            | 0             | 0             | 0             | 0          |

|                            |                                                           |                                                                                                       | Bit 7  | 6           | 5            | 4            | 3             | 2             | 1             | Bit 0      |

| 0x00c6_0003                | EPORT Port Interrupt<br>Enable Register (EPIER)           | Read:<br>Write:                                                                                       | EPIE7  | EPIE6       | EPIE5        | EPIE4        | EPIE3         | EPIE2         | EPIE1         | EPIE0      |

|                            | See page 267.                                             | Reset:                                                                                                | 0      | 0           | 0            | 0            | 0             | 0             | 0             | 0          |

|                            |                                                           |                                                                                                       | Bit 7  | 6           | 5            | 4            | 3             | 2             | 1             | Bit 0      |

| 0x00c6_0004                | EPORT Port Data<br>Register (EPDR)<br>See page 268.       | Read:<br>Write:                                                                                       | EPD7   | EPD6        | EPD5         | EPD4         | EPD3          | EPD2          | EPD1          | EPD0       |

|                            |                                                           | Reset:                                                                                                | 1      | 1           | 1            | 1            | 1             | 1             | 1             | 1          |

|                            |                                                           |                                                                                                       | Bit 7  | 6           | 5            | 4            | 3             | 2             | 1             | Bit 0      |

|                            | EPORT Port Pin Data                                       | Read:                                                                                                 | EPPD7  | EPPD6       | EPPD5        | EPPD4        | EPPD3         | EPPD2         | EPPD1         | EPPD0      |

| 0x00c6_0005                | Register (EPPDR)                                          | Write:                                                                                                |        |             |              |              |               |               |               |            |

|                            | See page 268.                                             | Reset:                                                                                                | Р      | Р           | Р            | Р            | Р             | Р             | Р             | Р          |

|                            |                                                           |                                                                                                       | Bit 7  | 6           | 5            | 4            | 3             | 2             | 1             | Bit 0      |

| 0x00c6_0006                | EPORT Port Flag Regiser<br>(EPFR)                         | Read:<br>Write:                                                                                       | EPF7   | EPF6        | EPF5         | EPF4         | EPF3          | EPF2          | EPF1          | EPF0       |

|                            | See page 269.                                             | Reset:                                                                                                | 0      | 0           | 0            | 0            | 0             | 0             | 0             | 0          |

|                            |                                                           |                                                                                                       | Bit 7  | 6           | 5            | 4            | 3             | 2             | 1             | Bit 0      |

| 0x00c6_0007                |                                                           | Writes have no effect, reads return 0s, and the access terminates without a transfer error exception. |        |             |              |              |               |               |               |            |

| P = Current pin s          | state U = Unaffected                                      |                                                                                                       |        | = Writes ha | ve no effect | and the acce | ess terminate | s without a t | ransfer error | exception. |

Figure 2-2. Register Summary (Sheet 17 of 34)

Address **Register Name** Bit Number Timer 1 (TIM1) and Timer 2 (TIM2) Note: Addresses for TIM1 are at 0x00ce\_#### and addresses for TIM2 are at 0x00cf\_####. Bit 7 4 3 2 1 Bit 0 0 0 0 0 Timer Input Capture/ Read: IOS2 IOS1 IOS0 **IOS3** 0x00ce\_0000 **Output Compare Select** Write: 0x00cf\_0000 Register (TIMIOS) See page 300. 0 0 0 0 Reset: 0 0 0 0 Bit 7 5 4 3 2 1 Bit 0 6 Read 0 0 0 0 0 0 **Timer Compare Force** 0x00ce\_0001 Register (TIMCFORC) FOC3 FOC2 FOC1 FOC0 Write: 0x00cf\_0001 See page 301. Reset: 0 0 0 0 0 0 0 0 Bit 7 5 4 3 2 Bit 0 6 1 0 0 0 0 **Timer Output Compare 3** Read: OC3M3 OC3M2 OC3M1 OC3M0 Mask Register 0x00ce\_0002 Write: (TIMOC3M) 0x00cf\_0002 See page 302. 0 0 0 0 0 0 0 Reset: 0 Bit 7 5 4 3 2 1 Bit 0 6 0 0 0 0 Read: **Timer Output Compare 3** OC3D3 OC3D2 OC3D1 OC3D0 0x00ce 0003 Data Register (TIMOC3D) Write: 0x00cf 0003 See page 303. Reset: 0 0 0 0 0 0 0 0 Bit 7 5 4 3 2 1 Bit 0 6 Read: Bit 15 14 13 12 11 10 9 Bit 8 **Timer Counter Register** 0x00ce\_0004 High (TIMCNTH) Write: 0x00cf\_0004 See page 304. Reset: 0 0 0 0 0 0 0 0 Bit 7 5 3 2 6 4 1 Bit 0 Bit 7 6 5 4 3 2 1 Bit 0 Read: **Timer Counter Register** 0x00ce\_0005 Low (TIMCNTL) Write: 0x00cf\_0005 See page 304. Reset: 0 0 0 0 0 0 0 0 Bit 7 5 4 3 2 Bit 0 6 1 0 Read: 0 0 0 0 0 **Timer System Control** TIMEN **TFFCA** 0x00ce\_0006 Register 1 (TIMSCR1) Write: 0x00cf\_0006 See page 305. 0 0 Reset: 0 0 0 0 = Writes have no effect and the access terminates without a transfer error exception. P = Current pin state U = Unaffected

Figure 2-2. Register Summary (Sheet 28 of 34)

Chip Configuration Module (CCM)

Memory Map and Registers

LOAD — Pad Driver Load Bit

The LOAD bit selects full or default drive strength for selected pad output drivers. For maximum capacitive load, set the LOAD bit to select full drive strength. For reduced power consumption, clear the LOAD bit to select default drive strength.

- 1 = Full drive strength

- 0 = Default drive strength

Table 3-2 shows the read/write accessibility of this write-once bit.

SHEN — Show Cycle Enable Bit

The SHEN bit enables the external memory interface to drive the external bus during internal transfer operations.

- 1 = Show cycles enabled

- 0 = Show cycles disabled

In emulation mode, the SHEN bit is read-only. In all other modes, it is a read/write bit.

EMINT — Emulate Internal Address Space Bit

The EMINT bit enables chip select 1 (CS1) to decode the internal memory address space.

- 1 = CS1 decodes internal memory address space.

- 0 = CS1 decodes external memory address space.

The EMINT bit is read-always but can be written only in emulation mode.

MODE[2:0] — Chip Configuration Mode Field

This read-only field reflects the chip configuration mode, as shown in **Table 3-4**.

Table 3-4. Chip Configuration Mode Selection

| MODE[2:0] | Chip Configuration Mode |

|-----------|-------------------------|

| 111       | Master mode             |

| 110       | Single-chip mode        |

| 10X       | FAST mode               |

| 0XX       | Emulation mode          |

## **Signal Description**

#### 4.5.2 Phase-Lock Loop (PLL) and Clock Signals

These signals are used to support the on-chip clock generation circuitry.

#### 4.5.2.1 External Clock In (EXTAL)

This input signal is always driven by an external clock input except when used as a connection to the external crystal when the internal oscillator circuit is used. The clock source is configured during reset.

#### 4.5.2.2 Crystal (XTAL)

This output signal is used as a connection to the external crystal when the internal oscillator circuit is used. XTAL should be grounded when using an external clock input.

#### 4.5.2.3 Clock Out (CLKOUT)

This output signal reflects the internal system clock.

#### 4.5.2.4 Synthesizer Power (V<sub>DDSYN</sub> and V<sub>SSSYN</sub>)

These are dedicated quiet power and ground supply signals for the frequency synthesizer circuit.

#### 4.5.3 External Memory Interface Signals

In addition to the function stated here, these signals can be configured as discrete I/O signals also.

#### 4.5.3.1 Data Bus (D[31:0])

These three-state bidirectional signals provide the general-purpose data path between the microcontroller unit (MCU) and all other devices.

Non-Volatile Memory FLASH (CMFR)

Registers and Memory Map

#### RSVD24 — Reserved

Writing to this read/write bit updates the value but has no effect on functionality.

#### SUPV[7:0] — Supervisor Space Field

The read-always SUPV[7:0] field controls supervisor/unrestricted address space assignment of array blocks. The field is writable when the LOCKCTL bit is clear.

Array blocks that correspond to 1s in SUPV[7:0] are selected for data address space.

Each array block can be mapped into supervisor or unrestricted address space. When an array block is mapped into supervisor address space (SUPV[M] = 1) only supervisor accesses are allowed. A user access to a location in supervisor address space causes a data error exception. When an array block is mapped into unrestricted address space (SUPV[M] = 0) both supervisor and user accesses are allowed.

The default reset state of SUPV[7:0] bits are supervisor address space (SUPV[M] = 1).

- 1 = Array block in supervisor address space

- 0 = Array block in unrestricted address space

#### DATA[7:0] — Data Space Field

The read-always DATA[7:0] field controls data/program address space assignment of array blocks. When LOCKCTL = 1, the DATA[7:0] field is write-protected, and writing to it has no effect.

Array blocks that correspond to 1s in DATA[7:0] are selected for data address space.

Each array block can be mapped into data address space or both data and program address space. When an array block is mapped into data address space (DATA[M] = 1) only data accesses are allowed. A program access to a location in data address space causes a data error exception. When an array block is mapped into both data and program address space (DATA[M] = 0) both data and program accesses are allowed.

The default reset state of DATA[7:0] bits are data and program address space (DATA[M] = 0).

- 1 = Array block in data address space

- 0 = Array block is both data and program address space

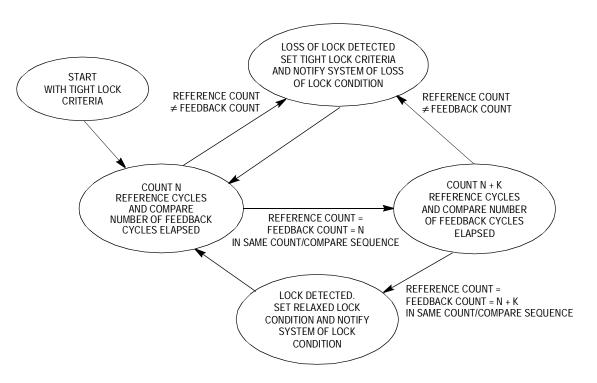

After lock is detected, the lock circuit continues to monitor the reference and feedback frequencies using the alternate count and compare process. If the counters do not match at any comparison time, then the LOCK flag is cleared to indicate that the PLL has lost lock. At this point, the lock criteria is tightened and the lock detect process is repeated.

The alternate count sequences prevent false lock detects due to frequency aliasing while the PLL tries to lock. Alternating between tight and relaxed lock criteria prevents the lock detect function from randomly toggling between locked and non-locked status due to phase sensitivities. Figure 10-6 shows the sequence for detecting locked and non-locked conditions.

In external clock mode, the PLL is disabled and cannot lock.

Figure 10-6. Lock Detect Sequence

# **Clock Module**

Table 10-8. Stop Mode Operation (Sheet 1 of 3)

| MODE | EN                          | RE        | RE                                     |       | ပ    | UP    | Expected PLL                   | PLL Action                                   | MODE                  | . KS   | ×    | ς      | _                                                                                                                                     |

|------|-----------------------------|-----------|----------------------------------------|-------|------|-------|--------------------------------|----------------------------------------------|-----------------------|--------|------|--------|---------------------------------------------------------------------------------------------------------------------------------------|

| In   | LOCEN                       | LOCRE     | LOLRE                                  | PLL   | osc  | FWKUP | Action at Stop                 | During Stop                                  | Out                   | LOCKS  | TOCK | SOOT   | Comments                                                                                                                              |

| EXT  | Х                           | Χ         | Х                                      | Х     | Х    | Х     | _                              | _                                            | EXT                   | 0      | 0    | 0      |                                                                                                                                       |

| LXI  | ,                           | ,         | ^                                      | ^     | ^    | ^     |                                | Lose reference clock                         | Stuck                 | _      | _    | -      |                                                                                                                                       |

|      |                             | •         |                                        | 0,11  | 0,11 |       | Lose lock,                     | Regain                                       | NRM                   | 'LK    | 1    | 'LC    |                                                                                                                                       |

| NRM  | 0                           | 0         | 0                                      | Off   | Off  | 0     | f.b. clock,<br>reference clock | No regain                                    | Stuck                 | _      |      | -      |                                                                                                                                       |

| NDM  | V                           | •         |                                        | 0#    | 0#   | 1     | Lose lock,                     | Regain clocks, but don't regain lock         | SCM-><br>unstable NRM | 0->'LK | 0->1 | 1->'LC | Block LOCS and LOCKS until<br>clock and lock respectively<br>regain; enter SCM regardless<br>of LOCEN bit until reference<br>regained |

| NRM  | X                           | 0         | 0                                      | Off   | Off  | 1     | f.b. clock,<br>reference clock | No reference clock regain                    | SCM->                 | 0->    | 0->  | 1->    | Block LOCS and LOCKS until<br>clock and lock respectively<br>regain; enter SCM regardless<br>of LOCEN bit                             |

|      |                             |           |                                        |       |      |       |                                | No f.b. clock regain                         | Stuck                 | _      | _    | _      |                                                                                                                                       |

|      |                             |           |                                        |       |      |       |                                | Regain                                       | NRM                   | 'LK    | 1    | 'LC    | Block LOCKS from being cleared                                                                                                        |

| NRM  | RM 0 0 0 Off On 0 Lose lock | Lose lock | Lose reference clock or no lock regain | Stuck | _    | _     | _                              |                                              |                       |        |      |        |                                                                                                                                       |

|      |                             |           |                                        |       |      |       |                                | Lose reference clock, regain                 | NRM                   | 'LK    | 1    | 'LC    | Block LOCKS from being cleared                                                                                                        |

|      |                             |           |                                        |       |      |       |                                | No lock regain                               | Unstable NRM          | 0->'LK | 0->1 | ĹĊ     | Block LOCKS until lock regained                                                                                                       |

| NRM  | 0                           | 0         | 0                                      | Off   | On   | 1     | Lose lock                      | Lose reference clock or no f.b. clock regain | Stuck                 | _      | ı    | ı      |                                                                                                                                       |

|      |                             |           |                                        |       |      |       |                                | Lose reference clock, regain                 | Unstable NRM          | 0->'LK | 0->1 | ĹĊ     | LOCS not set because<br>LOCEN = 0                                                                                                     |

|      |                             |           |                                        |       |      |       |                                | 1                                            | NRM                   | 'LK    | 1    | 'LC    |                                                                                                                                       |

|      |                             |           |                                        |       |      |       |                                | Lose lock or clock                           | Stuck                 | _      | _    |        |                                                                                                                                       |

| NRM  | 0                           | 0         | 0                                      | On    | On   | 0     | _                              | Lose lock, regain                            | NRM                   | 0      | 1    | 'LC    |                                                                                                                                       |

|      |                             |           |                                        |       |      |       |                                | Lose clock and lock, regain                  | NRM                   | 0      | 1    | 'LC    | LOCS not set because<br>LOCEN = 0                                                                                                     |

|      |                             |           |                                        |       |      |       |                                | _                                            | NRM                   | 'LK    | 1    | 'LC    |                                                                                                                                       |

|      |                             |           |                                        |       |      |       |                                | Lose lock                                    | Unstable NRM          | 0      | 0->1 | 'LC    |                                                                                                                                       |

|      |                             |           |                                        |       |      |       |                                | Lose lock, regain                            | NRM                   | 0      | 1    | 'LC    |                                                                                                                                       |

| NRM  | 0                           | 0         | 0                                      | On    | On   | 1     | _                              | Lose clock                                   | Stuck                 | _      | _    | _      |                                                                                                                                       |

|      |                             |           |                                        |       |      |       |                                | Lose clock, regain without lock              | Unstable NRM          | 0      | 0->1 | 'LC    |                                                                                                                                       |

|      |                             |           |                                        |       |      |       |                                | Lose clock, regain with lock                 | NRM                   | 0      | 1    | 'LC    |                                                                                                                                       |

|      |                             |           |                                        |       |      | _     |                                |                                              |                       |        |      |        |                                                                                                                                       |

## **Edge Port Module (EPORT)**

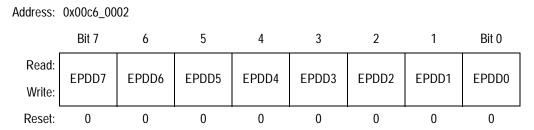

#### 12.5.2.2 EPORT Data Direction Register

Figure 12-3. EPORT Data Direction Register (EPDDR)

#### EPDD[7:0] — Edge Port Data Direction Bits

Setting any bit in the EPDDR configures the corresponding pin as an output. Clearing any bit in EPDDR configures the corresponding pin as an input. Pin direction is independent of the level/edge detection configuration. Reset clears EPDD[7:0].

To use an EPORT pin as an external interrupt request source, its corresponding bit in EPDDR must be clear. Software can generate interrupt requests by programming the EPORT data register when the EPDDR selects output.

- 1 = Corresponding EPORT pin configured as output

- 0 = Corresponding EPORT pin configured as input

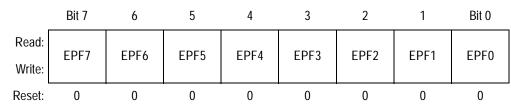

#### 12.5.2.6 Edge Port Flag Register

$Address: \ 0x00c6\_0006$

Figure 12-7. EPORT Port Flag Register (EPFR)

EPF[7:0] — Edge Port Flag Bits

When an EPORT pin is configured for edge triggering, its corresponding read/write bit in EPFR indicates that the selected edge has been detected. Reset clears EPF[7:0].

- 1 = Selected edge for INTx pin has been detected.

- 0 = Selected edge for INTx pin has not been detected.

Bits in this register are set when the selected edge is detected on the corresponding pin. A bit remains set until cleared by writing a 1 to it. Writing 0 has no effect. If a pin is configured as level-sensitive (EPPARx = 00), pin transitions do not affect this register.

## Technical Data — MMC2107

# Section 14. Programmable Interrupt Timer Modules (PIT1 and PIT2)

#### 14.1 Contents

| 14.2 Introduction                        |

|------------------------------------------|

| 14.3 Block Diagram                       |

| 14.4 Modes of Operation                  |

| 14.4.1 Wait Mode                         |

| 14.4.2 Doze Mode283                      |

| 14.4.3 Stop Mode                         |

| 14.4.4 Debug Mode                        |

| 14.5 Signals                             |

| 14.6 Memory Map and Registers            |

| 14.6.1 Memory Map284                     |

| 14.6.2 Registers                         |

| 14.6.2.1 PIT Control and Status Register |

| 14.6.2.2 PIT Modulus Register            |

| 14.6.2.3 PIT Count Register              |

| 14.7 Functional Description              |

| 14.7.1 Set-and-Forget Timer Operation290 |

| 14.7.2 Free-Running Timer Operation      |

| 14.7.3 Timeout Specifications            |

| 14.8 Interrupt Operation                 |

|                                          |

Serial Communications Interface Modules (SCI1 and SCI2)

Memory Map and Registers

#### 16.7.2 SCI Control Register 1

Address: SCI1 — 0x00cc\_0002

SCI2 — 0x00cd\_0002

|        | Bit 7 | 6       | 5    | 4  | 3    | 2   | 1  | Bit 0 |

|--------|-------|---------|------|----|------|-----|----|-------|

| Read:  | LOOPS | WOMS    | RSRC | NA | WAKE | ILT | PE | PT    |

| Write: | LUUPS | VVOIVIS | RSRC | M  | WAKE | ILI | PE | PI    |

| Reset: | 0     | 0       | 0    | 0  | 0    | 0   | 0  | 0     |

Figure 16-4. SCI Control Register 1 (SCICR1)

Read: Anytime

Write: Anytime

LOOPS — Loop Select Bit

This read/write control bit switches the SCI between normal mode and loop mode. Reset clears LOOPS.

1 = Loop mode SCI operation

0 = Normal mode SCI operation

The SCI operates normally (LOOPS = 0, RSRC = X) when the output of its transmitter is connected to the TXD pin, and the input of its receiver is connected to the RXD pin.

In loop mode (LOOPS =1, RSRC = 0), the input to the SCI receiver is internally disconnected from the RXD pin logic and instead connected to the output of the SCI transmitter. The behavior of TXD is governed by the DDRSC1 bit in SCIDDR. If DDRSC1 = 1, the TXD pin is driven with the output of the SCI transmitter. If DDRSC1 = 0, the TXD pin idles high. See **16.14 Loop Operation** for additional information.

For either loop mode or single-wire mode to function, both the SCI receiver and transmitter must be enabled by setting the RE and TE bits in SCIxCR2.

NOTE:

The RXD pin becomes general-purpose I/O when LOOPS = 1, regardless of the state of the RSRC bit. DDRSC0 in SCIDDR is the data direction bit for the RXD pin.

**Table 16-3** shows how the LOOPS, RSRC, and DDRSC0 bits affect SCI operation and the configuration of the RXD and TXD pins.

## Serial Communications Interface Modules (SCI1 and SCI2)

#### 16.10 Baud Rate Generation

A 13-bit modulus counter in the baud rate generator derives the baud rate for both the receiver and the transmitter. The value from 0 to 8191 written to SCIBDH and SCIBDL determines the system clock divisor. The baud rate clock is synchronized with the bus clock and drives the receiver. The baud rate clock divided by 16 drives the transmitter. The receiver acquisition rate is 16 samples per bit time.

Baud rate generation is subject to two sources of error:

- 1. Integer division of the module clock may not give the exact target frequency.

- 2. Synchronization with the bus clock can cause phase shift.

Table 16-4. Example Baud Rates (System Clock = 33 MHz)

| SBR[12:0] | Receiver Clock<br>(Hz) | Transmitter Clock<br>(Hz) | Target<br>Baud Rate | Percent<br>Error |

|-----------|------------------------|---------------------------|---------------------|------------------|

| 0x0012    | 1,833,333.3            | 114,583.3                 | 115,200             | 0.54             |

| 0x0024    | 916,666.7              | 57,291.7                  | 57,600              | 0.54             |

| 0x0036    | 611,111.1              | 38,194.4                  | 38,400              | 0.54             |

| 0x003d    | 540,983.6              | 33,811.4                  | 33,600              | 0.63             |

| 0x0048    | 458,333.3              | 28,645.8                  | 28,800              | 0.54             |

| 0x006b    | 308,411.2              | 19,275.7                  | 19,200              | 0.39             |

| 0x0008f   | 230,769.2              | 14,423.1                  | 14,400              | 0.16             |

| 0x00d7    | 153,488.4              | 95,93.0                   | 9,600               | 0.07             |

| 0x01ae    | 76,744.2               | 4,796.5                   | 4,800               | 0.07             |

| 0x035b    | 38,416.8               | 2,401.0                   | 2,400               | 0.04             |

| 0x06b7    | 19,197.2               | 1,199.8                   | 1,200               | 0.01             |

| 0x0d6d    | 9,601.4                | 600.1                     | 600                 | 0.01             |

| 0x1adb    | 4,800.0                | 300.0                     | 300                 | 0                |

## **Serial Communications Interface Modules (SCI1 and SCI2)**

#### 16.11.1 Frame Length

The transmitter can generate either 10-bit or 11-bit frames. In SCICR1, the M bit selects frame length, and the PE bit enables the parity function. One data bit may be an address mark or an extra stop bit. All frames begin with a start bit and end with one or two stop bits. When transmitting 9-bit data, bit T8 in SCI data register high (SCIDRH) is the ninth bit (bit 8).

Table 16-5. Example 10-Bit and 11-Bit Frames

| M Bit | Frame<br>Length | Start<br>Bit | Data<br>Bits | Parity<br>Bit | Address<br>Mark <sup>(1)</sup> | Stop<br>Bit(s) |

|-------|-----------------|--------------|--------------|---------------|--------------------------------|----------------|

| 0     |                 | 1            | 8            | No            | No                             | 1              |

|       | 10 bits         | 1            | 7            | No            | No                             | 2              |

|       |                 | 1            | 7            | No            | Yes                            | 1              |

|       |                 | 1            | 7            | Yes           | No                             | 1              |

|       | 44 64-          | 1            | 9            | No            | No                             | 1              |

|       |                 | 1            | 8            | No            | No                             | 2              |

| 1     |                 | 1            | 8            | No            | Yes                            | 1              |

|       | 11 bits         | 1            | 8            | Yes           | No                             | 1              |

|       |                 | 1            | 7            | No            | Yes                            | 2              |

|       |                 | 1            | 7            | Yes           | No                             | 2              |

<sup>1.</sup> When implementing a multidrop network using the SCI, the address mark bit is used to designate subsequent data frames as a network address and not device data.

## **Serial Peripheral Interface Module (SPI)**

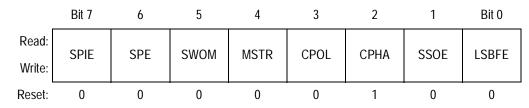

#### 17.7.1 SPI Control Register 1

Address: 0x00cb\_0000

Figure 17-2. SPI Control Register 1 (SPICR1)

Read: Anytime

Write: Anytime

SPIE — SPI Interrupt Enable Bit

The SPIE bit enables the SPIF and MODF flags to generate interrupt requests. Reset clears SPIE.

1 = SPIF and MODF interrupt requests enabled 0 = SPIF and MODF interrupt requests disabled

SPE — SPI System Enable Bit

The SPE bit enables the SPI and dedicates SPI port pins [3:0] to SPI functions. When SPE is clear, the SPI system is initialized but in a low-power disabled state. Reset clears SPE.

1 = SPI enabled

0 = SPI disabled

SWOM — SPI Wired-OR Mode Bit

The SWOM bit configures the output buffers of SPI port pins [3:0] as open-drain outputs. SWOM controls SPI port pins [3:0] whether they are SPI outputs or general-purpose outputs. Reset clears SWOM.

1 = Output buffers of SPI port pins [3:0] open-drain

0 = Output buffers of SPI port pins [3:0] CMOS drive

## **Serial Peripheral Interface Module (SPI)**

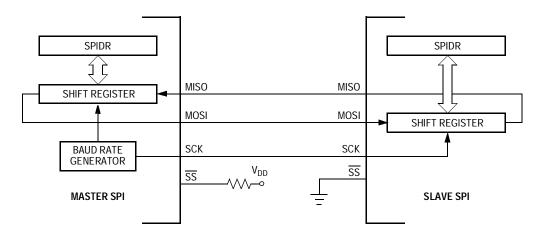

## 17.8 Functional Description

The SPI module allows full-duplex, synchronous, serial communication between the MCU and peripheral devices. Software can poll the SPI status flags or SPI operation can be interrupt driven.

Setting the SPE bit in SPICR1 enables the SPI and dedicates four SPI port pins to SPI functions:

- Slave select (SS)

- Serial clock (SCK)

- Master out/slave in (MOSI)

- Master in/slave out (MISO)

When the SPE bit is clear, the  $\overline{SS}$ , SCK, MOSI, and MISO pins are general-purpose I/O pins controlled by SPIDDR.

The 8-bit shift register in a master SPI is linked by the MOSI and MISO pins to the 8-bit shift register in the slave. The linked shift registers form a distributed 16-bit register. In an SPI transmission, the SCK clock from the master shifts the data in the 16-bit register eight bit positions, and the master and slave exchange data. Data written to the master SPIDR register is the output data to the slave. After the exchange, data read from the master SPIDR is the input data from the slave.

Figure 17-10. Full-Duplex Operation

Semiconductor, Inc.

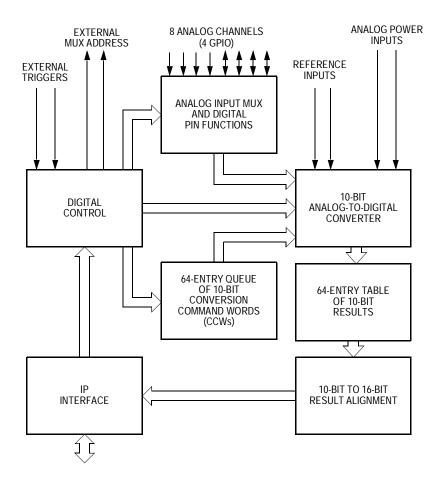

Queued Analog-to-Digital Converter (QADC)

Block Diagram

- Output data readable in three formats:

- Right-justified unsigned

- Left-justified signed

- Left-justified unsigned

- Unused analog channels can be used as digital ports

### 18.4 Block Diagram

Figure 18-1. QADC Block Diagram

External Bus Interface Module (EBI)

Bus Monitor

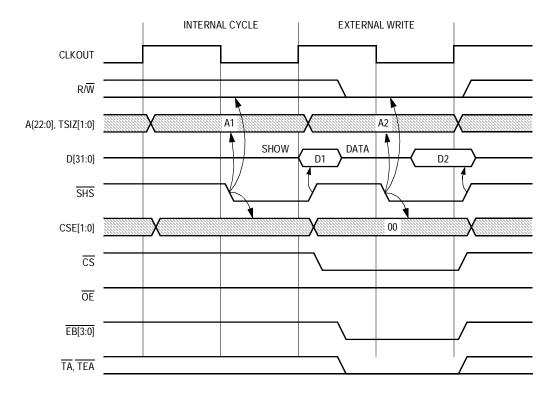

Figure 19-6. Internal (Show) Cycle Followed by External 1-Clock Write

#### 19.10 Bus Monitor

The bus monitor can be set detects excessively long bus access termination response times. Whenever an undecoded address is accessed or a peripheral is inoperative, the access is not terminated and the bus is potentially locked up while it waits for the required response.

The bus monitor monitors the cycle termination response times during a bus cycle. If the cycle termination response time exceeds a programmed count, the bus monitor asserts an internal bus error.

The bus monitor monitors the cycle termination response time (in system clock cycles) by using a programmable maximum allowable response period. There are four selectable response time periods for the bus monitor, selectable among 8, 16, 32, and 64 system clock cycles. The periods are selectable with the BMT[1:0] field in the chip configuration module CCR. The programmability of the timeout allows for varying external peripheral response times. The monitor is cleared and restarted

# **JTAG Test Access Port and OnCE**

| 21.13.4    | Debug Mode Select (TMS)                          | 556 |

|------------|--------------------------------------------------|-----|

| 21.13.5    | Test Reset (TRST)                                | 556 |

| 21.13.6    | Debug Event (DE)                                 | 556 |

| 21.14 Fu   | unctional Description                            | 556 |

| 21.14.1    | Operation                                        | 557 |

| 21.14.2    | OnCE Controller and Serial Interface             | 558 |

| 21.14.3    | OnCE Interface Signals                           | 559 |

| 21.14.3.1  | Internal Debug Request Input (IDR)               | 559 |

| 21.14.3.2  | CPU Debug Request (DBGRQ)                        | 560 |

| 21.14.3.3  | CPU Debug Acknowledge (DBGACK)                   | 560 |

| 21.14.3.4  | CPU Breakpoint Request (BRKRQ)                   | 560 |

| 21.14.3.5  | CPU Address, Attributes (ADDR, ATTR)             | 560 |

| 21.14.3.6  | CPU Status (PSTAT)                               | 560 |

| 21.14.3.7  | OnCE Debug Output (DEBUG)                        | 560 |

| 21.14.4    | OnCE Controller Registers                        | 561 |

| 21.14.4.1  | OnCE Command Register                            | 561 |

| 21.14.4.2  | OnCE Control Register                            | 564 |

| 21.14.4.3  | OnCE Status Register                             | 568 |

| 21.14.5    | OnCE Decoder (ODEC)                              | 570 |

| 21.14.6    | Memory Breakpoint Logic                          | 570 |

| 21.14.6.1  | Memory Address Latch (MAL)                       | 571 |

| 21.14.6.2  | Breakpoint Address Base Registers                | 571 |

| 21.14.7    | Breakpoint Address Mask Registers                | 571 |

| 21.14.7.1  | Breakpoint Address Comparators                   | 572 |

| 21.14.7.2  | Memory Breakpoint Counters                       | 572 |

| 21.14.8    | OnCE Trace Logic                                 | 572 |

| 21.14.8.1  | OnCE Trace Counter                               | 573 |

| 21.14.8.2  | Trace Operation                                  | 574 |

| 21.14.9    | Methods of Entering Debug Mode                   |     |

| 21.14.9.1  | Debug Request During RESET                       | 574 |

| 21.14.9.2  | Debug Request During Normal Activity             | 575 |

| 21.14.9.3  | Debug Request During Stop, Doze, or Wait Mode    | 575 |

| 21.14.9.4  | Software Request During Normal Activity          | 575 |

| 21.14.10   | Enabling OnCE Trace Mode                         | 575 |

| 21.14.11   | Enabling OnCE Memory Breakpoints                 | 576 |

| 21.14.12   | Pipeline Information and Write-Back Bus Register | 576 |

| 21.14.12.1 | Program Counter Register                         | 577 |

| 21.14.12.2 | 2 Instruction Register                           | 577 |

|            |                                                  |     |