Welcome to **E-XFL.COM**

<u>Embedded - Microcontrollers - Application</u>

<u>Specific</u>: Tailored Solutions for Precision and Performance

Embedded - Microcontrollers - Application Specific represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

What Are <u>Embedded - Microcontrollers - Application Specific?</u>

Application enecific microcontrollers are engineered to

| Details                 |                                                                           |

|-------------------------|---------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                  |

| Applications            | Automotive                                                                |

| Core Processor          | XC800                                                                     |

| Program Memory Type     | FLASH (64kB)                                                              |

| Controller Series       | -                                                                         |

| RAM Size                | 3.25K x 8                                                                 |

| Interface               | LIN, SSI, UART                                                            |

| Number of I/O           | 11                                                                        |

| Voltage - Supply        | 3V ~ 27V                                                                  |

| Operating Temperature   | -40°C ~ 150°C (TJ)                                                        |

| Mounting Type           | Surface Mount                                                             |

| Package / Case          | 48-VFQFN Exposed Pad                                                      |

| Supplier Device Package | PG-VQFN-48-29                                                             |

| Purchase URL            | https://www.e-xfl.com/product-detail/infineon-technologies/tle9834qxxuma1 |

|                         |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2012-03-08

Published by Infineon Technologies AG 81726 Munich, Germany © 2012 Infineon Technologies AG All Rights Reserved.

## **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

## Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

## Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

## **Table of Contents**

# **Table of Contents**

|                        | Table of Contents                        | . 3 |

|------------------------|------------------------------------------|-----|

| I                      | Summary of Features                      | . 5 |

| 1.1                    | Device Types / Ordering Information      |     |

| 1.2                    | Abbreviations                            | . 7 |

| <u> </u>               | General Device Information               | Ç   |

| <u>-</u><br>2.1        | Pin Configuration                        |     |

| 2.2                    | Pin Definitions and Functions            |     |

|                        |                                          |     |

| 3                      | Functional Description                   |     |

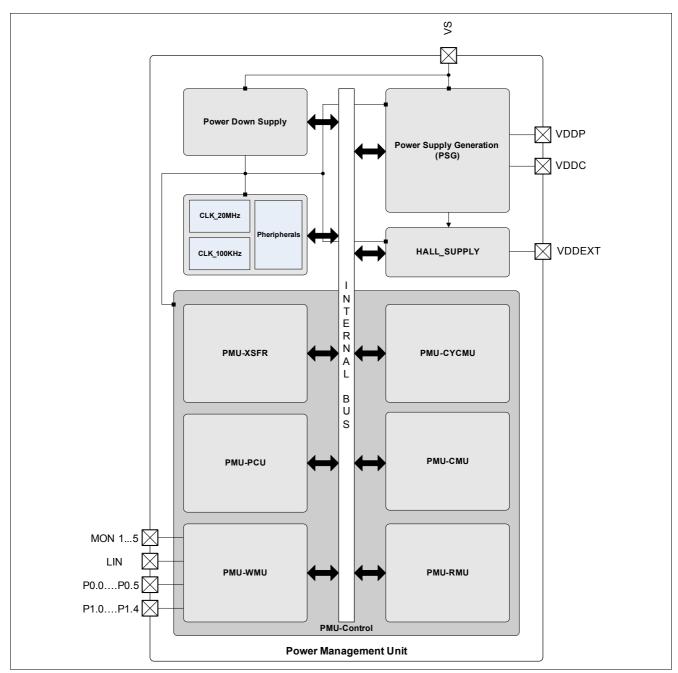

| 3.1<br>3.1.1           | Power Management Unit (PMU)              |     |

|                        | Voltage Regulator 5.0V (VDDP)            |     |

| 3.1.2                  | Voltage Regulator 1.5V (VDDC)            |     |

| 3.1.3<br>3.2           | External Voltage Regulator 5.0V (VDDEXT) |     |

| o.∠<br>3.2.1           | System Control Unit - Power Modules      |     |

| 3.2.1<br>3.2.2         | ·                                        |     |

| 3.2.2<br>3.3           | System Control Unit - Digital Part       |     |

| 3.4                    | Memory Architecture                      |     |

| 3. <del>4</del><br>3.5 | Flash Memory                             |     |

| 3.6                    | Watchdog Timer 1 (WDT1)                  |     |

| 3.7                    | Watchdog Timer (WDT)                     |     |

| 3.8                    | Interrupt System                         |     |

| 3.9                    | Multiplication/Division Unit             |     |

| 3.10                   | Parallel Ports                           |     |

| 3.11                   | Timer 0 and Timer 1                      |     |

| 3.12                   | Timer 2 and Timer 21                     |     |

| 3.13                   | Timer 3                                  |     |

| 3.14                   | Capture/Compare Unit 6 (CCU6)            |     |

| 3.15                   | UART                                     |     |

| 3.16                   | LIN Transceiver                          |     |

| 3.17                   | High-Speed Synchronous Serial Interface  |     |

| 3.18                   | Measurement Unit                         |     |

| 3.19                   | Measurement Core Module (incl. ADC2)     | 51  |

| 3.20                   | Analog Digital Converter (ADC1)          | 52  |

| 3.21                   | High Voltage Monitor Input               | 53  |

| 3.22                   | High Side Switches                       | 54  |

| 3.23                   | Low Side Switches                        | 55  |

| 3.24                   | PWM Generator                            | 56  |

| 3.25                   | Debug System                             | 57  |

| 1                      | Application Information                  | 58  |

| 1.1                    | Electric Drive Application               |     |

| 1.2                    | Connection of N.C. Pins                  |     |

| 1.3                    | Connection of ADCGND Pin                 |     |

| 1.4                    | Connection of Exposed Pad                |     |

| 1.5                    | Voltage Regulators-Blocking Capacitors   |     |

| 1.6                    | Additional External Components           |     |

| 1.7                    | ESD Tests                                |     |

| 5                      | Electrical Characteristics               | 61  |

| ,                      | LIGOLI IOGI OHGI GOLGI 131103            | υI  |

**Summary of Features**

# 1 Summary of Features

- High performance XC800 core

- compatible to standard 8051 core

- up to 40 MHz clock frequency

- two clocks per machine cycle architecture

- two data pointers

- On-chip memory

- 60 kByte + 4 kByte Flash for program code and data (4 kByte EEPROM emulation built-in)

- 512 Byte One Time Programmable Memory (OTP)

- 512 Byte 100 Time Programmable Memory (100TP)

- 256 Byte RAM, 3 kByte XRAM

- BootROM for startup firmware and Flash routines

- Core logic supply at 1.5 V

- On-chip OSC and PLL for clock generation

- Loss of clock detection with fail safe mode for power switches

- Watchdog timer (WDT) with programmable window feature for refresh operation and warning prior to overflow

- General-purpose I/O Port (GPIO) with wake-up capability

- Multiplication/division unit (MDU) for arithmetic calculation

- Software libraries to support floating point and MDU calculations

- Five 16-Bit timers Timer 0, Timer 1, Timer 2, Timer 21 and Timer 3

- Capture/compare unit for PWM signal generation (CCU6) with Timer 12 and Timer 13

- Full duplex serial interface (UART) with LIN support

- Synchronous serial channel (SSC)

- On-chip debug support via 2-wire Device Access Port (DAP)

- LIN Bootstrap loader (LIN BSL)

- LIN transceiver compliant to LIN 1.3, LIN 2.0 and LIN 2.1

- 2 x Low Side Switches with clamping capability incl. PWM functionality, e.g. as relay driver

- 2 x High Side Switches with cyclic sense option and PWM functionality, e.g. for LED or powering of switches

- 5 x High Voltage Monitor Input pins for wake-up and with cyclic sense and analog measurement option

- Measurement unit with 10 channels, 8-Bit A/D Converter (ADC2) and data post processing

- 8 channels, 10-Bit A/D Converter (including battery voltage and supply voltage measurement) (ADC1)

- Single power supply from 3.0 V to 27 V

- Low-dropout voltage regulators (LDO)

- Dedicated 5 V voltage regulator for external loads (e.g. hall sensor)

- Programmable window watchdog (WDT1) with independent on-chip clock source

- · Power saving modes

- MCU slow-down mode

- Stop Mode

- Sleep Mode

- Cyclic wake-up and cyclic sense during Stop Mode and Sleep Mode

- Power-on and undervoltage/brownout reset generator

- Overtemperature protection

- Overcurrent protection with shutdown

- Supported by a full range of development tools including C compilers, macro assembler packages, emulators, evaluation boards, HLL debugger, programming tools, software packages

- Temperature Range T<sub>.i</sub>: -40 °C up to 150 °C

- Package VQFN-48-29

- · Green package (RoHS compliant)

Figure 5 Power Management Unit Block Diagram

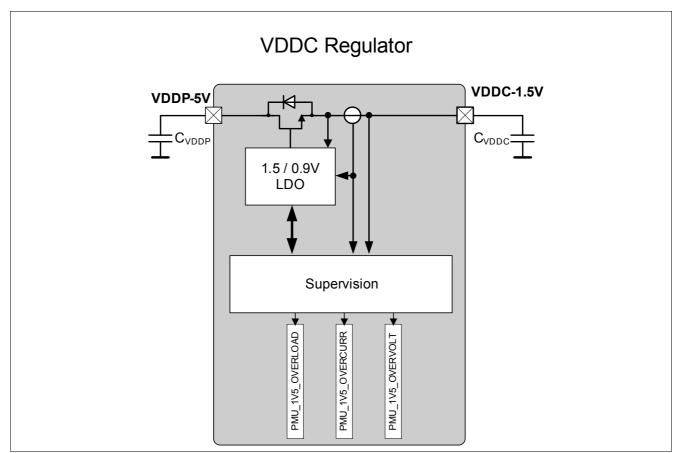

# 3.1.2 Voltage Regulator 1.5V (VDDC)

This module represents the 1.5 V voltage regulator, which serves as core supply for the 8-bit  $\mu$ C and other chip internal analog 1.5 V functions (e.g. 8 Bit ADC). To further reduce the current consumption of the 8-bit MCU during Stop Mode the output voltage is optionally reduced to 0.9 V.

#### **Features**

- 1.5 V low-drop voltage regulator

- Optional 0.9 V in Stop Mode

- · Current limitation

- · Overcurrent monitoring and shutdown with MCU signalling (interrupt)

- Overvoltage monitoring with MCU signalling (interrupt)

- Undervoltage monitoring with MCU signalling (interrupt)

- Pull-down current source at the output for Sleep Mode (100 μA)

The output capacitor C<sub>VDDC</sub> is mandatory to ensure a proper regulator functionality.

Figure 7 Module Block Diagram of VDDC Voltage Regulator

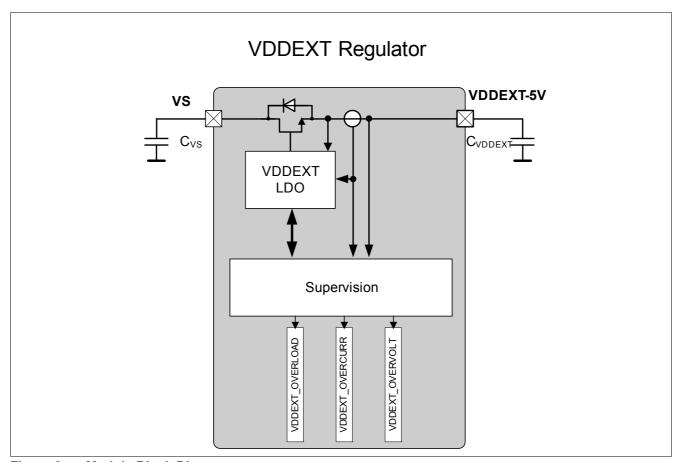

# 3.1.3 External Voltage Regulator 5.0V (VDDEXT)

The external voltage regulator provides 5 V output voltage in order to supply external circuitry like LEDs, hall sensors or potentiometers.

#### **Features**

- Switchable +5 V, 20 mA low-drop voltage regulator

- · Switch-on overcurrent blanking time in order to drive small capacitive loads

- Short circuit robust

- Overvoltage monitoring with MCU interrupt signalling

- Undervoltage monitoring with MCU interrupt signalling

- Selectable switch-on slew-rate 0.95 V/µs max. @10 mA supply current, 10 nF capacitive load

- Pull-down current source at the output for Sleep Mode and off mode (100 μA)

- Cyclic sense option together with GPIOs

Figure 8 Module Block Diagram

# 3.8 Interrupt System

The TLE9834QX supports 14 interrupt vectors with four priority levels. Eleven of these interrupt vectors are assigned to the on-chip peripherals: Timer 0, Timer 1, UART, SSC and A/D Converter are each assigned to one dedicated interrupt vector; while Timer2, Timer21, MDU, LIN and the Capture/Compare Unit share six interrupt vectors.

Two interrupt vectors are assigned to the external interrupts. External interrupts 0 to 1 are each assigned to one dedicated interrupt vector, external interrupt 2 shares on interrupt vector with Timer21 and the MDU.

One interrupt vector is dedicated to the XINT interrupt events whose interrupt flags are also located in registers in XSFR area.

A non-maskable interrupt (NMI) with the highest priority is shared by the following:

- Watchdog Timer, warning before overflow

- · MI CLK Watchdog Timer overflow event

- · PLL, loss of lock

- · Flash, on operation complete, e.g. erase.

- · OCDS, on user IRAM event

- Oscillator watchdog detection for too low oscillation of  $f_{

m OSC}$

- Flash map error

- Uncorrectable ECC error on Flash, XRAM and IRAM

- VSUP supply pre warning when any supply voltage drops below or exceeds any threshold.

Figure 14, Figure 15, Figure 16, Figure 17 and Figure 18 give a general overview of the interrupt sources and nodes, and their corresponding control and status flags. Figure 19 gives the corresponding overview for the NMI sources.

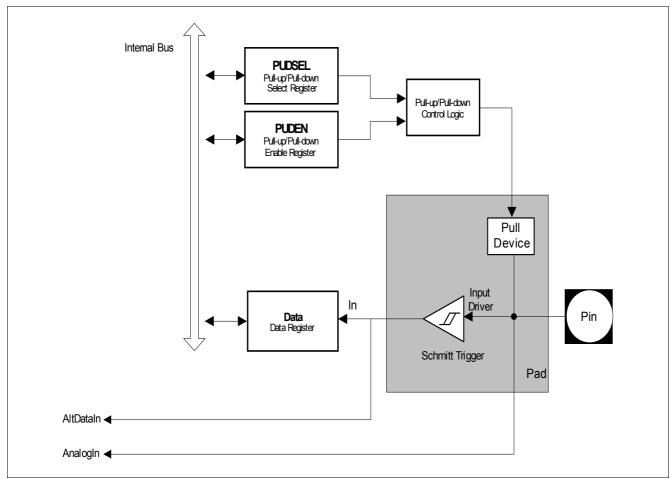

**Figure 21** shows the structure of an input-only port pin. Each P2 pin can only function in input mode. Register P2\_DIR is provided to enable or disable the input driver. When the input driver is enabled, the actual voltage level present at the port pin is translated into a logic 0 or 1 via a Schmitt-Trigger device and can be read via register. Each pin can also be programmed to activate an internal weak pull-up or pull-down device. The analog input (Analog In) bypasses the digital circuitry and Schmitt-Trigger device for direct feed-through to the ADC1 input channel.

Figure 21 General Structure of an Input Port Pin

- Programmable number of data Bits: 2 to 8 Bits

- Programmable shift direction: LSB or MSB shift first

- Programmable clock polarity: idle low or high state for the shift clock

- Programmable clock/data phase: data shift with leading or trailing edge of the shift clock

- Variable baud rate

- Compatible with Serial Peripheral Interface (SPI)

- Interrupt generation

- On a transmitter empty condition

- On a receiver full condition

- On an error condition (receive, phase, baud rate, transmit error)

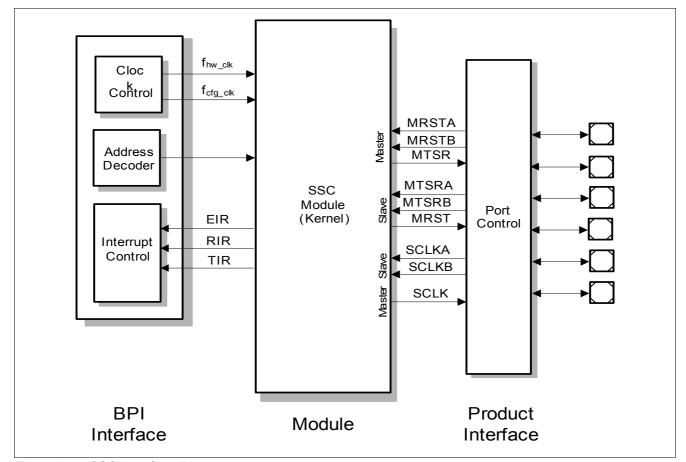

Data is transmitted or received on lines TXD and RXD, which are normally connected to the pins MTSR (Master Transmit/Slave Receive) and MRST (Master Receive/Slave Transmit). The clock signal is output via line MS\_CLK (Master Serial Shift Clock) or input via line SS\_CLK (Slave Serial Shift Clock). Both lines are normally connected to the pin SCLK. Transmission and reception of data are double-buffered.

Figure 24 shows all functional relevant interfaces associated with the SSC Kernel.

Figure 24 SSC Interface Diagram

**Application Information**

# 4 Application Information

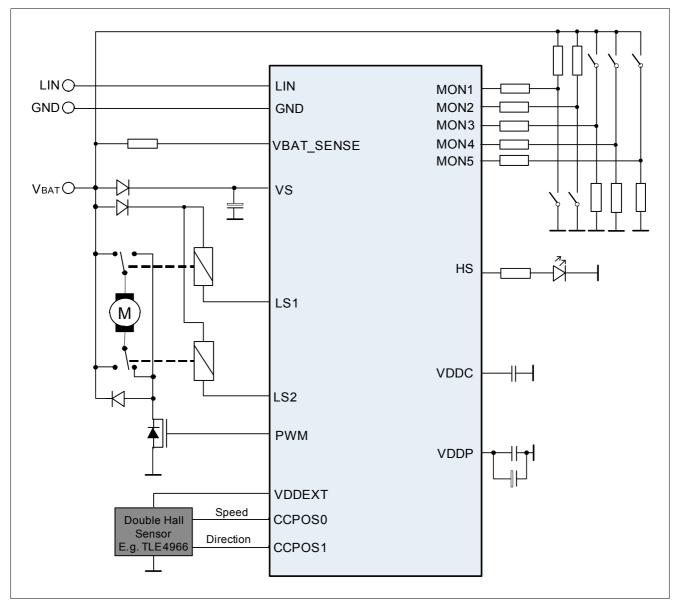

# 4.1 Electric Drive Application

**Figure 31** shows the TLE9834QX in an electric drive application setup controlling a DC-brush motor. The two Low Side Switches are controlling a relay each. An external FET allows to control the window lift motor with a PWM signal as generated with the CCU6 module of the microcontroller.

Note: The following information is given as a hint for the implementation of the device only and shall not be regarded as a description or warranty of a certain functionality, condition or quality of the device.

Figure 31 Simplified Application Diagram

**Application Information**

## 4.2 Connection of N.C. Pins

It is recommended to connect N.C. pins to GND unless otherwise specified. Since pins 10 and 46 are located next to high voltage pins (VS, MON5, LS1) these 2 N.C. pins can be also left unconnected in order to avoid huge current flow and damage of the system in case of short-circuit.

## 4.3 Connection of ADCGND Pin

The ADCGND pin is chip-internal connected to reference ground. In order to provide full offset compensation and achieve full accuracy of ADC1 the ADCGND pin must not be connected to board ground. ADCGND pin should be connected with a capacitor (100 nF) to VAREF only.

# 4.4 Connection of Exposed Pad

It is recommended to connect the exposed pad to GND.

# 4.5 Voltage Regulators-Blocking Capacitors

Table 11 External Component Recommendation

| Symbol              | Function                         | Comment                                  |

|---------------------|----------------------------------|------------------------------------------|

| C <sub>VS</sub>     | blocking capacitor at VS pin     | > 20 μF Elco + 100 nF Ceramic, ESR < 1 Ω |

| C <sub>VDDP</sub>   | blocking capacitor at VDDP pin   | 1 μF typ. + 100 nF Ceramic, ESR < 1 Ω    |

| C <sub>VDDEXT</sub> | blocking capacitor at VDDEXT pin | 100 nF typ., ESR < 1 Ω                   |

| C <sub>VDDC</sub>   | blocking capacitor at VDDC pin   | > 330 nF + 100 nF Ceramic, ESR < 1 Ω     |

| C <sub>VAREF</sub>  | blocking capacitor at VAREF pin  | > 100 nF, ESR < 1 Ω                      |

## 4.6 Additional External Components

Table 12 External Component Recommendation

| Symbol           | Function                         | Comment |

|------------------|----------------------------------|---------|

| C <sub>HSx</sub> | HF blocking capacitor at HSx pin | 6.8 nF  |

| $R_{MONx}$       | resistor at MONx pin             | 1 kΩ    |

| $R_{VBAT_{\_}}$  | resistor at VBAT_SENSE pin       | 1 kΩ    |

# 5.1.3 Current Consumption

Table 16 Electrical Characteristics 1)

$V_{\rm s}$  = 5.5V to 18V,  $T_{\rm J}$  = -40°C to 85°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                                  | Symbol               | Values |                | Unit | Note / Test Condition | Number                                                                                                                     |          |  |

|------------------------------------------------------------|----------------------|--------|----------------|------|-----------------------|----------------------------------------------------------------------------------------------------------------------------|----------|--|

|                                                            |                      | Min.   | lin. Typ. Max. |      |                       |                                                                                                                            |          |  |

| Current Consumption (                                      | ②VS pin              | l.     | Ш              |      | "                     |                                                                                                                            | 1        |  |

| Current Consumption in Active Mode                         | $I_{Active}$         | _      | 30             | 40   | mA                    | fsys = 40 MHz<br>no loads on pins, LIN in recessive<br>state, LS1, LS2, HS1 and HS2 off                                    | P_5.1.25 |  |

| Current consumption in Stop Mode                           | $I_{\sf Powerdown}$  | _      | 85             | 95   | μA                    | microcontroller in Stop Mode, LIN recessive state, MON1-5 disabled, GPIOs open (no loads)                                  | P_5.1.26 |  |

| Current consumption in Stop Mode with cyclic sense enabled | $I_{\sf Powerdown2}$ | -      | _              | 110  | μΑ                    | microcontroller in Stop Mode, LIN recessive state, GPIOs open (no loads)                                                   | P_5.1.27 |  |

| Current consumption in Sleep Mode                          | $I_{Sleep}$          | _      | _              | 25   | μΑ                    | system in Sleep Mode,<br>microcontroller not powered, LIN<br>recessive state, MON1-5 disabled<br>and GPIOs open (no loads) | P_5.1.28 |  |

<sup>1)</sup> Not subject to production test, specified by design.

Note: Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

## 5.1.4 Thermal Resistance

Table 17 Thermal Resistance

| Parameter           | Symbol     | Values |      | Values |     | Unit           | Note /   | Number |

|---------------------|------------|--------|------|--------|-----|----------------|----------|--------|

|                     |            | Min.   | Тур. | Max.   |     | Test Condition |          |        |

| Junction to Ambient | $R_{thJA}$ | _      | 23.9 | _      | K/W | 1)             | P_5.1.29 |        |

<sup>1)</sup> EIA/JESD 52 2, FR4, 76.2 x 114.3 x 1.5 mm; 35µ Cu, 5µ Sn; 300 mm<sup>2</sup>

# 5.2 Power Management Unit (PMU)

This chapter includes all electrical characteristics of the Power Management Unit

# 5.2.1 PMU I/O Supply Parameters VDDP

#### **Table 19 Electrical Characteristics**

| Parameter                                | Symbol                 | Values |      |      | Unit | Note / Test Condition                                         | Number   |  |

|------------------------------------------|------------------------|--------|------|------|------|---------------------------------------------------------------|----------|--|

|                                          |                        | Min.   | Тур. | Max. |      |                                                               |          |  |

| Specified Output Current                 | $I_{VDDP}$             | 0      | _    | 60   | mA   | 1)                                                            | P_5.2.1  |  |

| Required Output Capacitance              | $C_{VDDP}$             | 0.1    | _    | 10   | μF   | <sup>1)</sup> ESR < 1Ω                                        | P_5.2.2  |  |

| Output Voltage including line regulation | $V_{DDPOUT}$           | 4.9    | 5.0  | 5.1  | V    | $I_{\rm load}$ < 90mA;Vs > 5.5V                               | P_5.2.3  |  |

| Output Drop                              | Vs <sub>V DDPout</sub> | _      | _    | +400 | mV   | $I_{\rm load} < 70 \rm mA;$ $3 \rm V < V_{\rm s} < 5.5 \rm V$ | P_5.2.4  |  |

| Dynamic Load Regulation                  | $V_{\mathrm{VDDPLOR}}$ | -50    | _    | 50   | mV   | <sup>1)</sup> 2 70mA; C=470nF;<br>dI/dt=100mA/μs              | P_5.2.5  |  |

| Dynamic Line Regulation                  | $V_{ m VDDPLIR}$       | -25    | _    | 25   | mV   | $^{1)}$ $V_{\rm s}$ = 5.5 20V;<br>dV/dt=5V/ $\mu$ s           | P_5.2.6  |  |

| Power Supply Ripple Rejection            | $P_{SSRVDDP}$          | 50     | _    | _    | dB   | $^{1)}$ $V_{\rm s}$ = 13.5V; f=0<br>1KHz; Vr=2Vpp             | P_5.2.7  |  |

| Over Voltage Detection                   | $V_{DDPOV}$            | 5.05   | _    | 5.4  | V    | $V_{\rm s}$ > 5.5V; Overvoltage leads to SUPPLY_NMI           | P_5.2.8  |  |

| Under Voltage Reset                      | $V_{DDPUV}$            | 2.4    | _    | 2.7  | V    | V <sub>s</sub> > 5.5V                                         | P_5.2.9  |  |

| Over Current Shutdown                    | $I_{VDDPOC}$           | 90     | _    | 180  | mA   | _                                                             | P_5.2.10 |  |

<sup>1)</sup> Not subject to production test, specified by design

# 5.3 System Clocks

# 5.3.1 Oscillators and PLL

**Table 22 Electrical Characteristics**

| Parameter                      | Symbol                  |                | Values  | \$      | Unit | Note / Test Condition                                                                        | Number   |  |

|--------------------------------|-------------------------|----------------|---------|---------|------|----------------------------------------------------------------------------------------------|----------|--|

|                                |                         | Min. Typ. Max. |         | Max.    |      |                                                                                              |          |  |

| PMU Oscillators (Powe          | r Managei               | ment Unit)     |         |         |      |                                                                                              | 1        |  |

| Frequency of LP_CLK            | $f_{\sf LP\_CLK1}$      | 14             | 18      | 22      | MHz  | this clock is used at startup<br>and can be used in case the<br>PLL fails                    | P_5.3.1  |  |

| Frequency of LP_CLK2           | $f_{\sf LP\_CLK2}$      | 70             | 100     | 130     | kHz  | this clock is used for cyclic wake and cyclic sense                                          | P_5.3.2  |  |

| CGU Oscillator (Clock          | Generatio               | n Unit Mic     | roconti | roller) |      |                                                                                              |          |  |

| Short term frequency deviation | $f_{TRIMST}$            | -1.5%          | 5       | +1.5%   | MHz  | 1) with respect to nominal configured system frequency within one LIN message (< 10ms 100ms) | P_5.3.3  |  |

| Long term frequency deviation  | $f_{TRIMLT}$            | -3.0%          | 5       | +3.0%   | MHz  | with respect to nominal configured system frequency over lifetime and temperature            | P_5.3.4  |  |

| CGU-OSC Start-up time          | $T_{OSC}$               | _              | _       | 10      | μs   | startup time OSC from Sleep<br>Mode and Stop Mode, power<br>supply stable                    | P_5.3.5  |  |

| PLL (Clock Generation          | Unit Micro              | ocontrolle     | r)      |         |      |                                                                                              |          |  |

| VCO frequency range<br>Mode 0  | $f_{\text{VCO-0}}$      | 48             | _       | 112     | MHz  | VCOSEL ="0"                                                                                  | P_5.3.6  |  |

| VCO frequency range<br>Mode 1  | $f_{\text{VCO-1}}$      | 96             | _       | 160     | MHz  | VCOSEL ="1"                                                                                  | P_5.3.7  |  |

| Input frequency range          | $f_{\rm OSC}$           | 4              | _       | 16      | MHz  | _                                                                                            | P_5.3.8  |  |

| XTAL1 input freq. range        | $f_{ m OSC}$            | 4              | _       | 16      | MHz  | _                                                                                            | P_5.3.9  |  |

| Output freq. range             | $f_{PLL}$               | 0.04687        | _       | 80      | MHz  | _                                                                                            | P_5.3.10 |  |

| Free-running frequency Mode 0  | $f_{\text{VCOfree\_0}}$ | -              | _       | 38      | MHz  | VCOSEL ="0"                                                                                  | P_5.3.11 |  |

| Free-running frequency Mode 1  | $f_{\text{VCOfree\_1}}$ | -              | _       | 76      | MHz  | VCOSEL ="1"                                                                                  | P_5.3.12 |  |

| Input clock high/low time      | t <sub>high/low</sub>   | 10             | _       | _       | ns   | -                                                                                            | P_5.3.13 |  |

| Peak period jitter             | $t_{\rm jp}$            | -500           | _       | 500     | ps   | for K=1                                                                                      | P_5.3.14 |  |

# 5.4 Flash Parameters

This chapter includes the parameters for the 64 kByte embedded flash module.

## Table 24 Flash Characteristics 1)

| Parameter                              | Symbol       |      | Values          | S    | Unit    | Note /                       | Number  |

|----------------------------------------|--------------|------|-----------------|------|---------|------------------------------|---------|

|                                        |              | Min. | Тур.            | Max. |         | Test Condition               |         |

| Programming time per 128 Byte page     | $t_{PR}$     | _    | <sup>2)</sup> 3 | 3.5  | ms      | _                            | P_5.4.1 |

| Erase time per sector/page             | $t_{\sf ER}$ | _    | <sup>2)</sup> 4 | 4.5  | ms      | _                            | P_5.4.2 |

| Data retention time                    | $t_{RET}$    | 20   | _               | _    | years   | 1,000 erase / program cycles | P_5.4.3 |

| Flash erase endurance for user sectors | $N_{ER}$     | 30   | _               | _    | kcycles | Data retention time 5 years  | P_5.4.4 |

<sup>1)</sup> Not subject for production test, specified by design

<sup>2)</sup> Programming and erase times depend on the internal Flash clock source. The control state machine needs a few system clock cycles. This requirement is only relevant for extremely low system frequencies.

#### Table 26 **DC Characteristics**

$V_{\rm S}$  = 5.5 V to 27 V,  $T_{\rm i}$  = -40° C to +150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                | Symbol    |      | Values | ;    | Unit | Note /<br>Test Condition                                                                             | Number   |

|------------------------------------------|-----------|------|--------|------|------|------------------------------------------------------------------------------------------------------|----------|

|                                          |           | Min. | Тур.   | Max. |      |                                                                                                      |          |

| Input leakage current (all other)        | $I_{OZ2}$ | -15  | -      | +15  | μА   | $T_{\rm J} \le 150^{\circ}{\rm C},$<br>0.45 V < $V_{\rm IN}$<br>< $V_{\rm DDP}$                      | P_5.5.12 |

| Pull level keep current                  | $I_{PLK}$ | -240 | -      | +240 | μΑ   | $V_{\text{PIN}} \ge V_{\text{IH}} \text{ (up)}$<br>$V_{\text{PIN}} \le V_{\text{IL}} \text{ (dn)}$   | P_5.5.13 |

| Pull level force current                 | $I_{PLF}$ | -1.5 | -      | +1.5 | mA   | $V_{\text{PIN}} \leq V_{\text{IL}} \text{ (up)}$<br>$V_{\text{PIN}} \geq V_{\text{IH}} \text{ (dn)}$ | P_5.5.14 |

| Pin capacitance (digital inputs/outputs) | $C_{IO}$  | _    | -      | 10   | pF   | _                                                                                                    | P_5.5.15 |

- 1) Not subject to production test, specified by design.

- 2) The maximum deliverable output current of a port driver depends on the selected output driver mode. The limit for pin groups must be respected.

- 3) As a rule, with decreasing output current the output levels approach the respective supply level ( $V_{OL} \rightarrow GND$ ,  $V_{OH} \rightarrow V_{DDP}$ ). However, only the levels for nominal output currents are verified.

- 4) This specification is not valid for outputs which are switched to open drain mode. In this case the respective output will float and the voltage is determined by the external circuit.

- 5) The given values are worst-case values. In production test, this leakage current is only tested at 125°C; other values are ensured by correlation. For derating, please refer to the following descriptions:

- Leakage derating depending on temperature ( $T_{\rm J}$  = junction temperature [°C]):  $I_{\rm OZ}$  = 0.05 × e<sup>(1.5 + 0.028×TJ)</sup> [ $\mu$ A]. For example, at a temperature of 95°C the resulting leakage current is 3.2  $\mu$ A. Leakage derating depending on voltage level ( $\Delta V = V_{DDP} - V_{PIN} [V]$ ):

- $I_{OZ} = I_{OZtempmax} (1.6 \times \Delta V) [\mu A]$

- This voltage derating formula is an approximation which applies for maximum temperature.

- 6) Keep current: Limit the current through this pin to the indicated value so that the enabled pull device can keep the default pin level:  $V_{\text{PIN}} \ge V_{\text{IH}}$  for a pull-up;  $V_{\text{PIN}} \le V_{\text{IL}}$  for a pull-down.

- Force current: Drive the indicated minimum current through this pin to change the default pin level driven by the enabled pull device:  $V_{PIN} \le V_{IL}$  for a pull-up;  $V_{PIN} \ge V_{IH}$  for a pull-down.

- These values apply to the fixed pull-devices in dedicated pins and to the user-selectable pull-devices in general purpose IO pins.

**Data Sheet** 72 Rev. 1.1, 2012-03-08

# Table 41 Electrical Characteristics (cont'd)

| Parameter                                              | Symbol             | Values |           |      | Unit | Note / Test Condition                                                                | Number    |  |

|--------------------------------------------------------|--------------------|--------|-----------|------|------|--------------------------------------------------------------------------------------|-----------|--|

|                                                        |                    | Min.   | Тур. Мах. |      |      |                                                                                      |           |  |

| Turn OFF Delay time, PWM mode                          | $t_{dOff,f-LS}$    | _      | _         | 2    | μs   | LS_ON=0 to 0.1*Vs $V_{\rm S}$ =13.5V, $R_{\rm L}$ =270 $\Omega$                      | P_5.12.12 |  |

| Turn OFF Rise time, PWM mode                           | $t_{OFFR,PWM}$     | _      | 1         | 1.25 | μs   | $V_{\rm LS}$ 0.1*Vs to 0.9*Vs; $V_{\rm S}$ =13.5V, $R_{\rm L}$ =270 $\Omega$         | P_5.12.13 |  |

| Turn OFF Rise time, slow mode                          | $t_{OFFR,Slow}$    | _      | 100       | 150  | μs   | $^{1)}$ $V_{\rm LS}$ 0.9*Vs to 0.9*Vs; $V_{\rm S}$ =13.5V, $R_{\rm L}$ =270 $\Omega$ | P_5.12.14 |  |

| Minimum Duty Cycle Pulse Width variation               | ton <sub>MIN</sub> | 1.5    | 2         | 3.5  | μs   | $ton(dig) = 2\mu s^{2}$                                                              | P_5.12.15 |  |

| Typical (systematic) Pulse Width increase LS_ON to VLS | $d ton_{TYP}$      | _      | 1.25      | _    | μs   | $ton(dig) = 2\mu s^{2}$                                                              | P_5.12.16 |  |

| Zener Clamp Voltage                                    | $V_{AZ}$           | _      | 50        | _    | V    | values are valid at $T_{\rm j}$ = 25°C                                               | P_5.12.17 |  |

| Clamping Energy (repetitive)                           | $E_{\sf clamp}$    | _      | _         | 2    | mJ   | <sup>2)</sup> 1.000.000 cycles                                                       | P_5.12.18 |  |

| Clamping Energy                                        | $E_{clamp}$        | _      | _         | 14   | mJ   | <sup>2)</sup> <i>T</i> start = 25°C                                                  | P_5.12.19 |  |

| Clamping Energy (single), hot                          | $E_{clamp}$        | _      | _         | 7    | mJ   | <sup>2)</sup> 10 cycles, <i>T</i> start = 85°C                                       | P_5.12.20 |  |

<sup>1)</sup> Static ON mode (no PWM)

<sup>2)</sup> Not subject to production test, specified by design

**Package Outlines**

# 6 Package Outlines

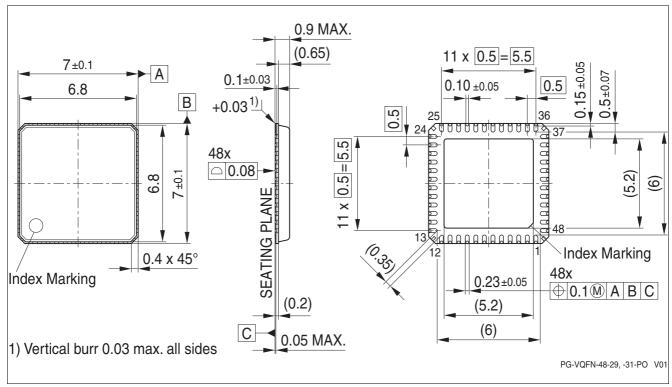

Figure 33 Package outline VQFN-48-29

## **Notes**

- 1. You can find all of our packages, sorts of packing and others in our Infineon Internet Page "Products": <a href="http://www.infineon.com/products">http://www.infineon.com/products</a>.

- 2. Dimensions in mm.

## **Revision History**

| Revision | Date       | Changes                                                                                                                                |

|----------|------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 1.1      | 2012-03-08 | Table 14: - Renamed Parameter "Output voltage VDDP" to "Voltage VDDP" (2x) - Renamed Parameter "Output voltage VDDC" to "Voltage VDDC" |

| 1.1      | 2012-03-08 | Table 28: Added value LIN input capacity C <sub>LIN_IN</sub>                                                                           |

#### **Trademarks of Infineon Technologies AG**

AURIXTM, C166TM, Canpaktm, CIPOSTM, CIPURSETM, EconoPacktm, CoolMostm, CoolSettm, Corecontroltm, Crossavetm, Davetm, EasyPIMTM, EconoBridgetm, EconoDualtm, EconoPiMTM, EiceDrivertm, eupectm, Fcostm, Hitfettm, HybridPacktm, I2rftm, Isopacetm, Isopacktm, Mipaqtm, ModStacktm, my-dtm, NovalithICtm, OptiMostm, Origatm, Primariontm, Primariontm, Primariontm, Primariontm, Rasictm, Reversavetm, Satrictm, Siegettm, Sindriontm, Sipmostm, Smartlewistm, Solid Flashtm, Tempfettm, thinq!tm, Trenchstoptm, Tricoretm.

#### Other Trademarks

Advance Design System™ (ADS) of Agilent Technologies, AMBA™, ARM™, MULTI-ICE™, KEIL™, PRIMECELL™, REALVIEW™, THUMB™, µVision™ of ARM Limited, UK. AUTOSAR™ is licensed by AUTOSAR development partnership. Bluetooth™ of Bluetooth SIG Inc. CAT-iq™ of DECT Forum. COLOSSUS™, FirstGPS™ of Trimble Navigation Ltd. EMV™ of EMVCo, LLC (Visa Holdings Inc.). EPCOS™ of Epcos AG. FLEXGO™ of Microsoft Corporation. FlexRay™ is licensed by FlexRay Consortium. HYPERTERMINAL™ of Hilgraeve Incorporated. IEC™ of Commission Electrotechnique Internationale. IrDA™ of Infrared Data Association Corporation. ISO™ of INTERNATIONAL ORGANIZATION FOR STANDARDIZATION. MATLAB™ of MathWorks, Inc. MAXIM™ of Maxim Integrated Products, Inc. MICROTEC™, NUCLEUS™ of Mentor Graphics Corporation. Mifare™ of NXP. MIPI™ of MIPI Alliance, Inc. MIPS™ of MIPS Technologies, Inc., USA. muRata™ of MURATA MANUFACTURING CO., MICROWAVE OFFICE™ (MWO) of Applied Wave Research Inc., OmniVision™ of OmniVision Technologies, Inc. Openwave™ Openwave Systems Inc. RED HAT™ Red Hat, Inc. RFMD™ RF Micro Devices, Inc. SIRIUS™ of Sirius Satellite Radio Inc. SOLARIS™ of Sun Microsystems, Inc. SPANSION™ of Spansion LLC Ltd. Symbian™ of Symbian Software Limited. TAIYO YUDEN™ of Taiyo Yuden Co. TEAKLITE™ of CEVA, Inc. TEKTRONIX™ of Tektronix Inc. TOKO™ of TOKO KABUSHIKI KAISHA TA. UNIX™ of X/Open Company Limited. VERILOG™, PALLADIUM™ of Cadence Design Systems, Inc. VLYNQ™ of Texas Instruments Incorporated. VXWORKS™, WIND RIVER™ of WIND RIVER SYSTEMS, INC. ZETEX™ of Diodes Zetex Limited.

Last Trademarks Update 2011-02-24

$w\ w\ w\ .\ i\ n\ f\ i\ n\ e\ o\ n\ .\ c\ o\ m$