Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                    |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, POR, PWM, WDT |

| Number of I/O              | 37                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 4K x 8                                                                  |

| RAM Size                   | 10K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-UFQFN Exposed Pad                                                    |

| Supplier Device Package    | 48-UFQFPN (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l151c6u6tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32L151x6/8/B and STM32L152x6/8/B ultra-low-power ARM<sup>®</sup> Cortex<sup>®</sup>-M3 based microcontrollers product line.

The ultra-low-power STM32L151x6/8/B and STM32L152x6/8/B family includes devices in 3 different package types: from 48 to 100 pins. Depending on the device chosen, different sets of peripherals are included, the description below gives an overview of the complete range of peripherals proposed in this family.

These features make the ultra-low-power STM32L151x6/8/B and STM32L152x6/8/B microcontroller family suitable for a wide range of applications:

- Medical and handheld equipment

- Application control and user interface

- PC peripherals, gaming, GPS and sport equipment

- Alarm systems, Wired and wireless sensors, Video intercom

- Utility metering

This STM32L151x6/8/B and STM32L152x6/8/B datasheet should be read in conjunction with the STM32L1xxxx reference manual (RM0038).

The document "Getting started with STM32L1xxxx hardware development" AN3216 gives a hardware implementation overview. Both documents are available from the STMicroelectronics website *www.st.com*.

For information on the ARM<sup>®</sup> Cortex<sup>®</sup>-M3 core please refer to the Cortex<sup>®</sup>-M3 Technical Reference Manual, available from the www.arm.com website.

Figure 1 shows the general block diagram of the device family.

**Caution:** This datasheet does not apply to STM32L15xx6/8/B-A covered by a separate datasheet.

# 2 Description

The ultra-low-power STM32L151x6/8/B and STM32L152x6/8/B devices incorporate the connectivity power of the universal serial bus (USB) with the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M3 32-bit RISC core operating at 32 MHz frequency (33.3 DMIPS), a memory protection unit (MPU), high-speed embedded memories (Flash memory up to 128 Kbytes and RAM up to 16 Kbytes) and an extensive range of enhanced I/Os and peripherals connected to two APB buses.

All the devices offer a 12-bit ADC, 2 DACs and 2 ultra-low-power comparators, six generalpurpose 16-bit timers and two basic timers, which can be used as time bases.

Moreover, the STM32L151x6/8/B and STM32L152x6/8/B devices contain standard and advanced communication interfaces: up to two I<sup>2</sup>Cs and SPIs, three USARTs and a USB. The STM32L151x6/8/B and STM32L152x6/8/B devices offer up to 20 capacitive sensing channels to simply add touch sensing functionality to any application.

They also include a real-time clock and a set of backup registers that remain powered in Standby mode.

Finally, the integrated LCD controller (except STM32L151x6/8/B devices) has a built-in LCD voltage generator that allows to drive up to 8 multiplexed LCDs with contrast independent of the supply voltage.

The ultra-low-power STM32L151x6/8/B and STM32L152x6/8/B devices operate from a 1.8 to 3.6 V power supply (down to 1.65 V at power down) with BOR and from a 1.65 to 3.6 V power supply without BOR option. It is available in the -40 to +85 °C temperature range, extended to 105°C in low power dissipation state. A comprehensive set of power-saving modes allows the design of low-power applications.

|                                 | Functionalities depending on the operating power supply range |                           |                                   |                      |  |  |  |

|---------------------------------|---------------------------------------------------------------|---------------------------|-----------------------------------|----------------------|--|--|--|

| Operating power<br>supply range | DAC and ADC<br>operation USB                                  |                           | Dynamic voltage<br>scaling range  | I/O operation        |  |  |  |

| V <sub>DD</sub> = 2.0 to 2.4 V  | Conversion time<br>up to 500 Ksps                             | Functional <sup>(2)</sup> | Range 1,<br>Range 2 or<br>Range 3 | Full speed operation |  |  |  |

| V <sub>DD</sub> = 2.4 to 3.6 V  | Conversion time<br>up to 1 Msps                               | Functional <sup>(2)</sup> | Range 1,<br>Range 2 or<br>Range 3 | Full speed operation |  |  |  |

#### Table 3. Functionalities depending on the operating power supply range (continued)

The CPU frequency changes from initial to final must respect "F<sub>CPU</sub> initial < 4\*F<sub>CPU</sub> final" to limit V<sub>CORE</sub> drop due to current consumption peak when frequency increases. It must also respect 5 µs delay between two changes. For example to switch from 4.2 MHz to 32 MHz, you can switch from 4.2 MHz to 16 MHz, wait 5 µs, then switch from 16 MHz to 32 MHz.

2. Should be USB compliant from I/O voltage standpoint, the minimum  $V_{DD}$  is 3.0 V.

| Table 4. CPU frequency range depending on dynamic voltage scaling |

|-------------------------------------------------------------------|

|-------------------------------------------------------------------|

| CPU frequency range                                 | Dynamic voltage scaling range |

|-----------------------------------------------------|-------------------------------|

| 16 MHz to 32 MHz (1ws)<br>32 kHz to 16 MHz (0ws)    | Range 1                       |

| 8 MHz to 16 MHz (1ws)<br>32 kHz to 8 MHz (0ws)      | Range 2                       |

| 2.1 MHz to 4.2 MHz (1ws)<br>32 kHz to 2.1 MHz (0ws) | Range 3                       |

# 3.4 Clock management

The clock controller distributes the clocks coming from different oscillators to the core and the peripherals. It also manages clock gating for low power modes and ensures clock robustness. It features:

- Clock prescaler: to get the best trade-off between speed and current consumption, the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler

- **Safe clock switching**: clock sources can be changed safely on the fly in run mode through a configuration register.

- **Clock management**: to reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

- **Master clock source**: three different clock sources can be used to drive the master clock:

- 1-24 MHz high-speed external crystal (HSE), that can supply a PLL

- 16 MHz high-speed internal RC oscillator (HSI), trimmable by software, that can supply a PLL

- Multispeed internal RC oscillator (MSI), trimmable by software, able to generate 7 frequencies (65.5 kHz, 131 kHz, 262 kHz, 524 kHz, 1.05 MHz, 2.1 MHz, 4.2 MHz) with a consumption proportional to speed, down to 750 nA typical. When a 32.768 kHz clock source is available in the system (LSE), the MSI frequency can be trimmed by software down to a ±0.5% accuracy.

- **Auxiliary clock source**: two ultra-low-power clock sources that can be used to drive the LCD controller and the real-time clock:

- 32.768 kHz low-speed external crystal (LSE)

- 37 kHz low-speed internal RC (LSI), also used to drive the independent watchdog. The LSI clock can be measured using the high-speed internal RC oscillator for greater precision.

- **RTC and LCD clock sources:** the LSI, LSE or HSE sources can be chosen to clock the RTC and the LCD, whatever the system clock.

- **USB clock source:** the embedded PLL has a dedicated 48 MHz clock output to supply the USB interface.

- **Startup clock:** after reset, the microcontroller restarts by default with an internal 2.1 MHz clock (MSI). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

- Clock security system (CSS): this feature can be enabled by software. If a HSE clock failure occurs, the master clock is automatically switched to HSI and a software interrupt is generated if enabled.

- Clock-out capability (MCO: microcontroller clock output): it outputs one of the internal clocks for external use by the application.

Several prescalers allow the configuration of the AHB frequency, the high-speed APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the AHB and the APB domains is 32 MHz. See *Figure 2* for details on the clock tree.

|                    |        |                    |          | Table 9.   | Alterna | te functio | n inpu     | t/output (co   | ntinue | ed)   |                            |        |        |          |       |

|--------------------|--------|--------------------|----------|------------|---------|------------|------------|----------------|--------|-------|----------------------------|--------|--------|----------|-------|

|                    |        |                    |          |            |         | Digital al | ternate fu | inction number |        |       |                            |        |        |          |       |

| Port name          | AFIO0  | AFIO1              | AFIO2    | AFIO3      | AFIO4   | AFIO5      | AFOI6      | AFIO7          | AFIO8  | AFIO9 | AFIO11                     | AFIO12 | AFIO13 | AFIO14   | AFIC  |

| Port name          |        | Alternate function |          |            |         |            |            |                |        |       |                            |        |        |          |       |

|                    | SYSTEM | TIM2               | TIM3/4   | TIM9/10/11 | I2C1/2  | SPI1/2     | N/A        | USART1/2/3     | N/A    | N/A   | LCD                        | N/A    | N/A    | RI       | SYS   |

| PC11               | -      | -                  | -        | -          | -       | -          | -          | USART3_RX      | -      | -     | COM5 /<br>SEG29 /<br>SEG41 | -      | -      | TIMx_IC4 | EVEN  |

| PC12               | -      | -                  | -        | -          | -       | -          | -          | USART3_CK      | -      | -     | COM6 /<br>SEG30 /<br>SEG42 | -      | -      | TIMx_IC1 | EVEN. |

| PC13-<br>WKUP2     | -      | -                  | -        | -          | -       | -          | -          | -              | -      | -     | -                          | -      | -      | TIMx_IC2 | EVEN  |

| PC14-<br>OSC32_IN  | -      | -                  | -        | -          | -       | -          | -          | -              | -      | -     | -                          | -      | -      | TIMx_IC3 | EVEN  |

| PC15-<br>OSC32_OUT | -      | -                  | -        | -          | -       | -          | -          | -              | -      | -     | -                          | -      | -      | TIMx_IC4 | EVEN  |

| PD0                | -      | -                  | -        | TIM9_CH1   | -       | SPI2_NSS   | -          | -              | -      | -     | -                          | -      | -      | TIMx_IC1 | EVEN  |

| PD1                | -      | -                  | -        | -          | -       | SPI2_SCK   | -          | -              | -      | -     | -                          | -      | -      | TIMx_IC2 | EVEN  |

| PD2                | -      | -                  | TIM3_ETR | -          | -       | -          | -          | -              | -      | -     | COM7 /<br>SEG31/<br>SEG43  | -      | -      | TIMx_IC3 | EVEN  |

| PD3                | -      | -                  | -        | -          | -       | SPI2_MISO  | -          | USART2_CTS     | -      | -     | -                          | -      | -      | TIMx_IC4 | EVEN  |

| PD4                | -      | -                  | -        | -          | -       | SPI2_MOSI  | -          | USART2_RTS     | -      | -     | -                          | -      | -      | TIMx_IC1 | EVEN  |

| PD5                | -      | -                  | -        | -          | -       | -          | -          | USART2_TX      | -      | -     | -                          | -      | -      | TIMx_IC2 | EVEN  |

| PD6                | -      | -                  | -        | -          | -       | -          | -          | USART2_RX      | -      | -     | -                          | -      | -      | TIMx_IC3 | EVEN  |

| PD7                | -      | -                  | -        | TIM9_CH2   | -       | -          | -          | USART2_CK      | -      | -     | -                          | -      | -      | TIMx_IC4 | EVEN  |

| PD8                | -      | -                  | -        | -          | -       | -          | -          | USART3_TX      | -      | -     | -                          | -      | -      | TIMx_IC1 | EVEN  |

| PD9                | -      | -                  | -        | -          | -       | -          | -          | USART3_RX      | -      | -     | -                          | -      | -      | TIMx_IC2 | EVEN  |

| PD10               | -      | -                  | -        | -          | -       | -          | -          | USART3_CK      | -      | -     | -                          | -      | -      | TIMx_IC3 | EVEN  |

| PD11               | -      | -                  | -        | -          | -       | -          | -          | USART3_CTS     | -      | -     | -                          | -      | -      | TIMx_IC4 | EVEN  |

| PD12               | -      | -                  | TIM4_CH1 | -          | -       | -          | -          | USART3_RTS     | -      | -     | -                          | -      | -      | TIMx_IC1 | EVEN  |

#### Table 9. Alternate function input/output (continued)

45/133

STM32L151x6/8/B STM32L152x6/8/B

Pin descriptions

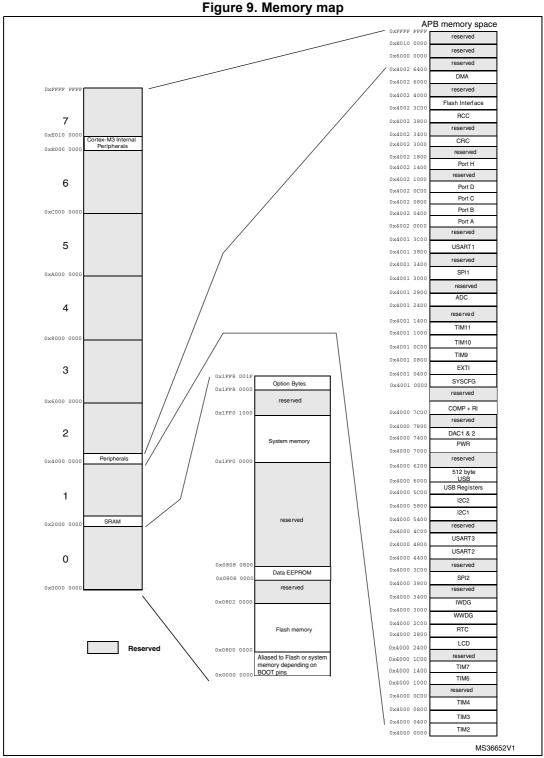

# 5 Memory mapping

The memory map is shown in *Figure 9*.

Figure 9 Momon

# 6.3.2 Embedded reset and power control block characteristics

The parameters given in the following table are derived from the tests performed under the ambient temperature condition summarized in the following table.

| Symbol                               | Parameter Conditions           |                                                     | Min  | Тур  | Мах    | Unit |  |

|--------------------------------------|--------------------------------|-----------------------------------------------------|------|------|--------|------|--|

|                                      | V rice time rate               | BOR detector enabled                                | 0    | -    | ~      |      |  |

| t <sub>VDD</sub> <sup>(1)</sup>      | V <sub>DD</sub> rise time rate | BOR detector disabled                               | 0    | -    | 1000   |      |  |

| <sup>I</sup> VDD <sup>(1)</sup>      | ) ( fall time rate             | BOR detector enabled                                | 20   | -    | ~      | µs/V |  |

|                                      | V <sub>DD</sub> fall time rate | BOR detector disabled                               | 0    | -    | 1000   |      |  |

| <b>T</b> (1)                         | Deast temperization            | V <sub>DD</sub> rising, BOR enabled                 | -    | 2    | 3.3    |      |  |

| T <sub>RSTTEMPO</sub> <sup>(1)</sup> | Reset temporization            | V <sub>DD</sub> rising, BOR disabled <sup>(2)</sup> | 0.4  | 0.7  | 1.6    | ms   |  |

| V                                    | Power on/power down reset      | Falling edge                                        | 1    | 1.5  | 1.65   | v    |  |

| V <sub>POR/PDR</sub>                 | threshold                      | Rising edge                                         | 1.3  | 1.5  | 1.65   | v    |  |

| N/                                   | Drown out react threshold 0    | Falling edge                                        | 1.67 | 1.7  | 7 1.74 |      |  |

| V <sub>BOR0</sub>                    | Brown-out reset threshold 0    | Rising edge                                         | 1.69 | 1.76 | 1.8    |      |  |

| N/                                   | Brown-out reset threshold 1    | Falling edge                                        | 1.87 | 1.93 | 1.97   |      |  |

| V <sub>BOR1</sub>                    | Brown-out reset threshold T    | Rising edge                                         | 1.96 | 2.03 | 2.07   |      |  |

| M                                    | Brown-out reset threshold 2    | Falling edge                                        | 2.22 | 2.30 | 2.35   | v    |  |

| V <sub>BOR2</sub>                    |                                | Rising edge                                         | 2.31 | 2.41 | 2.44   | v    |  |

| N/                                   | Drown out react threshold 2    | Falling edge                                        | 2.45 | 2.55 | 2.60   |      |  |

| V <sub>BOR3</sub>                    | Brown-out reset threshold 3    | Rising edge                                         | 2.54 | 2.66 | 2.7    |      |  |

| M                                    | Brown-out reset threshold 4    | Falling edge                                        | 2.68 | 2.8  | 2.85   |      |  |

| V <sub>BOR4</sub>                    |                                | Rising edge                                         | 2.78 | 2.9  | 2.95   |      |  |

Table 14. Embedded reset and power control block characteristics

# 6.3.3 Embedded internal reference voltage

The parameters given in the following table are based on characterization results, unless otherwise specified.

#### Table 15. Embedded internal reference voltage calibration values

| Calibration value name | Description                                                       | Memory address          |

|------------------------|-------------------------------------------------------------------|-------------------------|

| VREFINT_CAL            | Raw data acquired at temperature of 30 °C, V <sub>DDA</sub> = 3 V | 0x1FF8 0078-0x1FF8 0079 |

| Symbol                                   | Parameter                                                                                    | Conditions                                                                              | Min   | Тур   | Max   | Unit                  |

|------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------|-------|-------|-----------------------|

| V <sub>REFINT out</sub> <sup>(1)</sup>   | Internal reference voltage                                                                   | – 40 °C < T <sub>J</sub> < +105 °C                                                      | 1.202 | 1.224 | 1.242 | V                     |

| I <sub>REFINT</sub>                      | Internal reference current consumption                                                       | -                                                                                       | -     | 1.4   | 2.3   | μA                    |

| T <sub>VREFINT</sub>                     | Internal reference startup time                                                              | -                                                                                       | -     | 2     | 3     | ms                    |

| V <sub>VREF_MEAS</sub>                   | V <sub>DDA</sub> and V <sub>REF+</sub> voltage during<br>V <sub>REFINT</sub> factory measure | -                                                                                       | 2.99  | 3     | 3.01  | V                     |

| A <sub>VREF_MEAS</sub>                   | Accuracy of factory-measured $V_{REF}$ value $^{(2)}$                                        | Including uncertainties<br>due to ADC and<br>V <sub>DDA</sub> /V <sub>REF+</sub> values | -     | -     | ±5    | mV                    |

| T <sub>Coeff</sub> <sup>(3)</sup>        | Temperature coefficient                                                                      | –40 °C < T <sub>J</sub> < +105 °C                                                       | -     | 25    | 100   | ppm/°C                |

| A <sub>Coeff</sub> <sup>(3)</sup>        | Long-term stability                                                                          | 1000 hours, T= 25 °C                                                                    | -     | -     | 1000  | ppm                   |

| V <sub>DDCoeff</sub> <sup>(3)</sup>      | Voltage coefficient                                                                          | 3.0 V < V <sub>DDA</sub> < 3.6 V                                                        | -     | -     | 2000  | ppm/V                 |

| T <sub>S_vrefint</sub> <sup>(3)(4)</sup> | ADC sampling time when reading the internal reference voltage                                | -                                                                                       | 5     | 10    | -     | μs                    |

| T <sub>ADC_BUF</sub> <sup>(3)</sup>      | Startup time of reference voltage buffer for ADC                                             | -                                                                                       | -     | -     | 10    | μs                    |

| I <sub>BUF_ADC</sub> <sup>(3)</sup>      | Consumption of reference voltage buffer for ADC                                              | -                                                                                       | -     | 13.5  | 25    | μA                    |

| I <sub>VREF_OUT</sub> <sup>(3)</sup>     | VREF_OUT output current <sup>(5)</sup>                                                       | -                                                                                       | -     | -     | 1     | μA                    |

| C <sub>VREF_OUT</sub> <sup>(3)</sup>     | VREF_OUT output load                                                                         | -                                                                                       | -     | -     | 50    | pF                    |

| I <sub>LPBUF</sub> <sup>(3)</sup>        | Consumption of reference voltage buffer for VREF_OUT and COMP                                | -                                                                                       | -     | 730   | 1200  | nA                    |

| V <sub>REFINT_DIV1</sub> <sup>(3)</sup>  | 1/4 reference voltage                                                                        | -                                                                                       | 24    | 25    | 26    |                       |

| V <sub>REFINT_DIV2</sub> <sup>(3)</sup>  | 1/2 reference voltage                                                                        | -                                                                                       | 49    | 50    | 51    | % V <sub>REFINT</sub> |

| V <sub>REFINT_DIV3</sub> <sup>(3)</sup>  | 3/4 reference voltage                                                                        | -                                                                                       | 74    | 75    | 76    |                       |

#### Table 16. Embedded internal reference voltage

1. Tested in production.

2. The internal  $V_{REF}$  value is individually measured in production and stored in dedicated EEPROM bytes.

3. Guaranteed by characterization results.

4. Shortest sampling time can be determined in the application by multiple iterations.

5. To guarantee less than 1% VREF\_OUT deviation.

|                                            | Typical consumption, V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 25 °C |                                                       |                                                       |                                                       |                            |                      |

|--------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|----------------------------|----------------------|

| Peripheral                                 |                                                                      | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | Range 3,<br>V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | Low power<br>sleep and run | Unit                 |

|                                            | GPIOA                                                                | 5                                                     | 4.5                                                   | 3.5                                                   | 4                          |                      |

|                                            | GPIOB                                                                | 5                                                     | 4.5                                                   | 3.5                                                   | 4.5                        |                      |

|                                            | GPIOC                                                                | 5                                                     | 4.5                                                   | 3.5                                                   | 4.5                        |                      |

|                                            | GPIOD                                                                | 5                                                     | 4.5                                                   | 3.5                                                   | 4.5                        |                      |

| AHB                                        | GPIOE                                                                | 5                                                     | 4.5                                                   | 3.5                                                   | 4.5                        | µA/MHz               |

|                                            | GPIOH                                                                | 4                                                     | 4                                                     | 3                                                     | 3.5                        | (f <sub>HCLK</sub> ) |

|                                            | CRC                                                                  | 1                                                     | 0.5                                                   | 0.5                                                   | 0.5                        |                      |

|                                            | FLASH                                                                | 13                                                    | 11.5                                                  | 9                                                     | 18.5                       |                      |

|                                            | DMA1                                                                 | 12                                                    | 10                                                    | 8                                                     | 10.5                       |                      |

| All enabled                                |                                                                      | 166                                                   | 138                                                   | 106                                                   | 130                        |                      |

| I <sub>DD (RTC)</sub>                      |                                                                      |                                                       |                                                       |                                                       |                            |                      |

| I <sub>DD (LCD)</sub>                      |                                                                      |                                                       |                                                       |                                                       |                            |                      |

| I <sub>DD (ADC)</sub> <sup>(3)</sup>       |                                                                      |                                                       |                                                       |                                                       |                            |                      |

| I <sub>DD (DAC)</sub> <sup>(4)</sup>       |                                                                      |                                                       |                                                       |                                                       |                            |                      |

| I <sub>DD (COMP1)</sub>                    |                                                                      |                                                       | μA                                                    |                                                       |                            |                      |

| Slow mode                                  |                                                                      |                                                       |                                                       |                                                       |                            |                      |

| I <sub>DD (COMP2)</sub>                    | Fast mode                                                            |                                                       |                                                       |                                                       |                            |                      |

| I <sub>DD (PVD / BOR)</sub> <sup>(5)</sup> |                                                                      |                                                       |                                                       |                                                       |                            |                      |

| I <sub>DD (IWDG)</sub>                     |                                                                      |                                                       | 0.1                                                   | 25                                                    |                            |                      |

## Table 24. Peripheral current consumption<sup>(1)</sup> (continued)

Data based on differential I<sub>DD</sub> measurement between all peripherals OFF an one peripheral with clock enabled, in the following conditions: f<sub>HCLK</sub> = 32 MHz (Range 1), f<sub>HCLK</sub> = 16 MHz (Range 2), f<sub>HCLK</sub> = 4 MHz (Range 3), f<sub>HCLK</sub> = 64kHz (Low power run/sleep), f<sub>APB1</sub> = f<sub>HCLK</sub>, f<sub>APB2</sub> = f<sub>HCLK</sub>, default prescaler value for each peripheral. The CPU is in Sleep mode in both cases. No I/O pins toggling.

2. HSI oscillator is OFF for this measure.

3. Data based on a differential IDD measurement between ADC in reset configuration and continuous ADC conversion (HSI consumption not included).

4. Data based on a differential Ibb measurement between DAC in reset configuration and continuous DAC conversion of Vbb/2. DAC is in buffered mode, output is left floating.

5. Including supply current of internal reference voltage.

# 6.3.5 Wakeup time from Low power mode

The wakeup times given in the following table are measured with the MSI RC oscillator. The clock source used to wake up the device depends on the current operating mode:

- Sleep mode: the clock source is the clock that was set before entering Sleep mode

- Stop mode: the clock source is the MSI oscillator in the range configured before entering Stop mode

- Standby mode: the clock source is the MSI oscillator running at 2.1 MHz

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 13*.

| Symbol               | Parameter                                                | Conditions                                                              | Тур  | Max <sup>(1)</sup> | Unit |

|----------------------|----------------------------------------------------------|-------------------------------------------------------------------------|------|--------------------|------|

| t <sub>WUSLEEP</sub> | Wakeup from Sleep mode                                   | f <sub>HCLK</sub> = 32 MHz                                              | 0.36 | -                  |      |

| t                    | Wakeup from Low power sleep mode                         | f <sub>HCLK</sub> = 262 kHz<br>Flash enabled                            | 32   | -                  |      |

| twusleep_lp          | f <sub>HCLK</sub> = 262 kHz                              | f <sub>HCLK</sub> = 262 kHz<br>Flash switched OFF                       | 34   | -                  |      |

|                      | Wakeup from Stop mode, regulator in Run mode             | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz                          | 8.2  | -                  |      |

|                      |                                                          | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage Range 1 and 2 | 8.2  | 9.3                |      |

|                      |                                                          | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage Range 3       | 7.8  | 11.2               | μs   |

| t <sub>WUSTOP</sub>  | Wakeup from Stop mode,<br>regulator in low power<br>mode |                                                                         |      | 12                 |      |

|                      |                                                          | f <sub>HCLK</sub> = f <sub>MSI</sub> = 1.05 MHz                         | 15.5 | 20                 |      |

|                      |                                                          | f <sub>HCLK</sub> = f <sub>MSI</sub> = 524 kHz                          | 29   | 35                 |      |

|                      |                                                          | f <sub>HCLK</sub> = f <sub>MSI</sub> = 262 kHz                          | 53   | 63                 |      |

|                      |                                                          | f <sub>HCLK</sub> = f <sub>MSI</sub> = 131 kHz                          | 105  | 118                |      |

|                      |                                                          | f <sub>HCLK</sub> = MSI = 65 kHz                                        | 210  | 237                |      |

| twustdby             | Wakeup from Standby<br>mode<br>FWU bit = 1               | f <sub>HCLK</sub> = MSI = 2.1 MHz                                       | 50   | 103                |      |

|                      | Wakeup from Standby<br>mode<br>FWU bit = 0               | f <sub>HCLK</sub> = MSI = 2.1 MHz                                       | 2.5  | 3.2                | ms   |

Table 25. Low-power mode wakeup timings

1. Guaranteed by characterization results, unless otherwise specified

| Symbol               | Parameter                                                                                              | Conditions                                                                    | Min | Тур | Мах                                | Unit     |

|----------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----|-----|------------------------------------|----------|

| f <sub>OSC_IN</sub>  | Oscillator frequency                                                                                   | -                                                                             | 1   |     | 24                                 | MHz      |

| R <sub>F</sub>       | Feedback resistor                                                                                      | -                                                                             |     | 200 | -                                  | kΩ       |

| С                    | Recommended load<br>capacitance versus<br>equivalent serial resistance<br>of the crystal $(R_S)^{(3)}$ | R <sub>S</sub> = 30 Ω                                                         | -   | 20  | -                                  | pF       |

| I <sub>HSE</sub>     | HSE driving current                                                                                    | V <sub>DD</sub> = 3.3 V, V <sub>IN</sub> = V <sub>SS</sub><br>with 30 pF load | -   | -   | 3                                  | mA       |

|                      | HSE oscillator power                                                                                   | C = 20 pF<br>f <sub>OSC</sub> = 16 MHz                                        | -   | -   | 2.5 (startup)<br>0.7 (stabilized)  | mA       |

| IDD(HSE)             | consumption                                                                                            | C = 10 pF<br>f <sub>OSC</sub> = 16 MHz                                        | -   | -   | 2.5 (startup)<br>0.46 (stabilized) | mA       |

| 9 <sub>m</sub>       | Oscillator transconductance                                                                            | Startup                                                                       | 3.5 | -   | -                                  | mA<br>/V |

| t <sub>SU(HSE)</sub> | Startup time                                                                                           | $V_{DD}$ is stabilized                                                        | -   | 1   | -                                  | ms       |

| Table 28. | HSE | oscillator | characteristics <sup>(1)(2)</sup> |

|-----------|-----|------------|-----------------------------------|

|-----------|-----|------------|-----------------------------------|

1. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

2. Guaranteed by characterization results.

3. The relatively low value of the RF resistor offers a good protection against issues resulting from use in a humid environment, due to the induced leakage and the bias condition change. However, it is recommended to take this point into account if the MCU is used in tough humidity conditions.

t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 17*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ . Refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website *www.st.com*.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

|                             |                         |                                       |                             | Max vs                      |                              |                              |      |

|-----------------------------|-------------------------|---------------------------------------|-----------------------------|-----------------------------|------------------------------|------------------------------|------|

| Symbol                      | Parameter               | Conditions                            | Monitored<br>frequency band | 4 MHz<br>voltage<br>Range 3 | 16 MHz<br>voltage<br>Range 2 | 32 MHz<br>voltage<br>Range 1 | Unit |

|                             |                         | V <sub>DD</sub> = 3.3 V,              | 0.1 to 30 MHz               | 3                           | -6                           | -5                           |      |

| S <sub>EMI</sub> Peak level | $T_A = 25 \ ^\circ C$ , | 30 to 130 MHz                         | 18                          | 4                           | -7                           | dBµV                         |      |

|                             | Peak level              | LQFP100 package<br>compliant with IEC | 130 MHz to 1GHz             | 15                          | 5                            | -7                           |      |

|                             |                         | 61967-2                               | SAE EMI Level               | 2.5                         | 2                            | 1                            | -    |

#### Table 38. EMI characteristics

# 6.3.11 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

## Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114/C101 standard.

| Symbol                | Ratings                                               | Conditions                                         | Packages | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|----------------------------------------------------|----------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)    | $T_A = +25$ °C, conforming to JESD22-A114          | All      | 2     | 2000                            | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model) | T <sub>A</sub> = +25 °C, conforming to JESD22-C101 | All      | 111   | 500                             | v    |

#### Table 39. ESD absolute maximum ratings

1. Guaranteed by characterization results.

# 6.3.13 I/O port characteristics

# General input/output characteristics

Unless otherwise specified, the parameters given in *Table 42* are derived from tests performed under conditions summarized in *Table 13*. All I/Os are CMOS and TTL compliant.

| Table 42. I/O Static characteristics |                                                    |                                                                                                                                                                                      |                   |                     |                                    |                                   |      |  |  |

|--------------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------|------------------------------------|-----------------------------------|------|--|--|

| Symbol                               | Parameter                                          | Conc                                                                                                                                                                                 | litions           | Min                 | Тур                                | Мах                               | Unit |  |  |

| V <sub>IL</sub>                      | Input low level voltage                            | -                                                                                                                                                                                    | -                 | -                   | -                                  | 0.3V <sub>DD</sub> <sup>(1)</sup> |      |  |  |

| V                                    | Input high lovel veltage                           | Standard I/O                                                                                                                                                                         |                   | 0.7.\/              | -                                  | -                                 |      |  |  |

| VIH                                  | Input high level voltage                           | FT                                                                                                                                                                                   | · I/O             | 0.7 V <sub>DD</sub> | -                                  | -                                 | V    |  |  |

| V.                                   | I/O Schmitt trigger voltage                        | Stand                                                                                                                                                                                | ard I/O           | -                   | 10% V <sub>DD</sub> <sup>(3)</sup> | -                                 |      |  |  |

| V <sub>hys</sub>                     | hysteresis <sup>(2)</sup>                          | $\begin{tabular}{ c c c c } \hline FT I/O & \\ \hline V_{SS} \leq V_{IN} \leq V_{DD} & \\ \hline I/Os with LCD & \\ \hline V_{SS} \leq V_{IN} \leq V_{DD} & \\ \hline \end{tabular}$ |                   | -                   | 5% V <sub>DD</sub> <sup>(4)</sup>  | -                                 |      |  |  |

|                                      |                                                    |                                                                                                                                                                                      |                   | -                   | -                                  | ±50                               |      |  |  |

| I <sub>lkg</sub>                     | Input leakage current <sup>(5)</sup>               | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>I/Os with analog<br>switches                                                                                                    |                   | -                   |                                    | ±50                               |      |  |  |

|                                      |                                                    | $V_{SS} \leq V_{IN} \leq V_{DD}$<br>I/Os with analog<br>switches and LCD<br>$V_{SS} \leq V_{IN} \leq V_{DD}$<br>I/Os with USB                                                        |                   | -                   | -                                  | ±50                               | nA   |  |  |

|                                      |                                                    |                                                                                                                                                                                      |                   | -                   | -                                  | TBD                               |      |  |  |

|                                      |                                                    | FT I/O<br>V <sub>DD</sub> ≤V <sub>IN</sub> ≤5V                                                                                                                                       |                   | -                   | -                                  | TBD                               |      |  |  |

|                                      |                                                    | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>Standard I/Os                                                                                                                   |                   | -                   | -                                  | ±50                               |      |  |  |

| R <sub>PU</sub>                      | Weak pull-up equivalent resistor <sup>(6)(1)</sup> | $V_{IN} = V_{SS}$                                                                                                                                                                    |                   | 30                  | 45                                 | 60                                | kΩ   |  |  |

| R <sub>PD</sub>                      | Weak pull-down equivalent resistor <sup>(6)</sup>  | V <sub>IN</sub> =                                                                                                                                                                    | = V <sub>DD</sub> | 30                  | 45                                 | 60                                | kΩ   |  |  |

| C <sub>IO</sub>                      | I/O pin capacitance                                | -                                                                                                                                                                                    | -                 | -                   | 5                                  | -                                 | pF   |  |  |

|  | Table 42. | I/O | static | characteristics |

|--|-----------|-----|--------|-----------------|

|--|-----------|-----|--------|-----------------|

1. Tested in production

2. Hysteresis voltage between Schmitt trigger switching levels. Based on characterization.

3. With a minimum of 200 mV. Based on characterization results.

4. With a minimum of 100 mV. Based on characterization results.

5. The max. value may be exceeded if negative current is injected on adjacent pins.

Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This MOS/NMOS contribution to the series resistance is minimum (~10% order).

# Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 19* and *Table 44*, respectively.

Unless otherwise specified, the parameters given in *Table 44* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 13*.

| OSPEEDRx<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                                                   | Parameter                                                       | Conditions                                  | Min | Max <sup>(2)</sup> | Unit |

|-----------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------|-----|--------------------|------|

|                                               | f                                                        | Maximum frequency <sup>(3)</sup>                                | $C_L$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V    | -   | 400                | kHz  |

| 00                                            | f <sub>max(IO)out</sub>                                  |                                                                 | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V | -   | 400                | KUZ  |

| 00                                            | t <sub>f(IO)out</sub>                                    | Output rise and fall time                                       | $C_L$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V    | -   | 625                | ns   |

|                                               | t <sub>r(IO)out</sub>                                    |                                                                 | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V | -   | 625                | 115  |

|                                               | f                                                        | Maximum frequency <sup>(3)</sup>                                | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V  | -   | 2                  |      |

| f <sub>max(IO)out</sub>                       |                                                          |                                                                 | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V | -   | 1                  | MHz  |

| 01                                            | t <sub>f(IO)out</sub>                                    | Output rise and fall time                                       | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V  | -   | 125                | ns   |

| t <sub>r(IO)out</sub>                         |                                                          |                                                                 | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V | -   | 250                | 115  |

|                                               | E                                                        | Maximum frequency <sup>(3)</sup>                                | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V  | -   | 10                 | MHz  |

| 10                                            | rmax(IO)out                                              | max(IO)out Maximum frequency <sup>(3)</sup>                     | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V | -   | 2                  |      |

| 10                                            | t <sub>f(IO)out</sub>                                    | Output rise and fall time                                       | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V  | -   | 25                 | ns   |

|                                               | t <sub>r(IO)out</sub>                                    |                                                                 | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V | -   | 125                | 115  |

|                                               | E                                                        | Maximum frequency <sup>(3)</sup>                                | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V  | -   | 50                 | MHz  |

| 44                                            | F <sub>max(IO)out</sub> Maximum frequency <sup>(3)</sup> | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V                     | -                                           | 8   |                    |      |

| 11                                            | t <sub>f(IO)out</sub> Output rise and fall time          | $C_{L}$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V                      | -                                           | 5   |                    |      |

|                                               | t <sub>r(IO)out</sub>                                    | Output rise and fall time                                       | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V | -   | 30                 |      |

| -                                             | t <sub>EXTIpw</sub>                                      | Pulse width of external signals detected by the EXTI controller | -                                           | 8   | -                  | ns   |

| Table 44. | I/O AC | characteristics <sup>(1)</sup> |

|-----------|--------|--------------------------------|

|-----------|--------|--------------------------------|

1. The I/O speed is configured using the OSPEEDRx[1:0] bits. Refer to the STM32L151x6/8/B and STM32L152x6/8/B reference manual for a description of GPIO Port configuration register.

2. Guaranteed by design.

3. The maximum frequency is defined in *Figure 19*.

#### STM32L151x6/8/B STM32L152x6/8/B

| Symbol | Parameter                            | Test conditions                                                                                         | Min <sup>(3)</sup> | Тур | Max <sup>(3)</sup> | Unit |

|--------|--------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------|-----|--------------------|------|

| ET     | Total unadjusted error               |                                                                                                         | -                  | 2   | 4                  |      |

| EO     | Offset error                         | $2.4 \text{ V} \le \text{V}_{\text{DDA}} \le 3.6 \text{ V}$                                             | -                  | 1   | 2                  |      |

| EG     | Gain error                           | 2.4 V ≤ V <sub>REF+</sub> ≤ 3.6 V<br>f <sub>ADC</sub> = 8 MHz, R <sub>AIN</sub> = 50 Ω                  | -                  | 1.5 | 3.5                | LSB  |

| ED     | Differential linearity error         | $T_A = -40$ to 105 ° C                                                                                  | -                  | 1   | 2                  |      |

| EL     | Integral linearity error             |                                                                                                         | -                  | 1.7 | 3                  |      |

| ENOB   | Effective number of bits             | 2.4 V ≤ V <sub>DDA</sub> ≤ 3.6 V                                                                        | 9.2                | 10  | -                  | bits |

| SINAD  | Signal-to-noise and distortion ratio | $V_{\text{DDA}} = V_{\text{REF}+}$<br>f <sub>ADC</sub> = 16 MHz, R <sub>AIN</sub> = 50 Ω                | 57.5               | 62  | -                  |      |

| SNR    | Signal-to-noise ratio                | $T_{A} = -40 \text{ to } 105 \degree \text{C}$ $1 \text{ kHz} \le F_{\text{input}} \le 100 \text{ kHz}$ | 57.5               | 62  | -                  | dB   |

| THD    | Total harmonic distortion            |                                                                                                         | -74                | -75 | -                  |      |

| ET     | Total unadjusted error               |                                                                                                         | -                  | 4   | 6.5                |      |

| EO     | Offset error                         | 2.4 V ≤ V <sub>DDA</sub> ≤ 3.6 V                                                                        | -                  | 2   | 4                  |      |

| EG     | Gain error                           | 1.8 V ≤ V <sub>REF+</sub> ≤ 2.4 V<br>f <sub>ADC</sub> = 4 MHz, R <sub>AIN</sub> = 50 Ω                  | -                  | 4   | 6                  | LSB  |

| ED     | Differential linearity error         | $T_A = -40$ to 105 °C                                                                                   | -                  | 1   | 2                  |      |

| EL     | Integral linearity error             |                                                                                                         | -                  | 1.5 | 3                  |      |

| ET     | Total unadjusted error               |                                                                                                         | -                  | 2   | 3                  |      |

| EO     | Offset error                         | $1.8 V \le V_{DDA} \le 2.4 V$                                                                           | -                  | 1   | 1.5                |      |

| EG     | Gain error                           | 1.8 V ≤ V <sub>REF+</sub> ≤ 2.4 V<br>f <sub>ADC</sub> = 4 MHz, R <sub>AIN</sub> = 50 Ω                  | -                  | 1.5 | 2                  | LSB  |

| ED     | Differential linearity error         | $T_{A} = -40$ to 105 ° C                                                                                | -                  | 1   | 2                  |      |

| EL     | Integral linearity error             |                                                                                                         | -                  | 1   | 1.5                |      |

1. ADC DC accuracy values are measured after internal calibration.

ADC accuracy vs. negative injection current: Injecting a negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in Section 6.3.12 does not affect the ADC accuracy.

3. Guaranteed by characterization results.

| Symbol                                                                         | Parameter                                                                                                                                                       | Conditions                                                                         | Min | Тур             | Мах              | Unit  |

|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----|-----------------|------------------|-------|

| dOffeet/dT <sup>(1)</sup>                                                      | Offset error temperature                                                                                                                                        | $V_{DDA} = 3.3V$ , $T_A = 0$ to 50 ° C<br>DAC output buffer OFF                    | -20 | -10             | 0                | µV/°C |

| dOffset/dT <sup>(1)</sup> Offset error temperature<br>coefficient (code 0x800) |                                                                                                                                                                 | $V_{DDA} = 3.3V$ , $T_A = 0$ to 50 ° C<br>DAC output buffer ON                     | 0   | 20              | 50               | μν/ Ο |

| Gain <sup>(1)</sup>                                                            | Gain error <sup>(6)</sup>                                                                                                                                       | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON         | -   | +0.1 /<br>-0.2% | +0.2 / -<br>0.5% | %     |

| Gain                                                                           | Gain enor                                                                                                                                                       | No R <sub>LOAD</sub> , C <sub>L</sub> ≤50 pF<br>DAC output buffer OFF              | -   | +0 / -0.2%      | +0 / -0.4%       | 70    |

| dCoin/dT <sup>(1)</sup>                                                        | Gain error temperature                                                                                                                                          | $V_{DDA} = 3.3V$ , $T_A = 0$ to 50 ° C<br>DAC output buffer OFF                    | -10 | -2              | 0                | μV/°C |

|                                                                                | coefficient                                                                                                                                                     | $V_{DDA} = 3.3V$ , $T_A = 0$ to 50 ° C<br>DAC output buffer ON                     | -40 | -8              | 0                | μν/ Ο |

| TUE <sup>(1)</sup>                                                             | Total unadjusted error                                                                                                                                          | $C_L \le 50 \text{ pF}, \text{ R}_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON | -   | 12              | 30               | LSB   |

|                                                                                |                                                                                                                                                                 | No R <sub>LOAD</sub> , C <sub>L</sub> ≤50 pF<br>DAC output buffer OFF              | -   | 8               | 12               | LOD   |

| tSETTLING                                                                      | Settling time (full scale:<br>for a 12-bit code<br>transition between the<br>lowest and the highest<br>input codes till<br>DAC_OUT reaches final<br>value ±1LSB | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                 | -   | 7               | 12               | μs    |

| Update rate                                                                    | Max frequency for a<br>correct DAC_OUT<br>change (95% of final<br>value) with 1 LSB<br>variation in the input<br>code                                           | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                 | -   | -               | 1                | Msps  |

| t <sub>wakeup</sub>                                                            | Wakeup time from off<br>state (setting the ENx bit<br>in the DAC Control<br>register) <sup>(7)</sup>                                                            | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                 | -   | 9               | 15               | μs    |

| PSRR+                                                                          | V <sub>DDA</sub> supply rejection<br>ratio (static DC<br>measurement)                                                                                           | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                 | -   | -60             | -35              | dB    |

#### Table 57. DAC characteristics (continued)

1. Guaranteed by characterization results.

2. Difference between two consecutive codes - 1 LSB.

3. Difference between measured value at Code i and the value at Code i on a line drawn between Code 0 and last Code 4095.

4. Difference between the value measured at Code (0x800) and the ideal value = V/2.

5. Difference between the value measured at Code (0x001) and the ideal value.

6. Difference between ideal slope of the transfer function and measured slope computed from code 0x000 and 0xFFF when buffer is OFF, and from code giving 0.2 V and ( $V_{DDA} - 0.2$ ) V when buffer is ON.

7. In buffered mode, the output can overshoot above the final value for low input code (starting from min value).

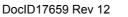

Figure 31. 12-bit buffered /non-buffered DAC

1. The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.

# 6.3.19 Temperature sensor characteristics

| Calibration value name | Description                                                                    | Memory address          |

|------------------------|--------------------------------------------------------------------------------|-------------------------|

| TS_CAL1                | TS ADC raw data acquired at<br>temperature of 30 °C,<br>V <sub>DDA</sub> = 3 V | 0x1FF8 007A-0x1FF8 007B |

| TS_CAL2                | TS ADC raw data acquired at<br>temperature of 110 °C<br>V <sub>DDA</sub> = 3 V | 0x1FF8 007E-0x1FF8 007F |

#### Table 58. Temperature sensor calibration values

| Symbol                                | Parameter                                      | Min  | Тур   | Max       | Unit  |

|---------------------------------------|------------------------------------------------|------|-------|-----------|-------|

| T <sub>L</sub> <sup>(1)</sup>         | V <sub>SENSE</sub> linearity with temperature  | -    | ±1    | <u>+2</u> | °C    |

| Avg_Slope <sup>(1)</sup>              | Average slope                                  | 1.48 | 1.61  | 1.75      | mV/°C |

| V <sub>110</sub>                      | Voltage at 110°C ±5°C <sup>(2)</sup>           | 612  | 626.8 | 641.5     | mV    |

| I <sub>DDA(TEMP)</sub> <sup>(3)</sup> | Current consumption                            | -    | 3.4   | 6         | μA    |

| t <sub>START</sub> <sup>(3)</sup>     | Startup time                                   | -    | -     | 10        |       |

| T <sub>S_temp</sub> <sup>(4)(3)</sup> | ADC sampling time when reading the temperature | 10   | -     | -         | μs    |

1. Guaranteed by characterization results.

2. Measured at  $V_{DD}$  = 3 V ±10 mV. V110 ADC conversion result is stored in the TS\_CAL2 byte.

- 3. Guaranteed by design.

- 4. Shortest sampling time can be determined in the application by multiple iterations.

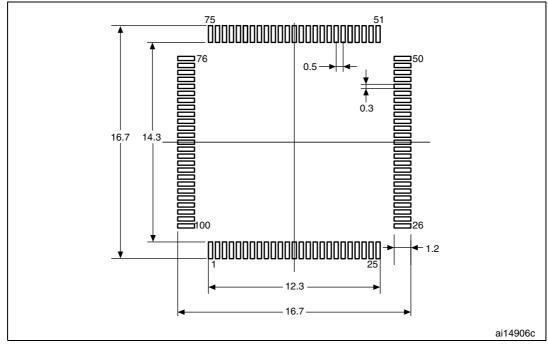

# Figure 33. LQPF100 14 x 14 mm, 100-pin low-profile quad flat package recommended footprint

1. Dimensions are in millimeters.

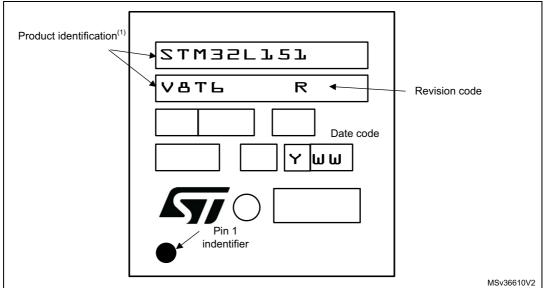

## LQFP100 device marking

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Figure 34. LQFP100 14 x 14 mm, 100-pin package top view example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

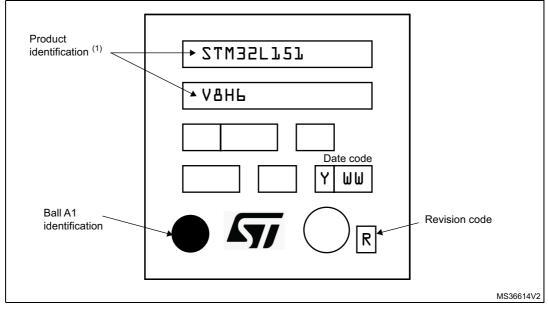

#### **UFBGA100** device marking

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Figure 46. UFBGA100 7 x 7 mm, 0.5 mm pitch, package top view example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

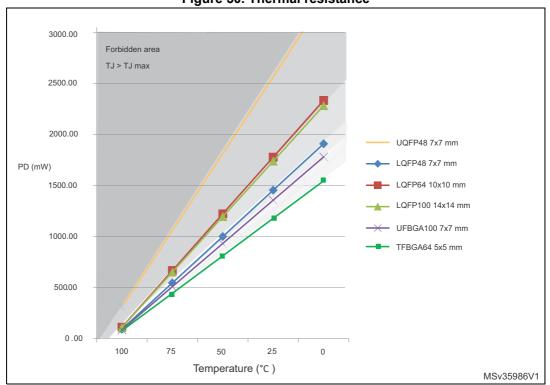

Figure 50. Thermal resistance

# 7.7.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.