Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Not For New Designs                                                     |

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                    |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, POR, PWM, WDT |

| Number of I/O              | 51                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 4K x 8                                                                  |

| RAM Size                   | 10K × 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Data Converters            | A/D 20x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l151r6t6   |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1 Introduction                                             | 9  |

|------------------------------------------------------------|----|

| 2 Description                                              | 10 |

| 2.1 Device overview                                        |    |

| 2.2 Ultra-low-power device continuum                       | 12 |

| 2.2.1 Performance                                          |    |

| 2.2.2 Shared peripherals                                   | 12 |

| 2.2.3 Common system strategy                               | 12 |

| 2.2.4 Features                                             | 12 |

| 3 Functional overview                                      | 13 |

| 3.1 Low power modes                                        | 14 |

| 3.2 ARM <sup>®</sup> Cortex <sup>®</sup> -M3 core with MPU | 18 |

| 3.3 Reset and supply management                            | 19 |

| 3.3.1 Power supply schemes                                 |    |

| 3.3.2 Power supply supervisor                              | 19 |

| 3.3.3 Voltage regulator                                    | 20 |

| 3.3.4 Boot modes                                           | 20 |

| 3.4 Clock management                                       |    |

| 3.5 Low power real-time clock and backup registers         |    |

| 3.6 GPIOs (general-purpose inputs/outputs)                 |    |

| 3.7 Memories                                               |    |

| 3.8 DMA (direct memory access)                             |    |

| 3.9 LCD (liquid crystal display)                           |    |

| 3.10 ADC (analog-to-digital converter)                     |    |

| 3.10.1 Temperature sensor                                  |    |

| 3.10.2 Internal voltage reference (V <sub>REFINT</sub> )   |    |

| 3.11 DAC (digital-to-analog converter)                     |    |

| 3.12 Ultra-low-power comparators and reference voltage     |    |

| 3.13 Routing interface                                     |    |

| 3.14 Touch sensing                                         |    |

|                                                            |    |

| Figure 48. | TFBGA64, 5 x 5 mm, 0.5 mm pitch, recommended footprint   | 121 |

|------------|----------------------------------------------------------|-----|

| Figure 49. | TFBGA64 5 x 5 mm, 0.5 mm pitch, package top view example | 122 |

| Figure 50. | Thermal resistance                                       | 124 |

## 3.7 Memories

The STM32L151x6/8/B and STM32L152x6/8/B devices have the following features:

- Up to 16 Kbytes of embedded RAM accessed (read/write) at CPU clock speed with 0 wait states. With the enhanced bus matrix, operating the RAM does not lead to any performance penalty during accesses to the system bus (AHB and APB buses).

- The non-volatile memory is divided into three arrays:

- 32, 64 or 128 Kbytes of embedded Flash program memory

- 4 Kbytes of data EEPROM

- Options bytes

The options bytes are used to write-protect the memory (with 4 Kbytes granularity) and/or readout-protect the whole memory with the following options:

- Level 0: no readout protection

- Level 1: memory readout protection, the Flash memory cannot be read from or written to if either debug features are connected or boot in RAM is selected

- Level 2: chip readout protection, debug features (Cortex<sup>®</sup>-M3 JTAG and serial wire) and boot in RAM selection disabled (JTAG fuse)

The whole non-volatile memory embeds the error correction code (ECC) feature.

## 3.8 DMA (direct memory access)

The flexible 7-channel, general-purpose DMA is able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The DMA controller supports circular buffer management, avoiding the generation of interrupts when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with software trigger support for each channel. Configuration is done by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals: SPI,  $I^2C$ , USART, general-purpose timers and ADC.

# 3.9 LCD (liquid crystal display)

The LCD drives up to 8 common terminals and 44 segment terminals to drive up to 320 pixels.

- Internal step-up converter to guarantee functionality and contrast control irrespective of V<sub>DD</sub>. This converter can be deactivated, in which case the V<sub>LCD</sub> pin is used to provide the voltage to the LCD

- Supports static, 1/2, 1/3, 1/4 and 1/8 duty

- Supports static, 1/2, 1/3 and 1/4 bias

- Phase inversion to reduce power consumption and EMI

- Up to 8 pixels can be programmed to blink

- Unneeded segments and common pins can be used as general I/O pins

- LCD RAM can be updated at any time owing to a double-buffer

- The LCD controller can operate in Stop mode

### 3.15.5 Window watchdog (WWDG)

The window watchdog is based on a 7-bit down-counter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

### 3.16 Communication interfaces

### 3.16.1 I<sup>2</sup>C bus

Up to two I<sup>2</sup>C bus interfaces can operate in multimaster and slave modes. They can support standard and fast modes.

They support dual slave addressing (7-bit only) and both 7- and 10-bit addressing in master mode. A hardware CRC generation/verification is embedded.

They can be served by DMA and they support SM Bus 2.0/PM Bus.

#### 3.16.2 Universal synchronous/asynchronous receiver transmitter (USART)

All USART interfaces are able to communicate at speeds of up to 4 Mbit/s. They provide hardware management of the CTS and RTS signals and are ISO 7816 compliant. They support IrDA SIR ENDEC and have LIN Master/Slave capability.

All USART interfaces can be served by the DMA controller.

### 3.16.3 Serial peripheral interface (SPI)

Up to two SPIs are able to communicate at up to 16 Mbits/s in slave and master modes in full-duplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes.

Both SPIs can be served by the DMA controller.

#### 3.16.4 Universal serial bus (USB)

The STM32L151x6/8/B and STM32L152x6/8/B devices embed a USB device peripheral compatible with the USB full speed 12 Mbit/s. The USB interface implements a full speed (12 Mbit/s) function interface. It has software-configurable endpoint setting and supports suspend/resume. The dedicated 48 MHz clock is generated from the internal main PLL (the clock source must use a HSE crystal oscillator).

# 4 Pin descriptions

|   | 1                  | 2                   | 3            | 4      | 5          | 6     | 7     | 8      | 9             | 10           | 11     | 12     |          |

|---|--------------------|---------------------|--------------|--------|------------|-------|-------|--------|---------------|--------------|--------|--------|----------|

|   | (T)                | <i>(</i> <b>-</b> ) | <i>(</i> , ) | (~)    | <i>(</i> ) | /TN   |       | (-)    | /~~           | (~)          | /T.\   | ~~     |          |

| Α | (PE3)              | (PE1)               | (PB8)        | iBOOT0 | (PD7)      | (PD5) | (PB4) | (PB3)  | (PA15)        | (PA14)       | (PA13) | (PA12) |          |

| в | (PE4)              | (PE2)               | (PB9)        | (PB7)  | (PB6)      | (PD6) | (PD4) | (PD3)  | (PD1)         | PC12)        | (PC10) | (PA11) |          |

| с | PC13<br>WKUP2      | (PE5)               | (PEO)        | VDD_B  | (PB5)      |       |       | (PD2)  | (PDO)         | PC11)        | (PH2)  | (PA10) |          |

| D | PC14)<br>0\$C32_IN | PE6)<br>WUKP3       | NSS_B        |        |            |       |       |        |               | (PA9)        | (PA8)  | (PC9)  |          |

| Е | PC15)<br>OSC32_C   | VLCD                | ŃSS_¥        |        |            |       |       |        |               | (PC8)        | (PC7)  | (PC6)  |          |

| F | PHO)<br>QSCZIN     | alesvi              |              |        |            |       | 1     |        |               |              | WSS_P  | ŃSS_N  |          |

| G | PH1)               |                     |              |        |            |       | ⊢ −   |        |               |              |        |        |          |

| н | (PC0)              | NRST                |              |        |            |       |       |        |               | PD15)        | PD14)  | (PD13) |          |

| J | VSSA)              | (PC1)               | (PC2)        |        |            |       |       |        |               | PD12)        | PD11)  | (PD10) |          |

| к | VREF               | (PC3)               | (PA2)        | (PA5)  | (PC4)      |       |       | (PD9)  | (PD8)         | (PB15)       | (PB14) | (PB13) |          |

| L | 、<br>(VRE俳+        | (PA0)<br>WKUP1      | (PA3)        | (PA6)  | (PC5)      | (PB2) | (PE8) | (PE10) | /=\<br>(PE12) | (PB10)       | (PB11) | (PB12) |          |

| М | NDDA               | (PA1)               | (PA4)        | (PA7)  | (PB0)      | (PB1) | (PE7) | (PE9)  | (PE11)        | /~\<br>(PE13 | (PE14  | PE13   |          |

|   |                    |                     |              |        |            |       |       |        |               |              |        |        |          |

|   |                    |                     |              |        |            |       |       |        |               |              |        |        | ai17096f |

Figure 3. STM32L15xVx UFBGA100 ballout

1. This figure shows the package top view.

#### STM32L151x6/8/B STM32L152x6/8/B

|   | 1                        | 2                 | 3       | 4                    | 5       | 6      | 7       | 8      |

|---|--------------------------|-------------------|---------|----------------------|---------|--------|---------|--------|

| A | •<br>/PC14-,<br>OŚC32_IN | , PC13-,<br>WKUP2 | ( PB9 ) | ( PB4 )              | ( PB3 ) | (PA15) | (PA14)  | (PA13) |

| В | /PC15-,<br>OSC32_OUT     | VLCD              | (PB8)   | ВООТО                | (PD2)   | (PC11) | (PC10)  | (PA12) |

| С | , ₽ĤŎ÷,<br>OSC_IN∳       | VSS_4             | ( PB7 ) | (PB5)                | (PC12)  | (PA10) | ( PA9 ) | (PA11) |

| D | OSC_OUT                  | V <sub>DD_4</sub> | (PB6)   | ,V <sub>SS_3</sub> , | VSS_2   | VSS_1  | ( PA8 ) | (PC9)  |

| E | (NRST)                   | (PC1)             | PC0     | 'VDD_3'              | 'VDD_2' | VDD_1  | (PC7)   | (PC8)  |

| F | (Vssa)                   | (PC2)             | (PA2)   | ( PA5 )              | (PB0)   | (PC6)  | (PB15)  | (PB14) |

| G | WREF+ F                  | PA(0-WKU)P1       | ( PA3 ) | ( PA6 )              | (PB1)   | (PB2)  | (PB10)  | (PB13) |

| н | VDDA,                    | ( PA1 )           | (PA4)   | ( PA7 )              | (PC4)   | PC5    | (PB11)  | (PB12) |

Figure 5. STM32L15xRx TFBGA64 ballout

1. This figure shows the package top view.

|         |        | Pins    |          |                    |                                  |                         |               |                                                  | Pins functions                  |                                            |

|---------|--------|---------|----------|--------------------|----------------------------------|-------------------------|---------------|--------------------------------------------------|---------------------------------|--------------------------------------------|

| LQFP100 | LQFP64 | TFBGA64 | UFBGA100 | LQFP48 or UFQFPN48 | Pin name                         | Pin type <sup>(1)</sup> | I/O structure | Main<br>function <sup>(2)</sup><br>(after reset) | Alternate functions             | Additional<br>functions                    |

| 1       | -      | -       | B2       | -                  | PE2                              | I/O                     | FT            | PE2                                              | TRACECLK/LCD_SEG38/<br>TIM3_ETR | -                                          |

| 2       | -      | -       | A1       | -                  | PE3                              | I/O                     | FT            | PE3                                              | TRACED0/LCD_SEG39/<br>TIM3_CH1  | -                                          |

| 3       | -      | -       | B1       | -                  | PE4                              | I/O                     | FT            | PE4                                              | TRACED1/TIM3_CH2                | -                                          |

| 4       | -      | -       | C2       | -                  | PE5                              | I/O                     | FT            | PE5                                              | TRACED2/TIM9_CH1                | -                                          |

| 5       | -      | -       | D2       | -                  | PE6-WKUP3                        | I/O                     | FT            | PE6                                              | TRACED3/TIM9_CH2                | WKUP3                                      |

| 6       | 1      | B2      | E2       | 1                  | V <sub>LCD</sub> <sup>(3)</sup>  | S                       |               | V <sub>LCD</sub>                                 | -                               | -                                          |

| 7       | 2      | A2      | C1       | 2                  | PC13-<br>WKUP2                   | I/O                     | FT            | PC13                                             | -                               | RTC_TAMP1/<br>RTC_TS/<br>RTC_OUT/<br>WKUP2 |

| 8       | 3      | A1      | D1       | 3                  | PC14-<br>OSC32_IN <sup>(4)</sup> | I/O                     | тс            | PC14                                             | -                               | OSC32_IN                                   |

| 9       | 4      | B1      | E1       | 4                  | PC15-<br>OSC32_OUT<br>(4)        | I/O                     | тс            | PC15                                             | -                               | OSC32_OUT                                  |

| 10      | -      | -       | F2       | -                  | V <sub>SS_5</sub>                | S                       | -             | V <sub>SS_5</sub>                                | -                               | -                                          |

| 11      | -      | -       | G2       | -                  | V <sub>DD_5</sub>                | S                       | -             | V <sub>DD_5</sub>                                | -                               | -                                          |

| 12      | 5      | C1      | F1       | 5                  | PH0-<br>OSC_IN <sup>(5)</sup>    | I/O                     | тс            | PH0                                              | -                               | OSC_IN                                     |

| 13      | 6      | D1      | G1       | 6                  | PH1-<br>OSC_OUT                  | I/O                     | тс            | PH1                                              | -                               | OSC_OUT                                    |

| 14      | 7      | E1      | H2       | 7                  | NRST                             | I/O                     | RST           | NRST                                             | -                               | -                                          |

| 15      | 8      | E3      | H1       | -                  | PC0                              | I/O                     | FT            | PC0                                              | LCD_SEG18                       | ADC_IN10/<br>/COMP1_INP                    |

| 16      | 9      | E2      | J2       | -                  | PC1                              | I/O                     | FT            | PC1                                              | LCD_SEG19                       | ADC_IN11/<br>COMP1_INP                     |

| 17      | 10     | F2      | JЗ       | -                  | PC2                              | I/O                     | FT            | PC2                                              | LCD_SEG20                       | ADC_IN12/<br>COMP1_INP                     |

| 18      | 11     | _(6)    | K2       | -                  | PC3                              | I/O                     | тс            | PC3                                              | LCD_SEG21                       | ADC_IN13/<br>COMP1_INP                     |

|         |        | Pins    | 5        |                    |                   |                         |               |                                                  | Pins functions                                 |                         |

|---------|--------|---------|----------|--------------------|-------------------|-------------------------|---------------|--------------------------------------------------|------------------------------------------------|-------------------------|

| LQFP100 | LQFP64 | TFBGA64 | UFBGA100 | LQFP48 or UFQFPN48 | Pin name          | Pin type <sup>(1)</sup> | I/O structure | Main<br>function <sup>(2)</sup><br>(after reset) | Alternate functions                            | Additional<br>functions |

| 90      | 56     | A4      | A7       | 40                 | PB4               | I/O                     | FT            | NJTRST                                           | TIM3_CH1/PB4/<br>SPI1_MISO/LCD_SEG8/<br>NJTRST | COMP2_INP               |

| 91      | 57     | C4      | C5       | 41                 | PB5               | I/O                     | FT            | PB5                                              | I2C1_SMBA/TIM3_CH2/<br>SPI1_MOSI/LCD_SEG9      | COMP2_INP               |

| 92      | 58     | D3      | B5       | 42                 | PB6               | I/O                     | FT            | PB6                                              | I2C1_SCL/TIM4_CH1/<br>USART1_TX                |                         |

| 93      | 59     | C3      | B4       | 43                 | PB7               | I/O                     | FT            | PB7                                              | I2C1_SDA/TIM4_CH2/<br>USART1_RX                | PVD_IN                  |

| 94      | 60     | B4      | A4       | 44                 | BOOT0             | Ι                       | В             | BOOT0                                            | -                                              | -                       |

| 95      | 61     | B3      | A3       | 45                 | PB8               | I/O                     | FT            | PB8                                              | TIM4_CH3/I2C1_SCL/<br>LCD_SEG16/TIM10_CH1      | -                       |

| 96      | 62     | A3      | B3       | 46                 | PB9               | I/O                     | FT            | PB9                                              | TIM4_CH4/I2C1_SDA/<br>LCD_COM3/TIM11_CH1       | -                       |

| 97      | -      | -       | C3       | -                  | PE0               | I/O                     | FT            | PE0                                              | TIM4_ETR/LCD_SEG36/<br>TIM10_CH1               | -                       |

| 98      | -      | -       | A2       | -                  | PE1               | I/O                     | FT            | PE1                                              | LCD_SEG37/TIM11_CH1                            | -                       |

| 99      | 63     | D4      | D3       | 47                 | V <sub>SS_3</sub> | S                       | -             | V <sub>SS_3</sub>                                | -                                              | -                       |

| 100     | 64     | E4      | C4       | 48                 | $V_{DD_3}$        | S                       | -             | V <sub>DD_3</sub>                                | -                                              | -                       |

| Table 8. STM32L151x6/8/B and STM32L152x6/8/B pin definitions (continued) | Table 8. STM32L151x6/8/B | 3 and STM32L152x6/8/B | pin definitions | (continued) |

|--------------------------------------------------------------------------|--------------------------|-----------------------|-----------------|-------------|

|--------------------------------------------------------------------------|--------------------------|-----------------------|-----------------|-------------|

1. I = input, O = output, S = supply.

Function availability depends on the chosen device. For devices having reduced peripheral counts, it is always the lower number of peripheral that is included. For example, if a device has only one SPI and two USARTs, they will be called SPI1 and USART1 & USART2, respectively. Refer to *Table 2 on page 11*.

3. Applicable to STM32L152xx devices only. In STM32L151xx devices, this pin should be connected to V<sub>DD</sub>.

4. The PC14 and PC15 I/Os are only configured as OSC32\_IN/OSC32\_OUT when the LSE oscillator is on (by setting the LSEON bit in the RCC\_CSR register). The LSE oscillator pins OSC32\_IN/OSC32\_OUT can be used as general-purpose PC14/PC15 I/Os, respectively, when the LSE oscillator is off (after reset, the LSE oscillator is off). The LSE has priority over the GPIO function. For more details, refer to Using the OSC32\_IN/OSC32\_OUT pins as GPIO PC14/PC15 port pins section in the STM32L1xxxx reference manual (RM0038).

The PH0 and PH1 I/Os are only configured as OSC\_IN/OSC\_OUT when the HSE oscillator is on (by setting the HSEON bit in the RCC\_CR register). The HSE oscillator pins OSC\_IN/OSC\_OUT can be used as general-purpose PH0/PH1 I/Os, respectively, when the HSE oscillator is off (after reset, the HSE oscillator is off). The HSE has priority over the GPIO function.

6. Unlike in the LQFP64 package, there is no PC3 in the TFBGA64 package. The V<sub>REF+</sub> functionality is provided instead.

| Symbol | Parameter                                                                             | Cond                                                                                                                   | itions                                                | f <sub>HCLK</sub> | Тур  |       |       | Unit               |      |

|--------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------|------|-------|-------|--------------------|------|

| Symbol | Falailletei                                                                           | Cond                                                                                                                   |                                                       |                   |      | 55 °C | 85 °C | 105 °C             | Unit |

|        |                                                                                       |                                                                                                                        | Range 3,                                              | 1 MHz             | 200  | 300   | 300   | 300                |      |

|        | Supply current<br>in Run mode,<br>code executed<br>from RAM,<br>Flash switched<br>off | $f_{HSE} = f_{HCLK}$<br>up to 16 MHz,<br>included<br>$f_{HSE} = f_{HCLK}/2$<br>above 16 MHz<br>(PLL ON) <sup>(2)</sup> | V <sub>CORE</sub> =1.2 V                              | 2 MHz             | 380  | 500   | 500   | 500                | μA   |

|        |                                                                                       |                                                                                                                        | VOS[1:0] = 11                                         | 4 MHz             | 720  | 860   | 860   | 860 <sup>(3)</sup> |      |

|        |                                                                                       |                                                                                                                        | Range 2,                                              | 4 MHz             | 0.9  | 1     | 1     | 1                  |      |

|        |                                                                                       |                                                                                                                        | V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10             | 8 MHz             | 1.65 | 2     | 2     | 2                  | mA   |

|        |                                                                                       |                                                                                                                        |                                                       | 16 MHz            | 3.2  | 3.7   | 3.7   | 3.7                |      |

|        |                                                                                       |                                                                                                                        | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | 8 MHz             | 2    | 2.5   | 2.5   | 2.5                |      |

|        |                                                                                       |                                                                                                                        |                                                       | 16 MHz            | 4    | 4.5   | 4.5   | 4.5                |      |

| from   |                                                                                       |                                                                                                                        |                                                       | 32 MHz            | 7.7  | 8.5   | 8.5   | 8.5                |      |

| RAM)   |                                                                                       | HSI clock source<br>(16 MHz)                                                                                           | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | 16 MHz            | 3.3  | 3.8   | 3.8   | 3.8                |      |

|        |                                                                                       |                                                                                                                        | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | 32 MHz            | 7.8  | 9.2   | 9.2   | 9.2                |      |

|        |                                                                                       | MSI clock, 65 kHz                                                                                                      | Range 3,                                              | 65 kHz            | 40   | 60    | 60    | 80                 | μA   |

|        |                                                                                       | MSI clock, 524 kHz                                                                                                     | V <sub>CORE</sub> =1.2 V                              | 524 kHz           | 110  | 140   | 140   | 160                |      |

|        |                                                                                       | MSI clock, 4.2 MHz                                                                                                     | VOS[1:0] = 11                                         | 4.2 MHz           | 700  | 800   | 800   | 820                |      |

#### Table 18. Current consumption in Run mode, code with data processing running from RAM

1. Guaranteed by characterization results, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

3. Tested in production.

| Symbol                     | Demonstern                                                     | Cond               | 4                                        | Tun               | Max <sup>(1)</sup> |       |       | 11     |      |

|----------------------------|----------------------------------------------------------------|--------------------|------------------------------------------|-------------------|--------------------|-------|-------|--------|------|

| Symbol                     | Parameter                                                      | Cond               | litions                                  | f <sub>HCLK</sub> | Тур                | 55 °C | 85 °C | 105 °C | Unit |

|                            | Supply                                                         | MSI clock, 65 kHz  |                                          | 65 kHz            | 40                 | 70    | 70    | 80     |      |

|                            | current in<br>Sleep<br>mode,<br>code<br>executed<br>from Flash | MSI clock, 524 kHz | Range 3,                                 | 524 kHz           | 60                 | 90    | 90    | 100    |      |

| I <sub>DD</sub><br>(Sleep) |                                                                | MSI clock, 4.2 MHz | V <sub>CORE</sub> =1.2V<br>VOS[1:0] = 11 | 4.2 MHz           | 210                | 250   | 250   | 260    | μA   |

Table 19. Current consumption in Sleep mode (continued)

1. Guaranteed by characterization results, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register)

3. Tested in production

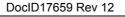

Figure 17. HSE oscillator circuit diagram

1. R<sub>EXT</sub> value depends on the crystal characteristics.

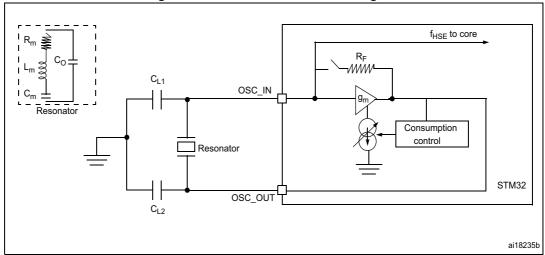

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 29*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                                                                                     | Conditions                            | Min | Тур    | Мах | Unit |  |

|-------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------|-----|--------|-----|------|--|

| f <sub>LSE</sub>                    | Low speed external oscillator<br>frequency                                                    | -                                     | -   | 32.768 | -   | kHz  |  |

| R <sub>F</sub>                      | Feedback resistor                                                                             | -                                     | -   | 1.2    | -   | MΩ   |  |

| C <sup>(2)</sup>                    | Recommended load capacitance versus equivalent serial resistance of the crystal $(R_S)^{(3)}$ | R <sub>S</sub> = 30 kΩ                | -   | 8      | -   | pF   |  |

| I <sub>LSE</sub>                    | LSE driving current                                                                           | $V_{DD}$ = 3.3 V, $V_{IN}$ = $V_{SS}$ | -   | -      | 1.1 | μA   |  |

|                                     |                                                                                               | V <sub>DD</sub> = 1.8 V               | -   | 450    | -   |      |  |

| I <sub>DD (LSE)</sub>               | LSE oscillator current<br>consumption                                                         | V <sub>DD</sub> = 3.0 V               | -   | 600    | -   | nA   |  |

|                                     |                                                                                               | V <sub>DD</sub> = 3.6V                | -   | 750    | -   |      |  |

| 9 <sub>m</sub>                      | Oscillator transconductance                                                                   | -                                     | 3   | -      | -   | µA/V |  |

| t <sub>SU(LSE)</sub> <sup>(4)</sup> | Startup time                                                                                  | V <sub>DD</sub> is stabilized         | -   | 1      | -   | s    |  |

| Table 29. LSE oscillator characteristics | (f <sub>LSE</sub> = 32.768 kHz) <sup>(1)</sup> |

|------------------------------------------|------------------------------------------------|

|------------------------------------------|------------------------------------------------|

1. Guaranteed by characterization results.

2. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

The oscillator selection can be optimized in terms of supply current using an high quality resonator with small R<sub>S</sub> value for example MSIV-TIN32.768kHz. Refer to crystal manufacturer for more details.

- t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

- Note: For CL1 and CL2, it is recommended to use high-quality ceramic capacitors in the 5 pF to 15 pF range selected to match the requirements of the crystal or resonator (see Figure 18). CL1 and CL2, are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of CL1 and CL2. Load capacitance CL has the following formula: CL = CL1 x CL2 / (CL1 + CL2) + Cstray where Cstray is the pin capacitance and board or trace PCB-related capacitance. Typically, it is between 2 pF and 7 pF.

- **Caution:** To avoid exceeding the maximum value of CL1 and CL2 (15 pF) it is strongly recommended to use a resonator with a load capacitance  $CL \le 7$  pF. Never use a resonator with a load capacitance of 12.5 pF.

Example: if a resonator is chosen with a load capacitance of CL = 6 pF and Cstray = 2 pF, then CL1 = CL2 = 8 pF.

#### Figure 18. Typical application with a 32.768 kHz crystal

#### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 19* and *Table 44*, respectively.

Unless otherwise specified, the parameters given in *Table 44* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 13*.

| OSPEEDRx<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                                                   | Parameter                                                       | Conditions                                  | Min        | Max <sup>(2)</sup> | Unit                                        |   |   |  |

|-----------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------|------------|--------------------|---------------------------------------------|---|---|--|

|                                               | f                                                        | Maximum frequency <sup>(3)</sup>                                | $C_L$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V    | -          | 400                | kHz                                         |   |   |  |

| 00                                            | f <sub>max(IO)out</sub>                                  |                                                                 | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V | -          | 400                | кпи                                         |   |   |  |

| 00                                            | t <sub>f(IO)out</sub>                                    | Output rise and fall time                                       | $C_L$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V    | -          | 625                | ns                                          |   |   |  |

|                                               | t <sub>r(IO)out</sub>                                    |                                                                 | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V | -          | 625                | 115                                         |   |   |  |

|                                               | f                                                        | Maximum frequency <sup>(3)</sup>                                | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V  | -          | 2                  | MHz                                         |   |   |  |

| 01                                            | f <sub>max(IO)out</sub>                                  |                                                                 | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V | -          | 1                  |                                             |   |   |  |

| 01                                            | true                                                     | Output rise and fall time                                       | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V  | -          | 125                | ns                                          |   |   |  |

|                                               | t <sub>r(IO)out</sub>                                    |                                                                 | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V | -          | 250                |                                             |   |   |  |

|                                               | E                                                        | Maximum frequency <sup>(3)</sup>                                | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V  | -          | 10                 | MHz                                         |   |   |  |

| 10                                            | F <sub>max(IO)out</sub>                                  | rmax(IO)out                                                     | <pre>' max(IO)out</pre>                     | max(IO)out | Maximum requency   | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V | - | 2 |  |

| 10                                            | trio                                                     | Output rise and fall time                                       | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V  | -          | 25                 | ns                                          |   |   |  |

|                                               | t <sub>r(IO)out</sub>                                    |                                                                 | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V | -          | 125                | 115                                         |   |   |  |

|                                               | F <sub>max(IQ)out</sub> Maximum frequency <sup>(3)</sup> | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V                      | -                                           | 50         | MHz                |                                             |   |   |  |

| 11                                            | F <sub>max(IO)out</sub>                                  |                                                                 | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V | -          | 8                  |                                             |   |   |  |

|                                               | t <sub>f(IO)out</sub>                                    | Output rise and fall time                                       | $C_{L}$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V  | -          | 5                  |                                             |   |   |  |

|                                               | t <sub>r(IO)out</sub>                                    |                                                                 | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V | -          | 30                 |                                             |   |   |  |

| -                                             | t <sub>EXTIpw</sub>                                      | Pulse width of external signals detected by the EXTI controller | -                                           | 8          | -                  | ns                                          |   |   |  |

| Table 44. | I/O AC | characteristics <sup>(1)</sup> |

|-----------|--------|--------------------------------|

|-----------|--------|--------------------------------|

1. The I/O speed is configured using the OSPEEDRx[1:0] bits. Refer to the STM32L151x6/8/B and STM32L152x6/8/B reference manual for a description of GPIO Port configuration register.

2. Guaranteed by design.

3. The maximum frequency is defined in *Figure 19*.

### 6.3.17 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 54* are guaranteed by design.

| Symbol           | Parameter                               | Conditions                     |                                |                                                                  | Min                  | Max | Unit |  |

|------------------|-----------------------------------------|--------------------------------|--------------------------------|------------------------------------------------------------------|----------------------|-----|------|--|

|                  | f <sub>ADC</sub> ADC clock<br>frequency |                                |                                |                                                                  | $V_{REF+} = V_{DDA}$ |     | 16   |  |

|                  |                                         | 2                              | 2.4 V ≤V <sub>DDA</sub> ≤3.6 V | $V_{REF+} < V_{DDA}$<br>$V_{REF+} > 2.4 V$                       |                      | 8   |      |  |

| f <sub>ADC</sub> |                                         |                                |                                | V <sub>REF+</sub> < V <sub>DDA</sub><br>V <sub>REF+</sub> ≤2.4 V |                      | 4   | MHz  |  |

|                  |                                         |                                | 191101 011                     | $V_{REF+} = V_{DDA}$                                             |                      | 8   |      |  |

|                  |                                         | 1.8 V ≤V <sub>DDA</sub> ≤2.4 V | $V_{REF+} < V_{DDA}$           |                                                                  | 4                    |     |      |  |

|                  |                                         | Voltage Range 3                |                                |                                                                  |                      | 4   |      |  |

Table 53. ADC clock frequency

### Table 54. ADC characteristics

| Symbol                           | Parameter                                 | Conditions                                                                                        | Min                | Тур              | Max              | Unit   |

|----------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------|------------------|------------------|--------|

| V <sub>DDA</sub>                 | Power supply                              | -                                                                                                 | 1.8                | -                | 3.6              | V      |

| V <sub>REF+</sub>                | Positive reference voltage                | 2.4 V ⊴V <sub>DDA</sub> ≤3.6 V<br>V <sub>REF+</sub> must be below<br>or equal to V <sub>DDA</sub> | 1.8 <sup>(1)</sup> | -                | V <sub>DDA</sub> | v      |

| $V_{REF-}$                       | Negative reference voltage                | -                                                                                                 | -                  | $V_{\text{SSA}}$ | -                | V      |

| I <sub>VDDA</sub>                | Current on the V <sub>DDA</sub> input pin | -                                                                                                 | -                  | 1000             | 1450             | μA     |

| ı (2)                            | Current on the V <sub>REF</sub> input     | Peak                                                                                              | -                  | 400              | 700              | μA     |

| I <sub>VREF</sub> <sup>(2)</sup> | pin                                       | Average                                                                                           | -                  | 400              | 450              | μA     |

| V <sub>AIN</sub>                 | Conversion voltage range <sup>(3)</sup>   | -                                                                                                 | 0 <sup>(4)</sup>   | -                | $V_{REF}$ +      | V      |

|                                  | 12 hit compling rate                      | Direct channels                                                                                   | 0.03               | -                | 1                | Msps   |

|                                  | 12-bit sampling rate                      | Multiplexed channels                                                                              | 0.03               | -                | 0.76             | ivisps |

|                                  | 10 bit compling rate                      | Direct channels                                                                                   | 0.03               | -                | 1.07             | Msps   |

|                                  | 10-bit sampling rate                      | Multiplexed channels                                                                              | 0.03               | -                | 0.8              | ivisps |

| f <sub>S</sub>                   | 9 hit compling rate                       | Direct channels                                                                                   | 0.03               | -                | 1.23             | Mana   |

|                                  | 8-bit sampling rate                       | Multiplexed channels                                                                              | 0.03               | -                | 0.89             | Msps   |

|                                  | 6-bit sampling rate                       | Direct channels                                                                                   | 0.03               | -                | 1.45             | Msps   |

|                                  |                                           | Multiplexed channels                                                                              | 0.03               | -                | 1                | ivisps |

| Symbol            | Parameter                                          | Conditions                                             | Min                                                            | Тур | Мах     | Unit               |

|-------------------|----------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------------|-----|---------|--------------------|

|                   |                                                    | Direct channels<br>2.4 V ≤V <sub>DDA</sub> ≤3.6 V      | 0.25                                                           | -   | -       |                    |

|                   |                                                    | Multiplexed channels<br>2.4 V ≤V <sub>DDA</sub> ≤3.6 V | 0.56                                                           | -   | -       | 110                |

| t <sub>S</sub>    | Sampling time <sup>(5)</sup>                       | Direct channels<br>1.8 V ⊴V <sub>DDA</sub> ⊴2.4 V      | 0.56                                                           | -   | -       | μs                 |

|                   |                                                    | Multiplexed channels<br>1.8 V ≤V <sub>DDA</sub> ≤2.4 V | 1                                                              | -   | -       |                    |

|                   |                                                    | -                                                      | 4                                                              | -   | 384     | 1/f <sub>ADC</sub> |

|                   |                                                    | f <sub>ADC</sub> = 16 MHz                              | 1                                                              | -   | 24.75   | μs                 |

| t <sub>CONV</sub> | Total conversion time<br>(including sampling time) | -                                                      | 4 to 384 (sampling<br>phase) +12 (successive<br>approximation) |     |         | 1/f <sub>ADC</sub> |

| C                 | Internal sample and hold capacitor                 | Direct channels                                        | -                                                              | 16  | -       | рF                 |

| C <sub>ADC</sub>  |                                                    | Multiplexed channels                                   | -                                                              | 10  | -       |                    |

| f                 | External trigger frequency                         | 12-bit conversions                                     | -                                                              | -   | Tconv+1 | 1/f <sub>ADC</sub> |

| f <sub>TRIG</sub> | Regular sequencer                                  | 6/8/10-bit conversions                                 | -                                                              | -   | Tconv   | 1/f <sub>ADC</sub> |

| f                 | External trigger frequency                         | 12-bit conversions                                     | -                                                              | -   | Tconv+2 | 1/f <sub>ADC</sub> |

| f <sub>TRIG</sub> | Injected sequencer                                 | 6/8/10-bit conversions                                 | -                                                              | -   | Tconv+1 | 1/f <sub>ADC</sub> |

| R <sub>AIN</sub>  | Signal source impedance <sup>(5)</sup>             | -                                                      | -                                                              | -   | 50      | кΩ                 |

| +                 | Injection trigger conversion                       | f <sub>ADC</sub> = 16 MHz                              | 219                                                            | -   | 281     | ns                 |

| t <sub>lat</sub>  | latency                                            | -                                                      | 3.5                                                            | -   | 4.5     | 1/f <sub>ADC</sub> |

| t                 | Regular trigger conversion                         | f <sub>ADC</sub> = 16 MHz                              | 156                                                            | -   | 219     | ns                 |

| t <sub>latr</sub> | latency                                            | -                                                      | 2.5                                                            | -   | 3.5     | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> | Power-up time                                      | -                                                      | -                                                              | -   | 3.5     | μs                 |

Table 54. ADC characteristics (continued)

The V<sub>REF+</sub> input can be grounded iif neither the ADC nor the DAC are used (this allows to shut down an external voltage reference).

2. The current consumption through  $\mathsf{V}_{\mathsf{REF}}$  is composed of two parameters:

- one constant (max 300 µA)

- one variable (max 400  $\mu$ A), only during sampling time + 2 first conversion pulses.

So, peak consumption is 300+400 = 700  $\mu A$  and average consumption is 300 + [(4 sampling + 2) /16] x 400 = 450  $\mu A$  at 1Msps

3.  $V_{REF+}$  can be internally connected to  $V_{DDA}$  and  $V_{REF-}$  can be internally connected to  $V_{SSA}$ , depending on the package. Refer to Section 4: Pin descriptions for further details.

4. V<sub>SSA</sub> must be tied to ground.

5. See Table 56: Maximum source impedance RAIN max for  $\mathsf{R}_{\mathsf{AIN}}$  limitation.

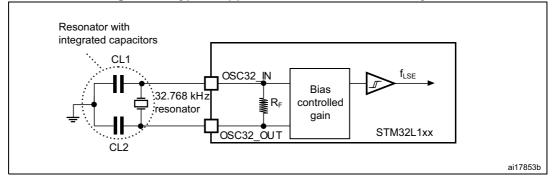

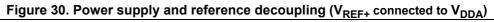

Figure 29. Power supply and reference decoupling (V<sub>REF+</sub> not connected to V<sub>DDA</sub>)

1.  $V_{\mathsf{REF}^+}$  and  $V_{\mathsf{REF}^-}$  inputs are available only on 100-pin packages.

1.  $V_{\mathsf{REF}\text{+}}$  and  $V_{\mathsf{REF}\text{-}}$  inputs are available only on 100-pin packages.

| Symbol                    | Parameter                                                                                                                                                       | Conditions                                                                         | Min | Тур             | Мах              | Unit  |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----|-----------------|------------------|-------|

| dOffset/dT <sup>(1)</sup> | Offset error temperature                                                                                                                                        | $V_{DDA} = 3.3V$ , $T_A = 0$ to 50 ° C<br>DAC output buffer OFF                    | -20 | -10             | 0                | µV/°C |

|                           | coefficient (code 0x800)                                                                                                                                        | $V_{DDA} = 3.3V$ , $T_A = 0$ to 50 ° C<br>DAC output buffer ON                     | 0   | 20              | 50               | μν/ Ο |

| Gain <sup>(1)</sup>       | Gain error <sup>(6)</sup>                                                                                                                                       | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON         | -   | +0.1 /<br>-0.2% | +0.2 / -<br>0.5% | %     |

| Gain                      | Gain enor                                                                                                                                                       | No R <sub>LOAD</sub> , C <sub>L</sub> ≤50 pF<br>DAC output buffer OFF              | -   | +0 / -0.2%      | +0 / -0.4%       | 70    |

| dGain/dT <sup>(1)</sup>   | Gain error temperature                                                                                                                                          | $V_{DDA} = 3.3V$ , $T_A = 0$ to 50 ° C<br>DAC output buffer OFF                    | -10 | -2              | 0                | μV/°C |

| aGain/d1(')               | coefficient                                                                                                                                                     | $V_{DDA} = 3.3V$ , $T_A = 0$ to 50 ° C<br>DAC output buffer ON                     | -40 | -8              | 0                | μν/ Ο |

| TUE <sup>(1)</sup>        | Total unadjusted error                                                                                                                                          | $C_L \le 50 \text{ pF}, \text{ R}_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON | -   | 12              | 30               | LSB   |

|                           |                                                                                                                                                                 | No R <sub>LOAD</sub> , C <sub>L</sub> ≤50 pF<br>DAC output buffer OFF              | -   | 8               | 12               | L3B   |

| tSETTLING                 | Settling time (full scale:<br>for a 12-bit code<br>transition between the<br>lowest and the highest<br>input codes till<br>DAC_OUT reaches final<br>value ±1LSB | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                 | -   | 7               | 12               | μs    |

| Update rate               | Max frequency for a<br>correct DAC_OUT<br>change (95% of final<br>value) with 1 LSB<br>variation in the input<br>code                                           | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                 | -   | -               | 1                | Msps  |

| t <sub>wakeup</sub>       | Wakeup time from off<br>state (setting the ENx bit<br>in the DAC Control<br>register) <sup>(7)</sup>                                                            | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                 | -   | 9               | 15               | μs    |

| PSRR+                     | V <sub>DDA</sub> supply rejection<br>ratio (static DC<br>measurement)                                                                                           | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                 | -   | -60             | -35              | dB    |

#### Table 57. DAC characteristics (continued)

1. Guaranteed by characterization results.

2. Difference between two consecutive codes - 1 LSB.

3. Difference between measured value at Code i and the value at Code i on a line drawn between Code 0 and last Code 4095.

4. Difference between the value measured at Code (0x800) and the ideal value = V/2.

5. Difference between the value measured at Code (0x001) and the ideal value.

6. Difference between ideal slope of the transfer function and measured slope computed from code 0x000 and 0xFFF when buffer is OFF, and from code giving 0.2 V and ( $V_{DDA} - 0.2$ ) V when buffer is ON.

7. In buffered mode, the output can overshoot above the final value for low input code (starting from min value).

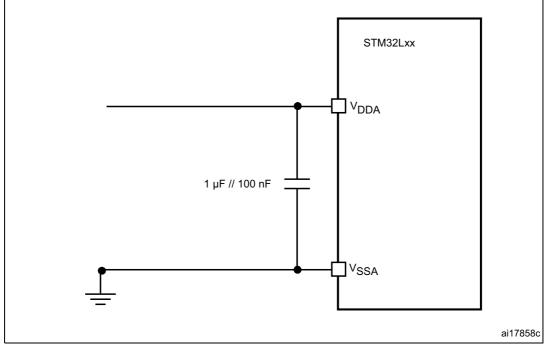

# 7.4 UFQFPN48 7 x 7 mm, 0.5 mm pitch, package information

Figure 41. UFQFPN48 7 x 7 mm, 0.5 mm pitch, package outline

1. Drawing is not to scale.

- 2. All leads/pads should also be soldered to the PCB to improve the lead/pad solder joint life.

- 3. There is an exposed die pad on the underside of the UFQFPN package. It is recommended to connect and solder this back-side pad to PCB ground.

|               | Table 73 | Document revision history (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date          | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 17-June-2011  | 5        | Modified 1st page (low power features)<br>Added STM32L15xC6 and STM32L15xR6 devices (32 Kbytes of<br>Flash memory).<br>Modified Section 3.6: GPIOs (general-purpose inputs/outputs) on<br>page 22<br>Modified Section 6.3: Operating conditions on page 53<br>Modified Table 55: ADC accuracy on page 95, Table 57: DAC<br>characteristics on page 99 and Table 60: Comparator 1<br>characteristics on page 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 25-Jan-2012 6 |          | <i>Features</i> : updated internal multispeed low power RC.<br><i>Table 2: Ultralow power STM32L15xx6/8/B device features and peripheral counts</i> : LCD 4x44 and 8x40 available for both 64- and 128-Kbyte devices; two comparators available for all devices.<br><i>Table 3: Functionalities depending on the operating power supply range</i> : added footnote 1.<br><i>Figure 8: STM32L15xCx UFQFPN48 pinout</i> : replaced VFQPN48 by UFQFPN48 as name of package.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|               | 6        | Table 8: STM32L15xx6/8/B pin definitions: replaced PH0/PH1 by<br>PC14/PC15.Table 9: Alternate function input/output: removed EVENT OUT from<br>PH2 port, AFIO15 column.Table 19: Current consumption in Sleep mode: updated MSI<br>conditions and f <sub>HCLK</sub> .Table 20: Current consumption in Low power run mode: updated<br>some temperature conditions; added footnote 2.Table 21: Current consumption in Low power sleep mode: updated                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|               |          | some temperature conditions and one of the MSI clock conditions.<br><i>Table 22: Typical and maximum current consumptions in Stop</i><br><i>mode</i> : updated I <sub>DD</sub> (WU from Stop) parameter.<br><i>Table 23: Typical and maximum current consumptions in Standby</i><br><i>mode</i> : updated I <sub>DD</sub> (WU from Standby) parameter.<br><i>Table 25: Low-power mode wakeup timings</i> : updated f <sub>HCLK</sub> value                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               |          | for $t_{WUSLEEP\_LP}$ ; updated typical value of parameter "Wakeup from<br>Stop mode, regulator in Run mode".<br><i>Table 24: Peripheral current consumption</i> : replaced GPIOF by<br>GPIOH.<br><i>Table 33: PLL characteristics</i> : updated "PLL output clock"<br><i>Table 35: Flash memory and data EEPROM characteristics</i> :<br>updated all information for I <sub>DD</sub> .<br><i>Figure 19: I/O AC characteristics definition</i> : replaced the falling<br>edge "t <sub>r(IO)out</sub> " by "t <sub>f(IO)out</sub> ".<br><i>Table 47: I2C characteristics</i> : updated f <sub>S</sub> max value for direct<br>channels, 6-bit sampling rate.<br><i>Table 55: ADC accuracy</i> : Updated the first, third and fourth f <sub>ADC</sub> test<br>condition.<br><i>Table 59: Temperature sensor characteristics</i> : updated typ, min,<br>and max values of the T <sub>S temp</sub> parameter. |

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30-Jan-2015 | 11       | Updated DMIPS features in cover page and Section 2: Description.<br>Updated Table 8: STM32L151x6/8/B and STM32L152x6/8/B pin<br>definitions and Table 9: Alternate function input/output putting<br>additional functions.<br>Updated package top view marking in Section 7.1: Package<br>mechanical data.<br>Updated Figure 9: Memory map.<br>Updated Table 56: Maximum source impedance RAIN max adding<br>note 2.<br>Updated Table 72: Ordering information scheme.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |