Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                    |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, POR, PWM, WDT |

| Number of I/O              | 51                                                                      |

| Program Memory Size        | 64KB (64K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 4K x 8                                                                  |

| RAM Size                   | 10K × 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Data Converters            | A/D 20x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-TFBGA                                                                |

| Supplier Device Package    | 64-TFBGA (5x5)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l151r8h6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.2 Ultra-low-power device continuum

The ultra-low-power STM32L151x6/8/B and STM32L152x6/8/B devices are fully pin-to-pin and software compatible. Besides the full compatibility within the family, the devices are part of STMicroelectronics microcontrollers ultra-low-power strategy which also includes STM8L101xx and STM8L15xx devices. The STM8L and STM32L families allow a continuum of performance, peripherals, system architecture and features.

They are all based on STMicroelectronics ultra-low leakage process.

Note: The ultra-low-power STM32L and general-purpose STM32Fxxxx families are pin-to-pin compatible. The STM8L15xxx devices are pin-to-pin compatible with the STM8L101xx devices. Please refer to the STM32F and STM8L documentation for more information on these devices.

## 2.2.1 Performance

All families incorporate highly energy-efficient cores with both Harvard architecture and pipelined execution: advanced STM8 core for STM8L families and ARM<sup>®</sup> Cortex<sup>®</sup>-M3 core for STM32L family. In addition specific care for the design architecture has been taken to optimize the mA/DMIPS and mA/MHz ratios.

This allows the ultra-low-power performance to range from 5 up to 33.3 DMIPs.

## 2.2.2 Shared peripherals

STM8L15xxx and STM32L1xxxx share identical peripherals which ensure a very easy migration from one family to another:

- Analog peripherals: ADC, DAC and comparators

- Digital peripherals: RTC and some communication interfaces

## 2.2.3 Common system strategy

To offer flexibility and optimize performance, the STM8L15xx and STM32L1xxxx families use a common architecture:

- Same power supply range from 1.65 V to 3.6 V, (1.65 V at power down only for STM8L15xx devices)

- Architecture optimized to reach ultra-low consumption both in low power modes and Run mode

- Fast startup strategy from low power modes

- Flexible system clock

- Ultrasafe reset: same reset strategy including power-on reset, power-down reset, brownout reset and programmable voltage detector.

# 2.2.4 Features

ST ultra-low-power continuum also lies in feature compatibility:

- More than 10 packages with pin count from 20 to 144 pins and size down to 3 x 3 mm

- Memory density ranging from 4 to 384 Kbytes

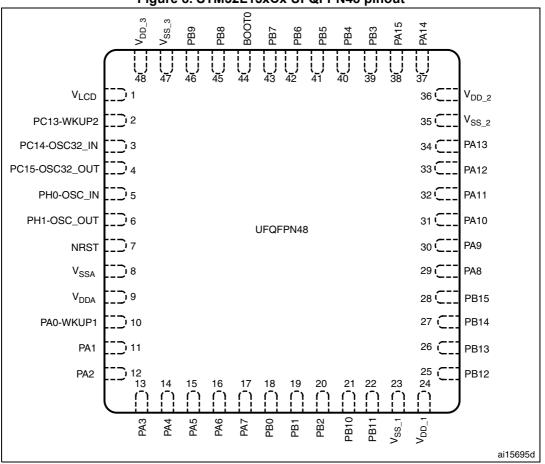

Figure 8. STM32L15xCx UFQFPN48 pinout

1. This figure shows the package top view.

|         |        | Pins      |          | . 01               |                   |                         |               |                                                  | B/B pin definitions (conti<br>Pins functions |                                    |

|---------|--------|-----------|----------|--------------------|-------------------|-------------------------|---------------|--------------------------------------------------|----------------------------------------------|------------------------------------|

|         |        |           | >        |                    |                   |                         |               |                                                  |                                              |                                    |

| LQFP100 | LQFP64 | TFBGA64   | UFBGA100 | LQFP48 or UFQFPN48 | Pin name          | Pin type <sup>(1)</sup> | I/O structure | Main<br>function <sup>(2)</sup><br>(after reset) | Alternate functions                          | Additional<br>functions            |

| 19      | 12     | F1        | J1       | 8                  | V <sub>SSA</sub>  | S                       | -             | V <sub>SSA</sub>                                 | -                                            | -                                  |

| 20      | -      | -         | K1       | -                  | V <sub>REF-</sub> | S                       | -             | V <sub>REF-</sub>                                | -                                            | -                                  |

| 21      | -      | G1<br>(6) | L1       | -                  | V <sub>REF+</sub> | S                       | -             | V <sub>REF+</sub>                                | -                                            | -                                  |

| 22      | 13     | H1        | M1       | 9                  | V <sub>DDA</sub>  | S                       | -             | V <sub>DDA</sub>                                 | -                                            | -                                  |

| 23      | 14     | G2        | L2       | 10                 | PA0-WKUP1         | I/O                     | FT            | PA0                                              | USART2_CTS/<br>TIM2_CH1_ETR                  | WKUP1/<br>ADC_IN0/<br>COMP1_INP    |

| 24      | 15     | H2        | M2       | 11                 | PA1               | I/O                     | FT            | PA1                                              | USART2_RTS/<br>TIM2_CH2/LCD_SEG0             | ADC_IN1/<br>COMP1_INP              |

| 25      | 16     | F3        | K3       | 12                 | PA2               | I/O                     | FT            | PA2                                              | USART2_TX/TIM2_CH3/<br>TIM9_CH1/LCD_SEG1     | ADC_IN2/<br>COMP1_INP              |

| 26      | 17     | G3        | L3       | 13                 | PA3               | I/O                     | тс            | PA3                                              | USART2_RX/TIM2_CH4/<br>TIM9_CH2/LCD_SEG2     | ADC_IN3/<br>COMP1_INP              |

| 27      | 18     | C2        | E3       | -                  | V <sub>SS_4</sub> | S                       | -             | V <sub>SS_4</sub>                                | -                                            | -                                  |

| 28      | 19     | D2        | H3       | -                  | V <sub>DD_4</sub> | S                       | -             | V <sub>DD_4</sub>                                | -                                            | -                                  |

| 29      | 20     | H3        | М3       | 14                 | PA4               | I/O                     | тс            | PA4                                              | SPI1_NSS/USART2_CK                           | ADC_IN4/<br>DAC_OUT1/<br>COMP1_INP |

| 30      | 21     | F4        | K4       | 15                 | PA5               | I/O                     | тс            | PA5                                              | SPI1_SCK/<br>TIM2_CH1_ETR                    | ADC_IN5/<br>DAC_OUT2/<br>COMP1_INP |

| 31      | 22     | G4        | L4       | 16                 | PA6               | I/O                     | FT            | PA6                                              | SPI1_MISO/TIM3_CH1/<br>LCD_SEG3/TIM10_CH1    | ADC_IN6<br>/COMP1_INP              |

| 32      | 23     | H4        | M4       | 17                 | PA7               | I/O                     | FT            | PA7                                              | SPI1_MOSI//TIM3_CH2/<br>LCD_SEG4/TIM11_CH1   | ADC_IN7/<br>COMP1_INP              |

| 33      | 24     | H5        | K5       | -                  | PC4               | I/O                     | FT            | PC4                                              | LCD_SEG22                                    | ADC_IN14/<br>COMP1_INP             |

| 34      | 25     | H6        | L5       | -                  | PC5               | I/O                     | FT            | PC5                                              | LCD_SEG23                                    | ADC_IN15/<br>COMP1_INP             |

# Table 8. STM32L151x6/8/B and STM32L152x6/8/B pin definitions (continued)

|         |        | Pin     |          |                    |          |                         |               |                                                  | Pins functions                        | ,                                    |

|---------|--------|---------|----------|--------------------|----------|-------------------------|---------------|--------------------------------------------------|---------------------------------------|--------------------------------------|

| LQFP100 | LQFP64 | TFBGA64 | UFBGA100 | LQFP48 or UFQFPN48 | Pin name | Pin type <sup>(1)</sup> | I/O structure | Main<br>function <sup>(2)</sup><br>(after reset) | Alternate functions                   | Additional<br>functions              |

| 53      | 35     | F8      | K11      | 27                 | PB14     | I/O                     | FT            | - PB14 USART3_RTS/<br>LCD_SEG14//TIM9_CH2        |                                       | ADC_IN20/<br>COMP1_INP               |

| 54      | 36     | F7      | K10      | 28                 | PB15     | I/O                     | FT            | PB15                                             | SPI2_MOSI/LCD_SEG15/<br>TIM11_CH1     | ADC_IN21/<br>COMP1_INP/<br>RTC_REFIN |

| 55      | -      | -       | K9       | -                  | PD8      | I/O                     | FT            | PD8                                              | PD8 USART3_TX/<br>LCD_SEG28           |                                      |

| 56      | -      | -       | K8       | -                  | PD9      | I/O                     | FT            | PD9 USART3_RX/<br>LCD_SEG29                      |                                       | -                                    |

| 57      | -      | -       | J12      | -                  | PD10     | I/O                     | FT            | PD10                                             | PD10 USART3_CK/<br>LCD_SEG30          |                                      |

| 58      | -      | -       | J11      | -                  | PD11     | I/O                     | FT            | PD11                                             | USART3_CTS/<br>LCD_SEG31              | -                                    |

| 59      | -      | -       | J10      | -                  | PD12     | I/O                     | FT            | PD12                                             | TIM4_CH1/<br>USART3_RTS/<br>LCD_SEG32 | -                                    |

| 60      | -      | -       | H12      | -                  | PD13     | I/O                     | FT            | PD13                                             | TIM4_CH2/LCD_SEG33                    | -                                    |

| 61      | -      | -       | H11      | -                  | PD14     | I/O                     | FT            | PD14                                             | TIM4_CH3/LCD_SEG34                    | -                                    |

| 62      | -      | -       | H10      | -                  | PD15     | I/O                     | FT            | PD15                                             | TIM4_CH4/LCD_SEG35                    | -                                    |

| 63      | 37     | F6      | E12      | -                  | PC6      | I/O                     | FT            | PC6                                              | TIM3_CH1/LCD_SEG24                    | -                                    |

| 64      | 38     | E7      | E11      | -                  | PC7      | I/O                     | FT            | PC7                                              | TIM3_CH2/LCD_SEG25                    | -                                    |

| 65      | 39     | E8      | E10      | -                  | PC8      | I/O                     | FT            | PC8                                              | TIM3_CH3/LCD_SEG26                    | -                                    |

| 66      | 40     | D8      | D12      | -                  | PC9      | I/O                     | FT            | PC9                                              | TIM3_CH4/LCD_SEG27                    | -                                    |

| 67      | 41     | D7      | D11      | 29                 | PA8      | I/O                     | FT            | PA8 USART1_CK/MCO/<br>LCD_COM0                   |                                       | -                                    |

| 68      | 42     | C7      | D10      | 30                 | PA9      | I/O                     | FT            | PA9 USART1_TX/LCD_COM1                           |                                       | -                                    |

| 69      | 43     | C6      | C12      | 31                 | PA10     | I/O                     | FT            | PA10                                             | USART1_RX/LCD_COM2                    | -                                    |

| 70      | 44     | C8      | B12      | 32                 | PA11     | I/O                     | FT            | PA11                                             | USART1_CTS/<br>SPI1_MISO              | USB_DM                               |

46/133

DocID17659 Rev 12

5

|                |                    | Digital alternate function number |          |            |        |           |       |            |       |       |        |        |        |          |          |

|----------------|--------------------|-----------------------------------|----------|------------|--------|-----------|-------|------------|-------|-------|--------|--------|--------|----------|----------|

| <b>B</b> . 4   | AFIO0              | AFIO1                             | AFIO2    | AFIO3      | AFIO4  | AFIO5     | AFOI6 | AFIO7      | AFIO8 | AFIO9 | AFIO11 | AFIO12 | AFIO13 | AFIO14   | AFIO15   |

| Port name      | Alternate function |                                   |          |            |        |           |       |            |       |       |        |        |        |          |          |

|                | SYSTEM             | TIM2                              | TIM3/4   | TIM9/10/11 | I2C1/2 | SPI1/2    | N/A   | USART1/2/3 | N/A   | N/A   | LCD    | N/A    | N/A    | RI       | SYSTEM   |

| PD13           | -                  | -                                 | TIM4_CH2 | -          | -      | -         | -     | -          | -     | -     | -      | -      | -      | TIMx_IC2 | EVENTOUT |

| PD14           | -                  | -                                 | TIM4_CH3 | -          | -      | -         | -     | -          | -     | -     | -      | -      | -      | TIMx_IC3 | EVENTOUT |

| PD15           | -                  | -                                 | TIM4_CH4 | -          | -      | -         | -     | -          | -     | -     | -      | -      | -      | TIMx_IC4 | EVENTOUT |

| PE0            | -                  | -                                 | TIM4_ETR | TIM10_CH1  | -      | -         | -     | -          | -     | -     | -      | -      | -      | TIMx_IC1 | EVENTOUT |

| PE1            | -                  | -                                 |          | TIM11_CH1  | -      | -         | -     | -          | -     | -     | -      | -      | -      | TIMx_IC2 | EVENTOUT |

| PE2            | TRACEC<br>K        | -                                 | TIM3_ETR | -          | -      | -         | -     | -          | -     | -     | -      | -      | -      | TIMx_IC3 | EVENTOUT |

| PE3            | TRACED<br>0        | -                                 | TIM3_CH1 | -          | -      | -         | -     | -          | -     | -     | -      | -      | -      | TIMx_IC4 | EVENTOUT |

| PE4            | TRACED<br>1        | -                                 | TIM3_CH2 | -          | -      | -         | -     | -          | -     | -     | -      | -      | -      | TIMx_IC1 | EVENTOUT |

| PE5            | TRACED<br>2        | -                                 | -        | TIM9_CH1*  | -      | -         | -     | -          | -     | -     | -      | -      | -      | TIMx_IC2 | EVENTOUT |

| PE6            | TRACED<br>3        | -                                 | -        | TIM9_CH2*  | -      | -         | -     | -          | -     | -     | -      | -      | -      | TIMx_IC3 | EVENTOUT |

| PE7            | -                  | -                                 | -        | -          | -      | -         | -     | -          | -     | -     | -      | -      | -      | TIMx_IC4 | EVENTOUT |

| PE8            | -                  | -                                 | -        | -          | -      | -         | -     | -          | -     | -     | -      | -      | -      | TIMx_IC1 | EVENTOUT |

| PE9            | -                  | TIM2_CH1_ETR                      | -        | -          | -      | -         | -     | -          | -     | -     | -      | -      | -      | TIMx_IC2 | EVENTOUT |

| PE10           | -                  | TIM2_CH2                          | -        | -          | -      | -         | -     | -          | -     | -     | -      | -      | -      | TIMx_IC3 | EVENTOUT |

| PE11           | -                  | TIM2_CH3                          | -        | -          | -      | -         | -     | -          | -     | -     | -      | -      | -      | TIMx_IC4 | EVENTOUT |

| PE12           | -                  | TIM2_CH4                          | -        | -          | -      | SPI1_NSS  | -     | -          | -     | -     | -      | -      | -      | TIMx_IC1 | EVENTOUT |

| PE13           | -                  | -                                 | -        | -          | -      | SPI1_SCK  | -     | -          | -     | -     | -      | -      | -      | TIMx_IC2 | EVENTOUT |

| PE14           | -                  | -                                 | -        | -          | -      | SPI1_MISO | -     | -          | -     | -     | -      | -      | -      | TIMx_IC3 | EVENTOUT |

| PE15           | -                  | -                                 | -        | -          | -      | SPI1_MOSI | -     | -          | -     | -     | -      | -      | -      | TIMx_IC4 | EVENTOUT |

| PH0-<br>OSC_IN | -                  | -                                 | -        | -          | -      | -         | -     | -          | -     | -     | -      | -      | -      | -        | -        |

## Table 9. Alternate function input/output (continued)

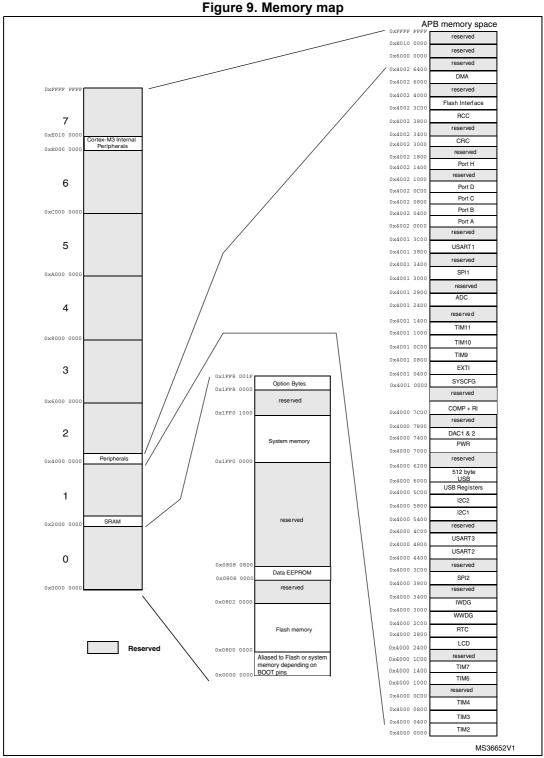

# 5 Memory mapping

The memory map is shown in *Figure 9*.

Figure 9 Momon

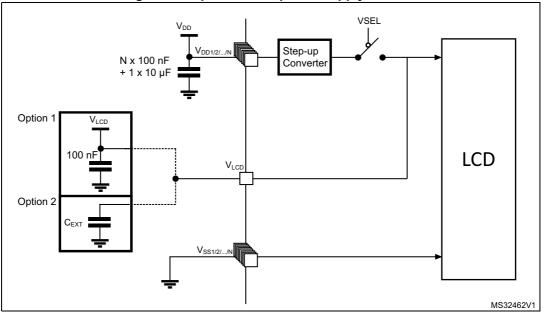

# 6.1.7 Optional LCD power supply scheme

#### Figure 13. Optional LCD power supply scheme

1. Option 1: LCD power supply is provided by a dedicated VLCD supply source, VSEL switch is open.

2. Option 2: LCD power supply is provided by the internal step-up converter, VSEL switch is closed, an external capacitance is needed for correct behavior of this converter.

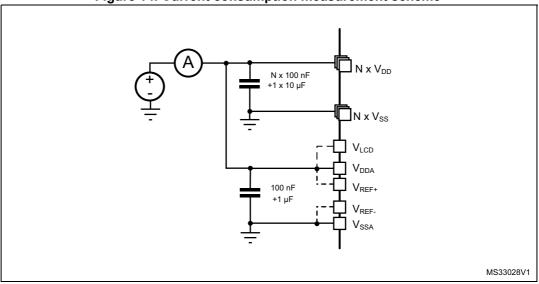

## 6.1.8 Current consumption measurement

#### Figure 14. Current consumption measurement scheme

# 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 10: Voltage characteristics*, *Table 11: Current characteristics*, and *Table 12: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                              | Ratings                                                               | Min                  | Мах                  | Unit |

|-------------------------------------|-----------------------------------------------------------------------|----------------------|----------------------|------|

| V <sub>DD</sub> -V <sub>SS</sub>    | External main supply voltage (including $V_{DDA}$ and $V_{DD})^{(1)}$ | -0.3                 | 4.0                  |      |

| V <sub>IN</sub> <sup>(2)</sup>      | Input voltage on five-volt tolerant pin                               | V <sub>SS</sub> –0.3 | V <sub>DD</sub> +4.0 | V    |

| VIN V                               | Input voltage on any other pin                                        | V <sub>SS</sub> -0.3 | 4.0                  |      |

| $ \Delta V_{DDx} $                  | Variations between different $V_{DD}$ power pins                      | -                    | 50                   | mV   |

| V <sub>SSX</sub> -V <sub>SS</sub>   | Variations between all different ground $pins^{(3)}$                  | -                    | 50                   |      |

| V <sub>REF+</sub> –V <sub>DDA</sub> | Allowed voltage difference for $V_{REF+} > V_{DDA}$                   | -                    | - 0.4                |      |

| V <sub>ESD(HBM)</sub>               | Electrostatic discharge voltage (human body model)                    | see Section 6        | .3.11                | -    |

#### Table 10. Voltage characteristics

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. V<sub>IN</sub> maximum must always be respected. Refer to Table 11 for maximum allowed injected current values.

3. Include VREF- pin.

#### Table 11. Current characteristics

| Symbol                               | Ratings                                                                 | Max.  | Unit |

|--------------------------------------|-------------------------------------------------------------------------|-------|------|

| Ι <sub>VDDΣ</sub>                    | Total current into $V_{DD}/V_{DDA}$ power lines (source) <sup>(1)</sup> | 80    |      |

| $I_{VSS\Sigma}$                      | Total current out of $V_{SS}$ ground lines (sink) <sup>(1)</sup>        | 80    |      |

| I                                    | Output current sunk by any I/O and control pin                          | 25    |      |

| Ι <sub>ΙΟ</sub>                      | Output current sourced by any I/O and control pin                       | - 25  |      |

| ı (2)                                | Injected current on five-volt tolerant I/O <sup>(3)</sup>               | -5/+0 |      |

| I <sub>INJ(PIN)</sub> <sup>(2)</sup> | Injected current on any other pin <sup>(4)</sup>                        | ± 5   |      |

| ΣΙ <sub>INJ(PIN)</sub>               | Total injected current (sum of all I/O and control pins) <sup>(5)</sup> | ± 25  | mA   |

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. Negative injection disturbs the analog performance of the device. See note in Section 6.3.17.

3. Positive current injection is not possible on these I/Os. A negative injection is induced by  $V_{IN}$ <V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 10* for maximum allowed input voltage values.

A positive injection is induced by V<sub>IN</sub> > V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 10: Voltage characteristics* for the maximum allowed input voltage values.

5. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | -65 to +150 | °C   |

| Τ <sub>J</sub>   | Maximum junction temperature | 150         | °C   |

#### Table 12. Thermal characteristics

# 6.3 Operating conditions

# 6.3.1 General operating conditions

| Symbol                          | Parameter                                                                                                   | Conditions                                                  | Min      | Max                         | Unit |  |

|---------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------|-----------------------------|------|--|

| f <sub>HCLK</sub>               | Internal AHB clock frequency                                                                                | -                                                           | 0        | 32                          |      |  |

| f <sub>PCLK1</sub>              | Internal APB1 clock frequency                                                                               | -                                                           | 0        | 32                          | MHz  |  |

| f <sub>PCLK2</sub>              | Internal APB2 clock frequency                                                                               | -                                                           | 0        | 32                          |      |  |

|                                 |                                                                                                             | BOR detector disabled                                       | 1.65     | 3.6                         |      |  |

| V <sub>DD</sub>                 | Standard operating voltage                                                                                  | BOR detector enabled,<br>at power on                        | 1.8      | 3.6                         | V    |  |

|                                 |                                                                                                             | BOR detector disabled, after power on                       | 1.65     | 3.6                         |      |  |

| V <sub>DDA</sub> <sup>(1)</sup> | Analog operating voltage<br>(ADC and DAC not used)                                                          | Must be the same voltage as                                 | 1.65     | 3.6                         | V    |  |

| VDDA` ′                         | Analog operating voltage<br>(ADC or DAC used) Must be the same voltage as<br>V <sub>DD</sub> <sup>(2)</sup> |                                                             | 1.8      | 3.6                         | v    |  |

|                                 | Input voltage on FT pins <sup>(3)</sup>                                                                     | 2.0 V ≤V <sub>DD</sub> ≤ 3.6 V                              | -0.3     | 5.5                         |      |  |

| V <sub>IN</sub>                 |                                                                                                             | $1.65 \text{ V} \le \text{V}_{\text{DD}} \le 2.0 \text{ V}$ | -0.3     | 5.25                        | V    |  |

|                                 | Input voltage on BOOT0 pin<br>Input voltage on any other pin                                                |                                                             | 0<br>0.3 | 5.5<br>V <sub>DD</sub> +0.3 |      |  |

| P <sub>D</sub>                  | Power dissipation at $T_A = 85 \ ^{\circ}C^{(4)}$                                                           | BGA100 package                                              | -        | 339                         | mW   |  |

| Та                              | Tomporatura ranga                                                                                           | Maximum power dissipation                                   |          | 85                          | °C   |  |

| IA                              | Temperature range                                                                                           | Low power dissipation <sup>(5)</sup>                        | 105      | U                           |      |  |

| TJ                              | Junction temperature range                                                                                  | -40 °C ≤T <sub>A</sub> ≤105°C                               | -40      | 105                         | °C   |  |

#### Table 13. General operating conditions

1. When the ADC is used, refer to Table 54: ADC characteristics.

2. It is recommended to power V<sub>DD</sub> and V<sub>DDA</sub> from the same source. A maximum difference of 300 mV between V<sub>DD</sub> and V<sub>DDA</sub> can be tolerated during power-up and operation.

3. To sustain a voltage higher than  $V_{DD}$ +0.3 V, the internal pull-up/pull-down resistors must be disabled.

If T<sub>A</sub> is lower, higher P<sub>D</sub> values are allowed as long as T<sub>J</sub> does not exceed T<sub>J</sub> max (see Table 12: Thermal characteristics on page 53).

In low power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>J</sub> max (see *Table 12: Thermal characteristics on page 53*).

| 0h.al                      | Demonster                             | 0                                                              |                                                       |                   | <b>T</b> |       | Max <sup>(1</sup> | )                  | 11   |

|----------------------------|---------------------------------------|----------------------------------------------------------------|-------------------------------------------------------|-------------------|----------|-------|-------------------|--------------------|------|

| Symbol                     | Parameter                             | arameter Conditions                                            |                                                       | f <sub>HCLK</sub> | Тур      | 55 °C | 85 °C             | 105 °C             | Unit |

|                            |                                       |                                                                | Range 3,                                              | 1 MHz             | 80       | 140   | 140               | 140                |      |

|                            |                                       |                                                                | V <sub>CORE</sub> =1.2 V                              | 2 MHz             | 150      | 210   | 210               | 210                |      |

|                            |                                       | f <sub>HSE</sub> = f <sub>HCLK</sub> up to<br>16 MHz included, | VOS[1:0] = 11                                         | 4 MHz             | 280      | 330   | 330               | 330 <sup>(3)</sup> |      |

|                            |                                       |                                                                | Range 2,                                              | 4 MHz             | 280      | 400   | 400               | 400                |      |

|                            |                                       | $f_{HSE} = f_{HCLK}/2$                                         | V <sub>CORE</sub> =1.5 V                              | 8 MHz             | 450      | 550   | 550               | 550                |      |

|                            | Supply<br>current in<br>Sleep         | above 16 MHz (PLL ON) <sup>(2)</sup>                           | VOS[1:0] = 10                                         | 16 MHz            | 900      | 1050  | 1050              | 1050               |      |

|                            |                                       | ,                                                              | Range 1,                                              | 8 MHz             | 550      | 650   | 650               | 650                |      |

|                            | mode,<br>code                         |                                                                | V <sub>CORE</sub> =1.8 V                              | 16 MHz            | 1050     | 1200  | 1200              | 1200               |      |

|                            | executed                              |                                                                | VOS[1:0] = 01                                         | 32 MHz            | 2300     | 2500  | 2500              | 2500               | μA   |

|                            | from RAM,<br>Flash<br>switched<br>OFF |                                                                | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | 16 MHz            | 1000     | 1100  | 1100              | 1100               |      |

|                            |                                       |                                                                | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | 32 MHz            | 2300     | 2500  | 2500              | 2500               |      |

|                            |                                       | MSI clock, 65 kHz                                              | Range 3,<br>V <sub>CORE</sub> =1.2 V                  | 65 kHz            | 30       | 50    | 50                | 60                 |      |

| I <sub>DD</sub><br>(Sleep) |                                       | MSI clock, 524 kHz                                             |                                                       | 524 kHz           | 50       | 70    | 70                | 80                 |      |

| (Sleep)                    |                                       | MSI clock, 4.2 MHz                                             | VOS[1:0] = 11                                         | 4.2 MHz           | 200      | 240   | 240               | 250                |      |

|                            |                                       |                                                                | Range 3,<br>V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | 1 MHz             | 80       | 140   | 140               | 140                |      |

|                            |                                       |                                                                |                                                       | 2 MHz             | 150      | 210   | 210               | 210                |      |

|                            |                                       |                                                                |                                                       | 4 MHz             | 290      | 350   | 350               | 350                |      |

|                            |                                       | f <sub>HSE</sub> = f <sub>HCLK</sub> up to<br>16 MHz included, | Range 2,                                              | 4 MHz             | 300      | 400   | 400               | 400                |      |

|                            | Supply                                | $f_{HSE} = f_{HCLK}/2$                                         | V <sub>CORE</sub> =1.5 V                              | 8 MHz             | 500      | 600   | 600               | 600                |      |

|                            | current in                            | above 16 MHz (PLL ON) <sup>(2)</sup>                           | VOS[1:0] = 10                                         | 16 MHz            | 1000     | 1100  | 1100              | 1100               |      |

|                            | Sleep<br>mode,                        |                                                                | Range 1,                                              | 8 MHz             | 550      | 650   | 650               | 650                | μA   |

|                            | code                                  |                                                                | V <sub>CORE</sub> =1.8 V                              | 16 MHz            | 1050     | 1200  | 1200              | 1200               | μ    |

|                            | executed<br>from Flash                |                                                                | VOS[1:0] = 01                                         | 32 MHz            | 2300     | 2500  | 2500              | 2500               |      |

|                            |                                       | HSI clock source<br>(16 MHz)                                   | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | 16 MHz            | 1000     | 1100  | 1100              | 1100               |      |

|                            |                                       |                                                                | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | 32 MHz            | 2300     | 2500  | 2500              | 2500               |      |

Table 19. Current consumption in Sleep mode

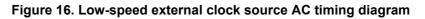

#### Low-speed external user clock generated from an external source

The characteristics given in the following table result from tests performed using a lowspeed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 13*.

| Symbol                                       | Parameter                               | Conditions                       | Min                | Тур    | Max                | Unit |

|----------------------------------------------|-----------------------------------------|----------------------------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                         | User external clock source<br>frequency |                                  | 1                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                            | OSC32_IN input pin high level voltage   |                                  | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | v    |

| V <sub>LSEL</sub>                            | OSC32_IN input pin low level voltage    | -                                | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> | v    |

| t <sub>w(LSEH)</sub><br>t <sub>w(LSEL)</sub> | OSC32_IN high or low time               |                                  | 465                | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub>   | OSC32_IN rise or fall time              |                                  | -                  | -      | 10                 | 115  |

| C <sub>IN(LSE)</sub>                         | OSC32_IN input capacitance              | -                                | -                  | 0.6    | -                  | pF   |

| DuCy <sub>(LSE)</sub>                        | Duty cycle                              | -                                | 45                 | -      | 55                 | %    |

| ١L                                           | OSC32_IN Input leakage current          | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | -      | ±1                 | μΑ   |

Table 27. Low-speed external user clock characteristics<sup>(1)</sup>

1. Guaranteed by design.

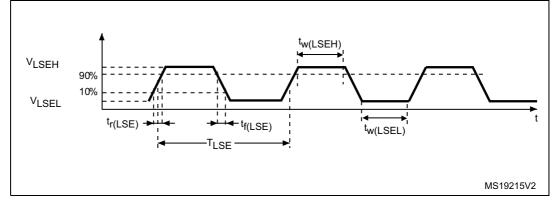

## High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 1 to 24 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 28*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

Figure 17. HSE oscillator circuit diagram

1. R<sub>EXT</sub> value depends on the crystal characteristics.

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 29*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                                                                                     | Conditions                            | Min | Тур    | Мах | Unit |  |

|-------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------|-----|--------|-----|------|--|

| f <sub>LSE</sub>                    | Low speed external oscillator<br>frequency                                                    | -                                     | -   | 32.768 | -   | kHz  |  |

| R <sub>F</sub>                      | Feedback resistor                                                                             | -                                     | -   | 1.2    | -   | MΩ   |  |

| C <sup>(2)</sup>                    | Recommended load capacitance versus equivalent serial resistance of the crystal $(R_S)^{(3)}$ | R <sub>S</sub> = 30 kΩ                | -   | 8      | -   | pF   |  |

| I <sub>LSE</sub>                    | LSE driving current                                                                           | $V_{DD}$ = 3.3 V, $V_{IN}$ = $V_{SS}$ | -   | -      | 1.1 | μA   |  |

|                                     |                                                                                               | V <sub>DD</sub> = 1.8 V               | -   | 450    | -   |      |  |

| I <sub>DD (LSE)</sub>               | LSE oscillator current<br>consumption                                                         | V <sub>DD</sub> = 3.0 V               | -   | 600    | -   | nA   |  |

|                                     |                                                                                               | V <sub>DD</sub> = 3.6V                | -   | 750    | -   |      |  |

| 9 <sub>m</sub>                      | Oscillator transconductance                                                                   | -                                     | 3   | -      | -   | µA/V |  |

| t <sub>SU(LSE)</sub> <sup>(4)</sup> | Startup time                                                                                  | V <sub>DD</sub> is stabilized         | -   | 1      | -   | s    |  |

| Table 29. LSE oscillator characteristics | s (f <sub>LSE</sub> = 32.768 kHz) <sup>(1)</sup> |

|------------------------------------------|--------------------------------------------------|

|------------------------------------------|--------------------------------------------------|

1. Guaranteed by characterization results.

2. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

The oscillator selection can be optimized in terms of supply current using an high quality resonator with small R<sub>S</sub> value for example MSIV-TIN32.768kHz. Refer to crystal manufacturer for more details.

# Multi-speed internal (MSI) RC oscillator

|                                       | Table 32. MSI oscillator characteristics                                                 |                                          |      |     |      |

|---------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------|------|-----|------|

| Symbol                                | Parameter                                                                                | Condition                                | Тур  | Мах | Unit |

|                                       |                                                                                          | MSI range 0                              | 65.5 | -   |      |

|                                       |                                                                                          | MSI range 1                              | 131  | -   | ku-  |

|                                       |                                                                                          | MSI range 2                              | 262  | -   | kHz  |

| f <sub>MSI</sub>                      | Frequency after factory calibration, done at $V_{DD}$ = 3.3 V and T <sub>A</sub> = 25 °C | MSI range 3                              | 524  | -   |      |

|                                       |                                                                                          | MSI range 4                              | 1.05 | -   |      |

|                                       |                                                                                          | MSI range 5                              | 2.1  | -   | MHz  |

|                                       |                                                                                          | MSI range 6                              | 4.2  | -   |      |

| ACC <sub>MSI</sub>                    | Frequency error after factory calibration                                                | -                                        | ±0.5 | -   | %    |

| D <sub>TEMP(MSI)</sub> <sup>(1)</sup> | MSI oscillator frequency drift<br>0 °C ≤T <sub>A</sub> ≤85 °C                            | -                                        | ±3   | -   | %    |

| D <sub>VOLT(MSI)</sub> <sup>(1)</sup> | MSI oscillator frequency drift<br>1.65 V ≤V <sub>DD</sub> ≤3.6 V, T <sub>A</sub> = 25 °C | -                                        | 2.5  | %/V |      |

|                                       |                                                                                          | MSI range 0                              | 0.75 | -   |      |

|                                       | MSI oscillator power consumption                                                         | MSI range 1                              | 1    | -   |      |

|                                       |                                                                                          | MSI range 2                              | 1.5  | -   | μA   |

| I <sub>DD(MSI)</sub> <sup>(2)</sup>   |                                                                                          | MSI range 3                              | 2.5  | -   |      |

|                                       |                                                                                          | MSI range 4                              | 4.5  | -   |      |

|                                       |                                                                                          | MSI range 5                              | 8    | -   |      |

|                                       |                                                                                          | MSI range 6                              | 15   | -   |      |

|                                       |                                                                                          | MSI range 0                              | 30   | -   |      |

|                                       |                                                                                          | MSI range 1                              | 20   | -   |      |

| <sup>t</sup> su(msi)                  |                                                                                          | MSI range 2                              | 15   | -   | 1    |

|                                       |                                                                                          | MSI range 3                              | 10   | -   |      |

|                                       | MSI oscillator startup time                                                              | MSI range 4                              | 6    | -   | - µs |

|                                       |                                                                                          | MSI range 5                              | 5    | -   |      |

|                                       |                                                                                          | MSI range 6,<br>Voltage range 1<br>and 2 | 3.5  | -   |      |

|                                       |                                                                                          | MSI range 6,<br>Voltage range 3          | 5    | -   |      |

## Table 32. MSI oscillator characteristics

#### **SPI characteristics**

Unless otherwise specified, the parameters given in the following table are derived from tests performed under ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 13*.

Refer to *Section 6.3.12: I/O current injection characteristics* for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                                                                     | Parameter                        | Conditions                 | Min                       | Max <sup>(2)</sup>        | Unit |

|----------------------------------------------------------------------------|----------------------------------|----------------------------|---------------------------|---------------------------|------|

| _                                                                          |                                  | Master mode                | -                         | 16                        |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>                                  | SPI clock frequency              | Slave mode                 | -                         | 16                        | MHz  |

|                                                                            |                                  | Slave transmitter          | -                         | 12 <sup>(3)</sup>         |      |

| t <sub>r(SCK)</sub> <sup>(2)</sup><br>t <sub>f(SCK)</sub> <sup>(2)</sup>   | SPI clock rise and fall time     | Capacitive load: C = 30 pF | -                         | 6                         | ns   |

| DuCy(SCK)                                                                  | SPI slave input clock duty cycle | Slave mode                 | 30                        | 70                        | %    |

| t <sub>su(NSS)</sub>                                                       | NSS setup time                   | Slave mode                 | 4t <sub>HCLK</sub>        | -                         |      |

| t <sub>h(NSS)</sub>                                                        | NSS hold time                    | Slave mode                 | 2t <sub>HCLK</sub>        | -                         |      |

| t <sub>w(SCKH)</sub> <sup>(2)</sup><br>t <sub>w(SCKL)</sub> <sup>(2)</sup> | SCK high and low time            | Master mode                | t <sub>SCK</sub> /2–<br>5 | t <sub>SCK</sub> /2+<br>3 |      |

| t <sub>su(MI)</sub> <sup>(2)</sup>                                         | Data input setup time            | Master mode                | 5                         | -                         |      |

| t <sub>su(SI)</sub> <sup>(2)</sup>                                         | Data input setup time            | Slave mode                 | 6                         | -                         |      |

| t <sub>h(MI)</sub> <sup>(2)</sup>                                          | Data input hold time             | Master mode                | 5                         | -                         | ns   |

| t <sub>h(SI)</sub> <sup>(2)</sup>                                          |                                  | Slave mode                 | 5                         | -                         |      |

| t <sub>a(SO)</sub> <sup>(4)</sup>                                          | Data output access time          | Slave mode                 | 0                         | 3t <sub>HCLK</sub>        |      |

| t <sub>v(SO)</sub> (2)                                                     | Data output valid time           | Slave mode                 | -                         | 33                        |      |

| t <sub>v(MO)</sub> <sup>(2)</sup>                                          | Data output valid time           | Master mode                | -                         | 6.5                       |      |

| t <sub>h(SO)</sub> <sup>(2)</sup>                                          | Data output hold time            | Slave mode                 | 17                        | -                         |      |

| t <sub>h(MO)</sub> <sup>(2)</sup>                                          | Data output hold time            | Master mode                | 0.5                       | -                         |      |

| Table 49. SPI characteristics | ble 49. SPI characteristics | (1) |

|-------------------------------|-----------------------------|-----|

|-------------------------------|-----------------------------|-----|

1. The characteristics above are given for voltage Range 1.

2. Guaranteed by characterization results.

3. The maximum SPI clock frequency in slave transmitter mode is given for an SPI slave input clock duty cycle (DuCy(SCK)) ranging between 40 to 60%.

4. Min time is for the minimum time to drive the output and max time is for the maximum time to validate the data.

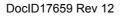

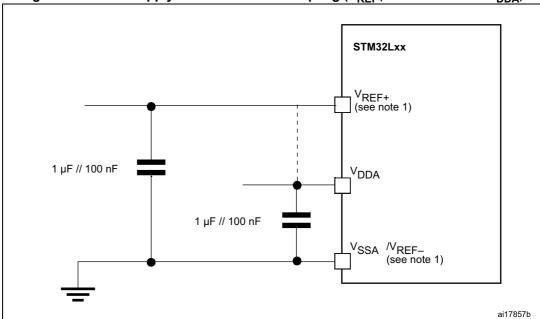

Figure 29. Power supply and reference decoupling (V<sub>REF+</sub> not connected to V<sub>DDA</sub>)

1.  $V_{\mathsf{REF}^+}$  and  $V_{\mathsf{REF}^-}$  inputs are available only on 100-pin packages.

1.  $V_{\mathsf{REF}\text{+}}$  and  $V_{\mathsf{REF}\text{-}}$  inputs are available only on 100-pin packages.

| Symbol                    | Parameter                                                                                                                                                       | Conditions                                                                         | Min | Тур             | Мах              | Unit  |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----|-----------------|------------------|-------|

| dOffset/dT <sup>(1)</sup> | Offset error temperature                                                                                                                                        | $V_{DDA} = 3.3V$ , $T_A = 0$ to 50 ° C<br>DAC output buffer OFF                    | -20 | -10             | 0                |       |

|                           | coefficient (code 0x800)                                                                                                                                        | $V_{DDA} = 3.3V$ , $T_A = 0$ to 50 ° C<br>DAC output buffer ON                     | 0   | 20              | 50               | µV/°C |

| Gain <sup>(1)</sup>       | Gain error <sup>(6)</sup>                                                                                                                                       | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON         | -   | +0.1 /<br>-0.2% | +0.2 / -<br>0.5% | %     |

| Gain                      | Gain enor                                                                                                                                                       | No R <sub>LOAD</sub> , C <sub>L</sub> ≤50 pF<br>DAC output buffer OFF              | -   | +0 / -0.2%      | +0 / -0.4%       | 70    |

| dGain/dT <sup>(1)</sup>   | Gain error temperature                                                                                                                                          | $V_{DDA} = 3.3V$ , $T_A = 0$ to 50 ° C<br>DAC output buffer OFF                    | -10 | -2              | 0                | μV/°C |

|                           | coefficient                                                                                                                                                     | $V_{DDA} = 3.3V$ , $T_A = 0$ to 50 ° C<br>DAC output buffer ON                     | -40 | -8              | 0                | μν/ Ο |

| TUE <sup>(1)</sup>        | Total unadjusted error                                                                                                                                          | $C_L \le 50 \text{ pF}, \text{ R}_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON | -   | 12              | 30               |       |

|                           |                                                                                                                                                                 | No R <sub>LOAD</sub> , C <sub>L</sub> ≤50 pF<br>DAC output buffer OFF              | -   | 8               | 12               | LSB   |

| tSETTLING                 | Settling time (full scale:<br>for a 12-bit code<br>transition between the<br>lowest and the highest<br>input codes till<br>DAC_OUT reaches final<br>value ±1LSB | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                 | -   | 7               | 12               | μs    |

| Update rate               | Max frequency for a<br>correct DAC_OUT<br>change (95% of final<br>value) with 1 LSB<br>variation in the input<br>code                                           | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                 | -   | -               | 1                | Msps  |

| t <sub>wakeup</sub>       | Wakeup time from off<br>state (setting the ENx bit<br>in the DAC Control<br>register) <sup>(7)</sup>                                                            | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                 | -   | 9               | 15               | μs    |

| PSRR+                     | V <sub>DDA</sub> supply rejection<br>ratio (static DC<br>measurement)                                                                                           | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                 | -   | -60             | -35              | dB    |

#### Table 57. DAC characteristics (continued)

1. Guaranteed by characterization results.

2. Difference between two consecutive codes - 1 LSB.

3. Difference between measured value at Code i and the value at Code i on a line drawn between Code 0 and last Code 4095.

4. Difference between the value measured at Code (0x800) and the ideal value = V/2.

5. Difference between the value measured at Code (0x001) and the ideal value.

6. Difference between ideal slope of the transfer function and measured slope computed from code 0x000 and 0xFFF when buffer is OFF, and from code giving 0.2 V and ( $V_{DDA} - 0.2$ ) V when buffer is ON.

7. In buffered mode, the output can overshoot above the final value for low input code (starting from min value).

# 6.3.21 LCD controller (STM32L152xx only)

The STM32L152xx embeds a built-in step-up converter to provide a constant LCD reference voltage independently from the V<sub>DD</sub> voltage. An external capacitor C<sub>ext</sub> must be connected to the V<sub>LCD</sub> pin to decouple this converter.

| Symbol                           | Parameter                                                | Min  | Тур                  | Max       | Unit |  |

|----------------------------------|----------------------------------------------------------|------|----------------------|-----------|------|--|

| $V_{LCD}$                        | LCD external voltage                                     | -    | -                    | 3.6       |      |  |

| V <sub>LCD0</sub>                | LCD internal reference voltage 0                         | -    | 2.6                  | -         |      |  |

| V <sub>LCD1</sub>                | LCD internal reference voltage 1                         | -    | 2.73                 | -         |      |  |

| V <sub>LCD2</sub>                | LCD internal reference voltage 2                         | -    | 2.86                 | -         |      |  |

| $V_{LCD3}$                       | LCD internal reference voltage 3                         | -    | 2.98                 | -         | V    |  |

| V <sub>LCD4</sub>                | LCD internal reference voltage 4                         | -    | 3.12                 | -         |      |  |

| $V_{LCD5}$                       | LCD internal reference voltage 5                         | -    | 3.26                 | -         | Ţ    |  |

| V <sub>LCD6</sub>                | LCD internal reference voltage 6                         | -    | 3.4                  | -         |      |  |

| $V_{LCD7}$                       | LCD internal reference voltage 7                         | -    | 3.55                 | -         | Ţ    |  |

| C <sub>ext</sub>                 | V <sub>LCD</sub> external capacitance                    | 0.1  | -                    | 2         | μF   |  |

| I <sub>LCD</sub> <sup>(1)</sup>  | Supply current at V <sub>DD</sub> = 2.2 V                | -    | 3.3                  | -         |      |  |

|                                  | Supply current at V <sub>DD</sub> = 3.0 V                | -    | 3.1                  | -         | μA   |  |

| R <sub>Htot</sub> <sup>(2)</sup> | Low drive resistive network overall value                | 5.28 | 6.6                  | 7.92      | MΩ   |  |

| $R_L^{(2)}$                      | High drive resistive network total value                 | 192  | 240                  | 288       | kΩ   |  |

| V <sub>44</sub>                  | Segment/Common highest level voltage                     | -    | -                    | $V_{LCD}$ | V    |  |

| V <sub>34</sub>                  | Segment/Common 3/4 level voltage                         | -    | 3/4 V <sub>LCD</sub> | -         |      |  |

| V <sub>23</sub>                  | Segment/Common 2/3 level voltage                         | -    | 2/3 V <sub>LCD</sub> | -         |      |  |

| V <sub>12</sub>                  | Segment/Common 1/2 level voltage                         | -    | 1/2 V <sub>LCD</sub> | -         |      |  |

| V <sub>13</sub>                  | Segment/Common 1/3 level voltage                         | -    | 1/3 V <sub>LCD</sub> | -         | V    |  |

| V <sub>14</sub>                  | Segment/Common 1/4 level voltage                         | -    | 1/4 V <sub>LCD</sub> | -         | 1    |  |

| V <sub>0</sub>                   | Segment/Common lowest level voltage                      | 0    | -                    | -         | 1    |  |

| $\Delta Vxx^{(3)}$               | Segment/Common level voltage error $T_A$ = -40 to 85 ° C | -    | -                    | ±50       | mV   |  |

|  | Table 62 | . LCD | controller | characteristics |

|--|----------|-------|------------|-----------------|

|--|----------|-------|------------|-----------------|

1. LCD enabled with 3 V internal step-up active, 1/8 duty, 1/4 bias, division ratio= 64, all pixels active, no LCD connected

2. Guaranteed by design.

3. Guaranteed by characterization results.

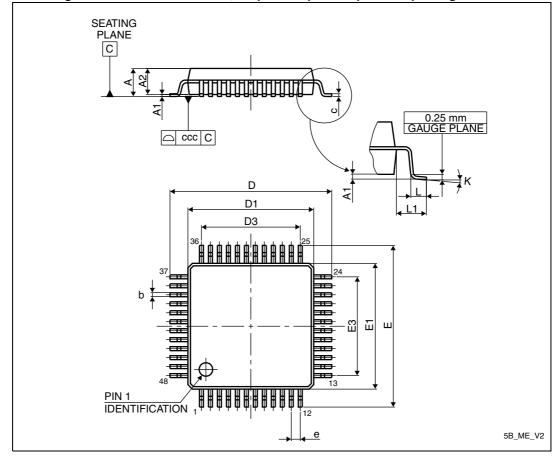

# 7.3 LQFP48 7 x 7 mm, 48-pin low-profile quad flat package information

Figure 38. LQFP48 7 x 7 mm, 48-pin low-profile quad flat package outline

1. Drawing is not to scale.

# 7.7 Thermal characteristics

The maximum chip-junction temperature,  $T_J$  max, in degrees Celsius, may be calculated using the following equation:

$T_J \max = T_A \max + (P_D \max \times \Theta_{JA})$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in ° C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

P<sub>I/O</sub> max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I}/\mathsf{O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

| Symbol        | Parameter                                                                  | Value | Unit |

|---------------|----------------------------------------------------------------------------|-------|------|

|               | Thermal resistance junction-ambient<br>BGA100 - 7 x 7 mm                   | 59    |      |

|               | Thermal resistance junction-ambient<br>LQFP100 - 14 x 14 mm / 0.5 mm pitch | t 46  |      |

| 0             | <b>Thermal resistance junction-ambient</b><br>TFBGA64 - 5 x 5 mm           | 65    |      |

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>LQFP64 - 10 x 10 mm / 0.5 mm pitch  | 45    | °C/W |

|               | Thermal resistance junction-ambient<br>LQFP48 - 7 x 7 mm / 0.5 mm pitch    | 55    |      |

|               | Thermal resistance junction-ambient16UFQFPN48 - 7 x 7 mm / 0.5 mm pitch16  |       |      |

Table 71. Thermal characteristics

| Date        | Revision | . Document revision history (continued)<br>Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date        | Revision | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 12-Nov-2013 | 9        | Changed voltage Range 1 minimum to 1.71 V and updated dynamic voltage scaling range in Table 3: Functionalities depending on the operating power supply range Updated LCD and ADC features and peripheral counts. Updated LCD and ADC features and peripheral counts. Updated Table 3: Functionalities depending on the operating power supply range. Updated Table 5: Working mode-dependent functionalities (from <i>Run/active down to standby</i> ). Updated Table 5: STM32L15xV6 UFBGA100 ballout Added Table 7: Legend/abbreviations used in the pinout table. Updated Table 8: STM32L15xV6/ <i>B</i> pin definitions Updated Table 10: Pin loading conditions and Figure 11: Pin input voltage. Updated Figure 12: Power supply scheme. Replaced "Σ" by "o" in Section 6.1.1 and Section 6.1.2. Updated Table 10: Voltage characteristics. Updated Table 13: General operating conditions. Added Section 6.1.7: Optional LCD power supply scheme. Updated Table 16: Embedded internal reference voltage. Added this Note in Section 1: High-speed external clock generated from a crystal/ceramic resonator Updated Section : Functional susceptibility to I/O current injection. This Section 6.3.5: Wakeup time from Low power mode was previously a paragraph in Section 6.3.4: Supply current characteristics. Updated f <sub>15E</sub> conditions in Table 17: Current consumption in Run mode, code with data processing running from Flash and Table 18: Current consumption in Run mode, code with data processing running from Flash and Table 18: Current consumptions in Standby mode. This Figure 15: High-speed external clock source AC timing diagram. Updated Table 28: Low-power mode wakeup timings tilte. Updated Table 28: Low-power mode wakeup timings tilte. Updated Table 28: HSE oscillator characteristics and Table 29: LSE oscillator characteristics. The taracteristics tilte. Updated Table 28: ESD absolute maximum ratings. Updated Table 28: HSE oscilla |