Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                     |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                    |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, POR, PWM, WDT |

| Number of I/O              | 51                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 4K x 8                                                                  |

| RAM Size                   | 16K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Data Converters            | A/D 20x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-TFBGA                                                                |

| Supplier Device Package    | 64-TFBGA (5x5)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l151rbh6   |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of figures

| Figure 1.                 | Ultra-low-power STM32L151x6/8/B and STM32L152x6/8/B block diagram                            | 13    |

|---------------------------|----------------------------------------------------------------------------------------------|-------|

| Figure 2.                 | Clock tree                                                                                   |       |

| Figure 3.                 | STM32L15xVx UFBGA100 ballout                                                                 | 31    |

| Figure 4.                 | STM32L15xVx LQFP100 pinout                                                                   | 32    |

| Figure 5.                 | STM32L15xRx TFBGA64 ballout                                                                  |       |

| Figure 6.                 | STM32L15xRx LQFP64 pinout                                                                    |       |

| Figure 7.                 | STM32L15xCx LQFP48 pinout                                                                    |       |

| Figure 8.                 | STM32L15xCx UFQFPN48 pinout                                                                  |       |

| Figure 9.                 | Memory map                                                                                   |       |

| Figure 10.                | Pin loading conditions.                                                                      |       |

| Figure 11.                | Pin input voltage                                                                            |       |

| Figure 12.                | Power supply scheme.                                                                         |       |

| Figure 13.                | Optional LCD power supply scheme                                                             |       |

| Figure 14.                | Current consumption measurement scheme                                                       |       |

| Figure 15.                | High-speed external clock source AC timing diagram                                           |       |

| Figure 16.                | Low-speed external clock source AC timing diagram                                            |       |

| Figure 17.                | HSE oscillator circuit diagram                                                               |       |

| Figure 18.                | Typical application with a 32.768 kHz crystal                                                |       |

| Figure 18.                | I/O AC characteristics definition                                                            |       |

| •                         | Recommended NRST pin protection                                                              |       |

| Figure 20.                |                                                                                              |       |

| Figure 21.                | I <sup>2</sup> C bus AC waveforms and measurement circuit                                    |       |

| Figure 22.                | SPI timing diagram - slave mode and CPHA = $0$                                               |       |

| Figure 23.                | SPI timing diagram - slave mode and CPHA = $1^{(1)}$                                         | 90    |

| Figure 24.                | SPI timing diagram - master mode <sup>(1)</sup>                                              |       |

| Figure 25.                | USB timings: definition of data signal rise and fall time                                    |       |

| Figure 26.                | ADC accuracy characteristics                                                                 | 96    |

| Figure 27.                | Typical connection diagram using the ADC                                                     | 96    |

| Figure 28.                | Maximum dynamic current consumption on V <sub>REF+</sub> supply pin during ADC               |       |

|                           | conversion                                                                                   |       |

| Figure 29.                | Power supply and reference decoupling (V <sub>REF+</sub> not connected to V <sub>DDA</sub> ) |       |

| Figure 30.                | Power supply and reference decoupling (V <sub>REF+</sub> connected to V <sub>DDA</sub> )     | 98    |

| Figure 31.                | 12-bit buffered /non-buffered DAC                                                            |       |

| Figure 32.                | LQFP100 14 x 14 mm, 100-pin low-profile quad flat package outline                            | . 105 |

| Figure 33.                | LQPF100 14 x 14 mm, 100-pin low-profile quad flat package recommended footprint .            | . 107 |

| Figure 34.                | LQFP100 14 x 14 mm, 100-pin package top view example                                         | . 107 |

| Figure 35.                | LQFP64 10 x 10 mm, 64-pin low-profile quad flat package outline                              | . 108 |

| Figure 36.                | LQFP64 10 x 10 mm, 64-pin low-profile quad flat package recommended footprint                | . 109 |

| Figure 37.                | LQFP64 10 x 10 mm, 64-pin low-profile quad flat package top view example                     |       |

| Figure 38.                | LQFP48 7 x 7 mm, 48-pin low-profile quad flat package outline                                |       |

| Figure 39.                | LQFP48 7 x 7 mm, 48-pin low-profile quad flat recommended footprint.                         |       |

| Figure 40.                | LQFP48 7 x 7 mm, 48-pin low-profile quad flat package top view example                       |       |

| Figure 41.                | UFQFPN48 7 x 7 mm, 0.5 mm pitch, package outline                                             |       |

| Figure 42.                | UFQFPN48 7 x 7 mm, 0.5 mm pitch, package recommended footprint                               | 115   |

| Figure 43.                | UFQFPN48 7 x 7 mm, 0.5 mm pitch, package top view example                                    | 116   |

| Figure 44.                | UFBGA100, 7 x 7 mm, 0.5 mm pitch, package outline                                            |       |

| Figure 45.                | UFBGA100 7 x 7 mm, 0.5 mm pitch, package recommended footprint                               | 118   |

| Figure 46.                | UFBGA100 7 x 7 mm, 0.5 mm pitch, package top view example.                                   |       |

| Figure 40.<br>Figure 47.  | TFBGA64 5 x 5 mm, 0.5 mm pitch, package outline                                              |       |

| $r_{i}$ guie $\tau_{i}$ . |                                                                                              | . 120 |

# **3** Functional overview

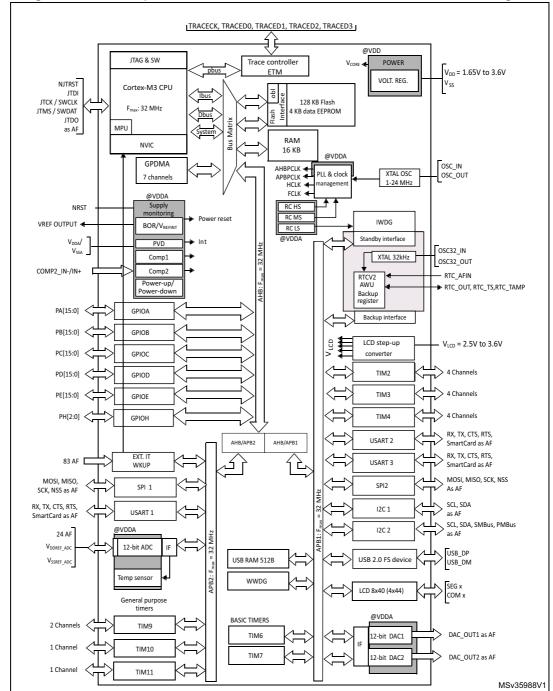

Figure 1 shows the block diagram.

#### Figure 1. Ultra-low-power STM32L151x6/8/B and STM32L152x6/8/B block diagram

1. AF = alternate function on I/O port pin.

# 3.1 Low power modes

The ultra-low-power STM32L151x6/8/B and STM32L152x6/8/B devices support dynamic voltage scaling to optimize its power consumption in run mode. The voltage from the internal low-drop regulator that supplies the logic can be adjusted according to the system's maximum operating frequency and the external voltage supply:

- In Range 1 (V<sub>DD</sub> range limited to 1.71-3.6 V), the CPU runs at up to 32 MHz (refer to Table 17 for consumption).

- In Range 2 (full V<sub>DD</sub> range), the CPU runs at up to 16 MHz (refer to *Table 17* for consumption)

- In Range 3 (full V<sub>DD</sub> range), the CPU runs at up to 4 MHz (generated only with the multispeed internal RC oscillator clock source). Refer to *Table 17* for consumption.

Seven low power modes are provided to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

• Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

Sleep mode power consumption: refer to *Table 19*.

Low power run mode

This mode is achieved with the multispeed internal (MSI) RC oscillator set to the minimum clock (65 kHz), execution from SRAM or Flash memory, and internal regulator in low power mode to minimize the regulator's operating current. In the Low power run mode, the clock frequency and the number of enabled peripherals are both limited.

Low power run mode consumption: refer to *Table 20: Current consumption in Low power run mode*.

#### Low power sleep mode

This mode is achieved by entering the Sleep mode with the internal voltage regulator in Low power mode to minimize the regulator's operating current. In the Low power sleep mode, both the clock frequency and the number of enabled peripherals are limited; a typical example would be to have a timer running at 32 kHz.

When wakeup is triggered by an event or an interrupt, the system reverts to the run mode with the regulator on.

Low power sleep mode consumption: refer to *Table 21: Current consumption in Low power sleep mode*.

• Stop mode with RTC

Stop mode achieves the lowest power consumption while retaining the RAM and register contents and real time clock. All clocks in the  $V_{CORE}$  domain are stopped, the PLL, MSI RC, HSI RC and HSE crystal oscillators are disabled. The LSE or LSI is still running. The voltage regulator is in the low power mode.

The device can be woken up from Stop mode by any of the EXTI line, in 8 µs. The EXTI line source can be one of the 16 external lines. It can be the PVD output, the Comparator 1 event or Comparator 2 event (if internal reference voltage is on), it can be the RTC alarm(s), the USB wakeup, the RTC tamper events, the RTC timestamp event or the RTC wakeup.

• **Stop** mode without RTC

Stop mode achieves the lowest power consumption while retaining the RAM and register contents. All clocks are stopped, the PLL, MSI RC, HSI and LSI RC, LSE and

|                                              |                       |                      | Low-         | Low-           |   | Stop                                  | 5                                        | Standby                                |

|----------------------------------------------|-----------------------|----------------------|--------------|----------------|---|---------------------------------------|------------------------------------------|----------------------------------------|

| lps                                          | Run/Active            | Sleep                | power<br>Run | power<br>Sleep |   | Wakeup<br>capability                  |                                          | Wakeup<br>capability                   |

| DAC                                          | Y                     | Y                    | Y            | Y              | Y | -                                     | -                                        | -                                      |

| Temperature<br>sensor                        | Y                     | Y                    | Y            | Y              | Y | -                                     | -                                        | -                                      |

| Comparators                                  | Y                     | Y                    | Y            | Y              | Y | Y                                     | -                                        | -                                      |

| 16-bit and 32-bit<br>Timers                  | Y                     | Y                    | Y            | Y              | - | -                                     | -                                        | -                                      |

| IWDG                                         | Y                     | Y                    | Y            | Y              | Y | Y                                     | Y                                        | Y                                      |

| WWDG                                         | Y                     | Y                    | Y            | Y              | - | -                                     | -                                        | -                                      |

| Touch sensing                                | Y                     | -                    | -            | -              | - | -                                     | -                                        | -                                      |

| Systick Timer                                | Y                     | Y                    | Y            | Y              | - | -                                     | -                                        | -                                      |

| GPIOs                                        | Y                     | Y                    | Y            | Y              | Y | Y                                     | -                                        | 3 Pins                                 |

| Wakeup time to<br>Run mode                   | 0 µs                  | 0.36 µs              | 3 µs         | 32 µs          |   | < 8 µs                                |                                          | 50 µs                                  |

|                                              |                       |                      |              |                |   | 5 µA (No<br>) V <sub>DD</sub> =1.8V   |                                          | IA (No RTC)<br>/ <sub>DD</sub> =1.8V   |

| Consumption<br>V <sub>DD</sub> =1.8V to 3.6V | Down to<br>214 µA/MHz | Down to<br>50 µA/MHz | Down to      | Down to        |   | 4 μΑ (with<br>) V <sub>DD</sub> =1.8V |                                          | (with RTC)<br>/ <sub>DD</sub> =1.8V    |

| (Typ)                                        | (from Flash)          | (from Flash)         | 9 µA         | 4.4 µA         |   | 5 µA (No<br>) V <sub>DD</sub> =3.0V   | 0.3 μA (No RTC)<br>V <sub>DD</sub> =3.0V |                                        |

|                                              |                       |                      |              |                |   | δ μΑ (with<br>) V <sub>DD</sub> =3.0V |                                          | 3 µA (with<br>≎) V <sub>DD</sub> =3.0V |

| Table 5. Working mode-dependent functionalities | (from Run/active down to standby) (continued) |

|-------------------------------------------------|-----------------------------------------------|

|                                                 |                                               |

1. The startup on communication line wakes the CPU which was made possible by an EXTI, this induces a delay before entering run mode.

# 3.2 ARM<sup>®</sup> Cortex<sup>®</sup>-M3 core with MPU

The ARM<sup>®</sup> Cortex<sup>®</sup>-M3 processor is the industry leading processor for embedded systems. It has been developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced system response to interrupts.

The ARM<sup>®</sup> Cortex<sup>®</sup>-M3 32-bit RISC processor features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

The memory protection unit (MPU) improves system reliability by defining the memory attributes (such as read/write access permissions) for different memory regions. It provides up to eight different regions and an optional predefined background region.

Owing to its embedded ARM core, the STM32L151x6/8/B and STM32L152x6/8/B devices are compatible with all ARM tools and software.

This dual digital Interface supports the following features:

- two DAC converters: one for each output channel

- left or right data alignment in 12-bit mode

- synchronized update capability

- noise-wave generation

- triangular-wave generation

- dual DAC channels' independent or simultaneous conversions

- DMA capability for each channel (including the underrun interrupt)

- external triggers for conversion

- input reference voltage V<sub>REF+</sub>

Eight DAC trigger inputs are used in the STM32L151x6/8/B and STM32L152x6/8/B devices. The DAC channels are triggered through the timer update outputs that are also connected to different DMA channels.

# 3.12 Ultra-low-power comparators and reference voltage

The STM32L151x6/8/B and STM32L152x6/8/B devices embed two comparators sharing the same current bias and reference voltage. The reference voltage can be internal or external (coming from an I/O).

- one comparator with fixed threshold

- one comparator with rail-to-rail inputs, fast or slow mode. The threshold can be one of the following:

- DAC output

- External I/O

- Internal reference voltage (V<sub>REFINT</sub>) or V<sub>REFINT</sub> submultiple (1/4, 1/2, 3/4)

Both comparators can wake up from Stop mode, and be combined into a window comparator.

The internal reference voltage is available externally via a low power / low current output buffer (driving current capability of 1  $\mu$ A typical).

# 3.13 Routing interface

This interface controls the internal routing of I/Os to TIM2, TIM3, TIM4 and to the comparator and reference voltage output.

# 3.14 Touch sensing

The STM32L151x6/8/B and STM32L152x6/8/B devices provide a simple solution for adding capacitive sensing functionality to any application. These devices offer up to 20 capacitive sensing channels distributed over 10 analog I/O groups. Only software capacitive sensing acquisition mode is supported.

Capacitive sensing technology is able to detect the presence of a finger near a sensor which is protected from direct touch by a dielectric (glass, plastic, ...). The capacitive variation introduced by the finger (or any conductive object) is measured using a proven

#### STM32L151x6/8/B STM32L152x6/8/B

|   | 1                        | 2                 | 3       | 4                    | 5       | 6      | 7       | 8      |

|---|--------------------------|-------------------|---------|----------------------|---------|--------|---------|--------|

| A | •<br>/PC14-,<br>OŚC32_IN | , PC13-,<br>WKUP2 | ( PB9 ) | ( PB4 )              | ( PB3 ) | (PA15) | (PA14)  | (PA13) |

| В | /PC15-,<br>OSC32_OUT     | VLCD              | (PB8)   | ВООТО                | (PD2)   | (PC11) | (PC10)  | (PA12) |

| С | , ₽ĤŎ÷,<br>OSC_IN∳       | VSS_4             | ( PB7 ) | (PB5)                | (PC12)  | (PA10) | ( PA9 ) | (PA11) |

| D | OSC_OUT                  | V <sub>DD_4</sub> | (PB6)   | ,V <sub>SS_3</sub> , | VSS_2   | VSS_1  | ( PA8 ) | (PC9)  |

| E | (NRST)                   | (PC1)             | PC0     | 'VDD_3'              | 'VDD_2' | VDD_1  | (PC7)   | (PC8)  |

| F | (Vssa)                   | (PC2)             | (PA2)   | ( PA5 )              | (PB0)   | (PC6)  | (PB15)  | (PB14) |

| G | WREF+ F                  | PA(0-WKU)P1       | ( PA3 ) | ( PA6 )              | (PB1)   | (PB2)  | (PB10)  | (PB13) |

| н | VDDA,                    | ( PA1 )           | (PA4)   | ( PA7 )              | (PC4)   | PC5    | (PB11)  | (PB12) |

Figure 5. STM32L15xRx TFBGA64 ballout

1. This figure shows the package top view.

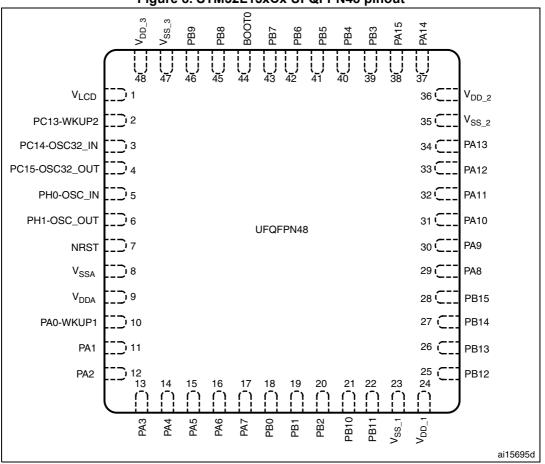

Figure 8. STM32L15xCx UFQFPN48 pinout

1. This figure shows the package top view.

|         |        | Pins    | 5        |                    |                   |                         |               |                                                  | Pins functions                                 |                         |

|---------|--------|---------|----------|--------------------|-------------------|-------------------------|---------------|--------------------------------------------------|------------------------------------------------|-------------------------|

| LQFP100 | LQFP64 | TFBGA64 | UFBGA100 | LQFP48 or UFQFPN48 | Pin name          | Pin type <sup>(1)</sup> | I/O structure | Main<br>function <sup>(2)</sup><br>(after reset) | Alternate functions                            | Additional<br>functions |

| 90      | 56     | A4      | A7       | 40                 | PB4               | I/O                     | FT            | NJTRST                                           | TIM3_CH1/PB4/<br>SPI1_MISO/LCD_SEG8/<br>NJTRST | COMP2_INP               |

| 91      | 57     | C4      | C5       | 41                 | PB5               | I/O                     | FT            | PB5                                              | I2C1_SMBA/TIM3_CH2/<br>SPI1_MOSI/LCD_SEG9      | COMP2_INP               |

| 92      | 58     | D3      | B5       | 42                 | PB6               | I/O                     | FT            | PB6                                              | I2C1_SCL/TIM4_CH1/<br>USART1_TX                |                         |

| 93      | 59     | C3      | B4       | 43                 | PB7               | I/O                     | FT            | PB7                                              | I2C1_SDA/TIM4_CH2/<br>USART1_RX                | PVD_IN                  |

| 94      | 60     | B4      | A4       | 44                 | BOOT0             | Ι                       | В             | BOOT0                                            | -                                              | -                       |

| 95      | 61     | B3      | A3       | 45                 | PB8               | I/O                     | FT            | PB8                                              | TIM4_CH3/I2C1_SCL/<br>LCD_SEG16/TIM10_CH1      | -                       |

| 96      | 62     | A3      | B3       | 46                 | PB9               | I/O                     | FT            | PB9                                              | TIM4_CH4/I2C1_SDA/<br>LCD_COM3/TIM11_CH1       | -                       |

| 97      | -      | -       | C3       | -                  | PE0               | I/O                     | FT            | PE0                                              | TIM4_ETR/LCD_SEG36/<br>TIM10_CH1               | -                       |

| 98      | -      | -       | A2       | -                  | PE1               | I/O                     | FT            | PE1                                              | LCD_SEG37/TIM11_CH1                            | -                       |

| 99      | 63     | D4      | D3       | 47                 | V <sub>SS_3</sub> | S                       | -             | V <sub>SS_3</sub>                                | -                                              | -                       |

| 100     | 64     | E4      | C4       | 48                 | $V_{DD_3}$        | S                       | -             | V <sub>DD_3</sub>                                | -                                              | -                       |

| Table 8. STM32L151x6/8/B and STM32L152x6/8/B pin definitions (continued) | Table 8. STM32L151x6/8/B | 3 and STM32L152x6/8/B | pin definitions | (continued) |

|--------------------------------------------------------------------------|--------------------------|-----------------------|-----------------|-------------|

|--------------------------------------------------------------------------|--------------------------|-----------------------|-----------------|-------------|

1. I = input, O = output, S = supply.

Function availability depends on the chosen device. For devices having reduced peripheral counts, it is always the lower number of peripheral that is included. For example, if a device has only one SPI and two USARTs, they will be called SPI1 and USART1 & USART2, respectively. Refer to *Table 2 on page 11*.

3. Applicable to STM32L152xx devices only. In STM32L151xx devices, this pin should be connected to V<sub>DD</sub>.

4. The PC14 and PC15 I/Os are only configured as OSC32\_IN/OSC32\_OUT when the LSE oscillator is on (by setting the LSEON bit in the RCC\_CSR register). The LSE oscillator pins OSC32\_IN/OSC32\_OUT can be used as general-purpose PC14/PC15 I/Os, respectively, when the LSE oscillator is off (after reset, the LSE oscillator is off). The LSE has priority over the GPIO function. For more details, refer to Using the OSC32\_IN/OSC32\_OUT pins as GPIO PC14/PC15 port pins section in the STM32L1xxxx reference manual (RM0038).

The PH0 and PH1 I/Os are only configured as OSC\_IN/OSC\_OUT when the HSE oscillator is on (by setting the HSEON bit in the RCC\_CR register). The HSE oscillator pins OSC\_IN/OSC\_OUT can be used as general-purpose PH0/PH1 I/Os, respectively, when the HSE oscillator is off (after reset, the HSE oscillator is off). The HSE has priority over the GPIO function.

6. Unlike in the LQFP64 package, there is no PC3 in the TFBGA64 package. The V<sub>REF+</sub> functionality is provided instead.

| Symbol                     | Parameter                               | Cond               | litions                                  |         | Turn  | Max <sup>(1)</sup> |        |      | Unit |

|----------------------------|-----------------------------------------|--------------------|------------------------------------------|---------|-------|--------------------|--------|------|------|

| Symbol                     | Farameter                               | Cond               | f <sub>HCLK</sub>                        | Тур     | 55 °C | 85 °C              | 105 °C | Unit |      |

| I <sub>DD</sub><br>(Sleep) | Supply<br>current in<br>Sleep           | MSI clock, 65 kHz  |                                          | 65 kHz  | 40    | 70                 | 70     | 80   |      |

|                            |                                         | MSI clock, 524 kHz | Range 3,                                 | 524 kHz | 60    | 90                 | 90     | 100  |      |

|                            | mode,<br>code<br>executed<br>from Flash | MSI clock, 4.2 MHz | V <sub>CORE</sub> =1.2V<br>VOS[1:0] = 11 | 4.2 MHz | 210   | 250                | 250    | 260  | μA   |

Table 19. Current consumption in Sleep mode (continued)

1. Guaranteed by characterization results, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register)

3. Tested in production

| Symbol                            | Parameter                                               | Conditions                                                                        | <b>Тур</b><br>(1)                                         | Max<br>(1)(2) | Unit              |    |

|-----------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------|---------------|-------------------|----|

| I <sub>DD (Stop)</sub>            | Supply current                                          | Regulator in LP mode, HSI and<br>HSE OFF, independent<br>watchdog and LSI enabled | $T_A = -40^{\circ}C$ to 25°C                              | 1.1           | 2.2               |    |

|                                   | in Stop mode                                            |                                                                                   | $T_A = -40^{\circ}C$ to $25^{\circ}C$                     | 0.5           | 0.9               | μA |

|                                   |                                                         | Regulator in LP mode, LSI, HSI and HSE OFF (no independent                        | T <sub>A</sub> = 55°C                                     | 1.9           |                   |    |

|                                   |                                                         | watchdog)                                                                         | T <sub>A</sub> = 85°C                                     | 3.7           | 8                 |    |

|                                   |                                                         |                                                                                   | T <sub>A</sub> = 105°C                                    | 8.9           | 20 <sup>(6)</sup> |    |

|                                   | RMS (root                                               | MSI = 4.2 MHz                                                                     |                                                           | 2             | -                 |    |

|                                   | mean square) supply current                             | MSI = 1.05 MHz                                                                    |                                                           | 1.45          | -                 |    |

| I <sub>DD</sub> (WU<br>from Stop) | during wakeup<br>time when<br>exiting from<br>Stop mode | MSI = 65 kHz <sup>(7)</sup>                                                       | V <sub>DD</sub> = 3.0 V<br>T <sub>A</sub> = -40°C to 25°C | 1.45          | -                 | mA |

Table 22. Typical and maximum current consumptions in Stop mode (continued)

1. The typical values are given for V<sub>DD</sub> = 3.0 V and max values are given for V<sub>DD</sub> = 3.6 V, unless otherwise specified.

2. Guaranteed by characterization results, unless otherwise specified

3. LCD enabled with external VLCD, static duty, division ratio = 256, all pixels active, no LCD connected

4. LCD enabled with external VLCD, 1/8 duty, 1/3 bias, division ratio = 64, all pixels active, no LCD connected.

5. Based on characterization done with a 32.768 kHz crystal (MC306-G-06Q-32.768, manufacturer JFVNY) with two 6.8pF loading capacitors.

6. Tested in production

7. When MSI = 64 kHz, the RMS current is measured over the first 15 µs following the wakeup event. For the remaining time of the wakeup period, the current is similar to the Run mode current.

## 6.3.6 External clock source characteristics

#### High-speed external user clock generated from an external source

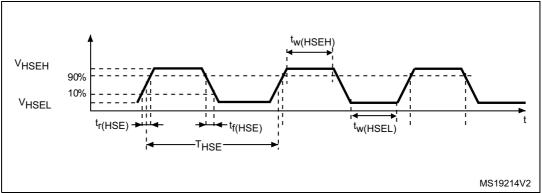

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO. The external clock signal has to respect the I/O characteristics in *Section 6.3.13*. However, the recommended clock input waveform is shown in *Figure 15: High-speed external clock source AC timing diagram*.

| Symbol                                       | Parameter                           | Conditions                       | Min                                                   | Тур | Мах             | Unit |

|----------------------------------------------|-------------------------------------|----------------------------------|-------------------------------------------------------|-----|-----------------|------|

| f                                            | User external clock source          | CSS is on or<br>PLL is used      | 1                                                     | 0   | 30              | MHz  |

| f <sub>HSE_ext</sub>                         | frequency                           | CSS is off, PLL<br>not used      | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ |     |                 |      |

| V <sub>HSEH</sub>                            | OSC_IN input pin high level voltage |                                  | $0.7V_{DD}$                                           | -   | V <sub>DD</sub> | V    |

| V <sub>HSEL</sub>                            | OSC_IN input pin low level voltage  | _                                | V <sub>SS</sub>                                       | -   | $0.3V_{DD}$     | v    |

| t <sub>w(HSEH)</sub><br>t <sub>w(HSEL)</sub> | OSC_IN high or low time             |                                  | 12                                                    | -   | -               | ns   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub>   | OSC_IN rise or fall time            |                                  | -                                                     | -   | 20              | 115  |

| C <sub>in(HSE)</sub>                         | OSC_IN input capacitance            | -                                | -                                                     | 2.6 | -               | pF   |

| DuCy <sub>(HSE)</sub>                        | Duty cycle                          | -                                | 45                                                    | -   | 55              | %    |

| ١L                                           | OSC_IN Input leakage current        | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                                                     | -   | ±1              | μA   |

Table 26. High-speed external user clock characteristics<sup>(1)</sup>

1. Guaranteed by design.

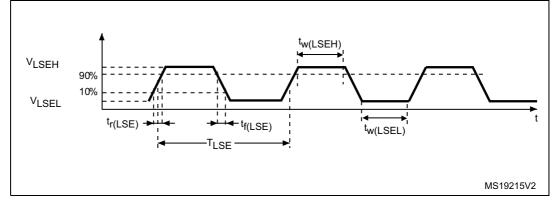

#### Low-speed external user clock generated from an external source

The characteristics given in the following table result from tests performed using a lowspeed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 13*.

| Symbol                                       | Parameter                               | Conditions                       | Min                | Тур    | Max                | Unit |  |

|----------------------------------------------|-----------------------------------------|----------------------------------|--------------------|--------|--------------------|------|--|

| f <sub>LSE_ext</sub>                         | User external clock source<br>frequency |                                  | 1                  | 32.768 | 1000               | kHz  |  |

| V <sub>LSEH</sub>                            | OSC32_IN input pin high level voltage   |                                  | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | v    |  |

| V <sub>LSEL</sub>                            | OSC32_IN input pin low level voltage    | -                                | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> | -    |  |

| t <sub>w(LSEH)</sub><br>t <sub>w(LSEL)</sub> | OSC32_IN high or low time               |                                  | 465                | -      | -                  | ns   |  |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub>   | OSC32_IN rise or fall time              |                                  | -                  | -      | 10                 | 115  |  |

| C <sub>IN(LSE)</sub>                         | OSC32_IN input capacitance              | -                                | -                  | 0.6    | -                  | pF   |  |

| DuCy <sub>(LSE)</sub>                        | Duty cycle                              | -                                | 45                 | -      | 55                 | %    |  |

| ١L                                           | OSC32_IN Input leakage current          | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | -      | ±1                 | μA   |  |

Table 27. Low-speed external user clock characteristics<sup>(1)</sup>

1. Guaranteed by design.

#### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 1 to 24 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 28*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol                      |                         |                                                  |                             | Max vs                      |                              |                              |      |

|-----------------------------|-------------------------|--------------------------------------------------|-----------------------------|-----------------------------|------------------------------|------------------------------|------|

|                             | Parameter               | Conditions                                       | Monitored<br>frequency band | 4 MHz<br>voltage<br>Range 3 | 16 MHz<br>voltage<br>Range 2 | 32 MHz<br>voltage<br>Range 1 | Unit |

|                             |                         | V <sub>DD</sub> = 3.3 V,                         | 0.1 to 30 MHz               | 3                           | -6                           | -5                           |      |

| S <sub>EMI</sub> Peak level | $T_A = 25 \ ^\circ C$ , | 30 to 130 MHz                                    | 18                          | 4                           | -7                           | dBµV                         |      |

|                             | Peak level              | LQFP100 package<br>compliant with IEC<br>61967-2 | 130 MHz to 1GHz             | 15                          | 5                            | -7                           |      |

|                             |                         |                                                  | SAE EMI Level               | 2.5                         | 2                            | 1                            | -    |

#### Table 38. EMI characteristics

### 6.3.11 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114/C101 standard.

| Symbol                | Ratings                                               | Conditions                                         | Packages | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|----------------------------------------------------|----------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)    | $T_A = +25$ °C, conforming to JESD22-A114          | All      | 2     | 2000                            | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model) | T <sub>A</sub> = +25 °C, conforming to JESD22-C101 | All      | 111   | 500                             | v    |

#### Table 39. ESD absolute maximum ratings

1. Guaranteed by characterization results.

#### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latch-up standard.

| Table 40. | Electrical | sensitivities  |

|-----------|------------|----------------|

|           | LICCUITCUI | 30113111411103 |

| Symbol | Parameter             | Conditions                                    | Class      |

|--------|-----------------------|-----------------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +105 \text{ °C conforming to JESD78A}$ | II level A |

#### 6.3.12 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error, out of spec current injection on adjacent pins or other functional failure (for example reset, oscillator frequency deviation, LCD levels, etc.).

The test results are given in Table 41.

#### Table 41. I/O current injection susceptibility

|                  |                                                | Functional s       | usceptibility      |      |

|------------------|------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                    | Negative injection | Positive injection | Unit |

|                  | Injected current on all 5 V tolerant (FT) pins | -5                 | +0                 | mA   |

| I <sub>INJ</sub> | NJ Injected current on any other pin           |                    | +5                 | IIIA |

*Note:* It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

#### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 20$  mA (with the non-standard V<sub>OL</sub>/V<sub>OH</sub> specifications given in *Table 43*.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 6.2*:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating I<sub>VDDΣ</sub> (see *Table 11*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating I<sub>VSSΣ</sub> (see *Table 11*).

#### **Output voltage levels**

Unless otherwise specified, the parameters given in *Table 43* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 13*. All I/Os are CMOS and TTL compliant.

| Symbol                            | Parameter                                | Conditions                       | Min                   | Max  | Unit |

|-----------------------------------|------------------------------------------|----------------------------------|-----------------------|------|------|

| V <sub>OL</sub> <sup>(1)(2)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = 8 mA           | -                     | 0.4  |      |

| V <sub>OH</sub> <sup>(3)(2)</sup> | Output high level voltage for an I/O pin | 2.7 V < V <sub>DD</sub> < 3.6 V  | 2.4                   | -    |      |

| V <sub>OL</sub> <sup>(1)(4)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = 4 mA           | -                     | 0.45 | v    |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin | 1.65 V < V <sub>DD</sub> < 2.7 V | V <sub>DD</sub> -0.45 | -    | v    |

| V <sub>OL</sub> <sup>(1)(4)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = 20 mA          | -                     | 1.3  |      |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin | 2.7 V < V <sub>DD</sub> < 3.6 V  | V <sub>DD</sub> -1.3  | -    |      |

#### Table 43. Output voltage characteristics

1. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 11* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. Tested in production.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in *Table 11* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

4. Guaranteed by characterization results.

| Symbol            | Parameter                                          | Conditions                                             | Min    | Тур                                            | Мах     | Unit               |

|-------------------|----------------------------------------------------|--------------------------------------------------------|--------|------------------------------------------------|---------|--------------------|

|                   |                                                    | Direct channels<br>2.4 V ≤V <sub>DDA</sub> ≤3.6 V      | 0.25   | -                                              | -       |                    |

|                   |                                                    | Multiplexed channels<br>2.4 V ≤V <sub>DDA</sub> ≤3.6 V | 0.56   | -                                              | -       |                    |

| t <sub>S</sub>    | Sampling time <sup>(5)</sup>                       | Direct channels<br>1.8 V ⊴V <sub>DDA</sub> ⊴2.4 V      | 0.56   | -                                              | -       | μs                 |

|                   |                                                    | Multiplexed channels<br>1.8 V ≤V <sub>DDA</sub> ≤2.4 V | 1      | -                                              |         |                    |

|                   |                                                    | -                                                      | 4      | -                                              | 384     | 1/f <sub>ADC</sub> |

|                   |                                                    | f <sub>ADC</sub> = 16 MHz                              | 1      | -                                              | 24.75   | μs                 |

| t <sub>CONV</sub> | Total conversion time<br>(including sampling time) | -                                                      | phase) | 34 (sampling<br>) +12 (successive<br>kimation) |         | 1/f <sub>ADC</sub> |

| 0                 | Internal sample and hold                           | Direct channels                                        | -      | 16                                             | -       | pF                 |

| C <sub>ADC</sub>  | capacitor                                          | Multiplexed channels                                   | -      | 10                                             | -       |                    |

| £                 | External trigger frequency                         | 12-bit conversions                                     | -      | -                                              | Tconv+1 | 1/f <sub>ADC</sub> |

| f <sub>TRIG</sub> | Regular sequencer                                  | 6/8/10-bit conversions                                 | -      | -                                              | Tconv   | 1/f <sub>ADC</sub> |

| f                 | External trigger frequency                         | 12-bit conversions                                     | -      | -                                              | Tconv+2 | 1/f <sub>ADC</sub> |

| f <sub>TRIG</sub> | Injected sequencer                                 | 6/8/10-bit conversions                                 | -      | -                                              | Tconv+1 | 1/f <sub>ADC</sub> |

| R <sub>AIN</sub>  | Signal source impedance <sup>(5)</sup>             | -                                                      | -      | -                                              | 50      | кΩ                 |

| 4                 | Injection trigger conversion                       | f <sub>ADC</sub> = 16 MHz                              | 219    | -                                              | 281     | ns                 |

| t <sub>lat</sub>  | latency                                            | -                                                      | 3.5    | -                                              | 4.5     | 1/f <sub>ADC</sub> |

| +                 | Regular trigger conversion                         | f <sub>ADC</sub> = 16 MHz                              | 156    | -                                              | 219     | ns                 |

| t <sub>latr</sub> | latency                                            | -                                                      | 2.5    | -                                              | 3.5     | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> | Power-up time                                      | -                                                      | -      | -                                              | 3.5     | μs                 |

Table 54. ADC characteristics (continued)

The V<sub>REF+</sub> input can be grounded iif neither the ADC nor the DAC are used (this allows to shut down an external voltage reference).

2. The current consumption through  $\mathsf{V}_{\mathsf{REF}}$  is composed of two parameters:

- one constant (max 300 µA)

- one variable (max 400  $\mu$ A), only during sampling time + 2 first conversion pulses.

So, peak consumption is 300+400 = 700  $\mu A$  and average consumption is 300 + [(4 sampling + 2) /16] x 400 = 450  $\mu A$  at 1Msps

3.  $V_{REF+}$  can be internally connected to  $V_{DDA}$  and  $V_{REF-}$  can be internally connected to  $V_{SSA}$ , depending on the package. Refer to Section 4: Pin descriptions for further details.

4. V<sub>SSA</sub> must be tied to ground.

5. See Table 56: Maximum source impedance RAIN max for  $\mathsf{R}_{\mathsf{AIN}}$  limitation.

# 6.3.18 DAC electrical specifications

Data guaranteed by design, unless otherwise specified.

| Symbol                              | Parameter                                             | С                                                                          | onditions                                | Min | Тур              | Мах                         | Unit |

|-------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------|-----|------------------|-----------------------------|------|

| V <sub>DDA</sub>                    | Analog supply voltage                                 | -                                                                          |                                          | 1.8 | -                | 3.6                         | V    |

| V <sub>REF+</sub>                   | Reference supply voltage                              | V <sub>REF+</sub> must always be below<br>V <sub>DDA</sub>                 |                                          | 1.8 | -                | 3.6                         | V    |

| V <sub>REF-</sub>                   | Lower reference voltage                               |                                                                            | -                                        | •   | V <sub>SSA</sub> |                             | V    |

| . (1)                               | Current consumption on                                | No load, mic                                                               | dle code (0x800)                         | -   | 130              | 220                         | μA   |

| I <sub>DDVREF+</sub> <sup>(1)</sup> | V <sub>REF+</sub> supply<br>V <sub>REF+</sub> = 3.3 V | No load, wo                                                                | rst code (0x000)                         | -   | 220              | 350                         | μA   |

| . (1)                               | Current consumption on                                | No load, mic                                                               | dle code (0x800)                         | -   | 210              | 320                         | μA   |

| I <sub>DDA</sub> <sup>(1)</sup>     | V <sub>DDA</sub> supply<br>V <sub>DDA</sub> = 3.3 V   | No load, wo                                                                | rst code (0xF1C)                         | -   | 320              | 520                         | μA   |

| RL                                  | Resistive load                                        | DAC output                                                                 | Connected to $V_{SSA}$                   | 5   | -                | -                           | kΩ   |

|                                     |                                                       | buffer ON                                                                  | Connected to $\mathrm{V}_{\mathrm{DDA}}$ | 25  | -                | -                           | N32  |

| CL                                  | Capacitive load                                       | DAC output                                                                 | buffer ON                                | -   | -                | 50                          | pF   |

| R <sub>O</sub>                      | Output impedance                                      | DAC output                                                                 | buffer OFF                               | 12  | 16               | 20                          | kΩ   |

| V <sub>DAC_OUT</sub>                | Voltage on DAC_OUT                                    | DAC output buffer ON                                                       |                                          | 0.2 | -                | V <sub>DDA</sub> – 0.2      | V    |

|                                     | output                                                | DAC output buffer OFF                                                      |                                          | 0.5 | -                | V <sub>REF+</sub> –<br>1LSB | mV   |

| DNL <sup>(1)</sup>                  | Differential non                                      | C <sub>L</sub> ≤ 50 pF, I<br>DAC output                                    | -                                        | -   | 1.5              | 3                           |      |

| DINE                                | linearity <sup>(2)</sup>                              | No $R_{LOAD}$ , $C_{L} \le 50 \text{ pF}$<br>DAC output buffer OFF         |                                          | -   | 1.5              | 3                           |      |

| INL <sup>(1)</sup>                  | Integral non linearity <sup>(3)</sup>                 | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON |                                          | -   | 2                | 4                           |      |

| IINE' '                             | integral non inteanty '                               | No $R_{LOAD}$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer OFF           |                                          | -   | 2                | 4                           | LSB  |

|                                     | Offset error at code                                  | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON |                                          | -   | ±10              | ±25                         |      |

| Offset <sup>(1)</sup>               | 0x800 <sup>(4)</sup>                                  | No R <sub>LOAD</sub> , C <sub>L</sub> ≤50 pF<br>DAC output buffer OFF      |                                          | -   | ±5               | ±8                          |      |

| Offset1 <sup>(1)</sup>              | Offset error at code<br>0x001 <sup>(5)</sup>          | No R <sub>LOAD</sub> , 0<br>DAC output                                     |                                          | -   | ±1.5             | ±5                          |      |

| Table | 57. | DAC | characteristics |

|-------|-----|-----|-----------------|

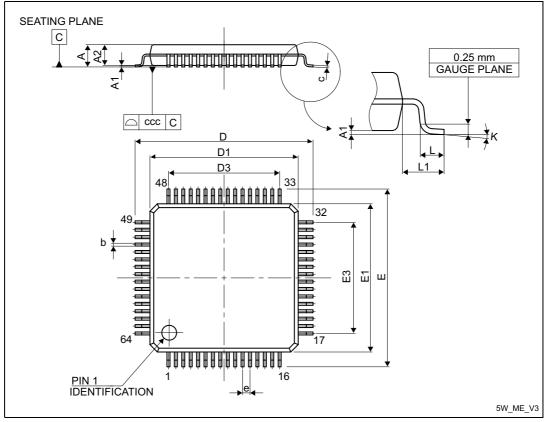

# 7.2 LQFP64 10 x 10 mm, 64-pin low-profile quad flat package information

Figure 35. LQFP64 10 x 10 mm, 64-pin low-profile quad flat package outline

1. Drawing is not to scale.

| Table 64. LQFP64 10 x 10 mm, 64-pin low-profile quad flat package mechanical |

|------------------------------------------------------------------------------|

| data                                                                         |

|             | uata  |             |       |        |                       |        |  |  |

|-------------|-------|-------------|-------|--------|-----------------------|--------|--|--|

| Currence al |       | millimeters |       |        | inches <sup>(1)</sup> |        |  |  |

| Symbol      | Min   | Тур         | Мах   | Тур    | Min                   | Max    |  |  |

| А           | -     | -           | 1.600 | -      | -                     | 0.0630 |  |  |

| A1          | 0.050 | -           | 0.150 | 0.0020 | -                     | 0.0059 |  |  |

| A2          | 1.350 | 1.400       | 1.450 | 0.0531 | 0.0551                | 0.0571 |  |  |

| b           | 0.170 | 0.220       | 0.270 | 0.0067 | 0.0087                | 0.0106 |  |  |

| С           | 0.090 | -           | 0.200 | 0.0035 | -                     | 0.0079 |  |  |

| D           | -     | 12.000      | -     | -      | 0.4724                | -      |  |  |

| D1          | -     | 10.000      | -     | -      | 0.3937                | -      |  |  |

| D3          | -     | 7.500       | -     | -      | 0.2953                | -      |  |  |

| Е           | -     | 12.000      | -     | -      | 0.4724                | -      |  |  |

| E1          | -     | 10.000      | -     | -      | 0.3937                | -      |  |  |

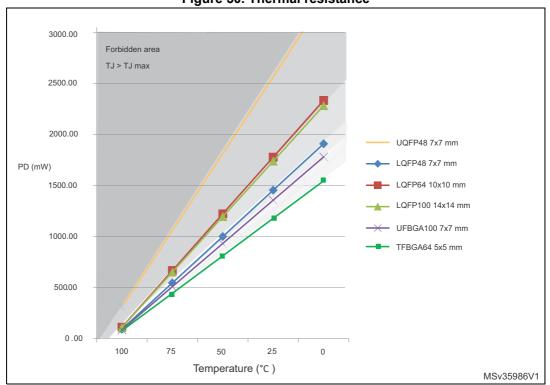

Figure 50. Thermal resistance

## 7.7.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.

| Date        | Revision | . Document revision history (continued)<br>Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date        | Revision | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 12-Nov-2013 | 9        | Changed voltage Range 1 minimum to 1.71 V and updated dynamic voltage scaling range in Table 3: Functionalities depending on the operating power supply range<br>Updated LCD and ADC features in Table 2: Ultralow power STM32L 15xx6/8/B device features and peripheral counts.<br>Updated Table 3: Functionalities depending on the operating power supply range.<br>Updated Table 5: Working mode-dependent functionalities (from <i>Run/active down to standby</i> ).<br>Updated Table 5: STM32L15xVx UFBGA100 ballout<br>Added Table 7: Legend/abbreviations used in the pinout table.<br>Updated Table 8: STM32L15xV6/BB pin definitions<br>Updated Table 8: STM32L15xX6/8/B pin definitions<br>Updated Table 8: STM32L15xX6/8/B pin definitions<br>Updated Table 8: STM32L15xx6/8/B pin definitions<br>Updated Table 10: Pin loading conditions and Figure 11: Pin input<br>voltage. Updated Figure 12: Power supply scheme.<br>Replaced "Σ" by "o" in Section 6.1.1 and Section 6.1.2.<br>Updated Table 10: Voltage characteristics.<br>Updated Table 13: General operating conditions.<br>Added Section 6.1.7: Optional LCD power supply scheme.<br>Updated Table 16: Embedded internal reference voltage.<br>Added this Note in Section 1: High-speed external clock generated<br>from a crystal/ceramic resonator<br>Updated Section : Functional susceptibility to I/O current injection.<br>This Section 6.3.5: Wakeup time from Low power mode was<br>previously a paragraph in Section 6.3.4: Supply current<br>characteristics.<br>Updated f <sub>HSE</sub> conditions in Table 17: Current consumption in Run<br>mode, code with data processing<br>running from RAM. Fixed IDD unit in Table 23: Typical and<br>maximum current consumptions in Standby mode.<br>This Figure 15: High-speed external clock source AC timing<br>diagram was moved up (was previously after Figure 16: Low-speed<br>external clock source AC timing diagram.<br>Updated Table 26: Low-power mode wakeup timings title.<br>Updated Table 27: Low-power mode wakeup timings title.<br>Updated Table 28: HSE oscillator characteristics and Table 29: LSE<br>oscillator characteristics (fLSE = 32.768 kHz).<br>Updated Table 29: ESD absolute maximum |