Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                        |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 32MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                   |

| Peripherals                | Cap Sense, DMA, I <sup>2</sup> S, POR, PWM, WDT                        |

| Number of I/O              | 51                                                                     |

| Program Memory Size        | 128KB (128K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 4K x 8                                                                 |

| RAM Size                   | 16K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                           |

| Data Converters            | A/D 20x12b; D/A 2x12b                                                  |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-TFBGA                                                               |

| Supplier Device Package    | 64-TFBGA (5x5)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l151rbh6d |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 48. | TFBGA64, 5 x 5 mm, 0.5 mm pitch, recommended footprint   | 121 |

|------------|----------------------------------------------------------|-----|

| Figure 49. | TFBGA64 5 x 5 mm, 0.5 mm pitch, package top view example | 122 |

| Figure 50. | Thermal resistance                                       | 124 |

## 2.2 Ultra-low-power device continuum

The ultra-low-power STM32L151x6/8/B and STM32L152x6/8/B devices are fully pin-to-pin and software compatible. Besides the full compatibility within the family, the devices are part of STMicroelectronics microcontrollers ultra-low-power strategy which also includes STM8L101xx and STM8L15xx devices. The STM8L and STM32L families allow a continuum of performance, peripherals, system architecture and features.

They are all based on STMicroelectronics ultra-low leakage process.

Note: The ultra-low-power STM32L and general-purpose STM32Fxxxx families are pin-to-pin compatible. The STM8L15xxx devices are pin-to-pin compatible with the STM8L101xx devices. Please refer to the STM32F and STM8L documentation for more information on these devices.

#### 2.2.1 Performance

All families incorporate highly energy-efficient cores with both Harvard architecture and pipelined execution: advanced STM8 core for STM8L families and ARM<sup>®</sup> Cortex<sup>®</sup>-M3 core for STM32L family. In addition specific care for the design architecture has been taken to optimize the mA/DMIPS and mA/MHz ratios.

This allows the ultra-low-power performance to range from 5 up to 33.3 DMIPs.

#### 2.2.2 Shared peripherals

STM8L15xxx and STM32L1xxxx share identical peripherals which ensure a very easy migration from one family to another:

- Analog peripherals: ADC, DAC and comparators

- Digital peripherals: RTC and some communication interfaces

#### 2.2.3 Common system strategy

To offer flexibility and optimize performance, the STM8L15xx and STM32L1xxxx families use a common architecture:

- Same power supply range from 1.65 V to 3.6 V, (1.65 V at power down only for STM8L15xx devices)

- Architecture optimized to reach ultra-low consumption both in low power modes and Run mode

- Fast startup strategy from low power modes

- Flexible system clock

- Ultrasafe reset: same reset strategy including power-on reset, power-down reset, brownout reset and programmable voltage detector.

#### 2.2.4 Features

ST ultra-low-power continuum also lies in feature compatibility:

- More than 10 packages with pin count from 20 to 144 pins and size down to 3 x 3 mm

- Memory density ranging from 4 to 384 Kbytes

HSE crystal oscillators are disabled. The voltage regulator is in the low power mode. The device can be woken up from Stop mode by any of the EXTI line, in 8  $\mu$ s. The EXTI line source can be one of the 16 external lines. It can be the PVD output, the Comparator 1 event or Comparator 2 event (if internal reference voltage is on). It can also be wakened by the USB wakeup.

Stop mode consumption: refer to *Table 22: Typical and maximum current consumptions in Stop mode*.

Standby mode with RTC

Standby mode is used to achieve the lowest power consumption and real time clock. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSI RC and HSE crystal oscillators are also switched off. The LSE or LSI is still running. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32K osc, RCC\_CSR).

The device exits Standby mode in 60 µs when an external reset (NRST pin), an IWDG reset, a rising edge on one of the three WKUP pins, RTC alarm (Alarm A or Alarm B), RTC tamper event, RTC timestamp event or RTC Wakeup event occurs.

Standby mode without RTC

Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI, RC, HSI and LSI RC, HSE and LSE crystal oscillators are also switched off. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32K osc, RCC\_CSR).

The device exits Standby mode in 60  $\mu$ s when an external reset (NRST pin) or a rising edge on one of the three WKUP pin occurs.

Standby mode consumption: refer to *Table 23*.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped by entering the Stop or Standby mode.

|                                                | Functionalitie                    | Functionalities depending on the operating power supply range |                                   |                            |  |  |  |  |  |

|------------------------------------------------|-----------------------------------|---------------------------------------------------------------|-----------------------------------|----------------------------|--|--|--|--|--|

| Operating power<br>supply range                | DAC and ADC operation             | USB                                                           | Dynamic voltage<br>scaling range  | I/O operation              |  |  |  |  |  |

| V <sub>DD</sub> = 1.65 to 1.71 V               | Not functional                    | Not functional                                                | Range 2 or<br>Range 3             | Degraded speed performance |  |  |  |  |  |

| V <sub>DD</sub> = 1.71 to 1.8 V <sup>(1)</sup> | Not functional                    | Not functional                                                | Range 1,<br>Range 2 or<br>Range 3 | Degraded speed performance |  |  |  |  |  |

| $V_{DD}$ = 1.8 to 2.0 V <sup>(1)</sup>         | Conversion time<br>up to 500 Ksps | Not functional                                                | Range 1,<br>Range 2 or<br>Range 3 | Degraded speed performance |  |  |  |  |  |

| Table 3. Functionalities dep | pending on the operating | power supply range |

|------------------------------|--------------------------|--------------------|

|------------------------------|--------------------------|--------------------|

Five BOR thresholds are available through option bytes, starting from 1.8 V to 3 V. To reduce the power consumption in Stop mode, it is possible to automatically switch off the internal reference voltage ( $V_{REFINT}$ ) in Stop mode. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for any external reset circuit.

Note: The start-up time at power-on is typically 3.3 ms when BOR is active at power-up, the startup time at power-on can be decreased down to 1 ms typically for devices with BOR inactive at power-up.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. This PVD offers 7 different levels between 1.85 V and 3.05 V, chosen by software, with a step around 200 mV. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

#### 3.3.3 Voltage regulator

The regulator has three operation modes: main (MR), low power (LPR) and power down.

- MR is used in Run mode (nominal regulation)

- LPR is used in the Low-power run, Low-power sleep and Stop modes

- Power down is used in Standby mode. The regulator output is high impedance, the kernel circuitry is powered down, inducing zero consumption but the contents of the registers and RAM are lost are lost except for the standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE crystal 32K osc, RCC\_CSR).

#### 3.3.4 Boot modes

At startup, boot pins are used to select one of three boot options:

- Boot from Flash memory

- Boot from System Memory

- Boot from embedded RAM

The boot loader is located in System Memory. It is used to reprogram the Flash memory by using USART1 or USART2. See STM32<sup>™</sup> microcontroller system memory boot mode AN2606 for details.

#### 3.4 Clock management

The clock controller distributes the clocks coming from different oscillators to the core and the peripherals. It also manages clock gating for low power modes and ensures clock robustness. It features:

- Clock prescaler: to get the best trade-off between speed and current consumption, the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler

- **Safe clock switching**: clock sources can be changed safely on the fly in run mode through a configuration register.

- **Clock management**: to reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

- **Master clock source**: three different clock sources can be used to drive the master clock:

- 1-24 MHz high-speed external crystal (HSE), that can supply a PLL

- 16 MHz high-speed internal RC oscillator (HSI), trimmable by software, that can supply a PLL

- Multispeed internal RC oscillator (MSI), trimmable by software, able to generate 7 frequencies (65.5 kHz, 131 kHz, 262 kHz, 524 kHz, 1.05 MHz, 2.1 MHz, 4.2 MHz) with a consumption proportional to speed, down to 750 nA typical. When a 32.768 kHz clock source is available in the system (LSE), the MSI frequency can be trimmed by software down to a ±0.5% accuracy.

- **Auxiliary clock source**: two ultra-low-power clock sources that can be used to drive the LCD controller and the real-time clock:

- 32.768 kHz low-speed external crystal (LSE)

- 37 kHz low-speed internal RC (LSI), also used to drive the independent watchdog. The LSI clock can be measured using the high-speed internal RC oscillator for greater precision.

- **RTC and LCD clock sources:** the LSI, LSE or HSE sources can be chosen to clock the RTC and the LCD, whatever the system clock.

- **USB clock source:** the embedded PLL has a dedicated 48 MHz clock output to supply the USB interface.

- **Startup clock:** after reset, the microcontroller restarts by default with an internal 2.1 MHz clock (MSI). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

- Clock security system (CSS): this feature can be enabled by software. If a HSE clock failure occurs, the master clock is automatically switched to HSI and a software interrupt is generated if enabled.

- Clock-out capability (MCO: microcontroller clock output): it outputs one of the internal clocks for external use by the application.

Several prescalers allow the configuration of the AHB frequency, the high-speed APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the AHB and the APB domains is 32 MHz. See *Figure 2* for details on the clock tree.

|         |        | Pins    |          |                    |                                  |                         |               |                                                  | Pins functions                  |                                            |

|---------|--------|---------|----------|--------------------|----------------------------------|-------------------------|---------------|--------------------------------------------------|---------------------------------|--------------------------------------------|

| LQFP100 | LQFP64 | TFBGA64 | UFBGA100 | LQFP48 or UFQFPN48 | Pin name                         | Pin type <sup>(1)</sup> | I/O structure | Main<br>function <sup>(2)</sup><br>(after reset) | Alternate functions             | Additional<br>functions                    |

| 1       | -      | -       | B2       | -                  | PE2                              | I/O                     | FT            | PE2                                              | TRACECLK/LCD_SEG38/<br>TIM3_ETR | -                                          |

| 2       | -      | -       | A1       | -                  | PE3                              | I/O                     | FT            | PE3                                              | TRACED0/LCD_SEG39/<br>TIM3_CH1  | -                                          |

| 3       | -      | -       | B1       | -                  | PE4                              | I/O                     | FT            | PE4                                              | TRACED1/TIM3_CH2                | -                                          |

| 4       | -      | -       | C2       | -                  | PE5                              | I/O                     | FT            | PE5                                              | TRACED2/TIM9_CH1                | -                                          |

| 5       | -      | -       | D2       | -                  | PE6-WKUP3                        | I/O                     | FT            | PE6                                              | TRACED3/TIM9_CH2                | WKUP3                                      |

| 6       | 1      | B2      | E2       | 1                  | V <sub>LCD</sub> <sup>(3)</sup>  | S                       |               | V <sub>LCD</sub>                                 | -                               | -                                          |

| 7       | 2      | A2      | C1       | 2                  | PC13-<br>WKUP2                   | I/O                     | FT            | PC13                                             | -                               | RTC_TAMP1/<br>RTC_TS/<br>RTC_OUT/<br>WKUP2 |

| 8       | 3      | A1      | D1       | 3                  | PC14-<br>OSC32_IN <sup>(4)</sup> | I/O                     | тс            | PC14                                             | -                               | OSC32_IN                                   |

| 9       | 4      | B1      | E1       | 4                  | PC15-<br>OSC32_OUT<br>(4)        | I/O                     | тс            | PC15                                             | -                               | OSC32_OUT                                  |

| 10      | -      | -       | F2       | -                  | V <sub>SS_5</sub>                | S                       | -             | V <sub>SS_5</sub>                                | -                               | -                                          |

| 11      | -      | -       | G2       | -                  | V <sub>DD_5</sub>                | S                       | -             | V <sub>DD_5</sub>                                | -                               | -                                          |

| 12      | 5      | C1      | F1       | 5                  | PH0-<br>OSC_IN <sup>(5)</sup>    | I/O                     | тс            | PH0                                              | -                               | OSC_IN                                     |

| 13      | 6      | D1      | G1       | 6                  | PH1-<br>OSC_OUT                  | I/O                     | тс            | PH1                                              | -                               | OSC_OUT                                    |

| 14      | 7      | E1      | H2       | 7                  | NRST                             | I/O                     | RST           | NRST                                             | -                               | -                                          |

| 15      | 8      | E3      | H1       | -                  | PC0                              | I/O                     | FT            | PC0                                              | LCD_SEG18                       | ADC_IN10/<br>/COMP1_INP                    |

| 16      | 9      | E2      | J2       | -                  | PC1                              | I/O                     | FT            | PC1                                              | LCD_SEG19                       | ADC_IN11/<br>COMP1_INP                     |

| 17      | 10     | F2      | JЗ       | -                  | PC2                              | I/O                     | FT            | PC2                                              | LCD_SEG20                       | ADC_IN12/<br>COMP1_INP                     |

| 18      | 11     | _(6)    | K2       | -                  | PC3                              | I/O                     | тс            | PC3                                              | LCD_SEG21                       | ADC_IN13/<br>COMP1_INP                     |

|         |        | Pin     | S        |                    |                   |                         |               |                                                  | Pins functions                                           | inicaj                             |

|---------|--------|---------|----------|--------------------|-------------------|-------------------------|---------------|--------------------------------------------------|----------------------------------------------------------|------------------------------------|

| LQFP100 | LQFP64 | TFBGA64 | UFBGA100 | LQFP48 or UFQFPN48 | Pin name          | Pin type <sup>(1)</sup> | I/O structure | Main<br>function <sup>(2)</sup><br>(after reset) | Alternate functions                                      | Additional<br>functions            |

| 35      | 26     | F5      | M5       | 18                 | PB0               | I/O                     | TC            | PB0                                              | TIM3_CH3/LCD_SEG5                                        | ADC_IN8/<br>COMP1_INP/<br>VREF_OUT |

| 36      | 27     | G5      | M6       | 19                 | PB1               | I/O                     | FT            | PB1                                              | TIM3_CH4/LCD_SEG6                                        | ADC_IN9/<br>COMP1_INP/<br>VREF_OUT |

| 37      | 28     | G6      | L6       | 20                 | PB2               | I/O                     | FT            | PB2/BOOT1                                        | BOOT1                                                    | -                                  |

| 38      | -      | -       | M7       | -                  | PE7               | I/O                     | тс            | PE7                                              | -                                                        | ADC_IN22/<br>COMP1_INP             |

| 39      | -      | -       | L7       | -                  | PE8               | I/O                     | тс            | PE8                                              | -                                                        | ADC_IN23/<br>COMP1_INP             |

| 40      | -      | -       | M8       | -                  | PE9               | I/O                     | тс            | PE9                                              | TIM2_CH1_ETR                                             | ADC_IN24/<br>COMP1_INP             |

| 41      | -      | -       | L8       | -                  | PE10              | I/O                     | тс            | PE10                                             | TIM2_CH2                                                 | ADC_IN25/<br>COMP1_INP             |

| 42      | -      | -       | M9       | -                  | PE11              | I/O                     | FT            | PE11                                             | TIM2_CH3                                                 | -                                  |

| 43      | -      | -       | L9       | -                  | PE12              | I/O                     | FT            | PE12                                             | TIM2_CH4/SPI1_NSS                                        | -                                  |

| 44      | -      | -       | M10      | -                  | PE13              | I/O                     | FT            | PE13                                             | SPI1_SCK                                                 | -                                  |

| 45      | -      | -       | M11      | -                  | PE14              | I/O                     | FT            | PE14                                             | SPI1_MISO                                                | -                                  |

| 46      | -      | -       | M12      | -                  | PE15              | I/O                     | FT            | PE15                                             | SPI1_MOSI                                                | -                                  |

| 47      | 29     | G7      | L10      | 21                 | PB10              | I/O                     | FT            | PB10                                             | I2C2_SCL/USART3_TX/<br>TIM2_CH3/LCD_SEG10                | -                                  |

| 48      | 30     | H7      | L11      | 22                 | PB11              | I/O                     | FT            | PB11                                             | I2C2_SDA/USART3_RX/<br>TIM2_CH4/LCD_SEG11                | -                                  |

| 49      | 31     | D6      | F12      | 23                 | V <sub>SS_1</sub> | S                       | -             | V <sub>SS_1</sub>                                | -                                                        | -                                  |

| 50      | 32     | E6      | G12      | 24                 | V <sub>DD_1</sub> | S                       | -             | V <sub>DD_1</sub>                                | -                                                        | -                                  |

| 51      | 33     | H8      | L12      | 25                 | PB12              | I/O                     | FT            | PB12                                             | SPI2_NSS/I2C2_SMBA/<br>USART3_CK/<br>LCD_SEG12/TIM10_CH1 | ADC_IN18/<br>COMP1_INP             |

| 52      | 34     | G8      | K12      | 26                 | PB13              | I/O                     | FT            | PB13                                             | SPI2_SCK/USART3_CTS/<br>LCD_SEG13/<br>TIM9_CH1           | ADC_IN19/<br>COMP1_INP             |

# Table 8. STM32L151x6/8/B and STM32L152x6/8/B pin definitions (continued)

46/133

DocID17659 Rev 12

5

|                |             |                    |          |            |        | Digital alt | ternate fu | nction number |       |       |        |        |        |          |          |

|----------------|-------------|--------------------|----------|------------|--------|-------------|------------|---------------|-------|-------|--------|--------|--------|----------|----------|

| <b>B</b> . 4   | AFIO0       | AFIO1              | AFIO2    | AFIO3      | AFIO4  | AFIO5       | AFOI6      | AFIO7         | AFIO8 | AFIO9 | AFIO11 | AFIO12 | AFIO13 | AFIO14   | AFIO15   |

| Port name      |             | Alternate function |          |            |        |             |            |               |       |       |        |        |        |          |          |

|                | SYSTEM      | TIM2               | TIM3/4   | TIM9/10/11 | I2C1/2 | SPI1/2      | N/A        | USART1/2/3    | N/A   | N/A   | LCD    | N/A    | N/A    | RI       | SYSTEM   |

| PD13           | -           | -                  | TIM4_CH2 | -          | -      | -           | -          | -             | -     | -     | -      | -      | -      | TIMx_IC2 | EVENTOUT |

| PD14           | -           | -                  | TIM4_CH3 | -          | -      | -           | -          | -             | -     | -     | -      | -      | -      | TIMx_IC3 | EVENTOUT |

| PD15           | -           | -                  | TIM4_CH4 | -          | -      | -           | -          | -             | -     | -     | -      | -      | -      | TIMx_IC4 | EVENTOUT |

| PE0            | -           | -                  | TIM4_ETR | TIM10_CH1  | -      | -           | -          | -             | -     | -     | -      | -      | -      | TIMx_IC1 | EVENTOUT |

| PE1            | -           | -                  |          | TIM11_CH1  | -      | -           | -          | -             | -     | -     | -      | -      | -      | TIMx_IC2 | EVENTOUT |

| PE2            | TRACEC<br>K | -                  | TIM3_ETR | -          | -      | -           | -          | -             | -     | -     | -      | -      | -      | TIMx_IC3 | EVENTOUT |

| PE3            | TRACED<br>0 | -                  | TIM3_CH1 | -          | -      | -           | -          | -             | -     | -     | -      | -      | -      | TIMx_IC4 | EVENTOUT |

| PE4            | TRACED<br>1 | -                  | TIM3_CH2 | -          | -      | -           | -          | -             | -     | -     | -      | -      | -      | TIMx_IC1 | EVENTOUT |

| PE5            | TRACED<br>2 | -                  | -        | TIM9_CH1*  | -      | -           | -          | -             | -     | -     | -      | -      | -      | TIMx_IC2 | EVENTOUT |

| PE6            | TRACED<br>3 | -                  | -        | TIM9_CH2*  | -      | -           | -          | -             | -     | -     | -      | -      | -      | TIMx_IC3 | EVENTOUT |

| PE7            | -           | -                  | -        | -          | -      | -           | -          | -             | -     | -     | -      | -      | -      | TIMx_IC4 | EVENTOUT |

| PE8            | -           | -                  | -        | -          | -      | -           | -          | -             | -     | -     | -      | -      | -      | TIMx_IC1 | EVENTOUT |

| PE9            | -           | TIM2_CH1_ETR       | -        | -          | -      | -           | -          | -             | -     | -     | -      | -      | -      | TIMx_IC2 | EVENTOUT |

| PE10           | -           | TIM2_CH2           | -        | -          | -      | -           | -          | -             | -     | -     | -      | -      | -      | TIMx_IC3 | EVENTOUT |

| PE11           | -           | TIM2_CH3           | -        | -          | -      | -           | -          | -             | -     | -     | -      | -      | -      | TIMx_IC4 | EVENTOUT |

| PE12           | -           | TIM2_CH4           | -        | -          | -      | SPI1_NSS    | -          | -             | -     | -     | -      | -      | -      | TIMx_IC1 | EVENTOUT |

| PE13           | -           | -                  | -        | -          | -      | SPI1_SCK    | -          | -             | -     | -     | -      | -      | -      | TIMx_IC2 | EVENTOUT |

| PE14           | -           | -                  | -        | -          | -      | SPI1_MISO   | -          | -             | -     | -     | -      | -      | -      | TIMx_IC3 | EVENTOUT |

| PE15           | -           | -                  | -        | -          | -      | SPI1_MOSI   | -          | -             | -     | -     | -      | -      | -      | TIMx_IC4 | EVENTOUT |

| PH0-<br>OSC_IN | -           | -                  | -        | -          | -      | -           | -          | -             | -     | -     | -      | -      | -      | -        | -        |

#### Table 9. Alternate function input/output (continued)

# 6 Electrical characteristics

### 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

#### 6.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\sigma$ ).

Please refer to device ErrataSheet for possible latest changes of electrical characteristics.

#### 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 3.6$  V (for the 1.65 V  $\leq V_{DD} \leq 3.6$  V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\sigma$ ).

#### 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

#### 6.1.4 Loading capacitor

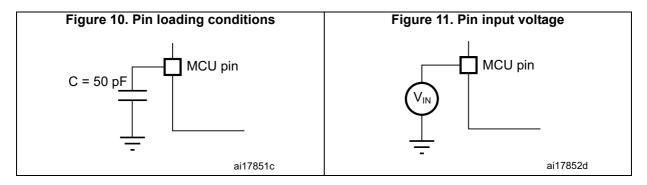

The loading conditions used for pin parameter measurement are shown in Figure 10.

#### 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 11*.

|      |                    | Typica                                                |                                                       | V <sub>DD</sub> = 3.0 V, T <sub>A</sub>               | = 25 °C                 |                                |

|------|--------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------|--------------------------------|

| I    | Peripheral         | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | Range 3,<br>V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | Low power sleep and run | Unit                           |

|      | TIM2               | 13                                                    | 10.5                                                  | 8                                                     | 10.5                    |                                |

|      | TIM3               | 14                                                    | 12                                                    | 9                                                     | 12                      |                                |

|      | TIM4               | 12.5                                                  | 10.5                                                  | 8                                                     | 11                      |                                |

|      | TIM6               | 5.5                                                   | 4.5                                                   | 3.5                                                   | 4.5                     |                                |

|      | TIM7               | 5.5                                                   | 5                                                     | 3.5                                                   | 4.5                     |                                |

|      | LCD                | 5.5                                                   | 5                                                     | 3.5                                                   | 5                       |                                |

|      | WWDG               | 4                                                     | 3.5                                                   | 2.5                                                   | 3.5                     |                                |

|      | SPI2               | 5.5                                                   | 5                                                     | 4                                                     | 5                       | µA/MHz                         |

| APB1 | USART2             | 9                                                     | 8                                                     | 5.5                                                   | 8.5                     | (f <sub>HCLK</sub> )           |

|      | USART3             | 10.5                                                  | 9                                                     | 6                                                     | 8                       |                                |

|      | I2C1               | 8.5                                                   | 7                                                     | 5.5                                                   | 7.5                     |                                |

|      | 12C2               | 8.5                                                   | 7                                                     | 5.5                                                   | 6.5                     |                                |

|      | USB                | 12.5                                                  | 10                                                    | 6.5                                                   | 10                      |                                |

|      | PWR                | 4.5                                                   | 4                                                     | 3                                                     | 3.5                     |                                |

|      | DAC                | 9                                                     | 7.5                                                   | 6                                                     | 7                       |                                |

|      | COMP               | 4.5                                                   | 4                                                     | 3.5                                                   | 4.5                     |                                |

|      | SYSCFG & RI        | 3                                                     | 2.5                                                   | 2                                                     | 2.5                     |                                |

|      | TIM9               | 9                                                     | 7.5                                                   | 6                                                     | 7                       |                                |

|      | TIM10              | 6.5                                                   | 5.5                                                   | 4.5                                                   | 5.5                     |                                |

| APB2 | TIM11              | 7                                                     | 6                                                     | 4.5                                                   | 5.5                     | µA/MHz<br>(f <sub>HCLK</sub> ) |

|      | ADC <sup>(2)</sup> | 11.5                                                  | 9.5                                                   | 8                                                     | 9                       | VIIULK/                        |

|      | SPI1               | 5                                                     | 4.5                                                   | 3                                                     | 4                       |                                |

|      | USART1             | 9                                                     | 7.5                                                   | 6                                                     | 7.5                     |                                |

Table 24. Peripheral current consumption<sup>(1)</sup>

#### 6.3.5 Wakeup time from Low power mode

The wakeup times given in the following table are measured with the MSI RC oscillator. The clock source used to wake up the device depends on the current operating mode:

- Sleep mode: the clock source is the clock that was set before entering Sleep mode

- Stop mode: the clock source is the MSI oscillator in the range configured before entering Stop mode

- Standby mode: the clock source is the MSI oscillator running at 2.1 MHz

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 13*.

| Symbol               | Parameter                                    | Conditions                                                              | Тур  | Max <sup>(1)</sup>                                                                                                 | Unit |

|----------------------|----------------------------------------------|-------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------|------|

| t <sub>WUSLEEP</sub> | Wakeup from Sleep mode                       | f <sub>HCLK</sub> = 32 MHz                                              | 0.36 | -                                                                                                                  |      |

| t                    | Wakeup from Low power sleep mode             | f <sub>HCLK</sub> = 262 kHz<br>Flash enabled                            | 32   | -                                                                                                                  |      |

| twusleep_lp          | f <sub>HCLK</sub> = 262 kHz                  | f <sub>HCLK</sub> = 262 kHz<br>Flash switched OFF                       | 34   |                                                                                                                    |      |

|                      | Wakeup from Stop mode, regulator in Run mode | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz                          | 8.2  | -                                                                                                                  |      |

|                      |                                              | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage Range 1 and 2 | 8.2  | 9.3                                                                                                                |      |

|                      |                                              | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage Range 3       | 7.8  | 11.2                                                                                                               | μs   |

| t <sub>WUSTOP</sub>  | Wakeup from Stop mode,                       | f <sub>HCLK</sub> = f <sub>MSI</sub> = 2.1 MHz                          | 10   | 8.2     9.3       7.8     11.2       10     12       15.5     20       29     35       53     63       105     118 |      |

|                      | regulator in low power mode                  | f <sub>HCLK</sub> = f <sub>MSI</sub> = 1.05 MHz                         | 15.5 | 20                                                                                                                 |      |

|                      |                                              | f <sub>HCLK</sub> = f <sub>MSI</sub> = 524 kHz                          | 29   | 35                                                                                                                 |      |

|                      |                                              | f <sub>HCLK</sub> = f <sub>MSI</sub> = 262 kHz                          | 53   | 63                                                                                                                 |      |

|                      |                                              | f <sub>HCLK</sub> = f <sub>MSI</sub> = 131 kHz                          | 105  | 118                                                                                                                |      |

|                      |                                              | f <sub>HCLK</sub> = MSI = 65 kHz                                        | 210  | 237                                                                                                                |      |

| t                    | Wakeup from Standby<br>mode<br>FWU bit = 1   | f <sub>HCLK</sub> = MSI = 2.1 MHz                                       | 50   | 103                                                                                                                |      |

| <sup>t</sup> wustdby | Wakeup from Standby<br>mode<br>FWU bit = 0   | f <sub>HCLK</sub> = MSI = 2.1 MHz                                       | 2.5  | 3.2                                                                                                                | ms   |

Table 25. Low-power mode wakeup timings

1. Guaranteed by characterization results, unless otherwise specified

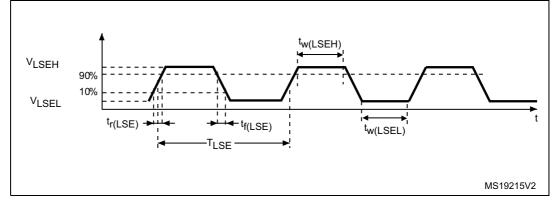

#### Low-speed external user clock generated from an external source

The characteristics given in the following table result from tests performed using a lowspeed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 13*.

| Symbol                                       | Parameter                               | Conditions                       | Min                | Тур    | Max                | Unit |

|----------------------------------------------|-----------------------------------------|----------------------------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                         | User external clock source<br>frequency |                                  | 1                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                            | OSC32_IN input pin high level voltage   |                                  | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | v    |

| V <sub>LSEL</sub>                            | OSC32_IN input pin low level voltage    | -                                | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> | v    |

| t <sub>w(LSEH)</sub><br>t <sub>w(LSEL)</sub> | OSC32_IN high or low time               |                                  | 465                | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub>   | OSC32_IN rise or fall time              |                                  | -                  | -      | 10                 | 115  |

| C <sub>IN(LSE)</sub>                         | OSC32_IN input capacitance              | -                                | -                  | 0.6    | -                  | pF   |

| DuCy <sub>(LSE)</sub>                        | Duty cycle                              | -                                | 45                 | -      | 55                 | %    |

| ١L                                           | OSC32_IN Input leakage current          | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | -      | ±1                 | μA   |

Table 27. Low-speed external user clock characteristics<sup>(1)</sup>

1. Guaranteed by design.

#### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 1 to 24 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 28*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

#### 6.3.7 Internal clock source characteristics

The parameters given in the following table are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 13*.

#### High-speed internal (HSI) RC oscillator

| Symbol                              | Parameter                               | Conditions                                                           | Min               | Тур  | Max                                                    | Unit |

|-------------------------------------|-----------------------------------------|----------------------------------------------------------------------|-------------------|------|--------------------------------------------------------|------|

| f <sub>HSI</sub>                    | Frequency                               | V <sub>DD</sub> = 3.0 V                                              | -                 | 16   | -                                                      | MHz  |

| TRIM <sup>(1)(2)</sup>              | HSI user-trimmed                        | Trimming code is not a multiple of 16                                | -                 | ±0.4 | 0.7                                                    | %    |

| TRIM                                | resolution                              | Trimming code is a multiple of 16                                    | -                 | -    | ±1.5                                                   | %    |

|                                     |                                         | V <sub>DDA</sub> = 3.0 V, T <sub>A</sub> = 25 °C                     | -1 <sup>(3)</sup> | -    | 1 <sup>(3)</sup>                                       | %    |

|                                     | $V_{DDA}$ = 3.0 V, $T_{A}$ = 0 to 55 °C |                                                                      |                   | -    | 1.5                                                    | %    |

|                                     | Accuracy of the                         | $V_{DDA}$ = 3.0 V, $T_A$ = -10 to 70 °C                              | -2                | -    | 2                                                      | %    |

| ACC <sub>HSI</sub> <sup>(2)</sup>   | factory-calibrated                      | $V_{DDA}$ = 3.0 V, $T_A$ = -10 to 85 °C                              | -2.5              | -    | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | %    |

|                                     | HSI oscillator                          | $V_{DDA}$ = 3.0 V, $T_A$ = -10 to 105 °C                             | -4                | -    |                                                        | %    |

|                                     |                                         | V <sub>DDA</sub> = 1.65 V to 3.6 V<br>T <sub>A</sub> = -40 to 105 °C | -4                | -    | 3                                                      | %    |

| t <sub>SU(HSI)</sub> <sup>(2)</sup> | HSI oscillator<br>startup time          | -                                                                    | -                 | 3.7  | 6                                                      | μs   |

| I <sub>DD(HSI)</sub> <sup>(2)</sup> | HSI oscillator<br>power consumption     | -                                                                    | -                 | 100  | 140                                                    | μA   |

1. The trimming step differs depending on the trimming code. It is usually negative on the codes which are multiples of 16 (0x00, 0x10, 0x20, 0x30...0xE0).

2. Guaranteed by characterization results.

3. Tested in production.

#### Low-speed internal (LSI) RC oscillator

| Table 31. | LSI | oscillator | characteristics |

|-----------|-----|------------|-----------------|

|-----------|-----|------------|-----------------|

| Symbol                              | Parameter                                                   | Min | Тур | Max | Unit |

|-------------------------------------|-------------------------------------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub> <sup>(1)</sup>     | LSI frequency                                               | 26  | 38  | 56  | kHz  |

| D <sub>LSI</sub> <sup>(2)</sup>     | LSI oscillator frequency drift<br>0°C ≤T <sub>A</sub> ≤85°C | -10 | -   | 4   | %    |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time                                 | -   | -   | 200 | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption                            | -   | 400 | 510 | nA   |

1. Tested in production.

2. This is a deviation for an individual part, once the initial frequency has been measured.

3. Guaranteed by design.

#### 6.3.9 Memory characteristics

The characteristics are given at  $T_{\text{A}}$  = -40 to 105  $^{\circ}\text{C}$  unless otherwise specified.

#### **RAM** memory

| Table | 34.   | RAM | and | hardware   | reaisters |

|-------|-------|-----|-----|------------|-----------|

|       | • • • |     |     | indiana io |           |

| Symbol | Parameter                          | Conditions           | Min  | Тур | Max | Unit |

|--------|------------------------------------|----------------------|------|-----|-----|------|

| VRM    | Data retention mode <sup>(1)</sup> | STOP mode (or RESET) | 1.65 | -   | -   | V    |

1. Minimum supply voltage without losing data stored in RAM (in Stop mode or under Reset) or in hardware registers (only in Stop mode).

#### Flash memory and data EEPROM

| Symbol          | Parameter                                             | Conditions                                      | Min  | Тур  | Max <sup>(1)</sup> | Unit |  |

|-----------------|-------------------------------------------------------|-------------------------------------------------|------|------|--------------------|------|--|

| V <sub>DD</sub> | Operating voltage<br>Read / Write / Erase             | -                                               | 1.65 | -    | 3.6                | V    |  |

|                 | Programming / erasing time for                        | Erasing                                         | -    | 3.28 | 3.94               |      |  |

| prog            | byte / word / double word / half-<br>page             | Programming                                     | -    | 3.28 | 3.94               | ms   |  |

| 1               | Average current during whole program/erase operation  | T - 25 °C V - 3 6 V                             | -    | 300  | -                  | μA   |  |

| I <sub>DD</sub> | Maximum current (peak) during program/erase operation | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 3.6 V | -    | 1.5  | 2.5                | mA   |  |

#### Table 35. Flash memory and data EEPROM characteristics

1. Guaranteed by design.

#### Table 36. Flash memory, data EEPROM endurance and data retention

| Symbol                          | Parameter                                                                           | Conditions     | Value              |     |     | Unit    |

|---------------------------------|-------------------------------------------------------------------------------------|----------------|--------------------|-----|-----|---------|

| Symbol                          | Falameter                                                                           | Conditions     | Min <sup>(1)</sup> | Тур | Max | Unit    |

| NCYC <sup>(2)</sup>             | Cycling (erase / write) $T_A = -40^{\circ}C$ toProgram memoryT_A = -40^{\circ}C to  |                | 10                 | -   | -   | kovolos |

| NOTO: 7                         | Cycling (erase / write)<br>EEPROM data memory                                       | 105 °C         | 300                | -   | -   | kcycles |

|                                 | Data retention (program memory) after<br>10 kcycles at T <sub>A</sub> = 85 °C       | TRET = +85 °C  | 30                 | -   | -   |         |

| t <sub>RET</sub> <sup>(2)</sup> | Data retention (EEPROM data memory) after 300 kcycles at $T_A$ = 85 °C              | INET = '03' C  | 30                 | -   | -   | voars   |

| 'RET`                           | Data retention (program memory) after<br>10 kcycles at T <sub>A</sub> = 105 °C      | TRET = +105 °C | 10                 | I   | -   | years   |

|                                 | Data retention (EEPROM data memory)<br>after 300 kcycles at T <sub>A</sub> = 105 °C | 11121 - 103 C  | 10                 | -   | -   |         |

1. Guaranteed by characterization results.

2. Characterization is done according to JEDEC JESD22-A117.

| Symbol              | Parameter                                     | Conditions                                                                                                                                | Min | Тур | Max <sup>(1)</sup> | Unit       |  |

|---------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--------------------|------------|--|

| V <sub>DDA</sub>    | Analog supply voltage                         | -                                                                                                                                         | 1.  | -   | 3.6                | V          |  |

| V <sub>IN</sub>     | Comparator 2 input voltage range              | -                                                                                                                                         | 0   | -   | V <sub>DDA</sub>   | V          |  |

| t                   | Comparator startup time                       | Fast mode                                                                                                                                 | -   | 15  | 20                 |            |  |

| t <sub>start</sub>  |                                               | Slow mode                                                                                                                                 | -   | 20  | 25                 |            |  |

| +                   | Propagation delay <sup>(2)</sup> in slow mode | 1. V ≤V <sub>DDA</sub> ≤2.7 V                                                                                                             | -   | 1.8 | 3.5                |            |  |

| t <sub>d slow</sub> | Fropagation delay fin slow mode               | 2.7 V ≤V <sub>DDA</sub> ≤3.6 V                                                                                                            | -   | 2.5 | 6                  | μs         |  |

|                     | Propagation delay <sup>(2)</sup> in fast mode | 1. V ⊴V <sub>DDA</sub> ⊴2.7 V                                                                                                             | -   | 0.8 | 2                  |            |  |

| t <sub>d fast</sub> | Fropagation delay 7 in last mode              | 2.7 V ≤V <sub>DDA</sub> ≤3.6 V                                                                                                            | -   | 1.2 | 4                  |            |  |

| V <sub>offset</sub> | Comparator offset error                       | -                                                                                                                                         | -   | ±4  | ±20                | mV         |  |

| dThreshold/<br>dt   | Threshold voltage temperature coefficient     | $V_{DDA} = 3.3V$<br>$T_{A} = 0 \text{ to } 50 \circ C$<br>$V = V_{REFINT},$<br>$3/4 V_{REFINT},$<br>$1/2 V_{REFINT},$<br>$1/4 V_{REFINT}$ | -   | 15  | 100                | ppm<br>/°C |  |

|                     | Current consumption <sup>(3)</sup>            | Fast mode                                                                                                                                 | -   | 3.5 | 5                  |            |  |

| I <sub>COMP2</sub>  |                                               | Slow mode                                                                                                                                 | -   | 0.5 | 2                  | μA         |  |

| Table 61. | Comparator | 2 characteristics |

|-----------|------------|-------------------|

|-----------|------------|-------------------|

1. Guaranteed by characterization results.

2. The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

3. Comparator consumption only. Internal reference voltage (necessary for comparator operation) is not included.

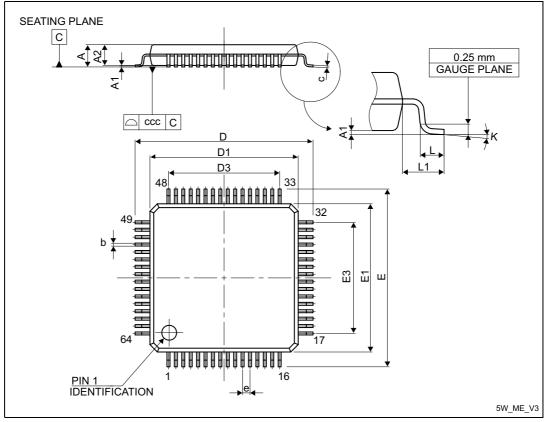

# 7.2 LQFP64 10 x 10 mm, 64-pin low-profile quad flat package information

Figure 35. LQFP64 10 x 10 mm, 64-pin low-profile quad flat package outline

1. Drawing is not to scale.

| Table 64. LQFP64 10 x 10 mm, 64-pin low-profile quad flat package mechanical |

|------------------------------------------------------------------------------|

| data                                                                         |

|        | Gata        |        |       |                       |        |        |  |  |  |

|--------|-------------|--------|-------|-----------------------|--------|--------|--|--|--|

| Symbol | millimeters |        |       | inches <sup>(1)</sup> |        |        |  |  |  |

|        | Min         | Тур    | Мах   | Тур                   | Min    | Max    |  |  |  |

| А      | -           | -      | 1.600 | -                     | -      | 0.0630 |  |  |  |

| A1     | 0.050       | -      | 0.150 | 0.0020                | -      | 0.0059 |  |  |  |

| A2     | 1.350       | 1.400  | 1.450 | 0.0531                | 0.0551 | 0.0571 |  |  |  |

| b      | 0.170       | 0.220  | 0.270 | 0.0067                | 0.0087 | 0.0106 |  |  |  |

| С      | 0.090       | -      | 0.200 | 0.0035                | -      | 0.0079 |  |  |  |

| D      | -           | 12.000 | -     | -                     | 0.4724 | -      |  |  |  |

| D1     | -           | 10.000 | -     | -                     | 0.3937 | -      |  |  |  |

| D3     | -           | 7.500  | -     | -                     | 0.2953 | -      |  |  |  |

| Е      | -           | 12.000 | -     | -                     | 0.4724 | -      |  |  |  |

| E1     | -           | 10.000 | -     | -                     | 0.3937 | -      |  |  |  |

| Symphol | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|---------|-------------|-------|-------|-----------------------|--------|--------|--|

| Symbol  | Min         | Тур   | Max   | Min                   | Тур    | Мах    |  |

| А       | -           | -     | 1.600 | -                     | -      | 0.0630 |  |

| A1      | 0.050       | -     | 0.150 | 0.0020                | -      | 0.0059 |  |

| A2      | 1.350       | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |  |

| b       | 0.170       | 0.220 | 0.270 | 0.0067                | 0.0087 | 0.0106 |  |

| С       | 0.090       | -     | 0.200 | 0.0035                | -      | 0.0079 |  |

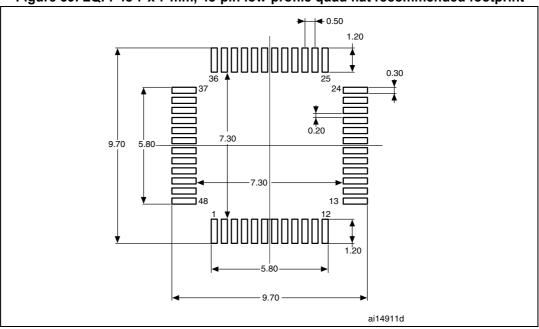

| D       | 8.800       | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |  |

| D1      | 6.800       | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |  |

| D3      | -           | 5.500 | -     | -                     | 0.2165 | -      |  |

| E       | 8.800       | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |  |

| E1      | 6.800       | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |  |

| E3      | -           | 5.500 | -     | -                     | 0.2165 | -      |  |

| е       | -           | 0.500 | -     | -                     | 0.0197 | -      |  |

| L       | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |  |

| L1      | -           | 1.000 | -     | -                     | 0.0394 | -      |  |

| k       | 0°          | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |  |

| CCC     | -           | -     | 0.080 | -                     | -      | 0.0031 |  |

Table 65. LQFP48 7 x 7 mm, 48-pin low-profile quad flat package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are in millimeters.

# 9 Revision history

| Table 73. Document revision history |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|-------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Date                                | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 02-Jul-2010                         | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 01-Oct-2010                         | 2        | Removed 5 V tolerance (FT) from PA3, PB0 and PC3 in <i>Table 8:</i><br><i>STM32L15xx6/8/B pin definitions</i><br>Updated <i>Table 14: Embedded reset and power control block</i><br><i>characteristics</i><br>Updated <i>Table 16: Embedded internal reference voltage</i><br>Added <i>Table 53: ADC clock frequency</i><br>Updated <i>Table 54: ADC characteristics</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 16-Dec-2010                         | 3        | Modified consumptions on page 1 and in Section 3.1: Low power<br>modes<br>LED_SEG8 removed on PB6.<br>Updated Section 6: Electrical characteristics<br>VFQFPN48 replaced by UFQFPN48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 25-Feb-2011                         | 4        | Section 3.3.2: Power supply supervisor: updated note.<br>Table 8: STM32L15xx6/8/B pin definitions: modified main function<br>(after reset) and alternate function for OSC_IN and OSC_OUT pins;<br>modified footnote 5; added footnote to OSC32_IN and OSC32_OUT<br>pins; C1 and D1 removed on PD0 and PD1 pins (TFBGA64<br>column).<br>Section 3.11: DAC (digital-to-analog converter): updated bullet list.<br>Table 10: Voltage characteristics on page 52: updated footnote 3<br>regarding I <sub>INJ(PIN)</sub> .<br>Table 11: Current characteristics on page 52: updated footnote 4<br>regarding positive and negative injection.<br>Table 14: Embedded reset and power control block characteristics<br>on page 54: updated typ and max values for T <sub>RSTTEMPO</sub> (V <sub>DD</sub><br>rising, BOR enabled).<br>Table 17: Current consumption in Run mode, code with data<br>processing running from Flash on page 58: removed values for HSI<br>clock source (16 MHz), Range 3.<br>Table 18: Current consumption in Run mode, code with data<br>processing running from RAM on page 59: removed values for HSI<br>clock source (16 MHz), Range 3.<br>Table 19: Current consumption in Sleep mode on page 60 removed<br>values for HSI clock source (16 MHz), Range 3.<br>Table 20: Current consumption in Low power run mode on page 62:<br>updated parameter and max value of I <sub>DD</sub> Max (LP Run).<br>Table 21: Current consumption in Low power sleep mode on<br>page 63: updated symbol, parameter, and max value of I <sub>DD</sub> Max (LP<br>Sleep).<br>Table 22: Typical and maximum current consumptions in Stop mode<br>on page 64 updated values for I <sub>DD</sub> (Stop with RTC) - RTC clocked by<br>LSE external clock (32.768 kHz), regulator in LP mode, HSI and<br>HSE OFF (no independent watchdog). |  |  |

#### Table 73. Document revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |