Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                     |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                    |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, POR, PWM, WDT |

| Number of I/O              | 83                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 4K x 8                                                                  |

| RAM Size                   | 16K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 100-UFBGA                                                               |

| Supplier Device Package    | 100-UFBGA (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l151vbh6   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 48. | TFBGA64, 5 x 5 mm, 0.5 mm pitch, recommended footprint   | 121 |

|------------|----------------------------------------------------------|-----|

| Figure 49. | TFBGA64 5 x 5 mm, 0.5 mm pitch, package top view example | 122 |

| Figure 50. | Thermal resistance                                       | 124 |

HSE crystal oscillators are disabled. The voltage regulator is in the low power mode. The device can be woken up from Stop mode by any of the EXTI line, in 8  $\mu$ s. The EXTI line source can be one of the 16 external lines. It can be the PVD output, the Comparator 1 event or Comparator 2 event (if internal reference voltage is on). It can also be wakened by the USB wakeup.

Stop mode consumption: refer to *Table 22: Typical and maximum current consumptions in Stop mode*.

Standby mode with RTC

Standby mode is used to achieve the lowest power consumption and real time clock. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSI RC and HSE crystal oscillators are also switched off. The LSE or LSI is still running. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32K osc, RCC\_CSR).

The device exits Standby mode in 60 µs when an external reset (NRST pin), an IWDG reset, a rising edge on one of the three WKUP pins, RTC alarm (Alarm A or Alarm B), RTC tamper event, RTC timestamp event or RTC Wakeup event occurs.

Standby mode without RTC

Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI, RC, HSI and LSI RC, HSE and LSE crystal oscillators are also switched off. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32K osc, RCC\_CSR).

The device exits Standby mode in 60  $\mu$ s when an external reset (NRST pin) or a rising edge on one of the three WKUP pin occurs.

Standby mode consumption: refer to *Table 23*.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped by entering the Stop or Standby mode.

|                                                | Functionalities depending on the operating power supply range |                |                                   |                            |  |  |  |  |

|------------------------------------------------|---------------------------------------------------------------|----------------|-----------------------------------|----------------------------|--|--|--|--|

| Operating power<br>supply range                | DAC and ADC operation                                         | USB -          |                                   | I/O operation              |  |  |  |  |

| V <sub>DD</sub> = 1.65 to 1.71 V               | Not functional                                                | Not functional | Range 2 or<br>Range 3             | Degraded speed performance |  |  |  |  |

| V <sub>DD</sub> = 1.71 to 1.8 V <sup>(1)</sup> | Not functional                                                | Not functional | Range 1,<br>Range 2 or<br>Range 3 | Degraded speed performance |  |  |  |  |

| $V_{DD}$ = 1.8 to 2.0 V <sup>(1)</sup>         | Conversion time<br>up to 500 Ksps                             | Not functional | Range 1,<br>Range 2 or<br>Range 3 | Degraded speed performance |  |  |  |  |

| Table 3. Functionalities dep | pending on the operating | power supply range |

|------------------------------|--------------------------|--------------------|

|------------------------------|--------------------------|--------------------|

# 3.15.1 General-purpose timers (TIM2, TIM3, TIM4, TIM9, TIM10 and TIM11)

There are six synchronizable general-purpose timers embedded in the STM32L151x6/8/B and STM32L152x6/8/B devices (see *Table 6* for differences).

#### TIM2, TIM3, TIM4

These timers are based on a 16-bit auto-reload up/down-counter and a 16-bit prescaler. They feature 4 independent channels each for input capture/output compare, PWM or onepulse mode output. This gives up to 12 input captures/output compares/PWMs on the largest packages.

The TIM2, TIM3, TIM4 general-purpose timers can work together or with the TIM10, TIM11 and TIM9 general-purpose timers via the Timer Link feature for synchronization or event chaining. Their counter can be frozen in debug mode. Any of the general-purpose timers can be used to generate PWM outputs.

TIM2, TIM3, TIM4 all have independent DMA request generation.

These timers are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

#### TIM10, TIM11 and TIM9

These timers are based on a 16-bit auto-reload up-counter and a 16-bit prescaler. They include a 16-bit prescaler. TIM10 and TIM11 feature one independent channel, whereas TIM9 has two independent channels for input capture/output compare, PWM or one-pulse mode output. They can be synchronized with the TIM2, TIM3, TIM4 full-featured general-purpose timers.

They can also be used as simple time bases and be clocked by the LSE clock source (32.768 kHz) to provide time bases independent from the main CPU clock.

#### 3.15.2 Basic timers (TIM6 and TIM7)

These timers are mainly used for DAC trigger generation. They can also be used as generic 16-bit time bases.

#### 3.15.3 SysTick timer

This timer is dedicated to the OS, but could also be used as a standard downcounter. It is based on a 24-bit down-counter with autoreload capability and a programmable clock source. It features a maskable system interrupt generation when the counter reaches 0.

# 3.15.4 Independent watchdog (IWDG)

The independent watchdog is based on a 12-bit down-counter and 8-bit prescaler. It is clocked from an independent 37 kHz internal RC and, as it operates independently of the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes. The counter can be frozen in debug mode.

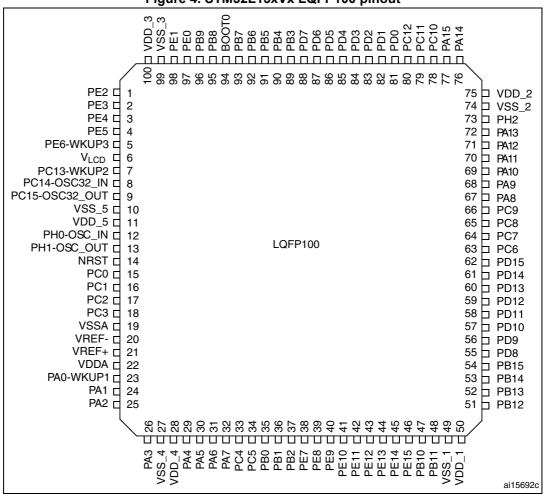

Figure 4. STM32L15xVx LQFP100 pinout

1. This figure shows the package top view.

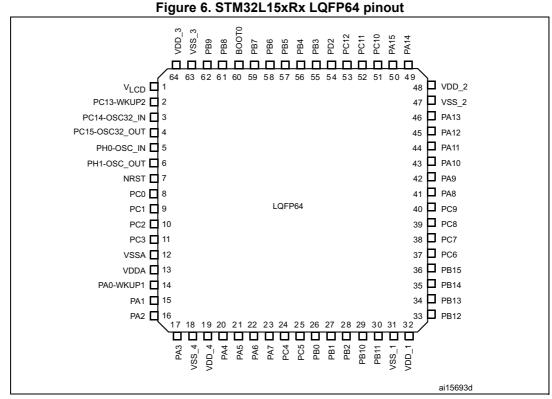

1. This figure shows the package top view.

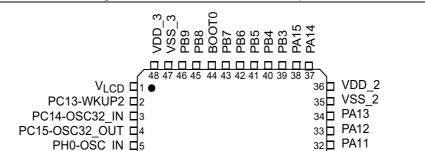

LQFP48

31 PA10

30 PA9

29 PA8

28 PB15

27 PB14

26 PB13 25 PB12

Figure 7. STM32L15xCx LQFP48 pinout

This figure shows the package top view.

PH1-OSC\_OUT

NRST 7

VSSA 🔤 🛚

VDDA

PA1 11 PA2 12

PA0-WKUP1 10

ai15694d

| Na               | me                     | Abbreviation                                                                                                                          | Abbreviation Definition                          |  |  |  |  |  |  |

|------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--|--|--|--|--|--|

| Pin r            | name                   | Unless otherwise specified in brackets below the pin name, the pin funct<br>during and after reset is the same as the actual pin name |                                                  |  |  |  |  |  |  |

|                  |                        | S                                                                                                                                     | Supply pin                                       |  |  |  |  |  |  |

| Pin              | type                   | I                                                                                                                                     | Input only pin                                   |  |  |  |  |  |  |

|                  |                        | I/O                                                                                                                                   | Input / output pin                               |  |  |  |  |  |  |

|                  |                        | FT                                                                                                                                    | 5 V tolerant I/O                                 |  |  |  |  |  |  |

| I/O atr          | ucture                 | TC Standard 3.3 V I/O                                                                                                                 |                                                  |  |  |  |  |  |  |

| i/O sti          | uclure                 | B Dedicated BOOT0 pin                                                                                                                 |                                                  |  |  |  |  |  |  |

|                  |                        | RST Bidirectional reset pin with embedded weak pull-up resis                                                                          |                                                  |  |  |  |  |  |  |

| No               | tes                    | Unless otherwise specified by a note, all I/Os are set as floating inputs durin<br>and after reset                                    |                                                  |  |  |  |  |  |  |

|                  | Alternate<br>functions | Functions selected through GPIOx_AFR registers                                                                                        |                                                  |  |  |  |  |  |  |

| Pin<br>functions | Additional functions   | Functions direct                                                                                                                      | ly selected/enabled through peripheral registers |  |  |  |  |  |  |

# Table 7. Legend/abbreviations used in the pinout table

|                 |        | Table 9. Alternate function input/output (continued) |        |            |        |            |            |               |       |       |        |        |        |        |        |

|-----------------|--------|------------------------------------------------------|--------|------------|--------|------------|------------|---------------|-------|-------|--------|--------|--------|--------|--------|

|                 |        |                                                      |        |            |        | Digital al | ternate fu | nction number |       |       |        |        |        |        |        |

| Port name       | AFIO0  | AFIO1                                                | AFIO2  | AFIO3      | AFIO4  | AFIO5      | AFOI6      | AFIO7         | AFIO8 | AFIO9 | AFIO11 | AFIO12 | AFIO13 | AFIO14 | AFIO15 |

| Fort name       |        | Alternate function                                   |        |            |        |            |            |               |       |       |        |        |        |        |        |

|                 | SYSTEM | TIM2                                                 | TIM3/4 | TIM9/10/11 | I2C1/2 | SPI1/2     | N/A        | USART1/2/3    | N/A   | N/A   | LCD    | N/A    | N/A    | RI     | SYSTEM |

| PH1-<br>OSC_OUT | -      | -                                                    | -      | -          | -      | -          | -          | -             | -     | -     | -      | -      | -      | -      | -      |

| PH2             | -      | -                                                    | -      | -          | -      | -          | -          | -             | -     | -     | -      | -      | -      | -      | -      |

577

# 6 Electrical characteristics

# 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

### 6.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\sigma$ ).

Please refer to device ErrataSheet for possible latest changes of electrical characteristics.

### 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 3.6$  V (for the 1.65 V  $\leq V_{DD} \leq 3.6$  V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\sigma$ ).

#### 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

#### 6.1.4 Loading capacitor

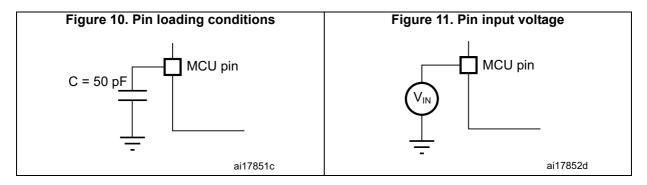

The loading conditions used for pin parameter measurement are shown in Figure 10.

#### 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 11*.

| Symbol                            | Parameter                                                  |                                            | Conditions                                                   |                                         |      | Max<br>(1) | Unit |

|-----------------------------------|------------------------------------------------------------|--------------------------------------------|--------------------------------------------------------------|-----------------------------------------|------|------------|------|

|                                   |                                                            |                                            | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 32 kHz<br>Flash OFF | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$ | 4.4  | -          |      |

|                                   |                                                            |                                            | MSI clock, 65 kHz                                            | $T_A$ = -40 °C to 25 °C                 | 17.5 | 25         |      |

|                                   |                                                            |                                            | f <sub>HCLK</sub> = 32 kHz                                   | T <sub>A</sub> = 85 °C                  | 22   | 27         |      |

|                                   |                                                            | All                                        | Flash ON                                                     | T <sub>A</sub> = 105 °C                 | 31   | 39         |      |

|                                   |                                                            | peripherals<br>OFF, V <sub>DD</sub>        | MSI clock, 65 kHz                                            | $T_A$ = -40 °C to 25 °C                 | 18   | 26         |      |

|                                   |                                                            | from 1.65 V<br>to 3.6 V                    | f <sub>HCLK</sub> = 65 kHz,                                  | T <sub>A</sub> = 85 °C                  | 23   | 28         |      |

|                                   |                                                            | 10 3.0 V                                   | Flash ON                                                     | T <sub>A</sub> = 105 °C                 | 31   | 40         |      |

|                                   |                                                            |                                            |                                                              | $T_A$ = -40 °C to 25 °C                 | 22   | 30         |      |

| I <sub>DD</sub> (LP               | Supply                                                     |                                            | MSI clock, 131 kHz                                           | T <sub>A</sub> = 55 °C                  | 24   | 32         | μΑ   |

|                                   | Low power                                                  |                                            | f <sub>HCLK</sub> = 131 kHz,<br>Flash ON                     | T <sub>A</sub> = 85 °C                  | 26   | 34         |      |

| Sleep)                            | sleep                                                      |                                            |                                                              | T <sub>A</sub> = 105 °C                 | 34   | 45         |      |

|                                   | mode                                                       |                                            |                                                              | $T_A$ = -40 °C to 25 °C                 | 17.5 | 25         |      |

|                                   |                                                            |                                            | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 32 kHz              | T <sub>A</sub> = 85 °C                  | 22   | 27         |      |

|                                   |                                                            |                                            |                                                              | T <sub>A</sub> = 105 °C                 | 31   | 39         |      |

|                                   |                                                            | TIM9 and<br>USART1                         | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 65 kHz              | $T_A$ = -40 °C to 25 °C                 | 18   | 26         |      |

|                                   |                                                            | enabled,                                   |                                                              | T <sub>A</sub> = 85 °C                  | 23   | 28         |      |

|                                   |                                                            | Flash ON,<br>V <sub>DD</sub> from          | HOLK OUT IN                                                  | T <sub>A</sub> = 105 °C                 | 31   | 40         |      |

|                                   |                                                            | 1.65 V to<br>3.6 V                         |                                                              | $T_A$ = -40 °C to 25 °C                 | 22   | 30         |      |

|                                   |                                                            | 0.0 V                                      | MSI clock, 131 kHz                                           | T <sub>A</sub> = 55 °C                  | 24   | 32         |      |

|                                   |                                                            |                                            | f <sub>HCLK</sub> = 131 kHz                                  | T <sub>A</sub> = 85 °C                  | 26   | 34         |      |

|                                   |                                                            |                                            |                                                              | T <sub>A</sub> = 105 °C                 | 34   | 45         |      |

| I <sub>DD</sub> Max<br>(LP Sleep) | Max<br>allowed<br>current in<br>Low power<br>Sleep<br>mode | V <sub>DD</sub> from<br>1.65 V to<br>3.6 V | -                                                            | -                                       | -    | 200        |      |

Table 21. Current consumption in Low power sleep mode

1. Guaranteed by characterization results, unless otherwise specified.

| Typical consumption, $V_{DD} = 3.0 \text{ V}$ , $T_A = 25 ^{\circ}\text{C}$ |           |                                                       |                                                       |                                                   |      |                      |  |  |

|-----------------------------------------------------------------------------|-----------|-------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------|------|----------------------|--|--|

| Peripheral                                                                  |           | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | V <sub>CORE</sub> =1.5 V V <sub>CORE</sub> =1.2 V |      | Unit                 |  |  |

|                                                                             | GPIOA     | 5                                                     | 4.5                                                   | 3.5                                               | 4    |                      |  |  |

|                                                                             | GPIOB     | 5                                                     | 4.5                                                   | 3.5                                               | 4.5  |                      |  |  |

|                                                                             | GPIOC     | 5                                                     | 4.5                                                   | 3.5                                               | 4.5  |                      |  |  |

|                                                                             | GPIOD     | 5                                                     | 4.5                                                   | 3.5                                               | 4.5  |                      |  |  |

| AHB                                                                         | GPIOE     | 5                                                     | 4.5                                                   | 3.5                                               | 4.5  | µA/MHz               |  |  |

|                                                                             | GPIOH     | 4                                                     | 4                                                     | 3                                                 | 3.5  | (f <sub>HCLK</sub> ) |  |  |

|                                                                             | CRC       | 1                                                     | 0.5                                                   | 0.5                                               | 0.5  |                      |  |  |

|                                                                             | FLASH     | 13                                                    | 11.5                                                  | 9                                                 | 18.5 |                      |  |  |

|                                                                             | DMA1      | 12                                                    | 10                                                    | 8                                                 | 10.5 |                      |  |  |

| All enabled                                                                 |           | 166                                                   | 138                                                   | 106                                               | 130  |                      |  |  |

| I <sub>DD (RTC)</sub>                                                       |           |                                                       |                                                       |                                                   |      |                      |  |  |

| I <sub>DD (LCD)</sub>                                                       |           |                                                       |                                                       |                                                   |      |                      |  |  |

| I <sub>DD (ADC)</sub> <sup>(3)</sup>                                        |           |                                                       |                                                       |                                                   |      |                      |  |  |

| I <sub>DD (DAC)</sub> <sup>(4)</sup>                                        |           |                                                       |                                                       |                                                   |      |                      |  |  |

| I <sub>DD</sub> (COMP1)                                                     |           |                                                       | μA                                                    |                                                   |      |                      |  |  |

|                                                                             | Slow mode |                                                       | 2                                                     |                                                   |      |                      |  |  |

| IDD (COMP2) Fast mode                                                       |           |                                                       |                                                       |                                                   |      |                      |  |  |

| I <sub>DD (PVD / BOR)</sub>                                                 | (5)       |                                                       |                                                       |                                                   |      |                      |  |  |

| I <sub>DD (IWDG)</sub>                                                      |           |                                                       | 0.1                                                   | 25                                                |      |                      |  |  |

#### Table 24. Peripheral current consumption<sup>(1)</sup> (continued)

Data based on differential I<sub>DD</sub> measurement between all peripherals OFF an one peripheral with clock enabled, in the following conditions: f<sub>HCLK</sub> = 32 MHz (Range 1), f<sub>HCLK</sub> = 16 MHz (Range 2), f<sub>HCLK</sub> = 4 MHz (Range 3), f<sub>HCLK</sub> = 64kHz (Low power run/sleep), f<sub>APB1</sub> = f<sub>HCLK</sub>, f<sub>APB2</sub> = f<sub>HCLK</sub>, default prescaler value for each peripheral. The CPU is in Sleep mode in both cases. No I/O pins toggling.

2. HSI oscillator is OFF for this measure.

3. Data based on a differential IDD measurement between ADC in reset configuration and continuous ADC conversion (HSI consumption not included).

4. Data based on a differential Ibb measurement between DAC in reset configuration and continuous DAC conversion of Vbb/2. DAC is in buffered mode, output is left floating.

5. Including supply current of internal reference voltage.

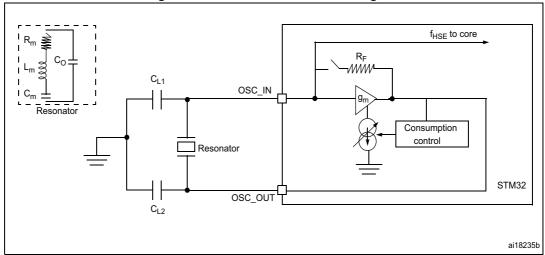

Figure 17. HSE oscillator circuit diagram

1. R<sub>EXT</sub> value depends on the crystal characteristics.

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 29*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                                                                                     | Conditions                            | Min | Тур    | Мах | Unit |

|-------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------|-----|--------|-----|------|

| f <sub>LSE</sub>                    | Low speed external oscillator<br>frequency                                                    | -                                     | -   | 32.768 | -   | kHz  |

| R <sub>F</sub>                      | Feedback resistor                                                                             | -                                     | -   | 1.2    | -   | MΩ   |

| C <sup>(2)</sup>                    | Recommended load capacitance versus equivalent serial resistance of the crystal $(R_S)^{(3)}$ | R <sub>S</sub> = 30 kΩ                | -   | 8      | -   | pF   |

| I <sub>LSE</sub>                    | LSE driving current                                                                           | $V_{DD}$ = 3.3 V, $V_{IN}$ = $V_{SS}$ | -   | -      | 1.1 | μA   |

|                                     |                                                                                               | V <sub>DD</sub> = 1.8 V               | -   | 450    | -   |      |

| I <sub>DD (LSE)</sub>               | LSE oscillator current consumption                                                            | V <sub>DD</sub> = 3.0 V               | -   | 600    | -   | nA   |

|                                     |                                                                                               | V <sub>DD</sub> = 3.6V                | -   | 750    | -   |      |

| 9 <sub>m</sub>                      | Oscillator transconductance                                                                   | -                                     | 3   | -      | -   | µA/V |

| t <sub>SU(LSE)</sub> <sup>(4)</sup> | Startup time                                                                                  | V <sub>DD</sub> is stabilized         | -   | 1      | -   | s    |

| Table 29. LSE oscillator characteristics | (f <sub>LSE</sub> = 32.768 kHz) <sup>(1)</sup> |

|------------------------------------------|------------------------------------------------|

|------------------------------------------|------------------------------------------------|

1. Guaranteed by characterization results.

2. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

The oscillator selection can be optimized in terms of supply current using an high quality resonator with small R<sub>S</sub> value for example MSIV-TIN32.768kHz. Refer to crystal manufacturer for more details.

# 6.3.13 I/O port characteristics

## General input/output characteristics

Unless otherwise specified, the parameters given in *Table 42* are derived from tests performed under conditions summarized in *Table 13*. All I/Os are CMOS and TTL compliant.

| Symbol           | Parameter                                          | Conc                                                                                                                                                                                                                                                                                                                                                                                                          | litions                                     | Min                 | Тур                                | Мах                               | Unit |

|------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|---------------------|------------------------------------|-----------------------------------|------|

| V <sub>IL</sub>  | Input low level voltage                            | -                                                                                                                                                                                                                                                                                                                                                                                                             | -                                           | -                   | -                                  | 0.3V <sub>DD</sub> <sup>(1)</sup> |      |

| V                | Input high lovel veltage                           | Stand                                                                                                                                                                                                                                                                                                                                                                                                         | ard I/O                                     | 0.7.\/              | -                                  | -                                 |      |

| VIH              | Input high level voltage                           | FT                                                                                                                                                                                                                                                                                                                                                                                                            | · I/O                                       | 0.7 V <sub>DD</sub> | -                                  | -                                 | V    |

| V.               | I/O Schmitt trigger voltage                        | Stand                                                                                                                                                                                                                                                                                                                                                                                                         | ard I/O                                     | -                   | 10% V <sub>DD</sub> <sup>(3)</sup> | -                                 |      |

| V <sub>hys</sub> | hysteresis <sup>(2)</sup>                          | FT                                                                                                                                                                                                                                                                                                                                                                                                            | I/O                                         | -                   | 5% V <sub>DD</sub> <sup>(4)</sup>  | -                                 |      |

|                  |                                                    | 00                                                                                                                                                                                                                                                                                                                                                                                                            | / <sub>IN</sub> ≤V <sub>DD</sub><br>ith LCD | -                   | -                                  | ±50                               |      |

|                  | Input leakage current <sup>(5)</sup>               | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>I/Os with analog<br>switches                                                                                                                                                                                                                                                                                                                             |                                             | -                   | -                                  | ±50                               |      |

| I <sub>lkg</sub> |                                                    | $\label{eq:second} \begin{array}{l} V_{SS} \leq V_{IN} \leq V_{DD} \\ I/Os \mbox{ with analog} \\ switches \mbox{ and } LCD \\ \end{array} \\ \begin{array}{l} V_{SS} \leq V_{IN} \leq V_{DD} \\ I/Os \mbox{ with } USB \\ \end{array} \\ \begin{array}{l} FT  I/O \\ V_{DD} \leq V_{IN} \leq SV \\ \end{array} \\ \begin{array}{l} V_{SS} \leq V_{IN} \leq V_{DD} \\ Standard  I/Os \end{array} \end{array}$ |                                             | -                   | -                                  | ±50                               | nA   |

|                  |                                                    |                                                                                                                                                                                                                                                                                                                                                                                                               |                                             | -                   | -                                  | TBD                               |      |

|                  |                                                    |                                                                                                                                                                                                                                                                                                                                                                                                               |                                             | -                   | -                                  | TBD                               |      |

|                  |                                                    |                                                                                                                                                                                                                                                                                                                                                                                                               |                                             | -                   | -                                  | ±50                               |      |

| R <sub>PU</sub>  | Weak pull-up equivalent resistor <sup>(6)(1)</sup> | V <sub>IN</sub> = V <sub>SS</sub>                                                                                                                                                                                                                                                                                                                                                                             |                                             | 30                  | 45                                 | 60                                | kΩ   |

| R <sub>PD</sub>  | Weak pull-down equivalent resistor <sup>(6)</sup>  | V <sub>IN</sub> =                                                                                                                                                                                                                                                                                                                                                                                             | = V <sub>DD</sub>                           | 30                  | 45                                 | 60                                | kΩ   |

| C <sub>IO</sub>  | I/O pin capacitance                                | -                                                                                                                                                                                                                                                                                                                                                                                                             | -                                           | -                   | 5                                  | -                                 | pF   |

|  | Table 42. | I/O | static | characteristics |

|--|-----------|-----|--------|-----------------|

|--|-----------|-----|--------|-----------------|

1. Tested in production

2. Hysteresis voltage between Schmitt trigger switching levels. Based on characterization.

3. With a minimum of 200 mV. Based on characterization results.

4. With a minimum of 100 mV. Based on characterization results.

5. The max. value may be exceeded if negative current is injected on adjacent pins.

Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This MOS/NMOS contribution to the series resistance is minimum (~10% order).

#### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 20$  mA (with the non-standard V<sub>OL</sub>/V<sub>OH</sub> specifications given in *Table 43*.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 6.2*:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating I<sub>VDDΣ</sub> (see *Table 11*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating I<sub>VSSΣ</sub> (see *Table 11*).

### **Output voltage levels**

Unless otherwise specified, the parameters given in *Table 43* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 13*. All I/Os are CMOS and TTL compliant.

| Symbol                            | Parameter                                | Conditions                       | Min                   | Max  | Unit |

|-----------------------------------|------------------------------------------|----------------------------------|-----------------------|------|------|

| V <sub>OL</sub> <sup>(1)(2)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = 8 mA           | -                     | 0.4  |      |

| V <sub>OH</sub> <sup>(3)(2)</sup> | Output high level voltage for an I/O pin | 2.7 V < V <sub>DD</sub> < 3.6 V  | 2.4                   | -    |      |

| V <sub>OL</sub> <sup>(1)(4)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = 4 mA           | -                     | 0.45 | v    |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin | 1.65 V < V <sub>DD</sub> < 2.7 V | V <sub>DD</sub> -0.45 | -    | v    |

| V <sub>OL</sub> <sup>(1)(4)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = 20 mA          | -                     | 1.3  |      |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin | 2.7 V < V <sub>DD</sub> < 3.6 V  | V <sub>DD</sub> -1.3  | -    |      |

#### Table 43. Output voltage characteristics

1. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 11* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. Tested in production.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in *Table 11* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

4. Guaranteed by characterization results.

### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 19* and *Table 44*, respectively.

Unless otherwise specified, the parameters given in *Table 44* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 13*.

| OSPEEDRx<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                                                                                | Parameter                                                | Conditions                                  | Min | Max <sup>(2)</sup> | Unit |  |

|-----------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------|---------------------------------------------|-----|--------------------|------|--|

| 00                                            | f                                                                                     | Maximum frequency <sup>(3)</sup>                         | $C_L$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V    | -   | 400                | kHz  |  |

|                                               | f <sub>max(IO)out</sub>                                                               |                                                          | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V | -   | 400                | ĸΠΖ  |  |

| 00                                            | t <sub>f(IO)out</sub>                                                                 | Output rise and fall time                                | $C_L$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V    | -   | 625                |      |  |

|                                               | t <sub>r(IO)out</sub>                                                                 |                                                          | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V | -   | 625                | ns   |  |

|                                               | f                                                                                     | Maximum frequency <sup>(3)</sup>                         | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V  | -   | 2                  | MHz  |  |

| 01                                            | f <sub>max(IO)out</sub>                                                               |                                                          | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V | -   | 1                  |      |  |

| 01                                            | t <sub>f(IO)out</sub> Output rise and fall t                                          |                                                          | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V  | -   | 125                | ns   |  |

|                                               | t <sub>r(IO)out</sub>                                                                 |                                                          | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V | -   | 250                | 115  |  |

|                                               | F <sub>max(IO)out</sub>                                                               | ut Maximum frequency <sup>(3)</sup>                      | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V  | -   | 10                 | MHz  |  |

| 10                                            |                                                                                       |                                                          | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V | -   | 2                  |      |  |

| 10                                            | t <sub>f(IO)out</sub>                                                                 | Output rise and fall time                                | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V  | -   | 25                 | ns   |  |

|                                               | t <sub>r(IO)out</sub>                                                                 |                                                          | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V | -   | 125                | 115  |  |

|                                               | г                                                                                     | F <sub>max(IQ)out</sub> Maximum frequency <sup>(3)</sup> | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V  | -   | 50                 | MHz  |  |

| 11                                            | F <sub>max(IO)out</sub> Maximum frequency <sup>(3)</sup>                              |                                                          | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V | -   | 8                  |      |  |

|                                               | t <sub>f(IO)out</sub>                                                                 | Output rise and fall time                                | $C_{L}$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V  | -   | 5                  |      |  |

|                                               | $t_{r(IO)out}$ Output rise and fall time                                              | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V              | -                                           | 30  |                    |      |  |

| -                                             | - t <sub>EXTIpw</sub> Pulse width of external signals detected by the EXTI controller |                                                          | -                                           | 8   | -                  | ns   |  |

| Table 44. | I/O AC | characteristics <sup>(1)</sup> |

|-----------|--------|--------------------------------|

|-----------|--------|--------------------------------|

1. The I/O speed is configured using the OSPEEDRx[1:0] bits. Refer to the STM32L151x6/8/B and STM32L152x6/8/B reference manual for a description of GPIO Port configuration register.

2. Guaranteed by design.

3. The maximum frequency is defined in *Figure 19*.

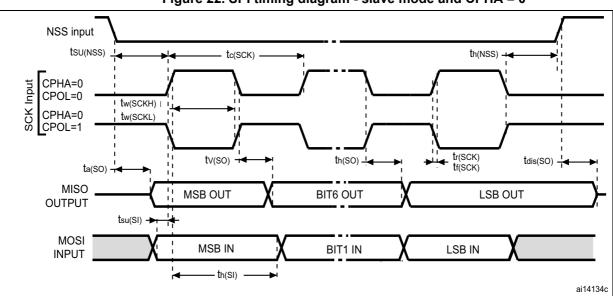

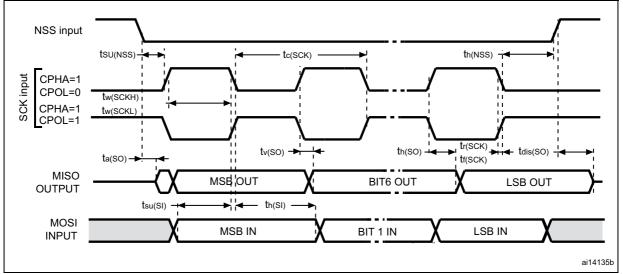

Figure 22. SPI timing diagram - slave mode and CPHA = 0

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}$

#### STM32L151x6/8/B STM32L152x6/8/B

| Symbol | Parameter                            | Test conditions                                                                          | Min <sup>(3)</sup> | Тур | Max <sup>(3)</sup> | Unit |

|--------|--------------------------------------|------------------------------------------------------------------------------------------|--------------------|-----|--------------------|------|

| ET     | Total unadjusted error               |                                                                                          | -                  | 2   | 4                  |      |

| EO     | Offset error                         | $2.4 \text{ V} \le \text{V}_{\text{DDA}} \le 3.6 \text{ V}$                              | -                  | 1   | 2                  |      |

| EG     | Gain error                           | 2.4 V ≤ V <sub>REF+</sub> ≤ 3.6 V<br>f <sub>ADC</sub> = 8 MHz, R <sub>AIN</sub> = 50 Ω   | -                  | 1.5 | 3.5                | LSB  |

| ED     | Differential linearity error         | $T_A = -40$ to 105 ° C                                                                   | -                  | 1   | 2                  |      |

| EL     | Integral linearity error             |                                                                                          | -                  | 1.7 | 3                  |      |

| ENOB   | Effective number of bits             | 2.4 V ≤ V <sub>DDA</sub> ≤ 3.6 V                                                         | 9.2                | 10  | -                  | bits |

| SINAD  | Signal-to-noise and distortion ratio | $V_{\text{DDA}} = V_{\text{REF}+}$<br>f <sub>ADC</sub> = 16 MHz, R <sub>AIN</sub> = 50 Ω | 57.5               | 62  | -                  |      |

| SNR    | Signal-to-noise ratio                | T <sub>A</sub> = -40 to 105 ° C                                                          | 57.5               | 62  | -                  | dB   |

| THD    | Total harmonic distortion            | 1 kHz ≤ F <sub>input</sub> ≤ 100 kHz                                                     | -74                | -75 | -                  |      |

| ET     | Total unadjusted error               |                                                                                          | -                  | 4   | 6.5                |      |

| EO     | Offset error                         | 2.4 V ≤ V <sub>DDA</sub> ≤ 3.6 V                                                         | -                  | 2   | 4                  | 1    |

| EG     | Gain error                           | 1.8 V ≤ V <sub>REF+</sub> ≤ 2.4 V<br>f <sub>ADC</sub> = 4 MHz, R <sub>AIN</sub> = 50 Ω   | -                  | 4   | 6                  | LSB  |

| ED     | Differential linearity error         | $T_A = -40$ to 105 °C                                                                    | -                  | 1   | 2                  |      |

| EL     | Integral linearity error             |                                                                                          | -                  | 1.5 | 3                  |      |

| ET     | Total unadjusted error               |                                                                                          | -                  | 2   | 3                  |      |

| EO     | Offset error                         | $1.8 V \le V_{DDA} \le 2.4 V$                                                            | -                  | 1   | 1.5                |      |

| EG     | Gain error                           | 1.8 V ≤ V <sub>REF+</sub> ≤ 2.4 V<br>f <sub>ADC</sub> = 4 MHz, R <sub>AIN</sub> = 50 Ω   | -                  | 1.5 | 2                  | LSB  |

| ED     | Differential linearity error         | $T_{A} = -40$ to 105 ° C                                                                 | -                  | 1   | 2                  |      |

| EL     | Integral linearity error             |                                                                                          | -                  | 1   | 1.5                |      |

1. ADC DC accuracy values are measured after internal calibration.

ADC accuracy vs. negative injection current: Injecting a negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in Section 6.3.12 does not affect the ADC accuracy.

3. Guaranteed by characterization results.

| Symbol                    | Parameter                                                                                                                                                       | Conditions                                                                         | Min | Тур             | Мах              | Unit    |  |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----|-----------------|------------------|---------|--|

| dOffset/dT <sup>(1)</sup> | Offset error temperature                                                                                                                                        | $V_{DDA} = 3.3V$ , $T_A = 0$ to 50 ° C<br>DAC output buffer OFF                    | -20 | -10             | 0                | µV/°C   |  |

|                           | coefficient (code 0x800)                                                                                                                                        | $V_{DDA} = 3.3V$ , $T_A = 0$ to 50 ° C<br>DAC output buffer ON                     | 0   | 20              | 50               | μν/ Ο   |  |

| Gain <sup>(1)</sup>       | Gain error <sup>(6)</sup>                                                                                                                                       | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON         | -   | +0.1 /<br>-0.2% | +0.2 / -<br>0.5% | %       |  |

| Gain                      | Gain enor                                                                                                                                                       | No R <sub>LOAD</sub> , C <sub>L</sub> ≤50 pF<br>DAC output buffer OFF              | -   | +0 / -0.2%      | +0 / -0.4%       | 70      |  |

| dGain/dT <sup>(1)</sup>   | Gain error temperature                                                                                                                                          | $V_{DDA} = 3.3V$ , $T_A = 0$ to 50 ° C<br>DAC output buffer OFF                    | -10 | -2              | 0                | - μV/°C |  |

| aGain/a i                 | coefficient                                                                                                                                                     | $V_{DDA} = 3.3V$ , $T_A = 0$ to 50 ° C<br>DAC output buffer ON                     | -40 | -8              | 0                |         |  |

| TUE <sup>(1)</sup>        | Total unadjusted error                                                                                                                                          | $C_L \le 50 \text{ pF}, \text{ R}_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON | -   | 12              | 30               | - LSB   |  |

|                           |                                                                                                                                                                 | No R <sub>LOAD</sub> , C <sub>L</sub> ≤50 pF<br>DAC output buffer OFF              | -   | 8               | 12               |         |  |

| tSETTLING                 | Settling time (full scale:<br>for a 12-bit code<br>transition between the<br>lowest and the highest<br>input codes till<br>DAC_OUT reaches final<br>value ±1LSB | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                 | -   | 7               | 12               | μs      |  |

| Update rate               | Max frequency for a<br>correct DAC_OUT<br>change (95% of final<br>value) with 1 LSB<br>variation in the input<br>code                                           | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                 | -   | -               | 1                | Msps    |  |

| t <sub>wakeup</sub>       | Wakeup time from off<br>state (setting the ENx bit<br>in the DAC Control<br>register) <sup>(7)</sup>                                                            | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                 | -   | 9               | 15               | μs      |  |

| PSRR+                     | V <sub>DDA</sub> supply rejection<br>ratio (static DC<br>measurement)                                                                                           | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                 | -   | -60             | -35              | dB      |  |

#### Table 57. DAC characteristics (continued)

1. Guaranteed by characterization results.

2. Difference between two consecutive codes - 1 LSB.

3. Difference between measured value at Code i and the value at Code i on a line drawn between Code 0 and last Code 4095.

4. Difference between the value measured at Code (0x800) and the ideal value = V/2.

5. Difference between the value measured at Code (0x001) and the ideal value.

6. Difference between ideal slope of the transfer function and measured slope computed from code 0x000 and 0xFFF when buffer is OFF, and from code giving 0.2 V and ( $V_{DDA} - 0.2$ ) V when buffer is ON.

7. In buffered mode, the output can overshoot above the final value for low input code (starting from min value).

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|-------|-------|-----------------------|--------|--------|--|

| Symbol | Min         | Тур   | Max   | Min                   | Тур    | Max    |  |

| А      | -           | -     | 1.600 | -                     | -      | 0.0630 |  |

| A1     | 0.050       | -     | 0.150 | 0.0020                | -      | 0.0059 |  |

| A2     | 1.350       | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |  |

| b      | 0.170       | 0.220 | 0.270 | 0.0067                | 0.0087 | 0.0106 |  |

| С      | 0.090       | -     | 0.200 | 0.0035                | -      | 0.0079 |  |

| D      | 8.800       | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |  |

| D1     | 6.800       | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |  |

| D3     | -           | 5.500 | -     | -                     | 0.2165 | -      |  |

| E      | 8.800       | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |  |

| E1     | 6.800       | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |  |

| E3     | -           | 5.500 | -     | -                     | 0.2165 | -      |  |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |  |

| L      | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |  |

| L1     | -           | 1.000 | -     | -                     | 0.0394 | -      |  |

| k      | 0°          | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |  |

| CCC    | -           | -     | 0.080 | -                     | -      | 0.0031 |  |

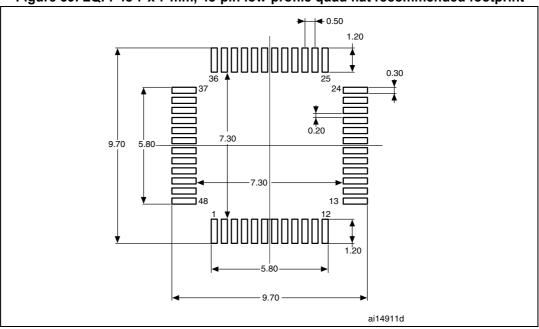

Table 65. LQFP48 7 x 7 mm, 48-pin low-profile quad flat package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are in millimeters.

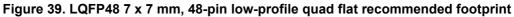

# **TFBGA64** device marking

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Figure 49. TFBGA64 5 x 5 mm, 0.5 mm pitch, package top view example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

# 8 Ordering information

| Table 72. Ordering                                  | information | on scheme |       |   |

|-----------------------------------------------------|-------------|-----------|-------|---|

| Example:                                            | STM32       | L 151 C 8 | T 6 7 |   |

| Device family                                       |             |           |       |   |

| STM32 = ARM-based 32-bit microcontroller            |             |           |       |   |

| Product type                                        |             |           |       |   |

| L = Low power                                       |             |           |       |   |

| Device subfamily                                    |             |           |       |   |

| 151: Devices without LCD                            |             |           |       |   |

| 152: Devices with LCD                               |             |           |       |   |

| 132. Devices with ECD                               |             |           |       |   |

| Pin count                                           |             |           |       |   |

| C = 48 pins                                         |             |           |       |   |

| R = 64 pins                                         |             |           |       |   |

| V = 100 pins                                        |             |           |       |   |

| Flash memory size                                   |             |           |       |   |

| 6 = 32 Kbytes of Flash memory                       |             |           |       |   |

| 8 = 64 Kbytes of Flash memory                       |             |           |       |   |

| B = 128 Kbytes of Flash memory                      |             |           |       |   |

| Package                                             |             |           |       |   |

| H = BGA                                             |             |           |       |   |

| T = LQFP                                            |             |           |       |   |

| U = UFQFPN                                          |             |           |       |   |

| Temperature range                                   |             |           |       |   |

| 6 = Industrial temperature range, -40 to 85 °C      |             |           | 1     |   |

| Options                                             |             |           |       |   |

| No character = $V_{DD}$ range: 1.8 to 3.6 V and BOF | R enabled   |           |       | • |

| T = $V_{DD}$ range: 1.65 to 3.6 V and BOR disabled  |             |           |       |   |

| Packing                                             |             |           |       |   |

TR = tape and reel No character = tray or tube

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.

DocID17659 Rev 12