Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                              |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                         |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT |

| Number of I/O              | 37                                                                           |

| Program Memory Size        | 32KB (32K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 4K x 8                                                                       |

| RAM Size                   | 10K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                        |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 48-LQFP                                                                      |

| Supplier Device Package    | 48-LQFP (7x7)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l152c6t6        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1 Introduction                                             | 9  |

|------------------------------------------------------------|----|

| 2 Description                                              | 10 |

| 2.1 Device overview                                        |    |

| 2.2 Ultra-low-power device continuum                       | 12 |

| 2.2.1 Performance                                          |    |

| 2.2.2 Shared peripherals                                   | 12 |

| 2.2.3 Common system strategy                               | 12 |

| 2.2.4 Features                                             | 12 |

| 3 Functional overview                                      | 13 |

| 3.1 Low power modes                                        | 14 |

| 3.2 ARM <sup>®</sup> Cortex <sup>®</sup> -M3 core with MPU | 18 |

| 3.3 Reset and supply management                            | 19 |

| 3.3.1 Power supply schemes                                 |    |

| 3.3.2 Power supply supervisor                              | 19 |

| 3.3.3 Voltage regulator                                    | 20 |

| 3.3.4 Boot modes                                           | 20 |

| 3.4 Clock management                                       |    |

| 3.5 Low power real-time clock and backup registers         |    |

| 3.6 GPIOs (general-purpose inputs/outputs)                 |    |

| 3.7 Memories                                               |    |

| 3.8 DMA (direct memory access)                             |    |

| 3.9 LCD (liquid crystal display)                           |    |

| 3.10 ADC (analog-to-digital converter)                     |    |

| 3.10.1 Temperature sensor                                  |    |

| 3.10.2 Internal voltage reference (V <sub>REFINT</sub> )   |    |

| 3.11 DAC (digital-to-analog converter)                     |    |

| 3.12 Ultra-low-power comparators and reference voltage     |    |

| 3.13 Routing interface                                     |    |

| 3.14 Touch sensing                                         |    |

|                                                            |    |

# 2.2 Ultra-low-power device continuum

The ultra-low-power STM32L151x6/8/B and STM32L152x6/8/B devices are fully pin-to-pin and software compatible. Besides the full compatibility within the family, the devices are part of STMicroelectronics microcontrollers ultra-low-power strategy which also includes STM8L101xx and STM8L15xx devices. The STM8L and STM32L families allow a continuum of performance, peripherals, system architecture and features.

They are all based on STMicroelectronics ultra-low leakage process.

Note: The ultra-low-power STM32L and general-purpose STM32Fxxxx families are pin-to-pin compatible. The STM8L15xxx devices are pin-to-pin compatible with the STM8L101xx devices. Please refer to the STM32F and STM8L documentation for more information on these devices.

## 2.2.1 Performance

All families incorporate highly energy-efficient cores with both Harvard architecture and pipelined execution: advanced STM8 core for STM8L families and ARM<sup>®</sup> Cortex<sup>®</sup>-M3 core for STM32L family. In addition specific care for the design architecture has been taken to optimize the mA/DMIPS and mA/MHz ratios.

This allows the ultra-low-power performance to range from 5 up to 33.3 DMIPs.

# 2.2.2 Shared peripherals

STM8L15xxx and STM32L1xxxx share identical peripherals which ensure a very easy migration from one family to another:

- Analog peripherals: ADC, DAC and comparators

- Digital peripherals: RTC and some communication interfaces

# 2.2.3 Common system strategy

To offer flexibility and optimize performance, the STM8L15xx and STM32L1xxxx families use a common architecture:

- Same power supply range from 1.65 V to 3.6 V, (1.65 V at power down only for STM8L15xx devices)

- Architecture optimized to reach ultra-low consumption both in low power modes and Run mode

- Fast startup strategy from low power modes

- Flexible system clock

- Ultrasafe reset: same reset strategy including power-on reset, power-down reset, brownout reset and programmable voltage detector.

# 2.2.4 Features

ST ultra-low-power continuum also lies in feature compatibility:

- More than 10 packages with pin count from 20 to 144 pins and size down to 3 x 3 mm

- Memory density ranging from 4 to 384 Kbytes

# **3** Functional overview

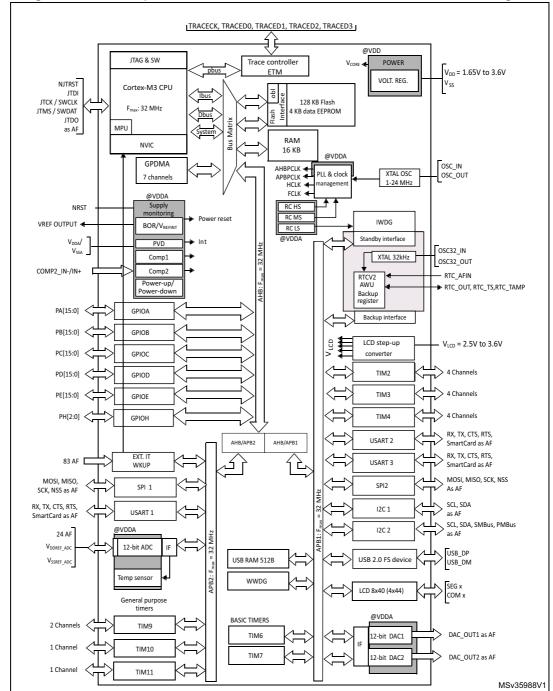

Figure 1 shows the block diagram.

#### Figure 1. Ultra-low-power STM32L151x6/8/B and STM32L152x6/8/B block diagram

1. AF = alternate function on I/O port pin.

|                                           |            |       | Low-         | Low-           |   | Stop                 |   | Standby              |

|-------------------------------------------|------------|-------|--------------|----------------|---|----------------------|---|----------------------|

| lps                                       | Run/Active | Sleep | power<br>Run | power<br>Sleep |   | Wakeup<br>capability |   | Wakeup<br>capability |

| CPU                                       | Y          | -     | Y            | -              | - | -                    | - | -                    |

| Flash                                     | Y          | Y     | Y            | Y              | - | -                    | - | -                    |

| RAM                                       | Y          | Y     | Y            | Y              | Y | -                    | - | -                    |

| Backup Registers                          | Y          | Y     | Y            | Y              | Y | -                    | Y | -                    |

| EEPROM                                    | Y          | -     | Y            | Y              | Y | -                    | - | -                    |

| Brown-out rest<br>(BOR)                   | Y          | Y     | Y            | Y              | Y | Y                    | Y | -                    |

| DMA                                       | Y          | Y     | Y            | Y              | - | -                    | - | -                    |

| Programmable<br>Voltage Detector<br>(PVD) | Y          | Y     | Y            | Y              | Y | Y                    | Y | -                    |

| Power On Reset<br>(POR)                   | Y          | Y     | Y            | Y              | Y | Y                    | Y | -                    |

| Power Down Rest<br>(PDR)                  | Y          | Y     | Y            | Y              | Y | -                    | Y | -                    |

| High Speed<br>Internal (HSI)              | Y          | Y     | -            | -              | - | -                    | - | -                    |

| High Speed<br>External (HSE)              | Y          | Y     | -            | -              | - | -                    | - | -                    |

| Low Speed Internal<br>(LSI)               | Y          | Y     | Y            | Y              | Y | -                    | Y | -                    |

| Low Speed<br>External (LSE)               | Y          | Y     | Y            | Y              | Y | -                    | Y | -                    |

| Multi-Speed<br>Internal (MSI)             | Y          | Y     | Y            | Y              | - | -                    | - | -                    |

| Inter-Connect<br>Controller               | Y          | Y     | Y            | Y              | - | -                    | - | -                    |

| RTC                                       | Y          | Y     | Y            | Y              | Y | Y                    | Y | -                    |

| RTC Tamper                                | Y          | Y     | Y            | Y              | Y | Y                    | Y | Y                    |

| Auto Wakeup<br>(AWU)                      | Y          | Y     | Y            | Y              | Y | Y                    | Y | Y                    |

| LCD                                       | Y          | Y     | Y            | Y              | Y | -                    | - | -                    |

| USB                                       | Y          | Y     | -            | -              | - | Y                    | - | -                    |

| USART                                     | Y          | Y     | Y            | Y              | Y | (1)                  | - | -                    |

| SPI                                       | Y          | Y     | Y            | Y              | - | -                    | - | -                    |

| I2C                                       | Y          | Y     | Y            | Y              | - | (1)                  | - | -                    |

| ADC                                       | Y          | Y     | -            | -              | - | -                    | - | -                    |

| Table 5. Working mode-dependent functionalities ( | from Run/active down to standby) |

|---------------------------------------------------|----------------------------------|

|---------------------------------------------------|----------------------------------|

|                                              |                       |                      | Low-         | Low-           |                                                                                        | Stop                                  | 5 | Standby                                |

|----------------------------------------------|-----------------------|----------------------|--------------|----------------|----------------------------------------------------------------------------------------|---------------------------------------|---|----------------------------------------|

| lps                                          | Run/Active            | Sleep                | power<br>Run | power<br>Sleep |                                                                                        | Wakeup<br>capability                  |   | Wakeup<br>capability                   |

| DAC                                          | Y                     | Y                    | Y            | Y              | Y                                                                                      | -                                     | - | -                                      |

| Temperature<br>sensor                        | Y                     | Y                    | Y            | Y              | Y                                                                                      | -                                     | - | -                                      |

| Comparators                                  | Y                     | Y                    | Y            | Y              | Y                                                                                      | Y                                     | - | -                                      |

| 16-bit and 32-bit<br>Timers                  | Y                     | Y                    | Y            | Y              | -                                                                                      | -                                     | - | -                                      |

| IWDG                                         | Y                     | Y                    | Y            | Y              | Y                                                                                      | Y                                     | Y | Y                                      |

| WWDG                                         | Y                     | Y                    | Y            | Y              | -                                                                                      | -                                     | - | -                                      |

| Touch sensing                                | Y                     | -                    | -            | -              | -                                                                                      | -                                     | - | -                                      |

| Systick Timer                                | Y                     | Y                    | Y            | Y              | -                                                                                      | -                                     | - | -                                      |

| GPIOs                                        | Y                     | Y                    | Y            | Y              | Y                                                                                      | Y                                     | - | 3 Pins                                 |

| Wakeup time to<br>Run mode                   | 0 µs                  | 0.36 µs              | 3 µs         | 32 µs          |                                                                                        | < 8 µs                                |   | 50 µs                                  |

|                                              |                       |                      |              |                |                                                                                        | 5 µA (No<br>) V <sub>DD</sub> =1.8V   |   | IA (No RTC)<br>/ <sub>DD</sub> =1.8V   |

| Consumption<br>V <sub>DD</sub> =1.8V to 3.6V | Down to<br>214 µA/MHz | Down to<br>50 µA/MHz | Down to      | Down to        | 1.4 μA (with<br>RTC) V <sub>DD</sub> =1.8V<br>0.5 μA (No<br>RTC) V <sub>DD</sub> =3.0V |                                       |   | (with RTC)<br>/ <sub>DD</sub> =1.8V    |

| (Typ)                                        | (from Flash)          | (from Flash)         | 9 µA         | 4.4 µA         |                                                                                        |                                       |   | IA (No RTC)<br>/ <sub>DD</sub> =3.0V   |

|                                              |                       |                      |              |                |                                                                                        | δ μΑ (with<br>) V <sub>DD</sub> =3.0V |   | 3 µA (with<br>≎) V <sub>DD</sub> =3.0V |

| Table 5. Working mode-dependent functionalities | (from Run/active down to standby) (continued) |

|-------------------------------------------------|-----------------------------------------------|

|                                                 |                                               |

1. The startup on communication line wakes the CPU which was made possible by an EXTI, this induces a delay before entering run mode.

# 3.2 ARM<sup>®</sup> Cortex<sup>®</sup>-M3 core with MPU

The ARM<sup>®</sup> Cortex<sup>®</sup>-M3 processor is the industry leading processor for embedded systems. It has been developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced system response to interrupts.

The ARM<sup>®</sup> Cortex<sup>®</sup>-M3 32-bit RISC processor features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

The memory protection unit (MPU) improves system reliability by defining the memory attributes (such as read/write access permissions) for different memory regions. It provides up to eight different regions and an optional predefined background region.

Owing to its embedded ARM core, the STM32L151x6/8/B and STM32L152x6/8/B devices are compatible with all ARM tools and software.

Five BOR thresholds are available through option bytes, starting from 1.8 V to 3 V. To reduce the power consumption in Stop mode, it is possible to automatically switch off the internal reference voltage ( $V_{REFINT}$ ) in Stop mode. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for any external reset circuit.

Note: The start-up time at power-on is typically 3.3 ms when BOR is active at power-up, the startup time at power-on can be decreased down to 1 ms typically for devices with BOR inactive at power-up.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. This PVD offers 7 different levels between 1.85 V and 3.05 V, chosen by software, with a step around 200 mV. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

# 3.3.3 Voltage regulator

The regulator has three operation modes: main (MR), low power (LPR) and power down.

- MR is used in Run mode (nominal regulation)

- LPR is used in the Low-power run, Low-power sleep and Stop modes

- Power down is used in Standby mode. The regulator output is high impedance, the kernel circuitry is powered down, inducing zero consumption but the contents of the registers and RAM are lost are lost except for the standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE crystal 32K osc, RCC\_CSR).

# 3.3.4 Boot modes

At startup, boot pins are used to select one of three boot options:

- Boot from Flash memory

- Boot from System Memory

- Boot from embedded RAM

The boot loader is located in System Memory. It is used to reprogram the Flash memory by using USART1 or USART2. See STM32<sup>™</sup> microcontroller system memory boot mode AN2606 for details.

|         |        | Pins    |          |                    |                   |                         |               |                                                  | Pins functions                               |                         |

|---------|--------|---------|----------|--------------------|-------------------|-------------------------|---------------|--------------------------------------------------|----------------------------------------------|-------------------------|

| LQFP100 | LQFP64 | TFBGA64 | UFBGA100 | LQFP48 or UFQFPN48 | Pin name          | Pin type <sup>(1)</sup> | I/O structure | Main<br>function <sup>(2)</sup><br>(after reset) | Alternate functions                          | Additional<br>functions |

| 71      | 45     | B8      | A12      | 33                 | PA12              | I/O                     | FT            | PA12                                             | USART1_RTS/<br>SPI1_MOSI                     | USB_DP                  |

| 72      | 46     | A8      | A11      | 34                 | PA13              | I/O                     | FT            | JTMS-<br>SWDIO                                   | JTMS-SWDIO                                   | -                       |

| 73      | -      | -       | C11      | -                  | PH2               | I/O                     | FT            | PH2                                              | -                                            | -                       |

| 74      | 47     | D5      | F11      | 35                 | V <sub>SS_2</sub> | S                       | -             | V <sub>SS_2</sub>                                | -                                            | -                       |

| 75      | 48     | E5      | G11      | 36                 | V <sub>DD_2</sub> | S                       | -             | V <sub>DD_2</sub>                                | -                                            | -                       |

| 76      | 49     | A7      | A10      | 37                 | PA14              | I/O                     | FT            | JTCK<br>-SWCLK                                   | JTCK-SWCLK                                   | -                       |

| 77      | 50     | A6      | A9       | 38                 | PA15              | I/O                     | FT            | JTDI                                             | TIM2_CH1_ETR/PA15/<br>SPI1_NSS/<br>LCD_SEG17 | -                       |

| 78      | 51     | B7      | B11      | -                  | PC10              | I/O                     | FT            | PC10                                             | USART3_TX/LCD_SEG28<br>/LCD_SEG40/LCD_COM4   | -                       |

| 79      | 52     | B6      | C10      | -                  | PC11              | I/O                     | FT            | PC11                                             | USART3_RX/LCD_SEG29<br>/LCD_SEG41/LCD_COM5   | -                       |

| 80      | 53     | C5      | B10      | -                  | PC12              | I/O                     | FT            | PC12                                             | USART3_CK/LCD_SEG30<br>/LCD_SEG42/LCD_COM6   | -                       |

| 81      | -      | -       | C9       | -                  | PD0               | I/O                     | FT            | PD0                                              | SPI2_NSS/TIM9_CH1                            | -                       |

| 82      | -      | -       | B9       | -                  | PD1               | I/O                     | FT            | PD1                                              | SPI2_SCK                                     | -                       |

| 83      | 54     | B5      | C8       | -                  | PD2               | I/O                     | FT            | PD2                                              | TIM3_ETR/LCD_SEG31/<br>LCD_SEG43/LCD_COM7    | -                       |

| 84      | -      | -       | B8       | -                  | PD3               | I/O                     | FT            | PD3                                              | USART2_CTS/<br>SPI2_MISO                     | -                       |

| 85      | -      | -       | B7       | -                  | PD4               | I/O                     | FT            | PD4                                              | USART2_RTS/<br>SPI2_MOSI                     | -                       |

| 86      | -      | -       | A6       | -                  | PD5               | I/O                     | FT            | PD5                                              | USART2_TX                                    | -                       |

| 87      | -      | -       | B6       | -                  | PD6               | I/O                     | FT            | PD6                                              | USART2_RX                                    | -                       |

| 88      | -      | -       | A5       | -                  | PD7               | I/O                     | FT            | PD7                                              | USART2_CK/TIM9_CH2                           | -                       |

| 89      | 55     | A5      | A8       | 39                 | PB3               | I/O                     | FT            | JTDO                                             | TIM2_CH2/PB3/<br>SPI1_SCK/LCD_SEG7/<br>JTDO  | COMP2_INM               |

# Table 8. STM32L151x6/8/B and STM32L152x6/8/B pin definitions (continued)

44/133

| Do  |

|-----|

| СГ  |

| 017 |

| 659 |

| 9 F |

| ۲ev |

| 12  |

|           |                    |          |          |            |               | Digital al | ternate fu | nction number |       |       |                           |        |        |          |                      |

|-----------|--------------------|----------|----------|------------|---------------|------------|------------|---------------|-------|-------|---------------------------|--------|--------|----------|----------------------|

| <b>D</b>  | AFIO0              | AFIO1    | AFIO2    | AFIO3      | AFIO4         | AFIO5      | AFOI6      | AFIO7         | AFIO8 | AFIO9 | AFIO11                    | AFIO12 | AFIO13 | AFIO14   | AFIO15               |

| Port name | Alternate function |          |          |            |               |            |            |               |       |       |                           |        |        |          |                      |

|           | SYSTEM             | TIM2     | TIM3/4   | TIM9/10/11 | I2C1/2        | SPI1/2     | N/A        | USART1/2/3    | N/A   | N/A   | LCD                       | N/A    | N/A    | RI       | SYSTEM               |

| PB5       | -                  | -        | TIM3_CH2 | -          | I2C1_<br>SMBA | SPI1_MOSI  | -          | -             | -     | -     | [SEG9]                    | -      | -      | -        | EVENTOU <sup>1</sup> |

| PB6       | -                  | -        | TIM4_CH1 | -          | I2C1_SCL      | -          | -          | USART1_TX     | -     | -     | -                         | -      | -      | -        | EVENTOU              |

| PB7       | -                  | -        | TIM4_CH2 | -          | I2C1_SDA      | -          | -          | USART1_RX     | -     | -     | -                         | -      | -      | -        | EVENTOU"             |

| PB8       | -                  | -        | TIM4_CH3 | TIM10_CH1* | I2C1_SCL      | -          | -          | -             | -     | -     | SEG16                     | -      | -      | -        | EVENTOU"             |

| PB9       | -                  | -        | TIM4_CH4 | TIM11_CH1* | I2C1_SDA      | -          | -          | -             | -     | -     | [COM3]                    | -      | -      | -        | EVENTOU"             |

| PB10      | -                  | TIM2_CH3 | -        | -          | I2C2_SCL      | -          | -          | USART3_TX     | -     | -     | SEG10                     | -      | -      | -        | EVENTOU              |

| PB11      | -                  | TIM2_CH4 | -        | -          | I2C2_SDA      | -          | -          | USART3_RX     | -     | -     | SEG11                     | -      | -      | -        | EVENTOU              |

| PB12      | -                  | -        | -        | TIM10_CH1  | I2C2_<br>SMBA | SPI2_NSS   | -          | USART3_CK     | -     | -     | SEG12                     | -      | -      | -        | EVENTOU              |

| PB13      | -                  | -        | -        | TIM9_CH1   | -             | SPI2_SCK   | -          | USART3_CTS    | -     | -     | SEG13                     | -      | -      | -        | EVENTOU              |

| PB14      | -                  | -        | -        | TIM9_CH2   | -             | SPI2_MISO  | -          | USART3_RTS    | -     | -     | SEG14                     | -      | -      | -        | EVENTOU              |

| PB15      | -                  | -        | -        | TIM11_CH1  | -             | SPI2_MOSI  | -          | -             | -     | -     | SEG15                     | -      | -      | -        | EVENTOU              |

| PC0       | -                  | -        | -        | -          | -             | -          | -          | -             | -     | -     | SEG18                     | -      | -      | TIMx_IC1 | EVENTOU              |

| PC1       | -                  | -        | -        | -          | -             | -          | -          | -             | -     | -     | SEG19                     | -      | -      | TIMx_IC2 | EVENTOU              |

| PC2       | -                  | -        | -        | -          | -             | -          | -          | -             | -     | -     | SEG20                     | -      | -      | TIMx_IC3 | EVENTOU              |

| PC3       | -                  | -        | -        | -          | -             | -          | -          | -             | -     | -     | SEG21                     | -      | -      | TIMx_IC4 | EVENTOU              |

| PC4       | -                  | -        | -        | -          | -             | -          | -          | -             | -     | -     | SEG22                     | -      | -      | TIMx_IC1 | EVENTOU              |

| PC5       | -                  | -        | -        | -          | -             | -          | -          | -             | -     | -     | SEG23                     | -      | -      | TIMx_IC2 | EVENTOU              |

| PC6       | -                  | -        | TIM3_CH1 | -          | -             | -          | -          | -             | -     | -     | SEG24                     | -      | -      | TIMx_IC3 | EVENTOU              |

| PC7       | -                  | -        | TIM3_CH2 | -          | -             | -          | -          | -             | -     | -     | SEG25                     | -      | -      | TIMx_IC4 | EVENTOU              |

| PC8       | -                  | -        | TIM3_CH3 | -          | -             | -          | -          | -             | -     | -     | SEG26                     | -      | -      | TIMx_IC1 | EVENTOU"             |

| PC9       | -                  | -        | TIM3_CH4 | -          | -             | -          | -          | -             | -     | -     | SEG27                     | -      | -      | TIMx_IC2 | EVENTOU              |

| PC10      | -                  | -        | -        | -          | -             | -          | -          | USART3_TX     | -     | -     | COM4 /<br>SEG28/<br>SEG40 | -      | -      | TIMx_IC3 | EVENTOU              |

Pin descriptions

# 6.3.2 Embedded reset and power control block characteristics

The parameters given in the following table are derived from the tests performed under the ambient temperature condition summarized in the following table.

| Symbol                               | Parameter                      | Conditions                                          | Min  | Тур  | Мах  | Unit |  |

|--------------------------------------|--------------------------------|-----------------------------------------------------|------|------|------|------|--|

|                                      | V rice time rate               | BOR detector enabled                                | 0    | -    | ~    |      |  |

| t <sub>VDD</sub> <sup>(1)</sup>      | V <sub>DD</sub> rise time rate | BOR detector disabled                               | 0    | -    | 1000 | μs/V |  |

| <sup>I</sup> VDD <sup>(1)</sup>      | ) ( fall time rate             | BOR detector enabled                                | 20   | -    | ~    | µs/v |  |

|                                      | V <sub>DD</sub> fall time rate | BOR detector disabled                               | 0    | -    | 1000 |      |  |

| <b>T</b> (1)                         | Deast temperization            | V <sub>DD</sub> rising, BOR enabled                 | -    | 2    | 3.3  |      |  |

| T <sub>RSTTEMPO</sub> <sup>(1)</sup> | Reset temporization            | V <sub>DD</sub> rising, BOR disabled <sup>(2)</sup> | 0.4  | 0.7  | 1.6  | ms   |  |

| V                                    | Power on/power down reset      | Falling edge                                        | 1    | 1.5  | 1.65 | v    |  |

| V <sub>POR/PDR</sub>                 | threshold                      | Rising edge                                         | 1.3  | 1.5  | 1.65 |      |  |

| N/                                   |                                | Falling edge                                        | 1.67 | 1.7  | 1.74 |      |  |

| V <sub>BOR0</sub>                    | Brown-out reset threshold 0    | Rising edge                                         | 1.69 | 1.76 | 1.8  |      |  |

| V                                    | Brown-out reset threshold 1    | Falling edge                                        | 1.87 | 1.93 | 1.97 |      |  |

| V <sub>BOR1</sub>                    | Brown-out reset threshold T    | Rising edge                                         | 1.96 | 2.03 | 2.07 |      |  |

| M                                    | Brown-out reset threshold 2    | Falling edge                                        | 2.22 | 2.30 | 2.35 | v    |  |

| V <sub>BOR2</sub>                    |                                | Rising edge                                         | 2.31 | 2.41 | 2.44 | v    |  |

| V                                    | Drown out react threshold 2    | Falling edge                                        | 2.45 | 2.55 | 2.60 |      |  |

| V <sub>BOR3</sub>                    | Brown-out reset threshold 3    | Rising edge                                         | 2.54 | 2.66 | 2.7  |      |  |

| M                                    | Brown-out reset threshold 4    | Falling edge                                        | 2.68 | 2.8  | 2.85 |      |  |

| V <sub>BOR4</sub>                    |                                | Rising edge                                         | 2.78 | 2.9  | 2.95 |      |  |

Table 14. Embedded reset and power control block characteristics

# 6.3.5 Wakeup time from Low power mode

The wakeup times given in the following table are measured with the MSI RC oscillator. The clock source used to wake up the device depends on the current operating mode:

- Sleep mode: the clock source is the clock that was set before entering Sleep mode

- Stop mode: the clock source is the MSI oscillator in the range configured before entering Stop mode

- Standby mode: the clock source is the MSI oscillator running at 2.1 MHz

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 13*.

| Symbol               | Parameter                                    | Conditions                                                              | Тур  | Max <sup>(1)</sup> | Unit |

|----------------------|----------------------------------------------|-------------------------------------------------------------------------|------|--------------------|------|

| t <sub>WUSLEEP</sub> | Wakeup from Sleep mode                       | f <sub>HCLK</sub> = 32 MHz                                              | 0.36 | -                  |      |

| t                    | Wakeup from Low power sleep mode             | f <sub>HCLK</sub> = 262 kHz<br>Flash enabled                            | 32   | -                  |      |

| twusleep_lp          | f <sub>HCLK</sub> = 262 kHz                  | f <sub>HCLK</sub> = 262 kHz<br>Flash switched OFF                       | 34   | -                  |      |

|                      | Wakeup from Stop mode, regulator in Run mode | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz                          | 8.2  | -                  |      |

|                      |                                              | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage Range 1 and 2 | 8.2  | 9.3                |      |

|                      |                                              | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage Range 3       | 7.8  | 11.2               | μs   |

| t <sub>WUSTOP</sub>  | Wakeup from Stop mode,                       | • · · · · · · · · · · · · · · · · · · ·                                 |      |                    |      |

|                      | regulator in low power mode                  | f <sub>HCLK</sub> = f <sub>MSI</sub> = 1.05 MHz                         | 15.5 | 20                 |      |

|                      |                                              | f <sub>HCLK</sub> = f <sub>MSI</sub> = 524 kHz                          | 29   | 35                 |      |

|                      |                                              | f <sub>HCLK</sub> = f <sub>MSI</sub> = 262 kHz                          | 53   | 63                 |      |

|                      |                                              | f <sub>HCLK</sub> = f <sub>MSI</sub> = 131 kHz                          | 105  | 118                |      |

|                      |                                              | f <sub>HCLK</sub> = MSI = 65 kHz                                        | 210  | 237                |      |

| t                    | Wakeup from Standby<br>mode<br>FWU bit = 1   | f <sub>HCLK</sub> = MSI = 2.1 MHz                                       | 50   | 103                |      |

| <sup>t</sup> wustdby | Wakeup from Standby<br>mode<br>FWU bit = 0   | f <sub>HCLK</sub> = MSI = 2.1 MHz                                       | 2.5  | 3.2                | ms   |

Table 25. Low-power mode wakeup timings

1. Guaranteed by characterization results, unless otherwise specified

| Symbol               | Parameter                                                                                              | Conditions                                                                    | Min | Тур | Мах                                | Unit     |

|----------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----|-----|------------------------------------|----------|

| f <sub>OSC_IN</sub>  | Oscillator frequency                                                                                   | -                                                                             | 1   |     | 24                                 | MHz      |

| R <sub>F</sub>       | Feedback resistor                                                                                      | -                                                                             |     | 200 | -                                  | kΩ       |

| С                    | Recommended load<br>capacitance versus<br>equivalent serial resistance<br>of the crystal $(R_S)^{(3)}$ | R <sub>S</sub> = 30 Ω                                                         | -   | 20  | -                                  | pF       |

| I <sub>HSE</sub>     | HSE driving current                                                                                    | V <sub>DD</sub> = 3.3 V, V <sub>IN</sub> = V <sub>SS</sub><br>with 30 pF load | -   | -   | 3                                  | mA       |

|                      | HSE oscillator power                                                                                   | C = 20 pF<br>f <sub>OSC</sub> = 16 MHz                                        | -   | -   | 2.5 (startup)<br>0.7 (stabilized)  | mA       |

| IDD(HSE)             | consumption                                                                                            | C = 10 pF<br>f <sub>OSC</sub> = 16 MHz                                        | -   | -   | 2.5 (startup)<br>0.46 (stabilized) | mA       |

| 9 <sub>m</sub>       | Oscillator transconductance                                                                            | Startup                                                                       | 3.5 | -   | -                                  | mA<br>/V |

| t <sub>SU(HSE)</sub> | Startup time                                                                                           | $V_{DD}$ is stabilized                                                        | -   | 1   | -                                  | ms       |

| Table 28. | HSE | oscillator | characteristics <sup>(1)(2)</sup> |

|-----------|-----|------------|-----------------------------------|

|-----------|-----|------------|-----------------------------------|

1. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

2. Guaranteed by characterization results.

3. The relatively low value of the RF resistor offers a good protection against issues resulting from use in a humid environment, due to the induced leakage and the bias condition change. However, it is recommended to take this point into account if the MCU is used in tough humidity conditions.

t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

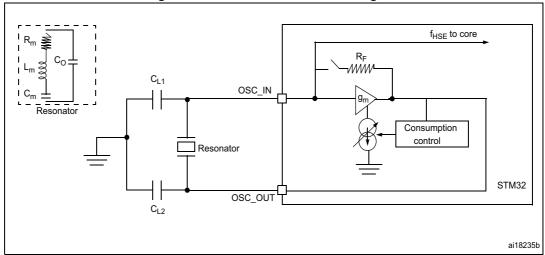

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 17*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ . Refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website *www.st.com*.

Figure 17. HSE oscillator circuit diagram

1. R<sub>EXT</sub> value depends on the crystal characteristics.

### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 29*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                                                                                     | Conditions                            | Min | Тур    | Мах | Unit |

|-------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------|-----|--------|-----|------|

| f <sub>LSE</sub>                    | Low speed external oscillator<br>frequency                                                    | -                                     | -   | 32.768 | -   | kHz  |

| R <sub>F</sub>                      | Feedback resistor                                                                             | -                                     | -   | 1.2    | -   | MΩ   |

| C <sup>(2)</sup>                    | Recommended load capacitance versus equivalent serial resistance of the crystal $(R_S)^{(3)}$ | R <sub>S</sub> = 30 kΩ                | -   | 8      | -   | pF   |

| I <sub>LSE</sub>                    | LSE driving current                                                                           | $V_{DD}$ = 3.3 V, $V_{IN}$ = $V_{SS}$ | -   | -      | 1.1 | μA   |

|                                     |                                                                                               | V <sub>DD</sub> = 1.8 V               | -   | 450    | -   |      |

| I <sub>DD (LSE)</sub>               | LSE oscillator current consumption                                                            | V <sub>DD</sub> = 3.0 V               | -   | 600    | -   | nA   |

|                                     |                                                                                               | V <sub>DD</sub> = 3.6V                | -   | 750    | -   |      |

| 9 <sub>m</sub>                      | Oscillator transconductance                                                                   | -                                     | 3   | -      | -   | µA/V |

| t <sub>SU(LSE)</sub> <sup>(4)</sup> | Startup time                                                                                  | V <sub>DD</sub> is stabilized         | -   | 1      | -   | s    |

| Table 29. LSE oscillator characteristics | s (f <sub>LSE</sub> = 32.768 kHz) <sup>(1)</sup> |

|------------------------------------------|--------------------------------------------------|

|------------------------------------------|--------------------------------------------------|

1. Guaranteed by characterization results.

2. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

The oscillator selection can be optimized in terms of supply current using an high quality resonator with small R<sub>S</sub> value for example MSIV-TIN32.768kHz. Refer to crystal manufacturer for more details.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol           |            | Conditions                                                                              |                             | Max vs                      |                              |                              |      |

|------------------|------------|-----------------------------------------------------------------------------------------|-----------------------------|-----------------------------|------------------------------|------------------------------|------|

|                  | Parameter  |                                                                                         | Monitored<br>frequency band | 4 MHz<br>voltage<br>Range 3 | 16 MHz<br>voltage<br>Range 2 | 32 MHz<br>voltage<br>Range 1 | Unit |

|                  |            | $V_{DD} = 3.3 V,$<br>$T_A = 25 °C,$<br>LQFP100 package<br>compliant with IEC<br>61967-2 | 0.1 to 30 MHz               | 3                           | -6                           | -5                           |      |

| 6                | Peak level |                                                                                         | 30 to 130 MHz               | 18                          | 4                            | -7                           | dBµV |

| S <sub>EMI</sub> | Feaklevel  |                                                                                         | 130 MHz to 1GHz             | 15                          | 5                            | -7                           |      |

|                  |            |                                                                                         | SAE EMI Level               | 2.5                         | 2                            | 1                            | -    |

#### Table 38. EMI characteristics

# 6.3.11 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

## Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114/C101 standard.

| Symbol                | Ratings                                               | Conditions                                         | Packages | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|----------------------------------------------------|----------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)    | $T_A = +25$ °C, conforming to JESD22-A114          | All      | 2     | 2000                            | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model) | T <sub>A</sub> = +25 °C, conforming to JESD22-C101 | All      | 111   | 500                             | v    |

### Table 39. ESD absolute maximum ratings

1. Guaranteed by characterization results.

### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latch-up standard.

| Table 40. | Electrical | sensitivities  |

|-----------|------------|----------------|

|           | LICCUITCUI | 30113111411103 |

| Symbol | Parameter             | Conditions                                    | Class      |

|--------|-----------------------|-----------------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +105 \text{ °C conforming to JESD78A}$ | II level A |

# 6.3.12 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error, out of spec current injection on adjacent pins or other functional failure (for example reset, oscillator frequency deviation, LCD levels, etc.).

The test results are given in Table 41.

#### Table 41. I/O current injection susceptibility

|                  |                                                | Functional s       |                    |      |

|------------------|------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                    | Negative injection | Positive injection | Unit |

|                  | Injected current on all 5 V tolerant (FT) pins | -5                 | +0                 | mA   |

| I <sub>INJ</sub> | Injected current on any other pin              | r pin -5           |                    | IIIA |

*Note:* It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 20$  mA (with the non-standard V<sub>OL</sub>/V<sub>OH</sub> specifications given in *Table 43*.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 6.2*:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating I<sub>VDDΣ</sub> (see *Table 11*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating I<sub>VSSΣ</sub> (see *Table 11*).

# **Output voltage levels**

Unless otherwise specified, the parameters given in *Table 43* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 13*. All I/Os are CMOS and TTL compliant.

| Symbol                            | Parameter                                | Conditions                       | Min                   | Max  | Unit |

|-----------------------------------|------------------------------------------|----------------------------------|-----------------------|------|------|

| V <sub>OL</sub> <sup>(1)(2)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = 8 mA           | -                     | 0.4  |      |

| V <sub>OH</sub> <sup>(3)(2)</sup> | Output high level voltage for an I/O pin | 2.7 V < V <sub>DD</sub> < 3.6 V  | 2.4                   | -    |      |

| V <sub>OL</sub> <sup>(1)(4)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = 4 mA           | -                     | 0.45 | v    |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin | 1.65 V < V <sub>DD</sub> < 2.7 V | V <sub>DD</sub> -0.45 | -    | v    |

| V <sub>OL</sub> <sup>(1)(4)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = 20 mA          | -                     | 1.3  |      |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin | 2.7 V < V <sub>DD</sub> < 3.6 V  | V <sub>DD</sub> -1.3  | -    |      |

#### Table 43. Output voltage characteristics

1. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 11* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. Tested in production.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in *Table 11* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

4. Guaranteed by characterization results.

# 6.3.16 Communication interfaces

# I<sup>2</sup>C interface characteristics

The STM32L151x6/8/B and STM32L152x6/8/B product line  $I^2C$  interface meets the requirements of the standard  $I^2C$  communication protocol with the following restrictions: SDA and SCL are not "true" open-drain I/O pins. When configured as open-drain, the PMOS connected between the I/O pin and V<sub>DD</sub> is disabled, but is still present.

The I<sup>2</sup>C characteristics are described in *Table 47*. Refer also to *Section 6.3.12: I/O current injection characteristics* for more details on the input/output alternate function characteristics (SDA and SCL).

| Symbol                                     | Parameter                               | Standard r | node l <sup>2</sup> C <sup>(1)</sup> | Fast mode I <sup>2</sup> C <sup>(1)(2)</sup> |                    | Unit |  |

|--------------------------------------------|-----------------------------------------|------------|--------------------------------------|----------------------------------------------|--------------------|------|--|

| Symbol                                     | Falameter                               | Min        | Max                                  | Min                                          | Max                | Unit |  |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                      | 4.7        | -                                    | 1.3                                          | -                  | 116  |  |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                     | 4.0        | -                                    | 0.6                                          | -                  | μs   |  |

| t <sub>su(SDA)</sub>                       | SDA setup time                          | 250        | -                                    | 100                                          | -                  |      |  |

| t <sub>h(SDA)</sub>                        | SDA data hold time                      | 0          | -                                    | 0                                            | 900 <sup>(3)</sup> |      |  |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                   | -          | 1000                                 | 20 + 0.1C <sub>b</sub>                       | 300                | ns   |  |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                   | -          | 300                                  | -                                            | 300                |      |  |

| t <sub>h(STA)</sub>                        | Start condition hold time               | 4.0        | -                                    | 0.6                                          | -                  |      |  |

| t <sub>su(STA)</sub>                       | Repeated Start condition setup time     | 4.7        | -                                    | 0.6                                          | -                  | μs   |  |

| t <sub>su(STO)</sub>                       | Stop condition setup time               | 4.0        | -                                    | 0.6                                          | -                  | μs   |  |

| t <sub>w(STO:STA)</sub>                    | Stop to Start condition time (bus free) | 4.7        | -                                    | 1.3                                          | -                  | μs   |  |

| C <sub>b</sub>                             | Capacitive load for each bus line       | -          | 400                                  | -                                            | 400                | pF   |  |

| Table 47. I <sup>2</sup> C | characteristics |

|----------------------------|-----------------|

|----------------------------|-----------------|

1. Guaranteed by design.

f<sub>PCLK1</sub> must be at least 2 MHz to achieve standard mode I<sup>2</sup>C frequencies. It must be at least 4 MHz to achieve fast mode I<sup>2</sup>C frequencies. It must be a multiple of 10 MHz to reach the 400 kHz maximum I<sup>2</sup>C fast mode clock.

3. The maximum Data hold time has only to be met if the interface does not stretch the low period of SCL signal.

### **SPI characteristics**

Unless otherwise specified, the parameters given in the following table are derived from tests performed under ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 13*.

Refer to *Section 6.3.12: I/O current injection characteristics* for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                                                                     | Parameter                        | Conditions                 | Min                       | Max <sup>(2)</sup>        | Unit |  |

|----------------------------------------------------------------------------|----------------------------------|----------------------------|---------------------------|---------------------------|------|--|

| _                                                                          |                                  | Master mode                | -                         | 16                        |      |  |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>                                  | SPI clock frequency              | Slave mode                 | -                         | 16                        | MHz  |  |

|                                                                            |                                  | Slave transmitter          | -                         | 12 <sup>(3)</sup>         |      |  |

| t <sub>r(SCK)</sub> <sup>(2)</sup><br>t <sub>f(SCK)</sub> <sup>(2)</sup>   | SPI clock rise and fall time     | Capacitive load: C = 30 pF | -                         | 6                         | ns   |  |

| DuCy(SCK)                                                                  | SPI slave input clock duty cycle | Slave mode                 | 30                        | 70                        | %    |  |

| t <sub>su(NSS)</sub>                                                       | NSS setup time                   | Slave mode                 | 4t <sub>HCLK</sub>        | -                         |      |  |

| t <sub>h(NSS)</sub>                                                        | NSS hold time                    | Slave mode                 | 2t <sub>HCLK</sub>        | -                         |      |  |

| t <sub>w(SCKH)</sub> <sup>(2)</sup><br>t <sub>w(SCKL)</sub> <sup>(2)</sup> | SCK high and low time            | Master mode                | t <sub>SCK</sub> /2–<br>5 | t <sub>SCK</sub> /2+<br>3 |      |  |

| t <sub>su(MI)</sub> <sup>(2)</sup>                                         | Data input setup time            | Master mode                | 5                         | -                         |      |  |

| t <sub>su(SI)</sub> <sup>(2)</sup>                                         | Data input setup time            | Slave mode                 | 6                         | -                         |      |  |

| t <sub>h(MI)</sub> <sup>(2)</sup>                                          | Data input hold time             | Master mode                | 5                         | -                         | ns   |  |

| t <sub>h(SI)</sub> <sup>(2)</sup>                                          |                                  | Slave mode                 | 5                         | -                         |      |  |

| t <sub>a(SO)</sub> <sup>(4)</sup>                                          | Data output access time          | Slave mode                 | 0                         | 3t <sub>HCLK</sub>        |      |  |

| t <sub>v(SO)</sub> (2)                                                     | Data output valid time           | Slave mode                 | -                         | 33                        |      |  |

| t <sub>v(MO)</sub> <sup>(2)</sup>                                          | Data output valid time           | Master mode                | -                         | 6.5                       |      |  |

| t <sub>h(SO)</sub> <sup>(2)</sup>                                          | Data output hold time            | Slave mode                 | 17                        | -                         |      |  |

| t <sub>h(MO)</sub> <sup>(2)</sup>                                          | Data output hold time            | Master mode                | 0.5                       | -                         |      |  |

| Table 49. SPI characteristics | ble 49. SPI characteristics | (1) |

|-------------------------------|-----------------------------|-----|

|-------------------------------|-----------------------------|-----|

1. The characteristics above are given for voltage Range 1.

2. Guaranteed by characterization results.

3. The maximum SPI clock frequency in slave transmitter mode is given for an SPI slave input clock duty cycle (DuCy(SCK)) ranging between 40 to 60%.

4. Min time is for the minimum time to drive the output and max time is for the maximum time to validate the data.

# Table 56. Maximum source impedance $R_{AIN} \max^{(1)}$

|            | R <sub>AIN</sub> max (kOhm)      |                                  |                                  |                                  |                                                         |  |

|------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|---------------------------------------------------------|--|

| Ts<br>(µs) | Multiplexed channels             |                                  | Direct channels                  |                                  | Ts (cycles)<br>f <sub>ADC</sub> = 16 MHz <sup>(2)</sup> |  |

|            | 2.4 V < V <sub>DDA</sub> < 3.6 V | 1.8 V < V <sub>DDA</sub> < 2.4 V | 2.4 V < V <sub>DDA</sub> < 3.3 V | 1.8 V < V <sub>DDA</sub> < 2.4 V | ADC                                                     |  |

| 0.25       | Not allowed                      | Not allowed                      | 0.7                              | Not allowed                      | 4                                                       |  |

| 0.5625     | 0.8                              | Not allowed                      | 2.0                              | 1.0                              | 9                                                       |  |

| 1          | 2.0                              | 0.8                              | 4.0                              | 3.0                              | 16                                                      |  |

| 1.5        | 3.0                              | 1.8                              | 6.0                              | 4.5                              | 24                                                      |  |

| 3          | 6.8                              | 4.0                              | 15.0                             | 10.0                             | 48                                                      |  |

| 6          | 15.0                             | 10.0                             | 30.0                             | 20.0                             | 96                                                      |  |

| 12         | 32.0                             | 25.0                             | 50.0                             | 40.0                             | 192                                                     |  |

| 24         | 50.0                             | 50.0                             | 50.0                             | 50.0                             | 384                                                     |  |

1. Guaranteed by design.

2. Number of samples calculated for  $f_{ADC}$  = 16 MHz. For  $f_{ADC}$  = 8 and 4 MHz the number of sampling cycles can be reduced with respect to the minimum sampling time Ts (us).

# **General PCB design guidelines**

Power supply decoupling should be performed as shown in The 10 nF capacitors should be ceramic (good quality). They should be placed as close as possible to the chip.

| Symbol              | Parameter                                     | Conditions                                                                                                                                | Min | Тур | Max <sup>(1)</sup> | Unit       |

|---------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--------------------|------------|

| V <sub>DDA</sub>    | Analog supply voltage                         | -                                                                                                                                         | 1.  | -   | 3.6                | V          |

| V <sub>IN</sub>     | Comparator 2 input voltage range              | -                                                                                                                                         | 0   | -   | V <sub>DDA</sub>   | V          |

| t <sub>start</sub>  | Comparator startup time                       | Fast mode                                                                                                                                 | -   | 15  | 20                 |            |

|                     |                                               | Slow mode                                                                                                                                 | -   | 20  | 25                 |            |

| t <sub>d slow</sub> | Propagation delay <sup>(2)</sup> in slow mode | 1. V ≤V <sub>DDA</sub> ≤2.7 V                                                                                                             | -   | 1.8 | 3.5                | μs         |

|                     |                                               | 2.7 V ≤V <sub>DDA</sub> ≤3.6 V                                                                                                            | -   | 2.5 | 6                  |            |

| 4                   | Propagation delay <sup>(2)</sup> in fast mode | 1. V ⊴V <sub>DDA</sub> ⊴2.7 V                                                                                                             | -   | 0.8 | 2                  |            |

| t <sub>d fast</sub> |                                               | 2.7 V ≤V <sub>DDA</sub> ≤3.6 V                                                                                                            | -   | 1.2 | 4                  |            |

| V <sub>offset</sub> | Comparator offset error                       | -                                                                                                                                         | -   | ±4  | ±20                | mV         |

| dThreshold/<br>dt   | Threshold voltage temperature coefficient     | $V_{DDA} = 3.3V$<br>$T_{A} = 0 \text{ to } 50 \circ C$<br>$V = V_{REFINT},$<br>$3/4 V_{REFINT},$<br>$1/2 V_{REFINT},$<br>$1/4 V_{REFINT}$ | -   | 15  | 100                | ppm<br>/°C |

|                     | Current consumption <sup>(3)</sup>            | Fast mode                                                                                                                                 | -   | 3.5 | 5                  |            |

| I <sub>COMP2</sub>  |                                               | Slow mode                                                                                                                                 | -   | 0.5 | 2                  | μA         |

| Table 61. | Comparator | 2 characteristics |

|-----------|------------|-------------------|

|-----------|------------|-------------------|

1. Guaranteed by characterization results.

2. The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

3. Comparator consumption only. Internal reference voltage (necessary for comparator operation) is not included.

# 7.7 Thermal characteristics

The maximum chip-junction temperature,  $T_J$  max, in degrees Celsius, may be calculated using the following equation:

$T_J \max = T_A \max + (P_D \max \times \Theta_{JA})$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in ° C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

P<sub>I/O</sub> max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I}/\mathsf{O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

| Symbol          | Parameter                                                                  | Value | Unit |  |

|-----------------|----------------------------------------------------------------------------|-------|------|--|

| Θ <sub>JA</sub> | Thermal resistance junction-ambient<br>BGA100 - 7 x 7 mm                   | 59    |      |  |

|                 | Thermal resistance junction-ambient<br>LQFP100 - 14 x 14 mm / 0.5 mm pitch | 46    |      |  |

|                 | <b>Thermal resistance junction-ambient</b><br>TFBGA64 - 5 x 5 mm           | 65    | °C/W |  |

|                 | Thermal resistance junction-ambient<br>LQFP64 - 10 x 10 mm / 0.5 mm pitch  | 45    | C/w  |  |

|                 | Thermal resistance junction-ambient<br>LQFP48 - 7 x 7 mm / 0.5 mm pitch    | 55    |      |  |

|                 | Thermal resistance junction-ambient<br>UFQFPN48 - 7 x 7 mm / 0.5 mm pitch  | 16    |      |  |

Table 71. Thermal characteristics