Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                              |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                         |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT |

| Number of I/O              | 37                                                                           |

| Program Memory Size        | 32KB (32K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 4K x 8                                                                       |

| RAM Size                   | 10K × 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                        |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 48-UFQFN Exposed Pad                                                         |

| Supplier Device Package    | 48-UFQFPN (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l152c6u6        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **3** Functional overview

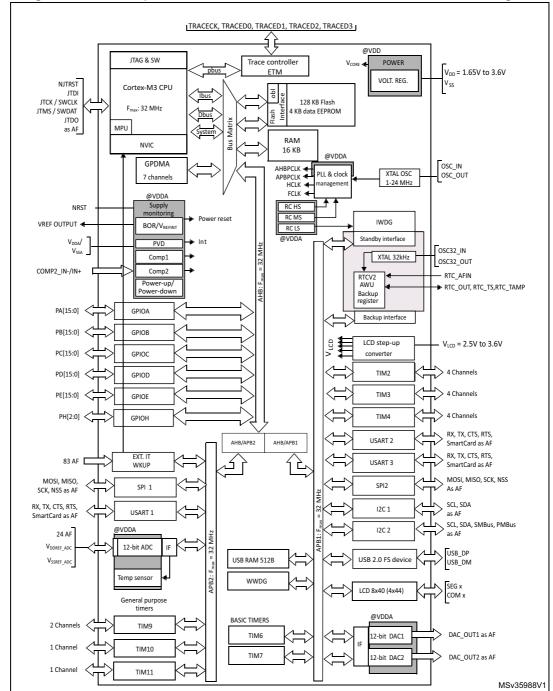

Figure 1 shows the block diagram.

#### Figure 1. Ultra-low-power STM32L151x6/8/B and STM32L152x6/8/B block diagram

1. AF = alternate function on I/O port pin.

#### Nested vectored interrupt controller (NVIC)

The ultra-low-power STM32L151x6/8/B and STM32L152x6/8/B devices embed a nested vectored interrupt controller able to handle up to 45 maskable interrupt channels (not including the 16 interrupt lines of Cortex<sup>®</sup>-M3) and 16 priority levels.

- Closely coupled NVIC gives low-latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of *late arriving*, higher-priority interrupts

- Support for tail-chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimal interrupt latency.

## 3.3 Reset and supply management

## 3.3.1 **Power supply schemes**

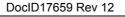

- V<sub>DD</sub> = 1.65 to 3.6 V: external power supply for I/Os and the internal regulator. Provided externally through V<sub>DD</sub> pins.

- $V_{SSA}$ ,  $V_{DDA}$  = 1.65 to 3.6 V: external analog power supplies for ADC, reset blocks, RCs and PLL (minimum voltage to be applied to  $V_{DDA}$  is 1.8 V when the ADC is used).  $V_{DDA}$  and  $V_{SSA}$  must be connected to  $V_{DD}$  and  $V_{SS}$ , respectively.

## 3.3.2 Power supply supervisor

The device has an integrated ZEROPOWER power-on reset (POR)/power-down reset (PDR) that can be coupled with a brownout reset (BOR) circuitry.

The device exists in two versions:

- The version with BOR activated at power-on operates between 1.8 V and 3.6 V.

- The other version without BOR operates between 1.65 V and 3.6 V.

After the  $V_{DD}$  threshold is reached (1.65 V or 1.8 V depending on the BOR which is active or not at power-on), the option byte loading process starts, either to confirm or modify default thresholds, or to disable the BOR permanently: in this case, the  $V_{DD}$  min value becomes 1.65 V (whatever the version, BOR active or not, at power-on).

When BOR is active at power-on, it ensures proper operation starting from 1.8 V whatever the power ramp-up phase before it reaches 1.8 V. When BOR is not active at power-up, the power ramp-up should guarantee that 1.65 V is reached on  $V_{DD}$  at least 1 ms after it exits the POR area.

## 3.7 Memories

The STM32L151x6/8/B and STM32L152x6/8/B devices have the following features:

- Up to 16 Kbytes of embedded RAM accessed (read/write) at CPU clock speed with 0 wait states. With the enhanced bus matrix, operating the RAM does not lead to any performance penalty during accesses to the system bus (AHB and APB buses).

- The non-volatile memory is divided into three arrays:

- 32, 64 or 128 Kbytes of embedded Flash program memory

- 4 Kbytes of data EEPROM

- Options bytes

The options bytes are used to write-protect the memory (with 4 Kbytes granularity) and/or readout-protect the whole memory with the following options:

- Level 0: no readout protection

- Level 1: memory readout protection, the Flash memory cannot be read from or written to if either debug features are connected or boot in RAM is selected

- Level 2: chip readout protection, debug features (Cortex<sup>®</sup>-M3 JTAG and serial wire) and boot in RAM selection disabled (JTAG fuse)

The whole non-volatile memory embeds the error correction code (ECC) feature.

## 3.8 DMA (direct memory access)

The flexible 7-channel, general-purpose DMA is able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The DMA controller supports circular buffer management, avoiding the generation of interrupts when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with software trigger support for each channel. Configuration is done by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals: SPI,  $I^2C$ , USART, general-purpose timers and ADC.

## 3.9 LCD (liquid crystal display)

The LCD drives up to 8 common terminals and 44 segment terminals to drive up to 320 pixels.

- Internal step-up converter to guarantee functionality and contrast control irrespective of V<sub>DD</sub>. This converter can be deactivated, in which case the V<sub>LCD</sub> pin is used to provide the voltage to the LCD

- Supports static, 1/2, 1/3, 1/4 and 1/8 duty

- Supports static, 1/2, 1/3 and 1/4 bias

- Phase inversion to reduce power consumption and EMI

- Up to 8 pixels can be programmed to blink

- Unneeded segments and common pins can be used as general I/O pins

- LCD RAM can be updated at any time owing to a double-buffer

- The LCD controller can operate in Stop mode

This dual digital Interface supports the following features:

- two DAC converters: one for each output channel

- left or right data alignment in 12-bit mode

- synchronized update capability

- noise-wave generation

- triangular-wave generation

- dual DAC channels' independent or simultaneous conversions

- DMA capability for each channel (including the underrun interrupt)

- external triggers for conversion

- input reference voltage V<sub>REF+</sub>

Eight DAC trigger inputs are used in the STM32L151x6/8/B and STM32L152x6/8/B devices. The DAC channels are triggered through the timer update outputs that are also connected to different DMA channels.

## 3.12 Ultra-low-power comparators and reference voltage

The STM32L151x6/8/B and STM32L152x6/8/B devices embed two comparators sharing the same current bias and reference voltage. The reference voltage can be internal or external (coming from an I/O).

- one comparator with fixed threshold

- one comparator with rail-to-rail inputs, fast or slow mode. The threshold can be one of the following:

- DAC output

- External I/O

- Internal reference voltage (V<sub>REFINT</sub>) or V<sub>REFINT</sub> submultiple (1/4, 1/2, 3/4)

Both comparators can wake up from Stop mode, and be combined into a window comparator.

The internal reference voltage is available externally via a low power / low current output buffer (driving current capability of 1  $\mu$ A typical).

## 3.13 Routing interface

This interface controls the internal routing of I/Os to TIM2, TIM3, TIM4 and to the comparator and reference voltage output.

## 3.14 Touch sensing

The STM32L151x6/8/B and STM32L152x6/8/B devices provide a simple solution for adding capacitive sensing functionality to any application. These devices offer up to 20 capacitive sensing channels distributed over 10 analog I/O groups. Only software capacitive sensing acquisition mode is supported.

Capacitive sensing technology is able to detect the presence of a finger near a sensor which is protected from direct touch by a dielectric (glass, plastic, ...). The capacitive variation introduced by the finger (or any conductive object) is measured using a proven

## 3.17 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

## 3.18 Development support

## Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target. The JTAG JTMS and JTCK pins are shared with SWDAT and SWCLK, respectively, and a specific sequence on the JTMS pin is used to switch between JTAG-DP and SW-DP.

The JTAG port can be permanently disabled with a JTAG fuse.

### Embedded Trace Macrocell™

The ARM Embedded Trace Macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32L151x6/8/B and STM32L152x6/8/B device through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. The TPA is connected to a host computer using USB, Ethernet, or any other high-speed channel. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer running debugger software. TPA hardware is commercially available from common development tool vendors. It operates with third party debugger software tools.

#### STM32L151x6/8/B STM32L152x6/8/B

|   | 1                        | 2                 | 3       | 4                    | 5       | 6      | 7       | 8      |

|---|--------------------------|-------------------|---------|----------------------|---------|--------|---------|--------|

| A | •<br>/PC14-,<br>OŚC32_IN | , PC13-,<br>WKUP2 | ( PB9 ) | ( PB4 )              | ( PB3 ) | (PA15) | (PA14)  | (PA13) |

| В | /PC15-,<br>OSC32_OUT     | VLCD              | (PB8)   | ВООТО                | (PD2)   | (PC11) | (PC10)  | (PA12) |

| С | , ₽ĤŎ÷,<br>OSC_IN∳       | VSS_4             | ( PB7 ) | (PB5)                | (PC12)  | (PA10) | ( PA9 ) | (PA11) |

| D | OSC_OUT                  | V <sub>DD_4</sub> | (PB6)   | ,V <sub>SS_3</sub> , | VSS_2   | VSS_1  | ( PA8 ) | (PC9)  |

| E | (NRST)                   | (PC1)             | PC0     | 'VDD_3'              | 'VDD_2' | VDD_1  | (PC7)   | (PC8)  |

| F | (Vssa)                   | (PC2)             | (PA2)   | ( PA5 )              | (PB0)   | (PC6)  | (PB15)  | (PB14) |

| G | WREF+ F                  | PA(0-WKU)P1       | ( PA3 ) | ( PA6 )              | (PB1)   | (PB2)  | (PB10)  | (PB13) |

| н | VDDA,                    | ( PA1 )           | (PA4)   | ( PA7 )              | (PC4)   | PC5    | (PB11)  | (PB12) |

Figure 5. STM32L15xRx TFBGA64 ballout

1. This figure shows the package top view.

## 6.1.6 Power supply scheme

Figure 12. Power supply scheme

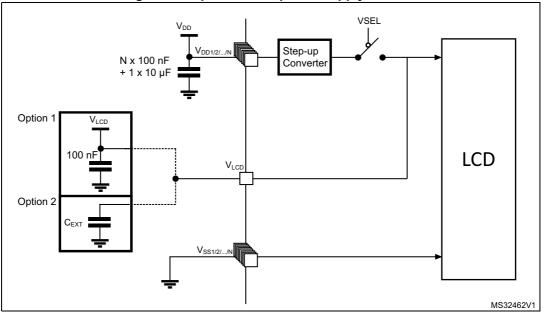

## 6.1.7 Optional LCD power supply scheme

#### Figure 13. Optional LCD power supply scheme

1. Option 1: LCD power supply is provided by a dedicated VLCD supply source, VSEL switch is open.

2. Option 2: LCD power supply is provided by the internal step-up converter, VSEL switch is closed, an external capacitance is needed for correct behavior of this converter.

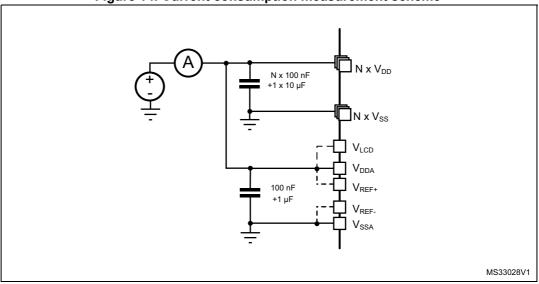

## 6.1.8 Current consumption measurement

#### Figure 14. Current consumption measurement scheme

## 6.3.3 Embedded internal reference voltage

The parameters given in the following table are based on characterization results, unless otherwise specified.

### Table 15. Embedded internal reference voltage calibration values

| Calibration value name | Description                                                       | Memory address          |

|------------------------|-------------------------------------------------------------------|-------------------------|

| VREFINT_CAL            | Raw data acquired at temperature of 30 °C, V <sub>DDA</sub> = 3 V | 0x1FF8 0078-0x1FF8 0079 |

| Symbol                                   | Parameter                                                                                    | Conditions                                                                              | Min   | Тур   | Max   | Unit                  |

|------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------|-------|-------|-----------------------|

| V <sub>REFINT out</sub> <sup>(1)</sup>   | Internal reference voltage                                                                   | – 40 °C < T <sub>J</sub> < +105 °C                                                      | 1.202 | 1.224 | 1.242 | V                     |

| I <sub>REFINT</sub>                      | Internal reference current consumption                                                       | -                                                                                       | -     | 1.4   | 2.3   | μA                    |

| T <sub>VREFINT</sub>                     | Internal reference startup time                                                              | -                                                                                       | -     | 2     | 3     | ms                    |

| V <sub>VREF_MEAS</sub>                   | V <sub>DDA</sub> and V <sub>REF+</sub> voltage during<br>V <sub>REFINT</sub> factory measure | -                                                                                       | 2.99  | 3     | 3.01  | V                     |

| A <sub>VREF_MEAS</sub>                   | Accuracy of factory-measured $V_{REF}$ value $^{(2)}$                                        | Including uncertainties<br>due to ADC and<br>V <sub>DDA</sub> /V <sub>REF+</sub> values | -     | -     | ±5    | mV                    |

| T <sub>Coeff</sub> <sup>(3)</sup>        | Temperature coefficient                                                                      | –40 °C < T <sub>J</sub> < +105 °C                                                       | -     | 25    | 100   | ppm/°C                |

| A <sub>Coeff</sub> <sup>(3)</sup>        | Long-term stability                                                                          | 1000 hours, T= 25 °C                                                                    | -     | -     | 1000  | ppm                   |

| V <sub>DDCoeff</sub> <sup>(3)</sup>      | Voltage coefficient                                                                          | 3.0 V < V <sub>DDA</sub> < 3.6 V                                                        | -     | -     | 2000  | ppm/V                 |

| T <sub>S_vrefint</sub> <sup>(3)(4)</sup> | ADC sampling time when reading the internal reference voltage                                | -                                                                                       | 5     | 10    | -     | μs                    |

| T <sub>ADC_BUF</sub> <sup>(3)</sup>      | Startup time of reference voltage buffer for ADC                                             | -                                                                                       | -     | -     | 10    | μs                    |

| I <sub>BUF_ADC</sub> <sup>(3)</sup>      | Consumption of reference voltage buffer for ADC                                              | -                                                                                       | -     | 13.5  | 25    | μA                    |

| I <sub>VREF_OUT</sub> <sup>(3)</sup>     | VREF_OUT output current <sup>(5)</sup>                                                       | -                                                                                       | -     | -     | 1     | μA                    |

| C <sub>VREF_OUT</sub> <sup>(3)</sup>     | VREF_OUT output load                                                                         | -                                                                                       | -     | -     | 50    | pF                    |

| I <sub>LPBUF</sub> <sup>(3)</sup>        | Consumption of reference voltage buffer for VREF_OUT and COMP                                | -                                                                                       | -     | 730   | 1200  | nA                    |

| V <sub>REFINT_DIV1</sub> <sup>(3)</sup>  | 1/4 reference voltage                                                                        | -                                                                                       | 24    | 25    | 26    |                       |

| V <sub>REFINT_DIV2</sub> <sup>(3)</sup>  | 1/2 reference voltage                                                                        | -                                                                                       | 49    | 50    | 51    | % V <sub>REFINT</sub> |

| V <sub>REFINT_DIV3</sub> <sup>(3)</sup>  | 3/4 reference voltage                                                                        | -                                                                                       | 74    | 75    | 76    |                       |

#### Table 16. Embedded internal reference voltage

1. Tested in production.

2. The internal  $V_{REF}$  value is individually measured in production and stored in dedicated EEPROM bytes.

3. Guaranteed by characterization results.

4. Shortest sampling time can be determined in the application by multiple iterations.

5. To guarantee less than 1% VREF\_OUT deviation.

| Symbol                                            | Parameter                                          |                                            | Conditions                                      |                                          |      | Max<br>(1) | Unit |

|---------------------------------------------------|----------------------------------------------------|--------------------------------------------|-------------------------------------------------|------------------------------------------|------|------------|------|

|                                                   |                                                    |                                            |                                                 | $T_A$ = -40 °C to 25 °C                  | 9    | 12         |      |

|                                                   |                                                    |                                            | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 32 kHz | T <sub>A</sub> = 85 °C                   | 17.5 | 24         |      |

|                                                   |                                                    | All<br>peripherals                         | HOLK 02 KHZ                                     | T <sub>A</sub> = 105 °C                  | 31   | 46         |      |

|                                                   |                                                    | OFF, code<br>executed                      |                                                 | $T_A = -40 \text{ °C to } 25 \text{ °C}$ | 14   | 17         |      |

|                                                   |                                                    | from RAM,                                  | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 65 kHz | T <sub>A</sub> = 85 °C                   | 22   | 29         |      |

|                                                   |                                                    | Flash<br>switched                          |                                                 | T <sub>A</sub> = 105 °C                  | 35   | 51         |      |

|                                                   |                                                    | OFF, V <sub>DD</sub>                       |                                                 | $T_A$ = -40 °C to 25 °C                  | 37   | 42         |      |

|                                                   |                                                    | from 1.65 V<br>to 3.6 V                    | MSI clock, 131 kHz                              | T <sub>A</sub> = 55 °C                   | 37   | 42         |      |

|                                                   | Supply<br>current in                               | 10 3.0 V                                   | f <sub>HCLK</sub> = 131 kHz                     | T <sub>A</sub> = 85 °C                   | 37   | 42         | μA   |

| I <sub>DD (LP</sub>                               |                                                    |                                            |                                                 | T <sub>A</sub> = 105 °C                  | 48   | 65         |      |

| Run)                                              | Low power<br>run mode                              | All peripherals                            | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 32 kHz | $T_A = -40 \degree C$ to 25 $\degree C$  | 24   | 32         |      |

|                                                   | Tull mode                                          |                                            |                                                 | T <sub>A</sub> = 85 °C                   | 33   | 42         |      |

|                                                   |                                                    |                                            |                                                 | T <sub>A</sub> = 105 °C                  | 48   | 64         |      |

|                                                   |                                                    |                                            | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 65 kHz | $T_A = -40 \text{ °C to } 25 \text{ °C}$ | 31   | 40         |      |

|                                                   |                                                    | OFF, code<br>executed                      |                                                 | T <sub>A</sub> = 85 °C                   | 40   | 48         |      |

|                                                   |                                                    | from Flash,<br>V <sub>DD</sub> from        | HOLK OUT IN 12                                  | T <sub>A</sub> = 105 °C                  | 54   | 70         |      |

|                                                   |                                                    | 1.65 V to                                  |                                                 | $T_A = -40 \degree C$ to 25 $\degree C$  | 48   | 58         |      |

|                                                   |                                                    | 3.6 V                                      | MSI clock, 131 kHz                              | T <sub>A</sub> = 55 °C                   | 54   | 63         |      |

|                                                   |                                                    |                                            | f <sub>HCLK</sub> = 131 kHz                     | T <sub>A</sub> = 85 °C                   | 56   | 65         |      |

|                                                   |                                                    |                                            |                                                 | T <sub>A</sub> = 105 °C                  | 70   | 90         |      |

| I <sub>DD</sub> Max<br>(LP<br>Run) <sup>(2)</sup> | Max allowed<br>current in<br>Low power<br>run mode | V <sub>DD</sub> from<br>1.65 V to<br>3.6 V | -                                               | -                                        | -    | 200        |      |

Table 20. Current consumption in Low power run mode

1. Guaranteed by characterization results, unless otherwise specified.

2. This limitation is related to the consumption of the CPU core and the peripherals that are powered by the regulator. Consumption of the I/Os is not included in this limitation.

| Symbol               | Parameter                                                                                                                 | Conditions                                                                    | Min | Тур | Мах                                | Unit     |

|----------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----|-----|------------------------------------|----------|

| f <sub>OSC_IN</sub>  | Oscillator frequency                                                                                                      | -                                                                             | 1   |     | 24                                 | MHz      |

| R <sub>F</sub>       | Feedback resistor                                                                                                         | -                                                                             |     | 200 | -                                  | kΩ       |

| С                    | Recommended load<br>capacitance versus<br>equivalent serial resistance<br>of the crystal (R <sub>S</sub> ) <sup>(3)</sup> | R <sub>S</sub> = 30 Ω                                                         | -   | 20  | -                                  | pF       |

| I <sub>HSE</sub>     | HSE driving current                                                                                                       | V <sub>DD</sub> = 3.3 V, V <sub>IN</sub> = V <sub>SS</sub><br>with 30 pF load | -   | -   | 3                                  | mA       |

|                      | HSE oscillator power                                                                                                      | C = 20 pF<br>f <sub>OSC</sub> = 16 MHz                                        | -   | -   | 2.5 (startup)<br>0.7 (stabilized)  | mA       |

| IDD(HSE)             | consumption                                                                                                               | C = 10 pF<br>f <sub>OSC</sub> = 16 MHz                                        | -   | -   | 2.5 (startup)<br>0.46 (stabilized) | mA       |

| 9 <sub>m</sub>       | Oscillator transconductance                                                                                               | Startup                                                                       | 3.5 | -   | -                                  | mA<br>/V |

| t <sub>SU(HSE)</sub> | Startup time                                                                                                              | $V_{DD}$ is stabilized                                                        | -   | 1   | -                                  | ms       |

| Table 28. | HSE | oscillator | characteristics <sup>(1)(2)</sup> |

|-----------|-----|------------|-----------------------------------|

|-----------|-----|------------|-----------------------------------|

1. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

2. Guaranteed by characterization results.

3. The relatively low value of the RF resistor offers a good protection against issues resulting from use in a humid environment, due to the induced leakage and the bias condition change. However, it is recommended to take this point into account if the MCU is used in tough humidity conditions.

t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 17*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ . Refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website *www.st.com*.

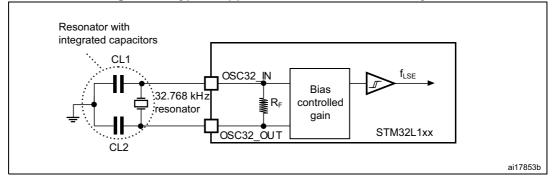

- t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

- Note: For CL1 and CL2, it is recommended to use high-quality ceramic capacitors in the 5 pF to 15 pF range selected to match the requirements of the crystal or resonator (see Figure 18). CL1 and CL2, are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of CL1 and CL2. Load capacitance CL has the following formula: CL = CL1 x CL2 / (CL1 + CL2) + Cstray where Cstray is the pin capacitance and board or trace PCB-related capacitance. Typically, it is between 2 pF and 7 pF.

- **Caution:** To avoid exceeding the maximum value of CL1 and CL2 (15 pF) it is strongly recommended to use a resonator with a load capacitance  $CL \le 7$  pF. Never use a resonator with a load capacitance of 12.5 pF.

Example: if a resonator is chosen with a load capacitance of CL = 6 pF and Cstray = 2 pF, then CL1 = CL2 = 8 pF.

#### Figure 18. Typical application with a 32.768 kHz crystal

#### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 20$  mA (with the non-standard V<sub>OL</sub>/V<sub>OH</sub> specifications given in *Table 43*.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 6.2*:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating I<sub>VDDΣ</sub> (see *Table 11*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating I<sub>VSSΣ</sub> (see *Table 11*).

## **Output voltage levels**

Unless otherwise specified, the parameters given in *Table 43* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 13*. All I/Os are CMOS and TTL compliant.

| Symbol                            | Parameter                                | Conditions                       | Min                   | Max  | Unit |

|-----------------------------------|------------------------------------------|----------------------------------|-----------------------|------|------|

| V <sub>OL</sub> <sup>(1)(2)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = 8 mA           | -                     | 0.4  |      |

| V <sub>OH</sub> <sup>(3)(2)</sup> | Output high level voltage for an I/O pin | 2.7 V < V <sub>DD</sub> < 3.6 V  | 2.4                   | -    |      |

| V <sub>OL</sub> <sup>(1)(4)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = 4 mA           | -                     | 0.45 | v    |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin | 1.65 V < V <sub>DD</sub> < 2.7 V | V <sub>DD</sub> -0.45 | -    | v    |

| V <sub>OL</sub> <sup>(1)(4)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = 20 mA          | -                     | 1.3  |      |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin | 2.7 V < V <sub>DD</sub> < 3.6 V  | V <sub>DD</sub> -1.3  | -    |      |

#### Table 43. Output voltage characteristics

1. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 11* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. Tested in production.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in *Table 11* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

4. Guaranteed by characterization results.

## 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

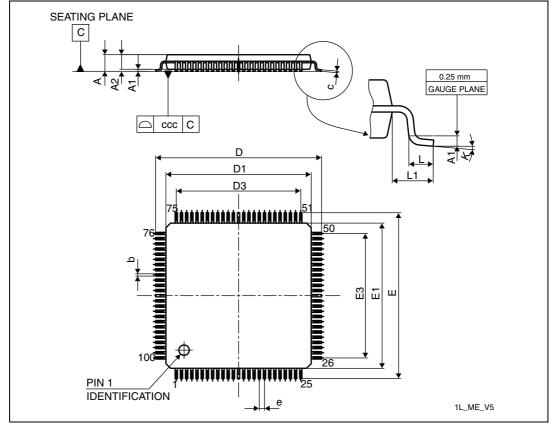

# 7.1 LQFP100 14 x 14 mm, 100-pin low-profile quad flat package information

Figure 32. LQFP100 14 x 14 mm, 100-pin low-profile quad flat package outline

1. Drawing is not to scale.

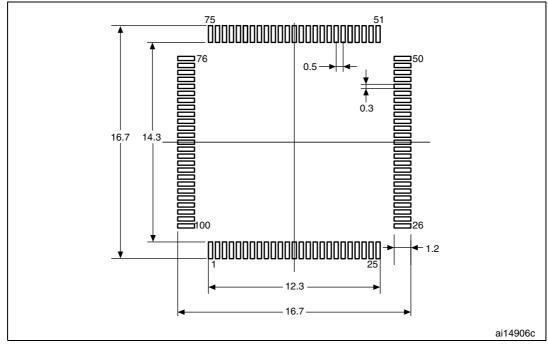

## Figure 33. LQPF100 14 x 14 mm, 100-pin low-profile quad flat package recommended footprint

1. Dimensions are in millimeters.

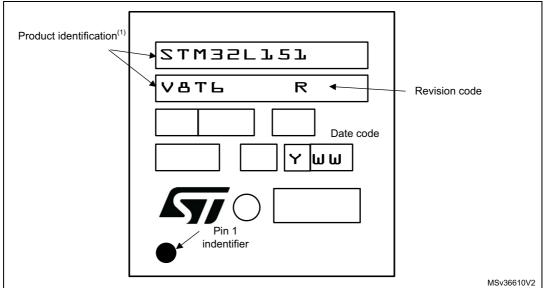

## LQFP100 device marking

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Figure 34. LQFP100 14 x 14 mm, 100-pin package top view example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

| Cumhal |            | millimeters |       | inches <sup>(1)</sup> |        |        |  |

|--------|------------|-------------|-------|-----------------------|--------|--------|--|

| Зутрої | Symbol Min |             | Max   | Тур                   | Min    | Мах    |  |

| E3     | -          | 7.500       | -     | -                     | 0.2953 | -      |  |

| е      | -          | 0.500       | -     | -                     | 0.0197 | -      |  |

| К      | 0°         | 3.5°        | 7°    | 0°                    | 3.5°   | 7°     |  |

| L      | 0.450      | 0.600       | 0.750 | 0.0177                | 0.0236 | 0.0295 |  |

| L1     | -          | 1.000       | -     | -                     | 0.0394 | -      |  |

| CCC    | -          | -           | 0.080 | -                     | -      | 0.0031 |  |

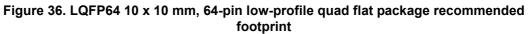

# Table 64. LQFP64 10 x 10 mm, 64-pin low-profile quad flat package mechanicaldata (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are in millimeters.

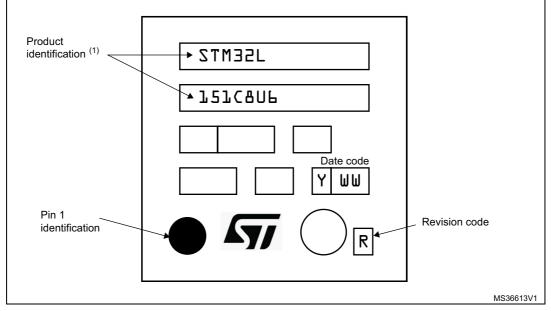

## **UFQFPN48** device marking

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

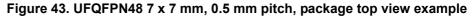

#### **UFBGA100** device marking

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Figure 46. UFBGA100 7 x 7 mm, 0.5 mm pitch, package top view example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

| Table 73. Document revision history (continued) |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|-------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Date                                            | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 17-June-2011                                    | 5        | Modified 1st page (low power features)<br>Added STM32L15xC6 and STM32L15xR6 devices (32 Kbytes of<br>Flash memory).<br>Modified Section 3.6: GPIOs (general-purpose inputs/outputs) on<br>page 22<br>Modified Section 6.3: Operating conditions on page 53<br>Modified Table 55: ADC accuracy on page 95, Table 57: DAC<br>characteristics on page 99 and Table 60: Comparator 1<br>characteristics on page 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                                                 |          | <i>Features</i> : updated internal multispeed low power RC.<br><i>Table 2: Ultralow power STM32L15xx6/8/B device features and peripheral counts</i> : LCD 4x44 and 8x40 available for both 64- and 128-Kbyte devices; two comparators available for all devices.<br><i>Table 3: Functionalities depending on the operating power supply range</i> : added footnote 1.<br><i>Figure 8: STM32L15xCx UFQFPN48 pinout</i> : replaced VFQPN48 by UFQFPN48 as name of package.                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|                                                 |          | Table 8: STM32L15xx6/8/B pin definitions: replaced PH0/PH1 by<br>PC14/PC15.Table 9: Alternate function input/output: removed EVENT OUT from<br>PH2 port, AFIO15 column.Table 19: Current consumption in Sleep mode: updated MSI<br>conditions and f <sub>HCLK</sub> .Table 20: Current consumption in Low power run mode: updated<br>some temperature conditions; added footnote 2.Table 21: Current consumption in Low power sleep mode: updated                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 25-Jan-2012                                     | 6        | some temperature conditions and one of the MSI clock conditions.<br><i>Table 22: Typical and maximum current consumptions in Stop</i><br><i>mode</i> : updated I <sub>DD</sub> (WU from Stop) parameter.<br><i>Table 23: Typical and maximum current consumptions in Standby</i><br><i>mode</i> : updated I <sub>DD</sub> (WU from Standby) parameter.<br><i>Table 25: Low-power mode wakeup timings</i> : updated f <sub>HCLK</sub> value                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|                                                 |          | for $t_{WUSLEEP\_LP}$ ; updated typical value of parameter "Wakeup from<br>Stop mode, regulator in Run mode".<br><i>Table 24: Peripheral current consumption</i> : replaced GPIOF by<br>GPIOH.<br><i>Table 33: PLL characteristics</i> : updated "PLL output clock"<br><i>Table 35: Flash memory and data EEPROM characteristics</i> :<br>updated all information for I <sub>DD</sub> .<br><i>Figure 19: I/O AC characteristics definition</i> : replaced the falling<br>edge "t <sub>r(IO)out</sub> " by "t <sub>f(IO)out</sub> ".<br><i>Table 47: I2C characteristics</i> : updated f <sub>S</sub> max value for direct<br>channels, 6-bit sampling rate.<br><i>Table 55: ADC accuracy</i> : Updated the first, third and fourth f <sub>ADC</sub> test<br>condition.<br><i>Table 59: Temperature sensor characteristics</i> : updated typ, min,<br>and max values of the T <sub>S temp</sub> parameter. |  |  |

| Date        | Revision         | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12-Nov-2013 | 9<br>(continued) | Updated Table 54: ADC characteristics and Figure 27: Typical connection diagram using the ADC.<br>Table 58: Temperature sensor calibration values was previously in Section 3.10.1: Temperature sensor. Updated Table 59:<br>Temperature sensor characteristics.<br>In Table 61: Comparator 2 characteristics, parameter dThreshold/dt, replaced any occurrence of "VREF+" by "V <sub>REFINT</sub> "Updated Table 63: LQPF100 14 x 14 mm, 100-pin low-profile quad flat package mechanical data, Table 64: LQFP64 10 x 10 mm 64-pin low-profile quad flat package mechanical data, Table 65: LQFP48 7 x 7 mm, 48-pin low-profile quad flat package mechanical data.<br>Updated Figure 33: LQFP100 recommended footprint.<br>Updated Figure 46: TFBGA64 - 5.0x5.0x1.2 mm, 0.5 mm pitch, thin fine-pitch dall grid array package outline title.<br>Remove minimum and typical values of A dimension in Table 67: UFBGA100 7 x 7 x 0.6 mm 0.5 mm pitch, ultra thin fine-pitch ball grid array package mechanical data<br>Deleted second footnote in Figure 42: UFQFPN48 recommended footprint.<br>Updated Section 8: Ordering information title and added first sentence.<br>Changed BOR disabled option identifier in Table 72: Ordering information scheme. |

| 22-Jul-2014 | 10               | Updated <i>Figure 14</i> , <i>Figure 15</i> .<br>Updated <i>Table 5</i> .<br>Updated <i>Figure 6.3.4</i> .<br>Updated note 5 inside <i>Table 54</i> .<br>Updated Ro value inside <i>Table 54</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Table 73. | Document revision history (continued) |

|-----------|---------------------------------------|

|           |                                       |