Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                          |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                              |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                         |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT |

| Number of I/O              | 37                                                                           |

| Program Memory Size        | 64KB (64K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 4K x 8                                                                       |

| RAM Size                   | 10K × 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                        |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 48-UFQFN Exposed Pad                                                         |

| Supplier Device Package    | 48-UFQFPN (7x7)                                                              |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|   |      | 6.3.9     | Memory characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---|------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |      | 6.3.10    | EMC characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   |      | 6.3.11    | Electrical sensitivity characteristics80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   |      | 6.3.12    | I/O current injection characteristics81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |      | 6.3.13    | I/O port characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   |      | 6.3.14    | NRST pin characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   |      | 6.3.15    | TIM timer characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   |      | 6.3.16    | Communication interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   |      | 6.3.17    | 12-bit ADC characteristics93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   |      | 6.3.18    | DAC electrical specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   |      | 6.3.19    | Temperature sensor characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |      | 6.3.20    | Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   |      | 6.3.21    | LCD controller (STM32L152xx only) 104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7 | Pack | kage info | ormation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   | 7.1  |           | 00 14 x 14 mm, 100-pin low-profile quad flat package<br>ation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | 7.2  | LQFP6     | 4 10 x 10 mm, 64-pin low-profile quad flat package information.108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   | 7.3  | LQFP4     | 8 7 x 7 mm, 48-pin low-profile quad flat package information 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 7.4  | UFQFF     | PN48 7 x 7 mm, 0.5 mm pitch, package information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 7.5  |           | A100 7 x 7 mm, 0.5 mm pitch, ultra thin fine-pitch<br>d array package information117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

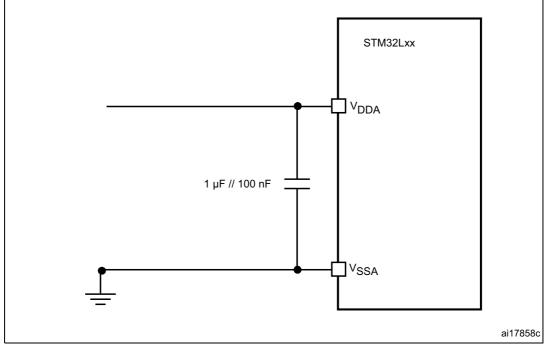

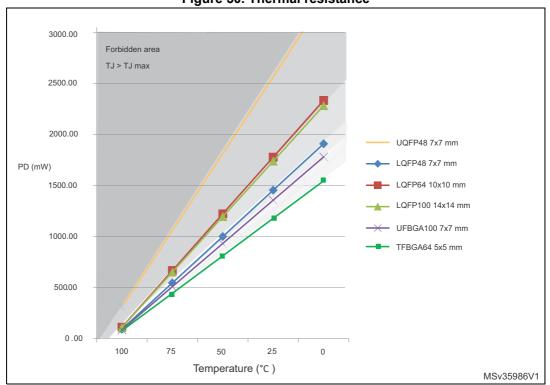

|   | 7.6  |           | A64 5 x 5 mm, 0.5 mm pitch, thin fine-pitch ball and the second sec |

|   | 7.7  | Therma    | al characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |      | 7.7.1     | Reference document                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 8 | Orde | ering inf | ormation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 9 | Revi | sion his  | story                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

# 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32L151x6/8/B and STM32L152x6/8/B ultra-low-power ARM<sup>®</sup> Cortex<sup>®</sup>-M3 based microcontrollers product line.

The ultra-low-power STM32L151x6/8/B and STM32L152x6/8/B family includes devices in 3 different package types: from 48 to 100 pins. Depending on the device chosen, different sets of peripherals are included, the description below gives an overview of the complete range of peripherals proposed in this family.

These features make the ultra-low-power STM32L151x6/8/B and STM32L152x6/8/B microcontroller family suitable for a wide range of applications:

- Medical and handheld equipment

- Application control and user interface

- PC peripherals, gaming, GPS and sport equipment

- Alarm systems, Wired and wireless sensors, Video intercom

- Utility metering

This STM32L151x6/8/B and STM32L152x6/8/B datasheet should be read in conjunction with the STM32L1xxxx reference manual (RM0038).

The document "Getting started with STM32L1xxxx hardware development" AN3216 gives a hardware implementation overview. Both documents are available from the STMicroelectronics website *www.st.com*.

For information on the ARM<sup>®</sup> Cortex<sup>®</sup>-M3 core please refer to the Cortex<sup>®</sup>-M3 Technical Reference Manual, available from the www.arm.com website.

Figure 1 shows the general block diagram of the device family.

**Caution:** This datasheet does not apply to STM32L15xx6/8/B-A covered by a separate datasheet.

#### Nested vectored interrupt controller (NVIC)

The ultra-low-power STM32L151x6/8/B and STM32L152x6/8/B devices embed a nested vectored interrupt controller able to handle up to 45 maskable interrupt channels (not including the 16 interrupt lines of Cortex<sup>®</sup>-M3) and 16 priority levels.

- Closely coupled NVIC gives low-latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of *late arriving*, higher-priority interrupts

- Support for tail-chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimal interrupt latency.

## 3.3 Reset and supply management

### 3.3.1 **Power supply schemes**

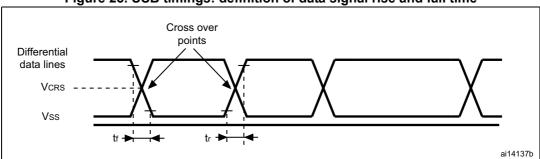

- V<sub>DD</sub> = 1.65 to 3.6 V: external power supply for I/Os and the internal regulator. Provided externally through V<sub>DD</sub> pins.

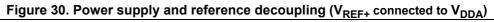

- $V_{SSA}$ ,  $V_{DDA}$  = 1.65 to 3.6 V: external analog power supplies for ADC, reset blocks, RCs and PLL (minimum voltage to be applied to  $V_{DDA}$  is 1.8 V when the ADC is used).  $V_{DDA}$  and  $V_{SSA}$  must be connected to  $V_{DD}$  and  $V_{SS}$ , respectively.

### 3.3.2 Power supply supervisor

The device has an integrated ZEROPOWER power-on reset (POR)/power-down reset (PDR) that can be coupled with a brownout reset (BOR) circuitry.

The device exists in two versions:

- The version with BOR activated at power-on operates between 1.8 V and 3.6 V.

- The other version without BOR operates between 1.65 V and 3.6 V.

After the  $V_{DD}$  threshold is reached (1.65 V or 1.8 V depending on the BOR which is active or not at power-on), the option byte loading process starts, either to confirm or modify default thresholds, or to disable the BOR permanently: in this case, the  $V_{DD}$  min value becomes 1.65 V (whatever the version, BOR active or not, at power-on).

When BOR is active at power-on, it ensures proper operation starting from 1.8 V whatever the power ramp-up phase before it reaches 1.8 V. When BOR is not active at power-up, the power ramp-up should guarantee that 1.65 V is reached on  $V_{DD}$  at least 1 ms after it exits the POR area.

## 3.4 Clock management

The clock controller distributes the clocks coming from different oscillators to the core and the peripherals. It also manages clock gating for low power modes and ensures clock robustness. It features:

- Clock prescaler: to get the best trade-off between speed and current consumption, the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler

- **Safe clock switching**: clock sources can be changed safely on the fly in run mode through a configuration register.

- **Clock management**: to reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

- **Master clock source**: three different clock sources can be used to drive the master clock:

- 1-24 MHz high-speed external crystal (HSE), that can supply a PLL

- 16 MHz high-speed internal RC oscillator (HSI), trimmable by software, that can supply a PLL

- Multispeed internal RC oscillator (MSI), trimmable by software, able to generate 7 frequencies (65.5 kHz, 131 kHz, 262 kHz, 524 kHz, 1.05 MHz, 2.1 MHz, 4.2 MHz) with a consumption proportional to speed, down to 750 nA typical. When a 32.768 kHz clock source is available in the system (LSE), the MSI frequency can be trimmed by software down to a ±0.5% accuracy.

- **Auxiliary clock source**: two ultra-low-power clock sources that can be used to drive the LCD controller and the real-time clock:

- 32.768 kHz low-speed external crystal (LSE)

- 37 kHz low-speed internal RC (LSI), also used to drive the independent watchdog. The LSI clock can be measured using the high-speed internal RC oscillator for greater precision.

- **RTC and LCD clock sources:** the LSI, LSE or HSE sources can be chosen to clock the RTC and the LCD, whatever the system clock.

- **USB clock source:** the embedded PLL has a dedicated 48 MHz clock output to supply the USB interface.

- **Startup clock:** after reset, the microcontroller restarts by default with an internal 2.1 MHz clock (MSI). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

- Clock security system (CSS): this feature can be enabled by software. If a HSE clock failure occurs, the master clock is automatically switched to HSI and a software interrupt is generated if enabled.

- Clock-out capability (MCO: microcontroller clock output): it outputs one of the internal clocks for external use by the application.

Several prescalers allow the configuration of the AHB frequency, the high-speed APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the AHB and the APB domains is 32 MHz. See *Figure 2* for details on the clock tree.

## 3.5 Low power real-time clock and backup registers

The real-time clock (RTC) is an independent BCD timer/counter. Dedicated registers contain the second, minute, hour (12/24 hour), week day, date, month, year, in BCD (binary-coded decimal) format. Correction for 28, 29 (leap year), 30, and 31 day of the month are made automatically. The RTC provides a programmable alarm and programmable periodic interrupts with wakeup from Stop and Standby modes.

- The programmable wakeup time ranges from 120 µs to 36 hours

- Stop mode consumption with LSI and Auto-wakeup: 1.2  $\mu A$  (at 1.8 V) and 1.4  $\mu A$  (at 3.0 V)

- Stop mode consumption with LSE, calendar and Auto-wakeup: 1.3 μA (at 1.8V), 1.6 μA (at 3.0 V)

The RTC can be calibrated with an external 512 Hz output, and a digital compensation circuit helps reduce drift due to crystal deviation.

There are twenty 32-bit backup registers provided to store 80 bytes of user application data. They are cleared in case of tamper detection.

## **3.6 GPIOs (general-purpose inputs/outputs)**

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions, and can be individually remapped using dedicated AFIO registers. All GPIOs are high current capable. The alternate function configuration of I/Os can be locked if needed following a specific sequence in order to avoid spurious writing to the I/O registers. The I/O controller is connected to the AHB with a toggling speed of up to 16 MHz.

### External interrupt/event controller (EXTI)

The external interrupt/event controller consists of 23 edge detector lines used to generate interrupt/event requests. Each line can be individually configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 83 GPIOs can be connected to the 16 external interrupt lines. The 7 other lines are connected to RTC, PVD, USB or Comparator events.

### 3.15.5 Window watchdog (WWDG)

The window watchdog is based on a 7-bit down-counter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

## 3.16 Communication interfaces

### 3.16.1 I<sup>2</sup>C bus

Up to two I<sup>2</sup>C bus interfaces can operate in multimaster and slave modes. They can support standard and fast modes.

They support dual slave addressing (7-bit only) and both 7- and 10-bit addressing in master mode. A hardware CRC generation/verification is embedded.

They can be served by DMA and they support SM Bus 2.0/PM Bus.

#### 3.16.2 Universal synchronous/asynchronous receiver transmitter (USART)

All USART interfaces are able to communicate at speeds of up to 4 Mbit/s. They provide hardware management of the CTS and RTS signals and are ISO 7816 compliant. They support IrDA SIR ENDEC and have LIN Master/Slave capability.

All USART interfaces can be served by the DMA controller.

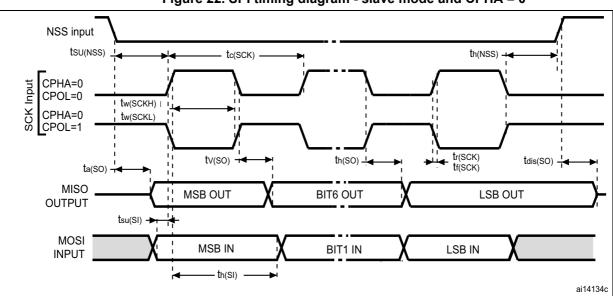

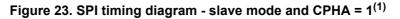

### 3.16.3 Serial peripheral interface (SPI)

Up to two SPIs are able to communicate at up to 16 Mbits/s in slave and master modes in full-duplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes.

Both SPIs can be served by the DMA controller.

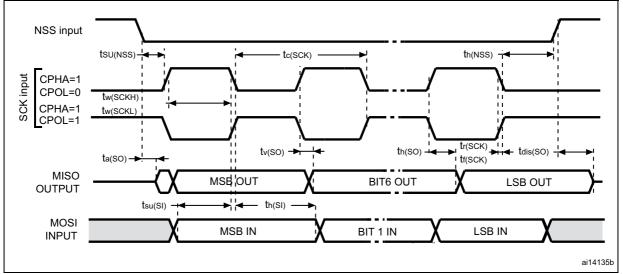

### 3.16.4 Universal serial bus (USB)

The STM32L151x6/8/B and STM32L152x6/8/B devices embed a USB device peripheral compatible with the USB full speed 12 Mbit/s. The USB interface implements a full speed (12 Mbit/s) function interface. It has software-configurable endpoint setting and supports suspend/resume. The dedicated 48 MHz clock is generated from the internal main PLL (the clock source must use a HSE crystal oscillator).

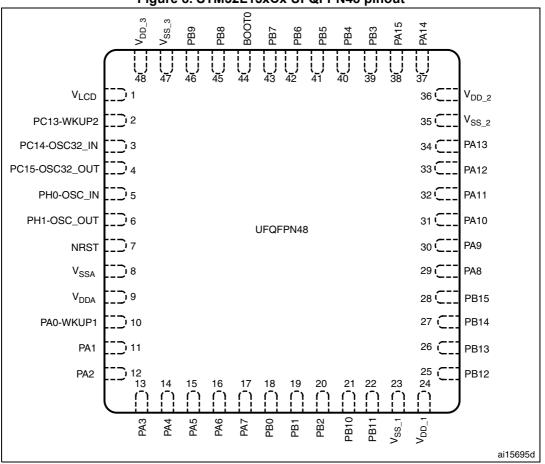

Figure 8. STM32L15xCx UFQFPN48 pinout

1. This figure shows the package top view.

|         |        | Pin     | S        |                    |                   |                         |               |                                                  | Pins functions                                           | inicaj                             |

|---------|--------|---------|----------|--------------------|-------------------|-------------------------|---------------|--------------------------------------------------|----------------------------------------------------------|------------------------------------|

| LQFP100 | LQFP64 | TFBGA64 | UFBGA100 | LQFP48 or UFQFPN48 | Pin name          | Pin type <sup>(1)</sup> | I/O structure | Main<br>function <sup>(2)</sup><br>(after reset) | Alternate functions                                      | Additional<br>functions            |

| 35      | 26     | F5      | M5       | 18                 | PB0               | I/O                     | TC            | PB0                                              | TIM3_CH3/LCD_SEG5                                        | ADC_IN8/<br>COMP1_INP/<br>VREF_OUT |

| 36      | 27     | G5      | M6       | 19                 | PB1               | I/O                     | FT            | PB1                                              | TIM3_CH4/LCD_SEG6                                        | ADC_IN9/<br>COMP1_INP/<br>VREF_OUT |

| 37      | 28     | G6      | L6       | 20                 | PB2               | I/O                     | FT            | PB2/BOOT1                                        | BOOT1                                                    | -                                  |

| 38      | -      | -       | M7       | -                  | PE7               | I/O                     | тс            | PE7                                              | -                                                        | ADC_IN22/<br>COMP1_INP             |

| 39      | -      | -       | L7       | -                  | PE8               | I/O                     | тс            | PE8                                              | -                                                        | ADC_IN23/<br>COMP1_INP             |

| 40      | -      | -       | M8       | -                  | PE9               | I/O                     | тс            | PE9                                              | TIM2_CH1_ETR                                             | ADC_IN24/<br>COMP1_INP             |

| 41      | -      | -       | L8       | -                  | PE10              | I/O                     | тс            | PE10                                             | TIM2_CH2                                                 | ADC_IN25/<br>COMP1_INP             |

| 42      | -      | -       | M9       | -                  | PE11              | I/O                     | FT            | PE11                                             | TIM2_CH3                                                 | -                                  |

| 43      | -      | -       | L9       | -                  | PE12              | I/O                     | FT            | PE12                                             | TIM2_CH4/SPI1_NSS                                        | -                                  |

| 44      | -      | -       | M10      | -                  | PE13              | I/O                     | FT            | PE13                                             | SPI1_SCK                                                 | -                                  |

| 45      | -      | -       | M11      | -                  | PE14              | I/O                     | FT            | PE14                                             | SPI1_MISO                                                | -                                  |

| 46      | -      | -       | M12      | -                  | PE15              | I/O                     | FT            | PE15                                             | SPI1_MOSI                                                | -                                  |

| 47      | 29     | G7      | L10      | 21                 | PB10              | I/O                     | FT            | PB10                                             | I2C2_SCL/USART3_TX/<br>TIM2_CH3/LCD_SEG10                | -                                  |

| 48      | 30     | H7      | L11      | 22                 | PB11              | I/O                     | FT            | PB11                                             | I2C2_SDA/USART3_RX/<br>TIM2_CH4/LCD_SEG11                | -                                  |

| 49      | 31     | D6      | F12      | 23                 | V <sub>SS_1</sub> | S                       | -             | V <sub>SS_1</sub>                                | -                                                        | -                                  |

| 50      | 32     | E6      | G12      | 24                 | V <sub>DD_1</sub> | S                       | -             | V <sub>DD_1</sub>                                | -                                                        | -                                  |

| 51      | 33     | H8      | L12      | 25                 | PB12              | I/O                     | FT            | PB12                                             | SPI2_NSS/I2C2_SMBA/<br>USART3_CK/<br>LCD_SEG12/TIM10_CH1 | ADC_IN18/<br>COMP1_INP             |

| 52      | 34     | G8      | K12      | 26                 | PB13              | I/O                     | FT            | PB13                                             | SPI2_SCK/USART3_CTS/<br>LCD_SEG13/<br>TIM9_CH1           | ADC_IN19/<br>COMP1_INP             |

# Table 8. STM32L151x6/8/B and STM32L152x6/8/B pin definitions (continued)

| Symbol            | Parameter                     | Conditions                                | Min  | Тур  | Max  | Unit |  |

|-------------------|-------------------------------|-------------------------------------------|------|------|------|------|--|

| V                 | Programmable voltage detector | Falling edge                              | 1.8  | 1.85 | 1.88 |      |  |

| V <sub>PVD0</sub> | threshold 0                   | Rising edge                               | 1.88 | 1.94 | 1.99 |      |  |

| V                 | PVD threshold 1               | Falling edge                              | 1.98 | 2.04 | 2.09 |      |  |

| V <sub>PVD1</sub> |                               | Rising edge                               | 2.08 | 2.14 | 2.18 |      |  |

| V                 | PVD threshold 2               | Falling edge                              | 2.20 | 2.24 | 2.28 |      |  |

| V <sub>PVD2</sub> |                               | Rising edge                               | 2.28 | 2.34 | 2.38 |      |  |

| V                 | PVD threshold 3               | Falling edge                              | 2.39 | 2.44 | 2.48 | V    |  |

| V <sub>PVD3</sub> |                               | Rising edge                               | 2.47 | 2.54 | 2.58 | v    |  |

| M                 | PVD threshold 4               | Falling edge                              | 2.57 | 2.64 | 2.69 |      |  |

| V <sub>PVD4</sub> |                               | Rising edge                               | 2.68 | 2.74 | 2.79 |      |  |

| V                 | PVD threshold 5               | Falling edge                              | 2.77 | 2.83 | 2.88 |      |  |

| $V_{PVD5}$        |                               | Rising edge                               | 2.87 | 2.94 | 2.99 |      |  |

| V                 | PVD threshold 6               | Falling edge                              | 2.97 | 3.05 | 3.09 |      |  |

| V <sub>PVD6</sub> |                               | Rising edge                               | 3.08 | 3.15 | 3.20 |      |  |

|                   |                               | BOR0 threshold                            | -    | 40   | -    |      |  |

| V <sub>hyst</sub> | Hysteresis voltage            | All BOR and PVD thresholds excepting BOR0 | -    | 100  | -    | mV   |  |

Table 14. Embedded reset and power control block characteristics (continued)

1. Guaranteed by characterization results.

2. Valid for device version without BOR at power up. Please see option "T" in Ordering information scheme for more details.

| Symbol                                            | Parameter                                          |                                            | Conditions                                             |                                          |      | Max<br>(1) | Unit |

|---------------------------------------------------|----------------------------------------------------|--------------------------------------------|--------------------------------------------------------|------------------------------------------|------|------------|------|

|                                                   |                                                    |                                            |                                                        | $T_A$ = -40 °C to 25 °C                  | 9    | 12         |      |

|                                                   |                                                    |                                            | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 32 kHz        | T <sub>A</sub> = 85 °C                   | 17.5 | 24         |      |

|                                                   |                                                    | All<br>peripherals                         | HOLK 02 KHZ                                            | T <sub>A</sub> = 105 °C                  | 31   | 46         |      |

|                                                   |                                                    | OFF, code<br>executed                      |                                                        | $T_A = -40 \text{ °C to } 25 \text{ °C}$ | 14   | 17         |      |

|                                                   |                                                    | from RAM,                                  | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 65 kHz        | T <sub>A</sub> = 85 °C                   | 22   | 29         |      |

|                                                   |                                                    | Flash<br>switched                          |                                                        | T <sub>A</sub> = 105 °C                  | 35   | 51         |      |

|                                                   |                                                    | OFF, V <sub>DD</sub>                       |                                                        | $T_A$ = -40 °C to 25 °C                  | 37   | 42         |      |

|                                                   |                                                    | from 1.65 V<br>to 3.6 V                    | MSI clock, 131 kHz                                     | T <sub>A</sub> = 55 °C                   | 37   | 42         |      |

|                                                   | Supply<br>current in<br>Low power<br>run mode      | 10 3.0 V                                   | f <sub>HCLK</sub> = 131 kHz                            | T <sub>A</sub> = 85 °C                   | 37   | 42         | -    |

| I <sub>DD (LP</sub>                               |                                                    |                                            |                                                        | T <sub>A</sub> = 105 °C                  | 48   | 65         |      |

| Run)                                              |                                                    | All<br>peripherals                         |                                                        | $T_A = -40 \degree C$ to 25 $\degree C$  | 24   | 32         |      |

|                                                   |                                                    |                                            | MSI clock, 65 kHz<br>$f_{HCLK}$ = 32 kHz $T_A$ = 85 °C |                                          | 33   | 42         | μA   |

|                                                   |                                                    |                                            | HOLK 02 KHZ                                            | T <sub>A</sub> = 105 °C                  | 48   | 64         |      |

|                                                   |                                                    |                                            |                                                        | $T_A = -40 \text{ °C to } 25 \text{ °C}$ | 31   | 40         |      |

|                                                   |                                                    | OFF, code<br>executed                      | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 65 kHz        | T <sub>A</sub> = 85 °C                   | 40   | 48         |      |

|                                                   |                                                    | from Flash,<br>V <sub>DD</sub> from        | HOLK OUT IN 12                                         | T <sub>A</sub> = 105 °C                  | 54   | 70         |      |

|                                                   |                                                    | 1.65 V to                                  |                                                        | $T_A = -40 \degree C$ to 25 $\degree C$  | 48   | 58         |      |

|                                                   |                                                    | 3.6 V                                      | MSI clock, 131 kHz                                     | T <sub>A</sub> = 55 °C                   | 54   | 63         |      |

|                                                   |                                                    |                                            | f <sub>HCLK</sub> = 131 kHz                            | T <sub>A</sub> = 85 °C                   | 56   | 65         |      |

|                                                   |                                                    |                                            |                                                        | T <sub>A</sub> = 105 °C                  | 70   | 90         |      |

| I <sub>DD</sub> Max<br>(LP<br>Run) <sup>(2)</sup> | Max allowed<br>current in<br>Low power<br>run mode | V <sub>DD</sub> from<br>1.65 V to<br>3.6 V | -                                                      | -                                        | -    | 200        |      |

Table 20. Current consumption in Low power run mode

1. Guaranteed by characterization results, unless otherwise specified.

2. This limitation is related to the consumption of the CPU core and the peripherals that are powered by the regulator. Consumption of the I/Os is not included in this limitation.

| Symbol                                  | Parameter                                                                  | Conditions                                                  |                                                             | Typ <sup>(1)</sup> | Max<br>(1)(2)    | Unit |

|-----------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|--------------------|------------------|------|

|                                         |                                                                            |                                                             | T <sub>A</sub> = -40 °C to 25 °C<br>V <sub>DD</sub> = 1.8 V | 0.9                | -                |      |

|                                         |                                                                            | RTC clocked by LSI (no                                      | $T_A = -40 \ ^\circ C \text{ to } 25 \ ^\circ C$            | 1.1                | 1.8              |      |

|                                         |                                                                            | independent watchdog)                                       | T <sub>A</sub> = 55 °C                                      | 1.42               | 2.5              |      |

|                                         |                                                                            |                                                             | T <sub>A</sub> = 85 °C                                      | 1.87               | 3                |      |

| I <sub>DD</sub>                         | Supply current in Standby                                                  |                                                             | T <sub>A</sub> = 105 °C                                     | 2.78               | 5                |      |

| (Standby<br>with RTC)                   | mode with RTC enabled                                                      |                                                             | T <sub>A</sub> = -40 °C to 25 °C<br>V <sub>DD</sub> = 1.8 V | 1                  | -                |      |

|                                         |                                                                            | RTC clocked by LSE (no independent watchdog) <sup>(3)</sup> | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$                     | 1.33               | 2.9              | μΑ   |

|                                         |                                                                            |                                                             | T <sub>A</sub> = 55 °C                                      | 1.59               | 3.4              |      |

|                                         |                                                                            |                                                             | T <sub>A</sub> = 85 °C                                      | 2.01               | 4.3              |      |

|                                         |                                                                            |                                                             | T <sub>A</sub> = 105 °C                                     | 3.27               | 6.3              |      |

|                                         |                                                                            | Independent watchdog<br>and LSI enabled                     | $T_A = -40 \text{ °C to } 25 \text{ °C}$                    | 1.1                | 1.6              |      |

| I <sub>DD</sub>                         | Supply current in Standby                                                  |                                                             | $T_A = -40 \degree C$ to 25 $\degree C$                     | 0.3                | 0.55             | -    |

| (Standby)                               | mode with RTC disabled                                                     | Independent watchdog                                        | T <sub>A</sub> = 55 °C                                      | 0.5                | 0.8              |      |

|                                         |                                                                            | and LSI OFF                                                 | T <sub>A</sub> = 85 °C                                      | 1                  | 1.7              |      |

|                                         |                                                                            |                                                             | T <sub>A</sub> = 105 °C                                     | 2.5                | 4 <sup>(4)</sup> |      |

| I <sub>DD (WU</sub><br>from<br>Standby) | RMS supply current during<br>wakeup time when exiting<br>from Standby mode | -                                                           | V <sub>DD</sub> = 3.0 V<br>T <sub>A</sub> = -40 °C to 25 °C | 1                  | -                |      |

| Table 23. Typical and maximum current consumption | s in Standby mode  |

|---------------------------------------------------|--------------------|

| Table 25. Typical and maximum current consumption | 5 III Stanuby moue |

1. The typical values are given for  $V_{DD}$  = 3.0 V and max values are given for  $V_{DD}$  = 3.6 V, unless otherwise specified.