Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                          |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                              |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                         |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT |

| Number of I/O              | 51                                                                           |

| Program Memory Size        | 64KB (64K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 4K x 8                                                                       |

| RAM Size                   | 10K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 20x12b; D/A 2x12b                                                        |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 64-TFBGA                                                                     |

| Supplier Device Package    | 64-TFBGA (5x5)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l152r8h6        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|   |        | 3.15.1    | General-purpose timers (TIM2, TIM3, TIM4, TIM9, TIM10 and TIM11) . | . 28 |

|---|--------|-----------|--------------------------------------------------------------------|------|

|   |        | 3.15.2    | Basic timers (TIM6 and TIM7)                                       | . 28 |

|   |        | 3.15.3    | SysTick timer                                                      | . 28 |

|   |        | 3.15.4    | Independent watchdog (IWDG)                                        | . 28 |

|   |        | 3.15.5    | Window watchdog (WWDG)                                             | . 29 |

|   | 3.16   | Commu     | nication interfaces                                                | 29   |

|   |        | 3.16.1    | I <sup>2</sup> C bus                                               | . 29 |

|   |        | 3.16.2    | Universal synchronous/asynchronous receiver transmitter (USART)    | . 29 |

|   |        | 3.16.3    | Serial peripheral interface (SPI)                                  | . 29 |

|   |        | 3.16.4    | Universal serial bus (USB)                                         | . 29 |

|   | 3.17   | CRC (cy   | clic redundancy check) calculation unit                            | 30   |

|   | 3.18   | Develop   | oment support                                                      | 30   |

|   |        |           |                                                                    |      |

| 4 | Pin de | escripti  | ons                                                                | 31   |

| 5 | Memo   | ory map   | ping                                                               | 48   |

|   |        | <b>,</b>  |                                                                    |      |

| 6 | Electi | rical cha | aracteristics                                                      | 49   |

|   | 6.1    | Parame    | ter conditions                                                     | 49   |

|   |        | 6.1.1     | Minimum and maximum values                                         | . 49 |

|   |        | 6.1.2     | Typical values                                                     | . 49 |

|   |        | 6.1.3     | Typical curves                                                     | . 49 |

|   |        | 6.1.4     | Loading capacitor                                                  | . 49 |

|   |        | 6.1.5     | Pin input voltage                                                  | . 49 |

|   |        | 6.1.6     | Power supply scheme                                                | . 50 |

|   |        | 6.1.7     | Optional LCD power supply scheme                                   |      |

|   |        | 6.1.8     | Current consumption measurement                                    | . 51 |

|   | 6.2    | Absolute  | e maximum ratings                                                  | 52   |

|   | 6.3    | Operatir  | ng conditions                                                      | 53   |

|   |        | 6.3.1     | General operating conditions                                       | . 53 |

|   |        | 6.3.2     | Embedded reset and power control block characteristics             | . 54 |

|   |        | 6.3.3     | Embedded internal reference voltage                                | . 56 |

|   |        | 6.3.4     | Supply current characteristics                                     | . 57 |

|   |        | 6.3.5     | Wakeup time from Low power mode                                    | . 69 |

|   |        | 6.3.6     | External clock source characteristics                              | . 70 |

|   |        | 6.3.7     | Internal clock source characteristics                              | . 75 |

|   |        | 6.3.8     | PLL characteristics                                                | . 77 |

|   |        |           |                                                                    |      |

# 2.2 Ultra-low-power device continuum

The ultra-low-power STM32L151x6/8/B and STM32L152x6/8/B devices are fully pin-to-pin and software compatible. Besides the full compatibility within the family, the devices are part of STMicroelectronics microcontrollers ultra-low-power strategy which also includes STM8L101xx and STM8L15xx devices. The STM8L and STM32L families allow a continuum of performance, peripherals, system architecture and features.

They are all based on STMicroelectronics ultra-low leakage process.

Note: The ultra-low-power STM32L and general-purpose STM32Fxxxx families are pin-to-pin compatible. The STM8L15xxx devices are pin-to-pin compatible with the STM8L101xx devices. Please refer to the STM32F and STM8L documentation for more information on these devices.

#### 2.2.1 Performance

All families incorporate highly energy-efficient cores with both Harvard architecture and pipelined execution: advanced STM8 core for STM8L families and ARM<sup>®</sup> Cortex<sup>®</sup>-M3 core for STM32L family. In addition specific care for the design architecture has been taken to optimize the mA/DMIPS and mA/MHz ratios.

This allows the ultra-low-power performance to range from 5 up to 33.3 DMIPs.

#### 2.2.2 Shared peripherals

STM8L15xxx and STM32L1xxxx share identical peripherals which ensure a very easy migration from one family to another:

- Analog peripherals: ADC, DAC and comparators

- Digital peripherals: RTC and some communication interfaces

#### 2.2.3 Common system strategy

To offer flexibility and optimize performance, the STM8L15xx and STM32L1xxxx families use a common architecture:

- Same power supply range from 1.65 V to 3.6 V, (1.65 V at power down only for STM8L15xx devices)

- Architecture optimized to reach ultra-low consumption both in low power modes and Run mode

- Fast startup strategy from low power modes

- Flexible system clock

- Ultrasafe reset: same reset strategy including power-on reset, power-down reset, brownout reset and programmable voltage detector.

### 2.2.4 Features

ST ultra-low-power continuum also lies in feature compatibility:

- More than 10 packages with pin count from 20 to 144 pins and size down to 3 x 3 mm

- Memory density ranging from 4 to 384 Kbytes

This dual digital Interface supports the following features:

- two DAC converters: one for each output channel

- left or right data alignment in 12-bit mode

- synchronized update capability

- noise-wave generation

- triangular-wave generation

- dual DAC channels' independent or simultaneous conversions

- DMA capability for each channel (including the underrun interrupt)

- external triggers for conversion

- input reference voltage V<sub>REF+</sub>

Eight DAC trigger inputs are used in the STM32L151x6/8/B and STM32L152x6/8/B devices. The DAC channels are triggered through the timer update outputs that are also connected to different DMA channels.

# 3.12 Ultra-low-power comparators and reference voltage

The STM32L151x6/8/B and STM32L152x6/8/B devices embed two comparators sharing the same current bias and reference voltage. The reference voltage can be internal or external (coming from an I/O).

- one comparator with fixed threshold

- one comparator with rail-to-rail inputs, fast or slow mode. The threshold can be one of the following:

- DAC output

- External I/O

- Internal reference voltage (V<sub>REFINT</sub>) or V<sub>REFINT</sub> submultiple (1/4, 1/2, 3/4)

Both comparators can wake up from Stop mode, and be combined into a window comparator.

The internal reference voltage is available externally via a low power / low current output buffer (driving current capability of 1  $\mu$ A typical).

# 3.13 Routing interface

This interface controls the internal routing of I/Os to TIM2, TIM3, TIM4 and to the comparator and reference voltage output.

# 3.14 Touch sensing

The STM32L151x6/8/B and STM32L152x6/8/B devices provide a simple solution for adding capacitive sensing functionality to any application. These devices offer up to 20 capacitive sensing channels distributed over 10 analog I/O groups. Only software capacitive sensing acquisition mode is supported.

Capacitive sensing technology is able to detect the presence of a finger near a sensor which is protected from direct touch by a dielectric (glass, plastic, ...). The capacitive variation introduced by the finger (or any conductive object) is measured using a proven

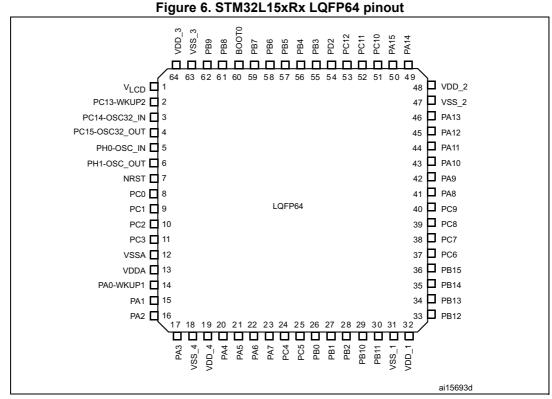

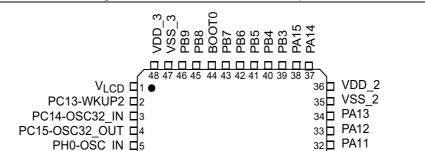

1. This figure shows the package top view.

LQFP48

31 PA10

30 PA9

29 PA8

28 PB15

27 PB14

26 PB13 25 PB12

Figure 7. STM32L15xCx LQFP48 pinout

This figure shows the package top view.

PH1-OSC\_OUT

NRST 7

VSSA 🔤 🛚

VDDA

PA1 11 PA2 12

PA0-WKUP1 10

ai15694d

|         |        | Pin     | S        |                    |                   |                         |               |                                                  | Pins functions                                           | inicaj                             |

|---------|--------|---------|----------|--------------------|-------------------|-------------------------|---------------|--------------------------------------------------|----------------------------------------------------------|------------------------------------|

| LQFP100 | LQFP64 | TFBGA64 | UFBGA100 | LQFP48 or UFQFPN48 | Pin name          | Pin type <sup>(1)</sup> | I/O structure | Main<br>function <sup>(2)</sup><br>(after reset) | Alternate functions                                      | Additional<br>functions            |

| 35      | 26     | F5      | M5       | 18                 | PB0               | I/O                     | TC            | PB0                                              | TIM3_CH3/LCD_SEG5                                        | ADC_IN8/<br>COMP1_INP/<br>VREF_OUT |

| 36      | 27     | G5      | M6       | 19                 | PB1               | I/O                     | FT            | PB1                                              | TIM3_CH4/LCD_SEG6                                        | ADC_IN9/<br>COMP1_INP/<br>VREF_OUT |

| 37      | 28     | G6      | L6       | 20                 | PB2               | I/O                     | FT            | PB2/BOOT1                                        | BOOT1                                                    | -                                  |

| 38      | -      | -       | M7       | -                  | PE7               | I/O                     | тс            | PE7                                              | -                                                        | ADC_IN22/<br>COMP1_INP             |

| 39      | -      | -       | L7       | -                  | PE8               | I/O                     | тс            | PE8                                              | -                                                        | ADC_IN23/<br>COMP1_INP             |

| 40      | -      | -       | M8       | -                  | PE9               | I/O                     | тс            | PE9                                              | TIM2_CH1_ETR                                             | ADC_IN24/<br>COMP1_INP             |

| 41      | -      | -       | L8       | -                  | PE10              | I/O                     | тс            | PE10                                             | TIM2_CH2                                                 | ADC_IN25/<br>COMP1_INP             |

| 42      | -      | -       | M9       | -                  | PE11              | I/O                     | FT            | PE11                                             | TIM2_CH3                                                 | -                                  |

| 43      | -      | -       | L9       | -                  | PE12              | I/O                     | FT            | PE12                                             | TIM2_CH4/SPI1_NSS                                        | -                                  |

| 44      | -      | -       | M10      | -                  | PE13              | I/O                     | FT            | PE13                                             | SPI1_SCK                                                 | -                                  |

| 45      | -      | -       | M11      | -                  | PE14              | I/O                     | FT            | PE14                                             | SPI1_MISO                                                | -                                  |

| 46      | -      | -       | M12      | -                  | PE15              | I/O                     | FT            | PE15                                             | SPI1_MOSI                                                | -                                  |

| 47      | 29     | G7      | L10      | 21                 | PB10              | I/O                     | FT            | PB10                                             | I2C2_SCL/USART3_TX/<br>TIM2_CH3/LCD_SEG10                | -                                  |

| 48      | 30     | H7      | L11      | 22                 | PB11              | I/O                     | FT            | PB11                                             | I2C2_SDA/USART3_RX/<br>TIM2_CH4/LCD_SEG11                | -                                  |

| 49      | 31     | D6      | F12      | 23                 | V <sub>SS_1</sub> | S                       | -             | V <sub>SS_1</sub>                                | -                                                        | -                                  |

| 50      | 32     | E6      | G12      | 24                 | V <sub>DD_1</sub> | S                       | -             | V <sub>DD_1</sub>                                | -                                                        | -                                  |

| 51      | 33     | H8      | L12      | 25                 | PB12              | I/O                     | FT            | PB12                                             | SPI2_NSS/I2C2_SMBA/<br>USART3_CK/<br>LCD_SEG12/TIM10_CH1 | ADC_IN18/<br>COMP1_INP             |

| 52      | 34     | G8      | K12      | 26                 | PB13              | I/O                     | FT            | PB13                                             | SPI2_SCK/USART3_CTS/<br>LCD_SEG13/<br>TIM9_CH1           | ADC_IN19/<br>COMP1_INP             |

# Table 8. STM32L151x6/8/B and STM32L152x6/8/B pin definitions (continued)

#### Table 9. Alternate function input/output Digital alternate function number AFIO0 AFIO1 AFIO2 AFIO3 AFIO4 AFIO5 AFOI6 AFIO8 AFIO9 AFIO11 AFIO12 AFIO13 AFIO14 AFIO15 AFIO7 Port name Alternate function TIM3/4 SPI1/2 SYSTEM TIM2 TIM9/10/11 I2C1/2 N/A **USART1/2/3** N/A N/A LCD N/A N/A RI SYSTEM BOOTO BOOT0 ----\_ -\_ \_ ---\_ \_ -NRST NRST --------------PA0-WKUP1 TIM2 CH1 ETR USART2 CTS TIMx IC1 EVENTOUT -----------PA1 -TIM2 CH2 -USART2 RTS -[SEG0] -TIMx IC2 EVENTOUT ------PA2 TIM2 CH3 TIM9 CH1 USART2\_TX [SEG1] TIMx\_IC3 EVENTOUT ---\_ -----PA3 TIMx\_IC4 EVENTOUT TIM2\_CH4 -TIM9 CH2 --USART2\_RX -[SEG2] -----TIMx\_IC1 EVENTOUT PA4 SPI1 NSS USART2 CK --------TIMx\_IC2 EVENTOUT PA5 TIM2 CH1 ETR SPI1 SCK ----------PA6 ТІМЗ СН1 TIM10 CH1 SPI1 MISO [SEG3] TIMx\_IC3 EVENTOUT ---------TIMx\_IC4 EVENTOUT PA7 TIM3\_CH2 TIM11 CH1 SPI1\_MOSI -[SEG4] --------TIMx\_IC1 EVENTOUT PA8 MCO --USART1\_CK -[COM0] -------PA9 USART1\_TX [COM1] TIMx\_IC2 EVENTOUT -----------TIMx\_IC3 EVENTOUT PA10 USART1\_RX -[COM2] ----------PA11 SPI1 MISO USART1\_CTS TIMx\_IC4 EVENTOUT -----------PA12 SPI1\_MOSI USART1\_RTS -TIMx\_IC1 EVENTOUT ----------JTMS-PA13 TIMx IC2 EVENTOUT -------SWDIO JTCK-TIMx\_IC3 EVENTOUT PA14 ---------SWCLK JTDI TIMx IC4 EVENTOUT PA15 TIM2 CH1 ETR SPI1 NSS SEG17 \_ . \_ ------PB0 ТІМЗ СНЗ [SEG5] EVENTOUT -----. ------PB1 TIM3 CH4 [SEG6] EVENTOUT ------------PB2 BOOT1 EVENTOUT -------------SPI1 SCK PB3 JTDO TIM2 CH2 [SEG7] EVENTOUT \_ . \_ . ------PB4 NJTRST TIM3 CH1 SPI1 MISO [SEG8] EVENTOUT ------. ---

43/133

Pin descriptions

# 6.3.3 Embedded internal reference voltage

The parameters given in the following table are based on characterization results, unless otherwise specified.

#### Table 15. Embedded internal reference voltage calibration values

| Calibration value name | Description                                                       | Memory address          |

|------------------------|-------------------------------------------------------------------|-------------------------|

| VREFINT_CAL            | Raw data acquired at temperature of 30 °C, V <sub>DDA</sub> = 3 V | 0x1FF8 0078-0x1FF8 0079 |

| Symbol                                   | Parameter                                                                                    | Conditions                                                                              | Min   | Тур   | Max   | Unit                  |

|------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------|-------|-------|-----------------------|

| V <sub>REFINT out</sub> <sup>(1)</sup>   | Internal reference voltage                                                                   | – 40 °C < T <sub>J</sub> < +105 °C                                                      | 1.202 | 1.224 | 1.242 | V                     |

| I <sub>REFINT</sub>                      | Internal reference current consumption                                                       | -                                                                                       | -     | 1.4   | 2.3   | μA                    |

| T <sub>VREFINT</sub>                     | Internal reference startup time                                                              | -                                                                                       | -     | 2     | 3     | ms                    |

| V <sub>VREF_MEAS</sub>                   | V <sub>DDA</sub> and V <sub>REF+</sub> voltage during<br>V <sub>REFINT</sub> factory measure | -                                                                                       | 2.99  | 3     | 3.01  | V                     |

| A <sub>VREF_MEAS</sub>                   | Accuracy of factory-measured $V_{REF}$ value $^{(2)}$                                        | Including uncertainties<br>due to ADC and<br>V <sub>DDA</sub> /V <sub>REF+</sub> values | -     | -     | ±5    | mV                    |

| T <sub>Coeff</sub> <sup>(3)</sup>        | Temperature coefficient                                                                      | –40 °C < T <sub>J</sub> < +105 °C                                                       | -     | 25    | 100   | ppm/°C                |

| A <sub>Coeff</sub> <sup>(3)</sup>        | Long-term stability                                                                          | 1000 hours, T= 25 °C                                                                    | -     | -     | 1000  | ppm                   |

| V <sub>DDCoeff</sub> <sup>(3)</sup>      | Voltage coefficient                                                                          | 3.0 V < V <sub>DDA</sub> < 3.6 V                                                        | -     | -     | 2000  | ppm/V                 |

| T <sub>S_vrefint</sub> <sup>(3)(4)</sup> | ADC sampling time when reading the internal reference voltage                                | -                                                                                       | 5     | 10    | -     | μs                    |

| T <sub>ADC_BUF</sub> <sup>(3)</sup>      | Startup time of reference voltage buffer for ADC                                             | -                                                                                       | -     | -     | 10    | μs                    |

| I <sub>BUF_ADC</sub> <sup>(3)</sup>      | Consumption of reference voltage buffer for ADC                                              | -                                                                                       | -     | 13.5  | 25    | μA                    |

| I <sub>VREF_OUT</sub> <sup>(3)</sup>     | VREF_OUT output current <sup>(5)</sup>                                                       | -                                                                                       | -     | -     | 1     | μA                    |

| C <sub>VREF_OUT</sub> <sup>(3)</sup>     | VREF_OUT output load                                                                         | -                                                                                       | -     | -     | 50    | pF                    |

| I <sub>LPBUF</sub> <sup>(3)</sup>        | Consumption of reference voltage buffer for VREF_OUT and COMP                                | -                                                                                       | -     | 730   | 1200  | nA                    |

| V <sub>REFINT_DIV1</sub> <sup>(3)</sup>  | 1/4 reference voltage                                                                        | -                                                                                       | 24    | 25    | 26    |                       |

| V <sub>REFINT_DIV2</sub> <sup>(3)</sup>  | 1/2 reference voltage                                                                        | -                                                                                       | 49    | 50    | 51    | % V <sub>REFINT</sub> |

| V <sub>REFINT_DIV3</sub> <sup>(3)</sup>  | 3/4 reference voltage                                                                        | -                                                                                       | 74    | 75    | 76    |                       |

#### Table 16. Embedded internal reference voltage

1. Tested in production.

2. The internal  $V_{REF}$  value is individually measured in production and stored in dedicated EEPROM bytes.

3. Guaranteed by characterization results.

4. Shortest sampling time can be determined in the application by multiple iterations.

5. To guarantee less than 1% VREF\_OUT deviation.

| Symbol               | Parameter               | Cons                                                | litions                                               | £       | Turn  |        | Unit |      |    |  |

|----------------------|-------------------------|-----------------------------------------------------|-------------------------------------------------------|---------|-------|--------|------|------|----|--|

| Symbol Parameter     | Cond                    | fhclk                                               | Тур                                                   | 55 °C   | 85 °C | 105 °C | Unit |      |    |  |

| Supply               |                         |                                                     | Range 3,                                              | 1 MHz   | 270   | 400    | 400  | 400  |    |  |

|                      |                         |                                                     | V <sub>CORE</sub> =1.2 V                              | 2 MHz   | 470   | 600    | 600  | 600  | μA |  |

|                      |                         | f <sub>HSE</sub> = f <sub>HCLK</sub>                | VOS[1:0] = 11                                         | 4 MHz   | 890   | 1025   | 1025 | 1025 |    |  |

|                      |                         | up to 16 MHz,                                       | Range 2,                                              | 4 MHz   | 1     | 1.3    | 1.3  | 1.3  |    |  |

|                      |                         | included<br>f <sub>HSE</sub> = f <sub>HCLK</sub> /2 | V <sub>CORE</sub> =1.5 V                              | 8 MHz   | 2     | 2.5    | 2.5  | 2.5  | -  |  |

|                      |                         | above 16 MHz<br>(PLL ON) <sup>(2)</sup>             | VOS[1:0] = 10                                         | 16 MHz  | 3.9   | 5      | 5    | 5    |    |  |

|                      | Supply                  |                                                     | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | 8 MHz   | 2.16  | 3      | 3    | 3    |    |  |

| I <sub>DD (Run</sub> | current in<br>Run mode, |                                                     |                                                       | 16 MHz  | 4.8   | 5.5    | 5.5  | 5.5  |    |  |

| from                 | code                    |                                                     |                                                       | 32 MHz  | 9.6   | 11     | 11   | 11   |    |  |

| _                    |                         |                                                     | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | 16 MHz  | 4     | 5      | 5    | 5    | mA |  |

|                      |                         |                                                     | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | 32 MHz  | 9.4   | 11     | 11   | 11   |    |  |

|                      |                         | MSI clock, 65 kHz                                   | Range 3,                                              | 65 kHz  | 0.05  | 0.085  | 0.09 | 0.1  | 1  |  |

|                      |                         | MSI clock, 524 kHz                                  | V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11             | 524 kHz | 0.15  | 0.185  | 0.19 | 0.2  |    |  |

|                      |                         | MSI clock, 4.2 MHz                                  |                                                       | 4.2 MHz | 0.9   | 1      | 1    | 1    |    |  |

1. Guaranteed by characterization results, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

57

|            |                    | Typica                                                |                                                       |                                                       |                         |                                |

|------------|--------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------|--------------------------------|

| Peripheral |                    | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | Range 3,<br>V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | Low power sleep and run | Unit                           |

|            | TIM2               | 13                                                    | 10.5                                                  | 8                                                     | 10.5                    |                                |

|            | TIM3               | 14                                                    | 12                                                    | 9                                                     | 12                      |                                |

|            | TIM4               | 12.5                                                  | 10.5                                                  | 8                                                     | 11                      |                                |

|            | TIM6               | 5.5                                                   | 4.5                                                   | 3.5                                                   | 4.5                     |                                |

|            | TIM7               | 5.5                                                   | 5                                                     | 3.5                                                   | 4.5                     |                                |

|            | LCD                | 5.5                                                   | 5                                                     | 3.5                                                   | 5                       |                                |

|            | WWDG               | 4                                                     | 3.5                                                   | 2.5                                                   | 3.5                     |                                |

| APB1       | SPI2               | 5.5                                                   | 5                                                     | 4                                                     | 5                       | µA/MHz                         |

| AFDI       | USART2             | 9                                                     | 8                                                     | 5.5                                                   | 8.5                     | (f <sub>HCLK</sub> )           |

|            | USART3             | 10.5                                                  | 9                                                     | 6                                                     | 8                       |                                |

|            | I2C1               | 8.5                                                   | 7                                                     | 5.5                                                   | 7.5                     |                                |

|            | 12C2               | 8.5                                                   | 7                                                     | 5.5                                                   | 6.5                     |                                |

|            | USB                | 12.5                                                  | 10                                                    | 6.5                                                   | 10                      |                                |

|            | PWR                | 4.5                                                   | 4                                                     | 3                                                     | 3.5                     |                                |

|            | DAC                | 9                                                     | 7.5                                                   | 6                                                     | 7                       |                                |

|            | COMP               | 4.5                                                   | 4                                                     | 3.5                                                   | 4.5                     |                                |

|            | SYSCFG & RI        | 3                                                     | 2.5                                                   | 2                                                     | 2.5                     |                                |

|            | TIM9               | 9                                                     | 7.5                                                   | 6                                                     | 7                       |                                |

|            | TIM10              | 6.5                                                   | 5.5                                                   | 4.5                                                   | 5.5                     |                                |

| APB2       | TIM11              | 7                                                     | 6                                                     | 4.5                                                   | 5.5                     | µA/MHz<br>(f <sub>HCLK</sub> ) |

|            | ADC <sup>(2)</sup> | 11.5                                                  | 9.5                                                   | 8                                                     | 9                       | VIIULK/                        |

|            | SPI1               | 5                                                     | 4.5                                                   | 3                                                     | 4                       |                                |

|            | USART1             | 9                                                     | 7.5                                                   | 6                                                     | 7.5                     |                                |

Table 24. Peripheral current consumption<sup>(1)</sup>

#### 6.3.5 Wakeup time from Low power mode

The wakeup times given in the following table are measured with the MSI RC oscillator. The clock source used to wake up the device depends on the current operating mode:

- Sleep mode: the clock source is the clock that was set before entering Sleep mode

- Stop mode: the clock source is the MSI oscillator in the range configured before entering Stop mode

- Standby mode: the clock source is the MSI oscillator running at 2.1 MHz

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 13*.

| Symbol               | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                 | Conditions                                      | Тур  | Max <sup>(1)</sup> | Unit |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------|--------------------|------|

| t <sub>WUSLEEP</sub> | Wakeup from Sleep mode                                                                                                                                                                                                                                                                                                                                                                                                    | f <sub>HCLK</sub> = 32 MHz                      | 0.36 | -                  |      |

| twusleep_lp          | Wakeup from Low power                                                                                                                                                                                                                                                                                                                                                                                                     | f <sub>HCLK</sub> = 262 kHz<br>Flash enabled    | 32   | -                  |      |

| 'WUSLEEP_LP          | Wakeup from Sleep mode $f_{HCLK} = 32 \text{ MHz}$ Wakeup from Low power<br>sleep mode<br>$f_{HCLK} = 262 \text{ kHz}$ $f_{HCLK} = 262 \text{ kHz}$ Flash enabled $f_{HCLK} = 262 \text{ kHz}$ Flash switched OFFWakeup from Stop mode,<br>regulator in Run mode $f_{HCLK} = f_{MSI} = 4.2 \text{ MHz}$ Wakeup from Stop mode,<br>regulator in Run mode $f_{HCLK} = f_{MSI} = 4.2 \text{ MHz}$ Wakeup from Stop mode,<br> | 34                                              | -    |                    |      |

|                      | Wakeup from Stop mode, regulator in Run mode                                                                                                                                                                                                                                                                                                                                                                              | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz  | 8.2  | -                  |      |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                 | 8.2  | 9.3                |      |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                 | 7.8  | 11.2               | μs   |

| t <sub>WUSTOP</sub>  | Wakeup from Stop mode,<br>regulator in low power<br>mode                                                                                                                                                                                                                                                                                                                                                                  | f <sub>HCLK</sub> = f <sub>MSI</sub> = 2.1 MHz  | 10   | 12                 |      |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                           | f <sub>HCLK</sub> = f <sub>MSI</sub> = 1.05 MHz | 15.5 | 20                 |      |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                           | f <sub>HCLK</sub> = f <sub>MSI</sub> = 524 kHz  | 29   | 35                 |      |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                           | f <sub>HCLK</sub> = f <sub>MSI</sub> = 262 kHz  | 53   | 63                 |      |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                           | f <sub>HCLK</sub> = f <sub>MSI</sub> = 131 kHz  | 105  | 118                |      |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                           | f <sub>HCLK</sub> = MSI = 65 kHz                | 210  | 237                |      |

| t                    | Wakeup from Standby<br>mode<br>FWU bit = 1                                                                                                                                                                                                                                                                                                                                                                                | f <sub>HCLK</sub> = MSI = 2.1 MHz               | 50   | 103                |      |

| <sup>t</sup> wustdby | Wakeup from Standby<br>mode<br>FWU bit = 0                                                                                                                                                                                                                                                                                                                                                                                | f <sub>HCLK</sub> = MSI = 2.1 MHz               | 2.5  | 3.2                | ms   |

Table 25. Low-power mode wakeup timings

1. Guaranteed by characterization results, unless otherwise specified

| Symbol                                  | Parameter                          | Condition                                | Тур | Мах   | Unit |

|-----------------------------------------|------------------------------------|------------------------------------------|-----|-------|------|

|                                         |                                    | MSI range 0                              | -   | 40 20 |      |

|                                         |                                    | MSI range 1                              | -   | 20    |      |

|                                         |                                    | MSI range 2                              | -   | 10    |      |

|                                         |                                    | MSI range 3                              | -   | 4     |      |

| t <sub>STAB(MSI)</sub> <sup>(2)</sup> I | MSI oscillator stabilization time  | MSI range 4                              | -   | 2.5   | μs   |

|                                         |                                    | MSI range 5                              | -   | 2     |      |

|                                         |                                    | MSI range 6,<br>Voltage range 1<br>and 2 | -   | 2     |      |

|                                         |                                    | MSI range 3,<br>Voltage Range 3          | -   | 3     |      |

| 4                                       | MSI oscillator frequency overshoot | Any range to range 5                     | -   | 4     | MHz  |

| f <sub>OVER(MSI)</sub>                  |                                    | Any range to range 6                     | -   | 6     |      |

Table 32. MSI oscillator characteristics (continued)

1. This is a deviation for an individual part, once the initial frequency has been measured.

2. Guaranteed by characterization results.

### 6.3.8 PLL characteristics

The parameters given in *Table 33* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 13*.

| Cumhal                 | Parameter                                                         |     | Unit |                    |        |

|------------------------|-------------------------------------------------------------------|-----|------|--------------------|--------|

| Symbol                 | Parameter                                                         | Min | Тур  | Max <sup>(1)</sup> | - Unit |

| 4                      | PLL input clock <sup>(2)</sup>                                    | 2   | -    | 24                 | MHz    |

| f <sub>PLL_IN</sub>    | PLL input clock duty cycle                                        | 45  | -    | 55                 | %      |

| f <sub>PLL_OUT</sub>   | PLL output clock                                                  | 2   | -    | 32                 | MHz    |

| t <sub>LOCK</sub>      | Worst case PLL lock time<br>PLL input = 2 MHz<br>PLL VCO = 96 MHz | -   | 100  | 130                | μs     |

| Jitter                 | Cycle-to-cycle jitter                                             | -   | -    | ± 600              | ps     |

| I <sub>DDA</sub> (PLL) | Current consumption on V <sub>DDA</sub>                           | -   | 220  | 450                |        |

| I <sub>DD</sub> (PLL)  | Current consumption on V <sub>DD</sub>                            | -   | 120  | 150                | - μΑ   |

1. Guaranteed by characterization results.

2. Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by  $f_{\mathsf{PLL\_OUT}}$ .

#### 6.3.10 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table* 37. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                                                                                                                            | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, LQFP100, T <sub>A</sub> = +25 °C,<br>f <sub>HCLK</sub> = 32 MHz<br>conforms to IEC 61000-4-2                                                                                                        | 2B              |

| V <sub>eftb</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $\label{eq:VDD} \begin{array}{l} V_{DD} = 3.3 \text{ V}, \text{ LQFP100}, \text{ T}_{\text{A}} = +25 \\ ^{\circ}\text{C}, \\ \text{f}_{\text{HCLK}} = 32 \text{ MHz} \\ \text{conforms to IEC 61000-4-4} \end{array}$ | 4A              |

Table 37. EMS characteristics

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the oscillator pins for 1 second.

#### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latch-up standard.

| Table 40. | Electrical | sensitivities  |

|-----------|------------|----------------|

|           | LICCUITCUI | 30113111411103 |

| Symbol | Parameter             | Conditions                            | Class      |

|--------|-----------------------|---------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +105$ °C conforming to JESD78A | II level A |

#### 6.3.12 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error, out of spec current injection on adjacent pins or other functional failure (for example reset, oscillator frequency deviation, LCD levels, etc.).

The test results are given in Table 41.

#### Table 41. I/O current injection susceptibility

|                  |                                                | Functional s       |                    |      |  |

|------------------|------------------------------------------------|--------------------|--------------------|------|--|

| Symbol           | Description                                    | Negative injection | Positive injection | Unit |  |

|                  | Injected current on all 5 V tolerant (FT) pins | -5                 | +0                 | mA   |  |

| I <sub>INJ</sub> | Injected current on any other pin              | -5                 | +5                 | IIIA |  |

*Note:* It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

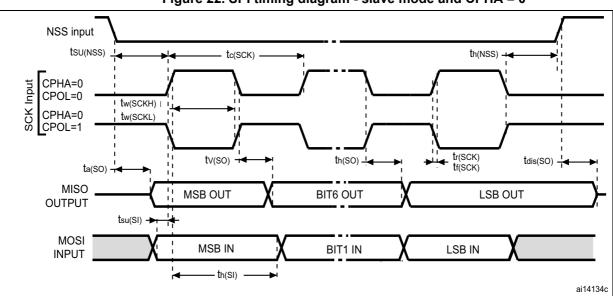

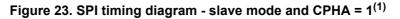

Figure 22. SPI timing diagram - slave mode and CPHA = 0

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}$

# 6.3.21 LCD controller (STM32L152xx only)

The STM32L152xx embeds a built-in step-up converter to provide a constant LCD reference voltage independently from the V<sub>DD</sub> voltage. An external capacitor C<sub>ext</sub> must be connected to the V<sub>LCD</sub> pin to decouple this converter.

| Symbol                           | Parameter                                                | Min  | Тур                  | Max       | Unit |

|----------------------------------|----------------------------------------------------------|------|----------------------|-----------|------|

| $V_{LCD}$                        | LCD external voltage                                     | -    | -                    | 3.6       |      |

| V <sub>LCD0</sub>                | LCD internal reference voltage 0                         | -    | 2.6                  | -         |      |

| V <sub>LCD1</sub>                | LCD internal reference voltage 1                         | -    | 2.73                 | -         |      |

| V <sub>LCD2</sub>                | LCD internal reference voltage 2                         | -    | 2.86                 | -         |      |

| $V_{LCD3}$                       | LCD internal reference voltage 3                         | -    | 2.98                 | -         | V    |

| V <sub>LCD4</sub>                | LCD internal reference voltage 4                         | -    | 3.12                 | -         |      |

| $V_{LCD5}$                       | LCD internal reference voltage 5                         | -    | 3.26                 | -         | Ţ    |

| V <sub>LCD6</sub>                | LCD internal reference voltage 6                         | -    | 3.4                  | -         |      |

| $V_{LCD7}$                       | LCD internal reference voltage 7                         | -    | 3.55                 | -         | Ţ    |

| C <sub>ext</sub>                 | V <sub>LCD</sub> external capacitance                    | 0.1  | -                    | 2         | μF   |

| I <sub>LCD</sub> <sup>(1)</sup>  | Supply current at V <sub>DD</sub> = 2.2 V                | -    | 3.3                  | -         |      |

|                                  | Supply current at V <sub>DD</sub> = 3.0 V                | -    | 3.1                  | -         | μA   |

| R <sub>Htot</sub> <sup>(2)</sup> | Low drive resistive network overall value                | 5.28 | 6.6                  | 7.92      | MΩ   |

| $R_L^{(2)}$                      | High drive resistive network total value                 | 192  | 240                  | 288       | kΩ   |

| V <sub>44</sub>                  | Segment/Common highest level voltage                     | -    | -                    | $V_{LCD}$ | V    |

| V <sub>34</sub>                  | Segment/Common 3/4 level voltage                         | -    | 3/4 V <sub>LCD</sub> | -         |      |

| V <sub>23</sub>                  | Segment/Common 2/3 level voltage                         | -    | 2/3 V <sub>LCD</sub> | -         |      |

| V <sub>12</sub>                  | Segment/Common 1/2 level voltage                         | -    | 1/2 V <sub>LCD</sub> | -         | V    |

| V <sub>13</sub>                  | Segment/Common 1/3 level voltage                         | -    | 1/3 V <sub>LCD</sub> | -         |      |

| V <sub>14</sub>                  | Segment/Common 1/4 level voltage                         | -    | 1/4 V <sub>LCD</sub> | -         | 1    |

| V <sub>0</sub>                   | Segment/Common lowest level voltage                      | 0    | -                    | -         | 1    |

| $\Delta Vxx^{(3)}$               | Segment/Common level voltage error $T_A$ = -40 to 85 ° C | -    | -                    | ±50       | mV   |

|  | Table 62 | . LCD | controller | characteristics |

|--|----------|-------|------------|-----------------|

|--|----------|-------|------------|-----------------|

1. LCD enabled with 3 V internal step-up active, 1/8 duty, 1/4 bias, division ratio= 64, all pixels active, no LCD connected

2. Guaranteed by design.

3. Guaranteed by characterization results.

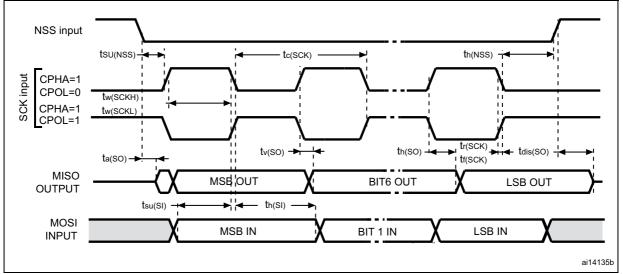

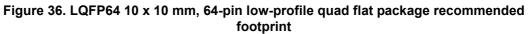

# Figure 33. LQPF100 14 x 14 mm, 100-pin low-profile quad flat package recommended footprint

1. Dimensions are in millimeters.

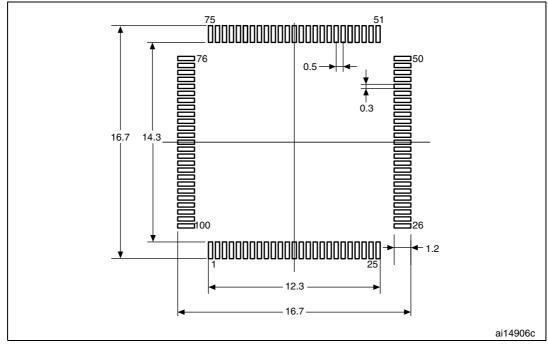

#### LQFP100 device marking

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Figure 34. LQFP100 14 x 14 mm, 100-pin package top view example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

|        | Min         | Тур   | Max   | Тур                   | Min    | Мах    |

| E3     | -           | 7.500 | -     | -                     | 0.2953 | -      |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |

| К      | 0°          | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |

| L      | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000 | -     | -                     | 0.0394 | -      |

| CCC    | -           | -     | 0.080 | -                     | -      | 0.0031 |

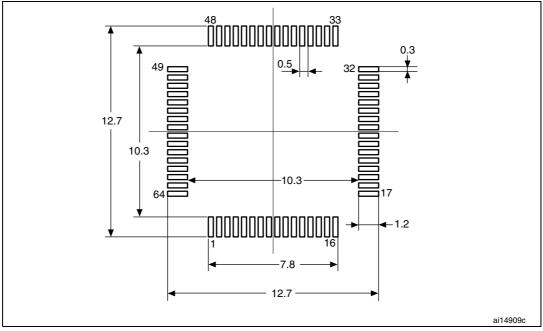

# Table 64. LQFP64 10 x 10 mm, 64-pin low-profile quad flat package mechanicaldata (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are in millimeters.

# 7.4 UFQFPN48 7 x 7 mm, 0.5 mm pitch, package information

Figure 41. UFQFPN48 7 x 7 mm, 0.5 mm pitch, package outline

1. Drawing is not to scale.

- 2. All leads/pads should also be soldered to the PCB to improve the lead/pad solder joint life.

- 3. There is an exposed die pad on the underside of the UFQFPN package. It is recommended to connect and solder this back-side pad to PCB ground.

# 7.7 Thermal characteristics

The maximum chip-junction temperature,  $T_J$  max, in degrees Celsius, may be calculated using the following equation:

$T_J \max = T_A \max + (P_D \max \times \Theta_{JA})$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in ° C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

P<sub>I/O</sub> max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I}/\mathsf{O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

| Symbol          | Parameter                                                                  | Value | Unit |

|-----------------|----------------------------------------------------------------------------|-------|------|

|                 | Thermal resistance junction-ambient<br>BGA100 - 7 x 7 mm                   | 59    |      |

| Θ <sub>JA</sub> | Thermal resistance junction-ambient<br>LQFP100 - 14 x 14 mm / 0.5 mm pitch | 46    |      |

|                 | <b>Thermal resistance junction-ambient</b><br>TFBGA64 - 5 x 5 mm           | 65    | °C/W |

|                 | Thermal resistance junction-ambient<br>LQFP64 - 10 x 10 mm / 0.5 mm pitch  | 45    | C/w  |

|                 | Thermal resistance junction-ambient<br>LQFP48 - 7 x 7 mm / 0.5 mm pitch    | 55    |      |

|                 | Thermal resistance junction-ambient<br>UFQFPN48 - 7 x 7 mm / 0.5 mm pitch  | 16    |      |

Table 71. Thermal characteristics

# 8 Ordering information

| Table 72. Ordering                                  | information | on scheme |       |   |

|-----------------------------------------------------|-------------|-----------|-------|---|

| Example:                                            | STM32       | L 151 C 8 | T 6 7 |   |

| Device family                                       |             |           |       |   |

| STM32 = ARM-based 32-bit microcontroller            |             |           |       |   |

| Product type                                        |             |           |       |   |

| L = Low power                                       |             |           |       |   |

| Device subfamily                                    |             |           |       |   |

| 151: Devices without LCD                            |             |           |       |   |

| 152: Devices with LCD                               |             |           |       |   |

| 132. Devices with ECD                               |             |           |       |   |

| Pin count                                           |             |           |       |   |

| C = 48 pins                                         |             |           |       |   |

| R = 64 pins                                         |             |           |       |   |

| V = 100 pins                                        |             |           |       |   |

| Flash memory size                                   |             |           |       |   |

| 6 = 32 Kbytes of Flash memory                       |             |           |       |   |

| 8 = 64 Kbytes of Flash memory                       |             |           |       |   |

| B = 128 Kbytes of Flash memory                      |             |           |       |   |

| Package                                             |             |           |       |   |

| H = BGA                                             |             |           |       |   |

| T = LQFP                                            |             |           |       |   |

| U = UFQFPN                                          |             |           |       |   |

| Temperature range                                   |             |           |       |   |

| 6 = Industrial temperature range, -40 to 85 °C      |             |           | 1     |   |

| Options                                             |             |           |       |   |

| No character = $V_{DD}$ range: 1.8 to 3.6 V and BOF | R enabled   |           |       | • |

| T = $V_{DD}$ range: 1.65 to 3.6 V and BOR disabled  |             |           |       |   |

| Packing                                             |             |           |       |   |

TR = tape and reel No character = tray or tube

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.

DocID17659 Rev 12