Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Not For New Designs                                                          |

| Core Processor             | ARM® Cortex®-M3                                                              |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                         |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT |

| Number of I/O              | 51                                                                           |

| Program Memory Size        | 128KB (128K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 4K x 8                                                                       |

| RAM Size                   | 16K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 20x12b; D/A 2x12b                                                        |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 64-LQFP                                                                      |

| Supplier Device Package    | 64-LQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l152rbt6        |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## List of figures

| Figure 1.                 | Ultra-low-power STM32L151x6/8/B and STM32L152x6/8/B block diagram                            | 13    |

|---------------------------|----------------------------------------------------------------------------------------------|-------|

| Figure 2.                 | Clock tree                                                                                   |       |

| Figure 3.                 | STM32L15xVx UFBGA100 ballout                                                                 | 31    |

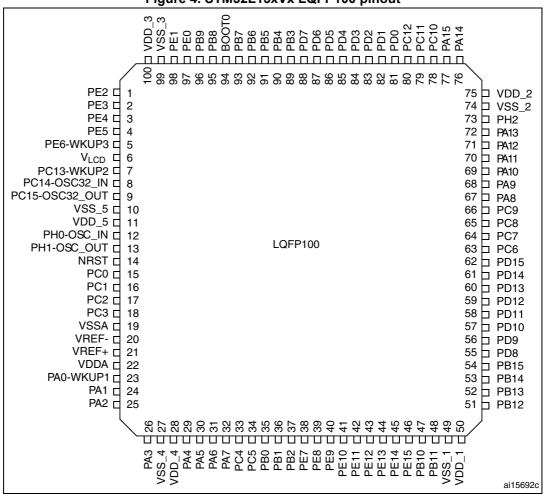

| Figure 4.                 | STM32L15xVx LQFP100 pinout                                                                   | 32    |

| Figure 5.                 | STM32L15xRx TFBGA64 ballout                                                                  |       |

| Figure 6.                 | STM32L15xRx LQFP64 pinout                                                                    |       |

| Figure 7.                 | STM32L15xCx LQFP48 pinout                                                                    |       |

| Figure 8.                 | STM32L15xCx UFQFPN48 pinout                                                                  |       |

| Figure 9.                 | Memory map                                                                                   |       |

| Figure 10.                | Pin loading conditions.                                                                      |       |

| Figure 11.                | Pin input voltage                                                                            |       |

| Figure 12.                | Power supply scheme.                                                                         |       |

| Figure 13.                | Optional LCD power supply scheme                                                             |       |

| Figure 14.                | Current consumption measurement scheme                                                       |       |

| Figure 15.                | High-speed external clock source AC timing diagram                                           |       |

| Figure 16.                | Low-speed external clock source AC timing diagram                                            |       |

| Figure 17.                | HSE oscillator circuit diagram                                                               |       |

| Figure 18.                | Typical application with a 32.768 kHz crystal                                                |       |

| Figure 18.                | I/O AC characteristics definition                                                            |       |

| •                         | Recommended NRST pin protection                                                              |       |

| Figure 20.                |                                                                                              |       |

| Figure 21.                | I <sup>2</sup> C bus AC waveforms and measurement circuit                                    |       |

| Figure 22.                | SPI timing diagram - slave mode and CPHA = $0$                                               |       |

| Figure 23.                | SPI timing diagram - slave mode and CPHA = $1^{(1)}$                                         | 90    |

| Figure 24.                | SPI timing diagram - master mode <sup>(1)</sup>                                              |       |

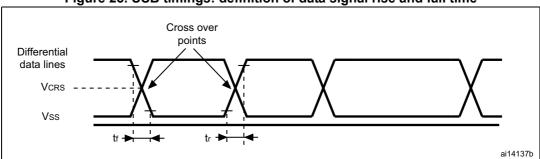

| Figure 25.                | USB timings: definition of data signal rise and fall time                                    |       |

| Figure 26.                | ADC accuracy characteristics                                                                 | 96    |

| Figure 27.                | Typical connection diagram using the ADC                                                     | 96    |

| Figure 28.                | Maximum dynamic current consumption on V <sub>REF+</sub> supply pin during ADC               |       |

|                           | conversion                                                                                   |       |

| Figure 29.                | Power supply and reference decoupling (V <sub>REF+</sub> not connected to V <sub>DDA</sub> ) |       |

| Figure 30.                | Power supply and reference decoupling (V <sub>REF+</sub> connected to V <sub>DDA</sub> )     | 98    |

| Figure 31.                | 12-bit buffered /non-buffered DAC                                                            |       |

| Figure 32.                | LQFP100 14 x 14 mm, 100-pin low-profile quad flat package outline                            | . 105 |

| Figure 33.                | LQPF100 14 x 14 mm, 100-pin low-profile quad flat package recommended footprint .            | . 107 |

| Figure 34.                | LQFP100 14 x 14 mm, 100-pin package top view example                                         | . 107 |

| Figure 35.                | LQFP64 10 x 10 mm, 64-pin low-profile quad flat package outline                              | . 108 |

| Figure 36.                | LQFP64 10 x 10 mm, 64-pin low-profile quad flat package recommended footprint                | . 109 |

| Figure 37.                | LQFP64 10 x 10 mm, 64-pin low-profile quad flat package top view example                     |       |

| Figure 38.                | LQFP48 7 x 7 mm, 48-pin low-profile quad flat package outline                                |       |

| Figure 39.                | LQFP48 7 x 7 mm, 48-pin low-profile quad flat recommended footprint.                         |       |

| Figure 40.                | LQFP48 7 x 7 mm, 48-pin low-profile quad flat package top view example                       |       |

| Figure 41.                | UFQFPN48 7 x 7 mm, 0.5 mm pitch, package outline                                             |       |

| Figure 42.                | UFQFPN48 7 x 7 mm, 0.5 mm pitch, package recommended footprint                               | 115   |

| Figure 43.                | UFQFPN48 7 x 7 mm, 0.5 mm pitch, package top view example                                    | 116   |

| Figure 44.                | UFBGA100, 7 x 7 mm, 0.5 mm pitch, package outline                                            |       |

| Figure 45.                | UFBGA100 7 x 7 mm, 0.5 mm pitch, package recommended footprint                               | 118   |

| Figure 46.                | UFBGA100 7 x 7 mm, 0.5 mm pitch, package top view example.                                   |       |

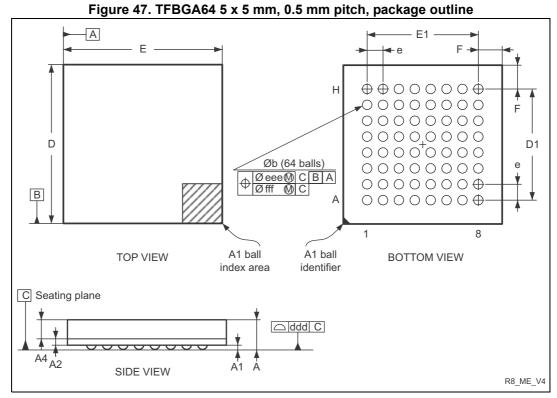

| Figure 40.<br>Figure 47.  | TFBGA64 5 x 5 mm, 0.5 mm pitch, package outline                                              |       |

| $r_{i}$ guie $\tau_{i}$ . |                                                                                              | . 120 |

This dual digital Interface supports the following features:

- two DAC converters: one for each output channel

- left or right data alignment in 12-bit mode

- synchronized update capability

- noise-wave generation

- triangular-wave generation

- dual DAC channels' independent or simultaneous conversions

- DMA capability for each channel (including the underrun interrupt)

- external triggers for conversion

- input reference voltage V<sub>REF+</sub>

Eight DAC trigger inputs are used in the STM32L151x6/8/B and STM32L152x6/8/B devices. The DAC channels are triggered through the timer update outputs that are also connected to different DMA channels.

## 3.12 Ultra-low-power comparators and reference voltage

The STM32L151x6/8/B and STM32L152x6/8/B devices embed two comparators sharing the same current bias and reference voltage. The reference voltage can be internal or external (coming from an I/O).

- one comparator with fixed threshold

- one comparator with rail-to-rail inputs, fast or slow mode. The threshold can be one of the following:

- DAC output

- External I/O

- Internal reference voltage (V<sub>REFINT</sub>) or V<sub>REFINT</sub> submultiple (1/4, 1/2, 3/4)

Both comparators can wake up from Stop mode, and be combined into a window comparator.

The internal reference voltage is available externally via a low power / low current output buffer (driving current capability of 1  $\mu$ A typical).

## 3.13 Routing interface

This interface controls the internal routing of I/Os to TIM2, TIM3, TIM4 and to the comparator and reference voltage output.

## 3.14 Touch sensing

The STM32L151x6/8/B and STM32L152x6/8/B devices provide a simple solution for adding capacitive sensing functionality to any application. These devices offer up to 20 capacitive sensing channels distributed over 10 analog I/O groups. Only software capacitive sensing acquisition mode is supported.

Capacitive sensing technology is able to detect the presence of a finger near a sensor which is protected from direct touch by a dielectric (glass, plastic, ...). The capacitive variation introduced by the finger (or any conductive object) is measured using a proven

Figure 4. STM32L15xVx LQFP100 pinout

1. This figure shows the package top view.

| Symbol            | Parameter                     | Conditions                                | Min  | Тур  | Max  | Unit |

|-------------------|-------------------------------|-------------------------------------------|------|------|------|------|

| V                 | Programmable voltage detector | Falling edge                              | 1.8  | 1.85 | 1.88 |      |

| V <sub>PVD0</sub> | threshold 0                   | Rising edge                               | 1.88 | 1.94 | 1.99 |      |

| V                 | PVD threshold 1               | Falling edge                              | 1.98 | 2.04 | 2.09 |      |

| V <sub>PVD1</sub> |                               | Rising edge                               | 2.08 | 2.14 | 2.18 |      |

| V                 | PVD threshold 2               | Falling edge                              | 2.20 | 2.24 | 2.28 |      |

| V <sub>PVD2</sub> |                               | Rising edge                               | 2.28 | 2.34 | 2.38 |      |

| V                 | PVD threshold 3               | Falling edge                              | 2.39 | 2.44 | 2.48 | V    |

| V <sub>PVD3</sub> |                               | Rising edge                               | 2.47 | 2.54 | 2.58 | v    |

| M                 | PVD threshold 4               | Falling edge                              | 2.57 | 2.64 | 2.69 |      |

| V <sub>PVD4</sub> |                               | Rising edge                               | 2.68 | 2.74 | 2.79 |      |

| V                 | PVD threshold 5               | Falling edge                              | 2.77 | 2.83 | 2.88 |      |

| $V_{PVD5}$        |                               | Rising edge                               | 2.87 | 2.94 | 2.99 |      |

| V                 | DVD threshold 6               | Falling edge                              | 2.97 | 3.05 | 3.09 |      |

| V <sub>PVD6</sub> | PVD threshold 6               | Rising edge                               | 3.08 | 3.15 | 3.20 |      |

|                   |                               | BOR0 threshold                            | -    | 40   | -    |      |

| V <sub>hyst</sub> | Hysteresis voltage            | All BOR and PVD thresholds excepting BOR0 | -    | 100  | -    | mV   |

Table 14. Embedded reset and power control block characteristics (continued)

1. Guaranteed by characterization results.

2. Valid for device version without BOR at power up. Please see option "T" in Ordering information scheme for more details.

|                                            |           | Туріса                                                | l consumption,                                        | V <sub>DD</sub> = 3.0 V, T <sub>A</sub>               | = 25 °C   |                      |  |

|--------------------------------------------|-----------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-----------|----------------------|--|

| Peri                                       | pheral    | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | Range 3,<br>V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | DRE=1.2 V | Unit                 |  |

|                                            | GPIOA     | 5                                                     | 4.5                                                   | 3.5                                                   | 4         |                      |  |

|                                            | GPIOB     | 5                                                     | 4.5                                                   | 3.5                                                   | 4.5       |                      |  |

|                                            | GPIOC     | 5                                                     | 4.5                                                   | 3.5                                                   | 4.5       |                      |  |

|                                            | GPIOD     | 5                                                     | 4.5                                                   | 3.5                                                   | 4.5       |                      |  |

| AHB                                        | GPIOE     | 5                                                     | 4.5                                                   | 3.5                                                   | 4.5       | µA/MHz               |  |

|                                            | GPIOH     | 4                                                     | 4                                                     | 3                                                     | 3.5       | (f <sub>HCLK</sub> ) |  |

|                                            | CRC       | 1                                                     | 0.5                                                   | 0.5                                                   | 0.5       |                      |  |

|                                            | FLASH     | 13                                                    | 11.5                                                  | 9                                                     | 18.5      |                      |  |

|                                            | DMA1      | 12                                                    | 10                                                    | 8                                                     | 10.5      |                      |  |

| All enabled                                |           | 166                                                   | 138                                                   | 106                                                   | 130       |                      |  |

| I <sub>DD (RTC)</sub>                      |           |                                                       |                                                       |                                                       |           |                      |  |

| I <sub>DD (LCD)</sub>                      |           |                                                       |                                                       |                                                       |           |                      |  |

| I <sub>DD (ADC)</sub> <sup>(3)</sup>       |           |                                                       |                                                       |                                                       |           |                      |  |

| I <sub>DD (DAC)</sub> <sup>(4)</sup>       |           |                                                       |                                                       |                                                       |           |                      |  |

| IDD (COMP1)                                |           |                                                       | μA                                                    |                                                       |           |                      |  |

|                                            | Slow mode |                                                       | 2                                                     | 2                                                     |           |                      |  |

| I <sub>DD (COMP2)</sub>                    | Fast mode |                                                       | Į                                                     | 5                                                     |           |                      |  |

| I <sub>DD (PVD / BOR)</sub> <sup>(5)</sup> |           |                                                       |                                                       |                                                       |           |                      |  |

| I <sub>DD (IWDG)</sub>                     |           |                                                       | 0.1                                                   | 25                                                    |           |                      |  |

#### Table 24. Peripheral current consumption<sup>(1)</sup> (continued)

Data based on differential I<sub>DD</sub> measurement between all peripherals OFF an one peripheral with clock enabled, in the following conditions: f<sub>HCLK</sub> = 32 MHz (Range 1), f<sub>HCLK</sub> = 16 MHz (Range 2), f<sub>HCLK</sub> = 4 MHz (Range 3), f<sub>HCLK</sub> = 64kHz (Low power run/sleep), f<sub>APB1</sub> = f<sub>HCLK</sub>, f<sub>APB2</sub> = f<sub>HCLK</sub>, default prescaler value for each peripheral. The CPU is in Sleep mode in both cases. No I/O pins toggling.

2. HSI oscillator is OFF for this measure.

3. Data based on a differential IDD measurement between ADC in reset configuration and continuous ADC conversion (HSI consumption not included).

4. Data based on a differential Ibb measurement between DAC in reset configuration and continuous DAC conversion of Vbb/2. DAC is in buffered mode, output is left floating.

5. Including supply current of internal reference voltage.

## 6.3.7 Internal clock source characteristics

The parameters given in the following table are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 13*.

## High-speed internal (HSI) RC oscillator

| Symbol                              | Parameter                                         | Conditions                                                           | Min               | Тур  | Max              | Unit |

|-------------------------------------|---------------------------------------------------|----------------------------------------------------------------------|-------------------|------|------------------|------|

| f <sub>HSI</sub>                    | Frequency                                         | V <sub>DD</sub> = 3.0 V                                              | -                 | 16   | -                | MHz  |

| TRIM <sup>(1)(2)</sup>              | HSI user-trimmed                                  | Trimming code is not a multiple of 16                                | -                 | ±0.4 | 0.7              | %    |

| TRIM                                | resolution                                        | Trimming code is a multiple of 16                                    | -                 | -    | ±1.5             | %    |

|                                     |                                                   | V <sub>DDA</sub> = 3.0 V, T <sub>A</sub> = 25 °C                     | -1 <sup>(3)</sup> | -    | 1 <sup>(3)</sup> | %    |

|                                     | Accuracy of the factory-calibrated HSI oscillator | V <sub>DDA</sub> = 3.0 V, T <sub>A</sub> = 0 to 55 °C                | -1.5              | -    | 1.5              | %    |

|                                     |                                                   | $V_{DDA}$ = 3.0 V, $T_A$ = -10 to 70 °C                              | -2                | -    | 2                | %    |

| ACC <sub>HSI</sub> <sup>(2)</sup>   |                                                   | $V_{DDA}$ = 3.0 V, $T_A$ = -10 to 85 °C                              | -2.5              | -    | 2                | %    |

|                                     |                                                   | $V_{DDA}$ = 3.0 V, $T_A$ = -10 to 105 °C                             | -4                | -    | 2                | %    |

|                                     |                                                   | V <sub>DDA</sub> = 1.65 V to 3.6 V<br>T <sub>A</sub> = -40 to 105 °C | -4                | -    | 3                | %    |

| t <sub>SU(HSI)</sub> <sup>(2)</sup> | HSI oscillator<br>startup time                    | -                                                                    | -                 | 3.7  | 6                | μs   |

| I <sub>DD(HSI)</sub> <sup>(2)</sup> | HSI oscillator<br>power consumption               | -                                                                    | -                 | 100  | 140              | μA   |

1. The trimming step differs depending on the trimming code. It is usually negative on the codes which are multiples of 16 (0x00, 0x10, 0x20, 0x30...0xE0).

2. Guaranteed by characterization results.

3. Tested in production.

## Low-speed internal (LSI) RC oscillator

| Table 31. | LSI | oscillator | characteristics |

|-----------|-----|------------|-----------------|

|-----------|-----|------------|-----------------|

| Symbol                              | Parameter                                                   | Min | Тур | Max | Unit |

|-------------------------------------|-------------------------------------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub> <sup>(1)</sup>     | LSI frequency                                               | 26  | 38  | 56  | kHz  |

| D <sub>LSI</sub> <sup>(2)</sup>     | LSI oscillator frequency drift<br>0°C ≤T <sub>A</sub> ≤85°C | -10 | -   | 4   | %    |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time                                 | -   | -   | 200 | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption                            | -   | 400 | 510 | nA   |

1. Tested in production.

2. This is a deviation for an individual part, once the initial frequency has been measured.

3. Guaranteed by design.

## 6.3.9 Memory characteristics

The characteristics are given at  $T_{\text{A}}$  = -40 to 105  $^{\circ}\text{C}$  unless otherwise specified.

#### **RAM** memory

| Table | 34.   | RAM | and | hardware   | reaisters |

|-------|-------|-----|-----|------------|-----------|

|       | • • • |     |     | indiana io |           |

| Symbol | Parameter                          | Conditions           | Min  | Тур | Max | Unit |

|--------|------------------------------------|----------------------|------|-----|-----|------|

| VRM    | Data retention mode <sup>(1)</sup> | STOP mode (or RESET) | 1.65 | -   | -   | V    |

1. Minimum supply voltage without losing data stored in RAM (in Stop mode or under Reset) or in hardware registers (only in Stop mode).

#### Flash memory and data EEPROM

| Symbol                  | Parameter                                                                                                                                                                                                                                      | Conditions                                      | Min  | Тур  | Max <sup>(1)</sup> | Unit |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------|------|--------------------|------|

| V <sub>DD</sub>         | Operating voltage<br>Read / Write / Erase                                                                                                                                                                                                      | -                                               | 1.65 | -    | 3.6                | V    |

|                         | VDD     Operating voltage<br>Read / Write / Erase       Vprogramming / erasing time for<br>byte / word / double word / half-<br>page       IDD     Average current during whole<br>program/erase operation       Maximum current (peak) during | Erasing                                         | -    | 3.28 | 3.94               |      |

| t <sub>prog</sub>       |                                                                                                                                                                                                                                                | Programming                                     | -    | 3.28 | 3.94               | ms   |

| program/erase operation |                                                                                                                                                                                                                                                | T - 25 °C V - 3 6 V                             | -    | 300  | -                  | μA   |

| 'DD                     | Maximum current (peak) during program/erase operation                                                                                                                                                                                          | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 3.6 V | -    | 1.5  | 2.5                | mA   |

#### Table 35. Flash memory and data EEPROM characteristics

1. Guaranteed by design.

#### Table 36. Flash memory, data EEPROM endurance and data retention

| Symbol              | Parameter                                                                           | Parameter Conditions    |                    | /alue |     | Unit    |

|---------------------|-------------------------------------------------------------------------------------|-------------------------|--------------------|-------|-----|---------|

| Symbol              | Falameter                                                                           | Conditions              | Min <sup>(1)</sup> | Тур   | Max | Unit    |

|                     | Cycling (erase / write)<br>Program memory                                           | $T_A = -40^{\circ}C$ to | 10                 | -     | -   | kcycles |

| INCTO: /            | Cycling (erase / write)<br>EEPROM data memory                                       | 105 °C                  | 300                | -     | -   | RUYCIUS |

|                     | Data retention (program memory) after<br>10 kcycles at T <sub>A</sub> = 85 °C       | TRET = +85 °C           | 30                 | -     | -   |         |

| + (2)               | Data retention (EEPROM data memory) after 300 kcycles at $T_A$ = 85 °C              | INET = '03' C           | 30                 | -     | -   | voars   |

| RET                 | Data retention (program memory) after<br>10 kcycles at T <sub>A</sub> = 105 °C      | TRET = +105 °C          | 10                 | I     | -   | years   |

| NCYC <sup>(2)</sup> | Data retention (EEPROM data memory)<br>after 300 kcycles at T <sub>A</sub> = 105 °C | 11121 - 103 C           | 10                 | -     | -   |         |

1. Guaranteed by characterization results.

2. Characterization is done according to JEDEC JESD22-A117.

## 6.3.10 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table* 37. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                                                                                                                           | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, LQFP100, T <sub>A</sub> = +25 °C,<br>f <sub>HCLK</sub> = 32 MHz<br>conforms to IEC 61000-4-2                                                                                                       | 2B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $\label{eq:VDD} \begin{array}{l} V_{DD} = 3.3 \text{ V}, \text{LQFP100},  \text{T}_{\text{A}} = +25 \\ ^{\circ}\text{C}, \\ \text{f}_{\text{HCLK}} = 32 \text{ MHz} \\ \text{conforms to IEC 61000-4-4} \end{array}$ | 4A              |

Table 37. EMS characteristics

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the oscillator pins for 1 second.

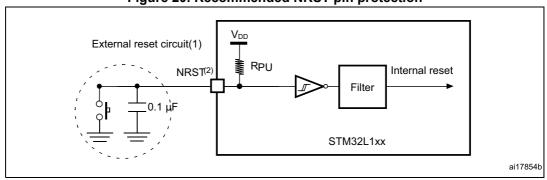

Figure 20. Recommended NRST pin protection

1. The reset network protects the device against parasitic resets.

The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 45. Otherwise the reset will not be taken into account by the device.

## 6.3.15 TIM timer characteristics

The parameters given in Table 46 are guaranteed by design.

Refer to Section 6.3.13: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Table 46. TIMX <sup>(*)</sup> Characteristics |                                                                           |                               |        |                         |                      |

|-----------------------------------------------|---------------------------------------------------------------------------|-------------------------------|--------|-------------------------|----------------------|

| Symbol                                        | Parameter                                                                 | Conditions                    | Min    | Max                     | Unit                 |

| t                                             | Timer resolution time                                                     | -                             | 1      | -                       | t <sub>TIMxCLK</sub> |

| <sup>t</sup> res(TIM)                         |                                                                           | f <sub>TIMxCLK</sub> = 32 MHz | 31.25  | -                       | ns                   |

| f                                             | Timer external clock                                                      | -                             | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |

| f <sub>EXT</sub>                              | frequency on CH1 to CH4                                                   | f <sub>TIMxCLK</sub> = 32 MHz | 0      | 16                      | MHz                  |

| Res <sub>TIM</sub>                            | Timer resolution                                                          | -                             | -      | 16                      | bit                  |

|                                               | 16-bit counter clock                                                      | -                             | 1      | 65536                   | t <sub>TIMxCLK</sub> |

| <sup>t</sup> COUNTER                          | period when internal clock<br>is selected (timer's<br>prescaler disabled) | f <sub>TIMxCLK</sub> = 32 MHz | 0.0312 | 2048                    | μs                   |

| tury court                                    | Maximum possible count                                                    | -                             | -      | 65536 × 65536           | t <sub>TIMxCLK</sub> |

| t <sub>MAX_COUNT</sub>                        |                                                                           | f <sub>TIMxCLK</sub> = 32 MHz | -      | 134.2                   | S                    |

Table 46. TIMx<sup>(1)</sup> characteristics

1. TIMx is used as a general term to refer to the TIM2, TIM3 and TIM4 timers.

| Parameter                            | Conditions                                                                                                                                                                            | Min. <sup>(1)</sup>                                                                                                                                                                                                                                                                         | Max. <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                             | Unit                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ls                                   |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                 | -                                                                                                                                                                                                                                                                                                                                                                                                                               |

| USB operating voltage <sup>(2)</sup> | -                                                                                                                                                                                     | 3.0                                                                                                                                                                                                                                                                                         | 3.6                                                                                                                                                                                                                                                                                                                                                                             | V                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Differential input sensitivity       | I(USB_DP, USB_DM)                                                                                                                                                                     | 0.2                                                                                                                                                                                                                                                                                         | -                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Differential common mode range       | Includes V <sub>DI</sub> range                                                                                                                                                        | 0.8                                                                                                                                                                                                                                                                                         | 2.5                                                                                                                                                                                                                                                                                                                                                                             | V                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Single ended receiver threshold -    |                                                                                                                                                                                       | 1.3                                                                                                                                                                                                                                                                                         | 2.0                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| vels                                 |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Static output level low              | ${\sf R}_{\sf L}$ of 1.5 k $\Omega$ to 3.6 ${\sf V}^{(5)}$                                                                                                                            | -                                                                                                                                                                                                                                                                                           | 0.3                                                                                                                                                                                                                                                                                                                                                                             | v                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Static output level high             | ${\sf R}_{\sf L}$ of 15 ${\sf k}\Omega$ to ${\sf V}_{\sf SS}{}^{(5)}$                                                                                                                 | 2.8                                                                                                                                                                                                                                                                                         | 3.6                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                      | USB operating voltage <sup>(2)</sup><br>Differential input sensitivity<br>Differential common mode range<br>Single ended receiver threshold<br><b>rels</b><br>Static output level low | USB operating voltage <sup>(2)</sup> -<br>Differential input sensitivity I(USB_DP, USB_DM)<br>Differential common mode range Includes V <sub>DI</sub> range<br>Single ended receiver threshold -<br><b>rels</b><br>Static output level low R <sub>L</sub> of 1.5 kΩ to 3.6 V <sup>(5)</sup> | USB operating voltage <sup>(2)</sup> -       3.0         Differential input sensitivity       I(USB_DP, USB_DM)       0.2         Differential common mode range       Includes V <sub>DI</sub> range       0.8         Single ended receiver threshold       -       1.3         rels         Static output level low       R <sub>L</sub> of 1.5 kΩ to 3.6 V <sup>(5)</sup> - | USB operating voltage <sup>(2)</sup> -       3.0       3.6         Differential input sensitivity       I(USB_DP, USB_DM)       0.2       -         Differential common mode range       Includes V <sub>DI</sub> range       0.8       2.5         Single ended receiver threshold       -       1.3       2.0         rels         Static output level low       R <sub>L</sub> of 1.5 kΩ to 3.6 V <sup>(5)</sup> -       0.3 |

Table 51. USB DC electrical characteristics

1. All the voltages are measured from the local ground potential.

2. To be compliant with the USB 2.0 full speed electrical specification, the USB\_DP (D+) pin should be pulled up with a 1.5 k $\Omega$  resistor to a 3.0-to-3.6 V voltage range.

3. Guaranteed by characterization results.

4. Tested in production.

5.  $R_L$  is the load connected on the USB drivers.

#### Figure 25. USB timings: definition of data signal rise and fall time

|                  | Driver characteristics <sup>(1)</sup> |                                |     |     |      |  |

|------------------|---------------------------------------|--------------------------------|-----|-----|------|--|

| Symbol           | Parameter                             | Conditions                     | Min | Max | Unit |  |

| t <sub>r</sub>   | Rise time <sup>(2)</sup>              | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |

| t <sub>f</sub>   | Fall Time <sup>(2)</sup>              | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |

| t <sub>rfm</sub> | Rise/ fall time matching              | t <sub>r</sub> /t <sub>f</sub> | 90  | 110 | %    |  |

| V <sub>CRS</sub> | Output signal crossover voltage       |                                | 1.3 | 2.0 | V    |  |

1. Guaranteed by design.

2. Measured from 10% to 90% of the data signal. For more detailed informations, please refer to USB Specification - Chapter 7 (version 2.0).

| Symbol            | Parameter                                          | Conditions                                             | Min                           | Тур                | Мах     | Unit               |  |

|-------------------|----------------------------------------------------|--------------------------------------------------------|-------------------------------|--------------------|---------|--------------------|--|

|                   |                                                    | Direct channels<br>2.4 V ≤V <sub>DDA</sub> ≤3.6 V      | 0.25                          | -                  | -       |                    |  |

|                   |                                                    | Multiplexed channels<br>2.4 V ≤V <sub>DDA</sub> ≤3.6 V | 0.56                          | -                  | -       |                    |  |

| t <sub>S</sub>    | Sampling time <sup>(5)</sup>                       | Direct channels<br>1.8 V ⊴V <sub>DDA</sub> ⊴2.4 V      | 0.56                          | -                  | -       | μs                 |  |

|                   |                                                    | Multiplexed channels<br>1.8 V ≤V <sub>DDA</sub> ≤2.4 V | 1                             | -                  | -       |                    |  |

|                   |                                                    | -                                                      | 4                             | -                  | 384     | 1/f <sub>ADC</sub> |  |

|                   |                                                    | f <sub>ADC</sub> = 16 MHz                              | 1                             | -                  | 24.75   | μs                 |  |

| t <sub>CONV</sub> | Total conversion time<br>(including sampling time) | -                                                      | 4 to 384<br>phase)<br>approxi | 1/f <sub>ADC</sub> |         |                    |  |

| 0                 | Internal sample and hold                           | Direct channels                                        | -                             | 16                 | -       | - <b>F</b>         |  |

| C <sub>ADC</sub>  | capacitor                                          | Multiplexed channels                                   | -                             | 10                 | -       | pF                 |  |

| £                 | External trigger frequency                         | 12-bit conversions                                     | -                             | -                  | Tconv+1 | 1/f <sub>ADC</sub> |  |

| f <sub>TRIG</sub> | Regular sequencer                                  | 6/8/10-bit conversions                                 | -                             | -                  | Tconv   | 1/f <sub>ADC</sub> |  |

| f                 | External trigger frequency                         | 12-bit conversions                                     | -                             | -                  | Tconv+2 | 1/f <sub>ADC</sub> |  |

| f <sub>TRIG</sub> | Injected sequencer                                 | 6/8/10-bit conversions                                 | -                             | -                  | Tconv+1 | 1/f <sub>ADC</sub> |  |

| R <sub>AIN</sub>  | Signal source impedance <sup>(5)</sup>             | -                                                      | -                             | -                  | 50      | кΩ                 |  |

|                   | Injection trigger conversion                       | f <sub>ADC</sub> = 16 MHz                              | 219                           | -                  | 281     | ns                 |  |

| t <sub>lat</sub>  | latency                                            | -                                                      | 3.5                           | -                  | 4.5     | 1/f <sub>ADC</sub> |  |

| +                 | Regular trigger conversion                         | f <sub>ADC</sub> = 16 MHz                              | 156                           | -                  | 219     | ns                 |  |

| t <sub>latr</sub> | latency                                            | -                                                      | 2.5                           | -                  | 3.5     | 1/f <sub>ADC</sub> |  |

| t <sub>STAB</sub> | Power-up time                                      | -                                                      | -                             | -                  | 3.5     | μs                 |  |

Table 54. ADC characteristics (continued)

The V<sub>REF+</sub> input can be grounded iif neither the ADC nor the DAC are used (this allows to shut down an external voltage reference).

2. The current consumption through  $\mathsf{V}_{\mathsf{REF}}$  is composed of two parameters:

- one constant (max 300 µA)

- one variable (max 400  $\mu$ A), only during sampling time + 2 first conversion pulses.

So, peak consumption is 300+400 = 700  $\mu A$  and average consumption is 300 + [(4 sampling + 2) /16] x 400 = 450  $\mu A$  at 1Msps

3.  $V_{REF+}$  can be internally connected to  $V_{DDA}$  and  $V_{REF-}$  can be internally connected to  $V_{SSA}$ , depending on the package. Refer to Section 4: Pin descriptions for further details.

4. V<sub>SSA</sub> must be tied to ground.

5. See Table 56: Maximum source impedance RAIN max for  $\mathsf{R}_{\mathsf{AIN}}$  limitation.

| Symbol                    | Parameter                                                                                                                                                       | Conditions                                                                         | Min | Тур             | Мах              | Unit   |  |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----|-----------------|------------------|--------|--|

| dOffset/dT <sup>(1)</sup> | Offset error temperature                                                                                                                                        | $V_{DDA} = 3.3V$ , $T_A = 0$ to 50 ° C<br>DAC output buffer OFF                    | -20 | -10             | 0                | µV/°C  |  |

|                           | coefficient (code 0x800)                                                                                                                                        | $V_{DDA} = 3.3V$ , $T_A = 0$ to 50 ° C<br>DAC output buffer ON                     | 0   | 20              | 50               | μν/ Ο  |  |

| Gain <sup>(1)</sup>       | Gain error <sup>(6)</sup>                                                                                                                                       | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON         | -   | +0.1 /<br>-0.2% | +0.2 / -<br>0.5% | %      |  |

| Gain                      | Gain enor                                                                                                                                                       | No R <sub>LOAD</sub> , C <sub>L</sub> ≤50 pF<br>DAC output buffer OFF              | -   | +0 / -0.2%      | +0 / -0.4%       | 70     |  |

| dGain/dT <sup>(1)</sup>   | Gain error temperature                                                                                                                                          | $V_{DDA} = 3.3V$ , $T_A = 0$ to 50 ° C<br>DAC output buffer OFF                    | -10 | -2              | 0                |        |  |

|                           | coefficient                                                                                                                                                     | $V_{DDA} = 3.3V$ , $T_A = 0$ to 50 ° C<br>DAC output buffer ON                     | -40 | -8              | 0                | −µV/°C |  |

| TUE <sup>(1)</sup>        | Total unadjusted error                                                                                                                                          | $C_L \le 50 \text{ pF}, \text{ R}_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON | -   | 12              | 30               | LSB    |  |

| TUE                       |                                                                                                                                                                 | No R <sub>LOAD</sub> , C <sub>L</sub> ≤50 pF<br>DAC output buffer OFF              | -   | 8               | 12               | LOD    |  |

| tSETTLING                 | Settling time (full scale:<br>for a 12-bit code<br>transition between the<br>lowest and the highest<br>input codes till<br>DAC_OUT reaches final<br>value ±1LSB | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                 | -   | 7               | 12               | μs     |  |

| Update rate               | Max frequency for a<br>correct DAC_OUT<br>change (95% of final<br>value) with 1 LSB<br>variation in the input<br>code                                           | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                 | -   | -               | 1                | Msps   |  |

| t <sub>wakeup</sub>       | Wakeup time from off<br>state (setting the ENx bit<br>in the DAC Control<br>register) <sup>(7)</sup>                                                            | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                 | -   | 9               | 15               | μs     |  |

| PSRR+                     | V <sub>DDA</sub> supply rejection<br>ratio (static DC<br>measurement)                                                                                           | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                 | -   | -60             | -35              | dB     |  |

#### Table 57. DAC characteristics (continued)

1. Guaranteed by characterization results.

2. Difference between two consecutive codes - 1 LSB.

3. Difference between measured value at Code i and the value at Code i on a line drawn between Code 0 and last Code 4095.

4. Difference between the value measured at Code (0x800) and the ideal value = V/2.

5. Difference between the value measured at Code (0x001) and the ideal value.

6. Difference between ideal slope of the transfer function and measured slope computed from code 0x000 and 0xFFF when buffer is OFF, and from code giving 0.2 V and ( $V_{DDA} - 0.2$ ) V when buffer is ON.

7. In buffered mode, the output can overshoot above the final value for low input code (starting from min value).

## 6.3.21 LCD controller (STM32L152xx only)

The STM32L152xx embeds a built-in step-up converter to provide a constant LCD reference voltage independently from the V<sub>DD</sub> voltage. An external capacitor C<sub>ext</sub> must be connected to the V<sub>LCD</sub> pin to decouple this converter.

| Symbol                           | Parameter                                                | Min  | Тур                  | Max       | Unit |

|----------------------------------|----------------------------------------------------------|------|----------------------|-----------|------|

| $V_{LCD}$                        | LCD external voltage                                     | -    | -                    | 3.6       |      |

| V <sub>LCD0</sub>                | LCD internal reference voltage 0                         | -    | 2.6                  | -         |      |

| V <sub>LCD1</sub>                | LCD internal reference voltage 1                         | -    | 2.73                 | -         |      |

| V <sub>LCD2</sub>                | LCD internal reference voltage 2                         | -    | 2.86                 | -         |      |

| $V_{LCD3}$                       | LCD internal reference voltage 3                         | -    | 2.98                 | -         | V    |

| V <sub>LCD4</sub>                | LCD internal reference voltage 4                         | -    | 3.12                 | -         |      |

| $V_{LCD5}$                       | LCD internal reference voltage 5                         | -    | 3.26                 | -         | Ţ    |

| V <sub>LCD6</sub>                | LCD internal reference voltage 6                         | -    | 3.4                  | -         |      |

| $V_{LCD7}$                       | LCD internal reference voltage 7                         | -    | 3.55                 | -         | Ţ    |

| C <sub>ext</sub>                 | V <sub>LCD</sub> external capacitance                    | 0.1  | -                    | 2         | μF   |

| I <sub>LCD</sub> <sup>(1)</sup>  | Supply current at V <sub>DD</sub> = 2.2 V                | -    | 3.3                  | -         |      |

|                                  | Supply current at V <sub>DD</sub> = 3.0 V                | -    | 3.1                  | -         | μA   |

| R <sub>Htot</sub> <sup>(2)</sup> | Low drive resistive network overall value                | 5.28 | 6.6                  | 7.92      | MΩ   |

| $R_L^{(2)}$                      | High drive resistive network total value                 | 192  | 240                  | 288       | kΩ   |

| V <sub>44</sub>                  | Segment/Common highest level voltage                     | -    | -                    | $V_{LCD}$ | V    |

| V <sub>34</sub>                  | Segment/Common 3/4 level voltage                         | -    | 3/4 V <sub>LCD</sub> | -         |      |

| V <sub>23</sub>                  | Segment/Common 2/3 level voltage                         | -    | 2/3 V <sub>LCD</sub> | -         |      |

| V <sub>12</sub>                  | Segment/Common 1/2 level voltage                         | -    | 1/2 V <sub>LCD</sub> | -         | V    |

| V <sub>13</sub>                  | Segment/Common 1/3 level voltage                         | -    | 1/3 V <sub>LCD</sub> | -         |      |

| V <sub>14</sub>                  | Segment/Common 1/4 level voltage                         | -    | 1/4 V <sub>LCD</sub> | -         | 1    |

| V <sub>0</sub>                   | Segment/Common lowest level voltage                      | 0    | -                    | -         | 1    |

| $\Delta Vxx^{(3)}$               | Segment/Common level voltage error $T_A$ = -40 to 85 ° C | -    | -                    | ±50       | mV   |

|  | Table 62 | . LCD | controller | characteristics |

|--|----------|-------|------------|-----------------|

|--|----------|-------|------------|-----------------|

1. LCD enabled with 3 V internal step-up active, 1/8 duty, 1/4 bias, division ratio= 64, all pixels active, no LCD connected

2. Guaranteed by design.

3. Guaranteed by characterization results.

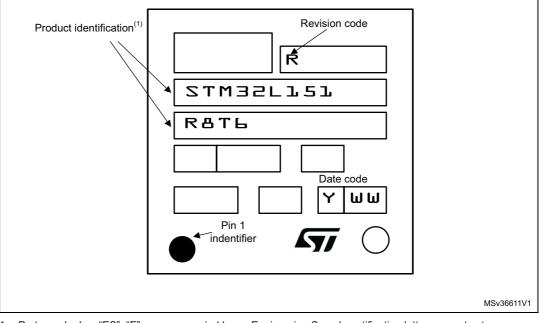

## LQFP64 device marking

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

#### Figure 37. LQFP64 10 x 10 mm, 64-pin low-profile quad flat package top view example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

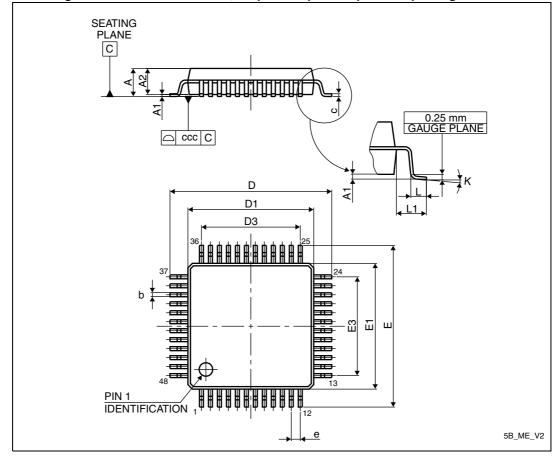

# 7.3 LQFP48 7 x 7 mm, 48-pin low-profile quad flat package information

Figure 38. LQFP48 7 x 7 mm, 48-pin low-profile quad flat package outline

1. Drawing is not to scale.

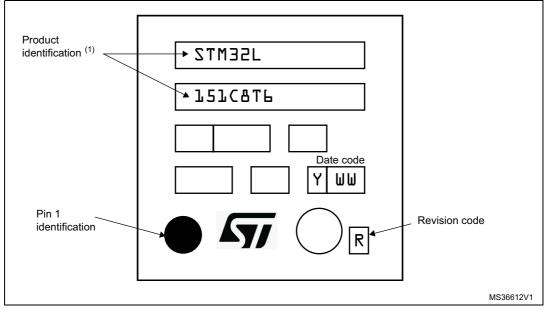

#### LQFP48 device marking

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

| Querra ha a l | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|---------------|-------------|-------|-------|-----------------------|--------|--------|

| Symbol        | Min         | Тур   | Мах   | Min                   | Тур    | Max    |

| А             | 0.500       | 0.550 | 0.600 | 0.0197                | 0.0217 | 0.0236 |

| A1            | 0.000       | 0.020 | 0.050 | 0.0000                | 0.0008 | 0.0020 |

| D             | 6.900       | 7.000 | 7.100 | 0.2717                | 0.2756 | 0.2795 |

| E             | 6.900       | 7.000 | 7.100 | 0.2717                | 0.2756 | 0.2795 |

| D2            | 5.500       | 5.600 | 5.700 | 0.2165                | 0.2205 | 0.2244 |

| E2            | 5.500       | 5.600 | 5.700 | 0.2165                | 0.2205 | 0.2244 |

| L             | 0.300       | 0.400 | 0.500 | 0.0118                | 0.0157 | 0.0197 |

| Т             | -           | 0.152 | -     | -                     | 0.0060 | -      |

| b             | 0.200       | 0.250 | 0.300 | 0.0079                | 0.0098 | 0.0118 |

| е             | -           | 0.500 | -     | -                     | 0.0197 | -      |

| ddd           | -           | -     | 0.080 | -                     | -      | 0.0031 |

Table 66. UFQFPN48 7 x 7 mm, 0.5 mm pitch, package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

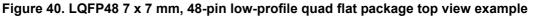

#### Figure 42. UFQFPN48 7 x 7 mm, 0.5 mm pitch, package recommended footprint

1. Dimensions are in millimeters.

#### TFBGA64 5 x 5 mm, 0.5 mm pitch, thin fine-pitch ball 7.6 grid array package information

1. Drawing is not to scale.

| Table 69. TFBGA64 5 x 5 mm, 0.5 mm pitch, package mechanical data |             |       |       |                       |        |        |

|-------------------------------------------------------------------|-------------|-------|-------|-----------------------|--------|--------|

| Symbol                                                            | millimeters |       |       | inches <sup>(1)</sup> |        |        |

| Symbol                                                            | Min         | Тур   | Max   | Min                   | Тур    | Max    |

| А                                                                 | -           | -     | 1.200 | -                     | -      | 0.0472 |

| A1                                                                | 0.150       | -     | -     | 0.0059                | -      | -      |

| A2                                                                | -           | 0.200 | -     | -                     | 0.0079 | -      |

| A4                                                                | -           | -     | 0.600 | -                     | -      | 0.0236 |

| b                                                                 | 0.250       | 0.300 | 0.350 | 0.0098                | 0.0118 | 0.0138 |

| D                                                                 | 4.850       | 5.000 | 5.150 | 0.1909                | 0.1969 | 0.2028 |

| D1                                                                | -           | 3.500 | -     | -                     | 0.1378 | -      |

| E                                                                 | 4.850       | 5.000 | 5.150 | 0.1909                | 0.1969 | 0.2028 |

| E1                                                                | -           | 3.500 | -     | -                     | 0.1378 | -      |

| е                                                                 | -           | 0.500 | -     | -                     | 0.0197 | -      |

| F                                                                 | -           | 0.750 | -     | -                     | 0.0295 | -      |

| ddd                                                               | -           | -     | 0.080 | -                     | -      | 0.0031 |

| Table 69. TFBGA64 5 x 5 mm | , 0.5 mm pitch, packag | e mechanical data |

|----------------------------|------------------------|-------------------|

|----------------------------|------------------------|-------------------|

| Symbol | millimeters |     |      | inches <sup>(1)</sup> |     |        |

|--------|-------------|-----|------|-----------------------|-----|--------|

|        | Min         | Тур | Max  | Min                   | Тур | Мах    |

| eee    | -           | -   | 0.15 | -                     | -   | 0.0059 |

| fff    | -           | -   | 0.05 | -                     | -   | 0.002  |

#### Table 69. TFBGA64 5 x 5 mm, 0.5 mm pitch, package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

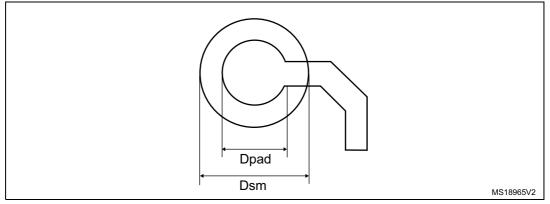

#### Figure 48. TFBGA64, 5 x 5 mm, 0.5 mm pitch, recommended footprint

#### Table 70. TFBGA64 5 x 5 mm, 0.5 mm pitch, recommended PCB design rules

| Dimension    | Recommended values                                              |

|--------------|-----------------------------------------------------------------|

| Pitch        | 0.5                                                             |

| Dpad         | 0.27 mm                                                         |

| Dsm          | 0.35 mm typ. (depends on the soldermask registration tolerance) |

| Solder paste | 0.27 mm aperture diameter.                                      |

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |