Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                              |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                         |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT |

| Number of I/O              | 83                                                                           |

| Program Memory Size        | 64KB (64K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 4K x 8                                                                       |

| RAM Size                   | 10K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                        |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 100-UFBGA                                                                    |

| Supplier Device Package    | 100-UFBGA (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l152v8h6        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.10 ADC (analog-to-digital converter)

A 12-bit analog-to-digital converters is embedded into STM32L151x6/8/B and STM32L152x6/8/B devices with up to 24 external channels, performing conversions in single-shot or scan mode. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The events generated by the general-purpose timers (TIMx) can be internally connected to the ADC start trigger and injection trigger, to allow the application to synchronize A/D conversions and timers. An injection mode allows high priority conversions to be done by interrupting a scan mode which runs in as a background task.

The ADC includes a specific low power mode. The converter is able to operate at maximum speed even if the CPU is operating at a very low frequency and has an auto-shutdown function. The ADC's runtime and analog front-end current consumption are thus minimized whatever the MCU operating mode.

# 3.10.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $\mathsf{V}_{\mathsf{SENSE}}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode, see *Table 58: Temperature sensor calibration values*.

# 3.10.2 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC and Comparators.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. It enables accurate monitoring of the  $V_{DD}$  value (when no external voltage, VREF+, is available for ADC). The precise voltage of  $V_{REFINT}$  is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode see *Table 16: Embedded internal reference voltage*.

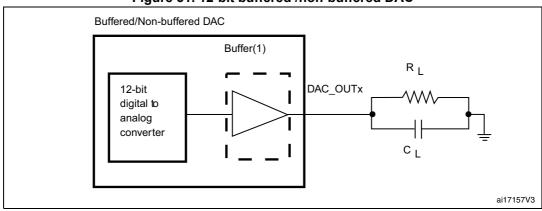

# 3.11 DAC (digital-to-analog converter)

The two 12-bit buffered DAC channels can be used to convert two digital signals into two analog voltage signal outputs. The chosen design structure is composed of integrated resistor strings and an amplifier in non-inverting configuration.

DocID17659 Rev 12

# 3.15.5 Window watchdog (WWDG)

The window watchdog is based on a 7-bit down-counter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

# 3.16 Communication interfaces

# 3.16.1 I<sup>2</sup>C bus

Up to two I<sup>2</sup>C bus interfaces can operate in multimaster and slave modes. They can support standard and fast modes.

They support dual slave addressing (7-bit only) and both 7- and 10-bit addressing in master mode. A hardware CRC generation/verification is embedded.

They can be served by DMA and they support SM Bus 2.0/PM Bus.

## 3.16.2 Universal synchronous/asynchronous receiver transmitter (USART)

All USART interfaces are able to communicate at speeds of up to 4 Mbit/s. They provide hardware management of the CTS and RTS signals and are ISO 7816 compliant. They support IrDA SIR ENDEC and have LIN Master/Slave capability.

All USART interfaces can be served by the DMA controller.

# 3.16.3 Serial peripheral interface (SPI)

Up to two SPIs are able to communicate at up to 16 Mbits/s in slave and master modes in full-duplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes.

Both SPIs can be served by the DMA controller.

# 3.16.4 Universal serial bus (USB)

The STM32L151x6/8/B and STM32L152x6/8/B devices embed a USB device peripheral compatible with the USB full speed 12 Mbit/s. The USB interface implements a full speed (12 Mbit/s) function interface. It has software-configurable endpoint setting and supports suspend/resume. The dedicated 48 MHz clock is generated from the internal main PLL (the clock source must use a HSE crystal oscillator).

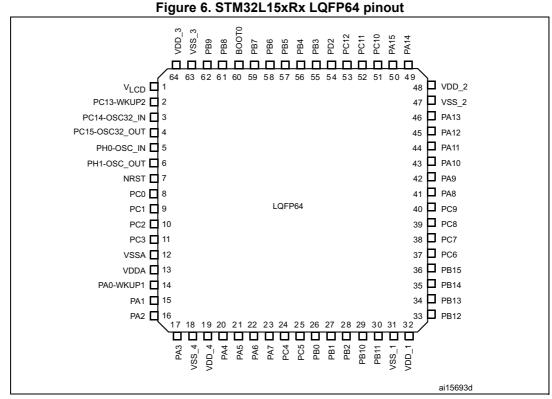

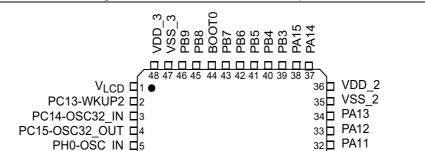

1. This figure shows the package top view.

LQFP48

31 PA10

30 PA9

29 PA8

28 PB15

27 PB14

26 PB13 25 PB12

Figure 7. STM32L15xCx LQFP48 pinout

This figure shows the package top view.

PH1-OSC\_OUT

NRST 7

VSSA 🔤 🛚

VDDA

PA1 11 PA2 12

PA0-WKUP1 10

ai15694d

|         |        | Pins    |          |                    |                                  |                         |               |                                                  | Pins functions                  |                                            |

|---------|--------|---------|----------|--------------------|----------------------------------|-------------------------|---------------|--------------------------------------------------|---------------------------------|--------------------------------------------|

| LQFP100 | LQFP64 | TFBGA64 | UFBGA100 | LQFP48 or UFQFPN48 | Pin name                         | Pin type <sup>(1)</sup> | I/O structure | Main<br>function <sup>(2)</sup><br>(after reset) | Alternate functions             | Additional<br>functions                    |

| 1       | -      | -       | B2       | -                  | PE2                              | I/O                     | FT            | PE2                                              | TRACECLK/LCD_SEG38/<br>TIM3_ETR | -                                          |

| 2       | -      | -       | A1       | -                  | PE3                              | I/O                     | FT            | PE3                                              | TRACED0/LCD_SEG39/<br>TIM3_CH1  | -                                          |

| 3       | -      | -       | B1       | -                  | PE4                              | I/O                     | FT            | PE4                                              | TRACED1/TIM3_CH2                | -                                          |

| 4       | -      | -       | C2       | -                  | PE5                              | I/O                     | FT            | PE5                                              | TRACED2/TIM9_CH1                | -                                          |

| 5       | -      | -       | D2       | -                  | PE6-WKUP3                        | I/O                     | FT            | PE6                                              | TRACED3/TIM9_CH2                | WKUP3                                      |

| 6       | 1      | B2      | E2       | 1                  | V <sub>LCD</sub> <sup>(3)</sup>  | S                       |               | V <sub>LCD</sub>                                 | -                               | -                                          |

| 7       | 2      | A2      | C1       | 2                  | PC13-<br>WKUP2                   | I/O                     | FT            | PC13                                             | -                               | RTC_TAMP1/<br>RTC_TS/<br>RTC_OUT/<br>WKUP2 |

| 8       | 3      | A1      | D1       | 3                  | PC14-<br>OSC32_IN <sup>(4)</sup> | I/O                     | тс            | PC14                                             | -                               | OSC32_IN                                   |

| 9       | 4      | B1      | E1       | 4                  | PC15-<br>OSC32_OUT<br>(4)        | I/O                     | тс            | PC15                                             | -                               | OSC32_OUT                                  |

| 10      | -      | -       | F2       | -                  | V <sub>SS_5</sub>                | S                       | -             | V <sub>SS_5</sub>                                | -                               | -                                          |

| 11      | -      | -       | G2       | -                  | V <sub>DD_5</sub>                | S                       | -             | V <sub>DD_5</sub>                                | -                               | -                                          |

| 12      | 5      | C1      | F1       | 5                  | PH0-<br>OSC_IN <sup>(5)</sup>    | I/O                     | тс            | PH0                                              | -                               | OSC_IN                                     |

| 13      | 6      | D1      | G1       | 6                  | PH1-<br>OSC_OUT                  | I/O                     | тс            | PH1                                              | -                               | OSC_OUT                                    |

| 14      | 7      | E1      | H2       | 7                  | NRST                             | I/O                     | RST           | NRST                                             | -                               | -                                          |

| 15      | 8      | E3      | H1       | -                  | PC0                              | I/O                     | FT            | PC0                                              | LCD_SEG18                       | ADC_IN10/<br>/COMP1_INP                    |

| 16      | 9      | E2      | J2       | -                  | PC1                              | I/O                     | FT            | PC1                                              | LCD_SEG19                       | ADC_IN11/<br>COMP1_INP                     |

| 17      | 10     | F2      | JЗ       | -                  | PC2                              | I/O                     | FT            | PC2                                              | LCD_SEG20                       | ADC_IN12/<br>COMP1_INP                     |

| 18      | 11     | _(6)    | K2       | -                  | PC3                              | I/O                     | тс            | PC3                                              | LCD_SEG21                       | ADC_IN13/<br>COMP1_INP                     |

# 6 Electrical characteristics

# 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

# 6.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\sigma$ ).

Please refer to device ErrataSheet for possible latest changes of electrical characteristics.

# 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 3.6$  V (for the 1.65 V  $\leq V_{DD} \leq 3.6$  V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\sigma$ ).

# 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

# 6.1.4 Loading capacitor

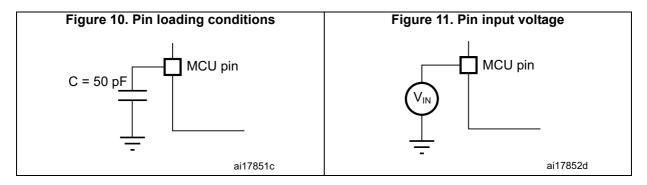

The loading conditions used for pin parameter measurement are shown in Figure 10.

# 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 11*.

| Symbol                                  | Parameter                                                                  | Conditions                                                  |                                                             | Typ <sup>(1)</sup> | Max<br>(1)(2)    | Unit |

|-----------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|--------------------|------------------|------|

|                                         |                                                                            |                                                             | T <sub>A</sub> = -40 °C to 25 °C<br>V <sub>DD</sub> = 1.8 V | 0.9                | -                |      |

|                                         |                                                                            | RTC clocked by LSI (no                                      | $T_A = -40 \ ^\circ C \text{ to } 25 \ ^\circ C$            | 1.1                | 1.8              |      |

|                                         |                                                                            | independent watchdog)                                       | T <sub>A</sub> = 55 °C                                      | 1.42               | 2.5              |      |

|                                         |                                                                            |                                                             | T <sub>A</sub> = 85 °C                                      | 1.87               | 3                |      |

| I <sub>DD</sub>                         | Supply current in Standby                                                  |                                                             | T <sub>A</sub> = 105 °C                                     | 2.78               | 5                |      |

| (Standby<br>with RTC)                   | mode with RTC enabled                                                      |                                                             | T <sub>A</sub> = -40 °C to 25 °C<br>V <sub>DD</sub> = 1.8 V | 1                  | -                |      |

|                                         |                                                                            | RTC clocked by LSE (no independent watchdog) <sup>(3)</sup> | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$                     | 1.33               | 2.9              |      |

|                                         |                                                                            |                                                             | T <sub>A</sub> = 55 °C                                      | 1.59               | 3.4              |      |

|                                         |                                                                            |                                                             | T <sub>A</sub> = 85 °C                                      | 2.01               | 4.3              | μA   |

|                                         |                                                                            |                                                             | T <sub>A</sub> = 105 °C                                     | 3.27               | 6.3              |      |

|                                         |                                                                            | Independent watchdog<br>and LSI enabled                     | $T_A = -40 \text{ °C to } 25 \text{ °C}$                    | 1.1                | 1.6              |      |

| I <sub>DD</sub>                         | Supply current in Standby                                                  |                                                             | $T_A = -40 \degree C$ to 25 $\degree C$                     | 0.3                | 0.55             |      |

| (Standby)                               | mode with RTC disabled                                                     | Independent watchdog                                        | T <sub>A</sub> = 55 °C                                      | 0.5                | 0.8              |      |

|                                         |                                                                            | and LSI OFF $T_A = 85 \degree C$                            |                                                             | 1                  | 1.7              |      |

|                                         |                                                                            |                                                             | T <sub>A</sub> = 105 °C                                     | 2.5                | 4 <sup>(4)</sup> |      |

| I <sub>DD (WU</sub><br>from<br>Standby) | RMS supply current during<br>wakeup time when exiting<br>from Standby mode | -                                                           | V <sub>DD</sub> = 3.0 V<br>T <sub>A</sub> = -40 °C to 25 °C | 1                  | -                |      |

| Table 23. Typical and maximum current consumption | s in Standby mode  |

|---------------------------------------------------|--------------------|

| Table 25. Typical and maximum current consumption | 5 III Stanuby moue |

1. The typical values are given for  $V_{DD}$  = 3.0 V and max values are given for  $V_{DD}$  = 3.6 V, unless otherwise specified.

2. Guaranteed by characterization results, unless otherwise specified.

Based on characterization done with a 32.768 kHz crystal (MC306-G-06Q-32.768, manufacturer JFVNY) with two 6.8pF loading capacitors.

4. Tested in production.

# On-chip peripheral current consumption

The current consumption of the on-chip peripherals is given in the following table. The MCU is placed under the following conditions:

- all I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

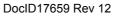

- t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

- Note: For CL1 and CL2, it is recommended to use high-quality ceramic capacitors in the 5 pF to 15 pF range selected to match the requirements of the crystal or resonator (see Figure 18). CL1 and CL2, are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of CL1 and CL2. Load capacitance CL has the following formula: CL = CL1 x CL2 / (CL1 + CL2) + Cstray where Cstray is the pin capacitance and board or trace PCB-related capacitance. Typically, it is between 2 pF and 7 pF.

- **Caution:** To avoid exceeding the maximum value of CL1 and CL2 (15 pF) it is strongly recommended to use a resonator with a load capacitance  $CL \le 7$  pF. Never use a resonator with a load capacitance of 12.5 pF.

Example: if a resonator is chosen with a load capacitance of CL = 6 pF and Cstray = 2 pF, then CL1 = CL2 = 8 pF.

#### Figure 18. Typical application with a 32.768 kHz crystal

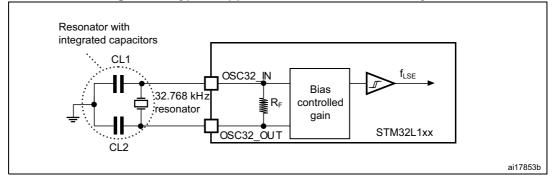

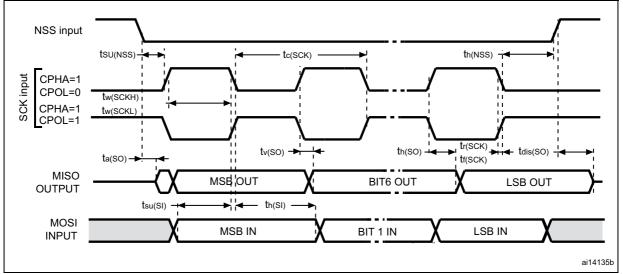

## **SPI characteristics**

Unless otherwise specified, the parameters given in the following table are derived from tests performed under ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 13*.

Refer to *Section 6.3.12: I/O current injection characteristics* for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                                                                     | Parameter                        | Conditions                 | Min                       | Max <sup>(2)</sup>        | Unit |  |

|----------------------------------------------------------------------------|----------------------------------|----------------------------|---------------------------|---------------------------|------|--|

| _                                                                          |                                  | Master mode                | -                         | 16                        |      |  |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>                                  | SPI clock frequency              | Slave mode                 | -                         | 16                        | MHz  |  |

|                                                                            |                                  | Slave transmitter          | -                         | 12 <sup>(3)</sup>         |      |  |

| t <sub>r(SCK)</sub> <sup>(2)</sup><br>t <sub>f(SCK)</sub> <sup>(2)</sup>   | SPI clock rise and fall time     | Capacitive load: C = 30 pF | -                         | 6                         | ns   |  |

| DuCy(SCK)                                                                  | SPI slave input clock duty cycle | Slave mode                 | 30                        | 70                        | %    |  |

| t <sub>su(NSS)</sub>                                                       | NSS setup time                   | Slave mode                 | 4t <sub>HCLK</sub>        | -                         |      |  |

| t <sub>h(NSS)</sub>                                                        | NSS hold time                    | Slave mode                 | 2t <sub>HCLK</sub>        | -                         |      |  |

| t <sub>w(SCKH)</sub> <sup>(2)</sup><br>t <sub>w(SCKL)</sub> <sup>(2)</sup> | SCK high and low time            | Master mode                | t <sub>SCK</sub> /2–<br>5 | t <sub>SCK</sub> /2+<br>3 |      |  |

| t <sub>su(MI)</sub> <sup>(2)</sup>                                         | Data input setup time            | Master mode                | 5                         | -                         |      |  |

| t <sub>su(SI)</sub> <sup>(2)</sup>                                         | Data input setup time            | Slave mode                 | 6                         | -                         |      |  |

| t <sub>h(MI)</sub> <sup>(2)</sup>                                          | Data input hold time             | Master mode                | 5                         | -                         | ns   |  |

| t <sub>h(SI)</sub> <sup>(2)</sup>                                          | Data input hold time             | Slave mode                 | 5                         | -                         |      |  |

| t <sub>a(SO)</sub> <sup>(4)</sup>                                          | Data output access time          | Slave mode                 | 0                         | 3t <sub>HCLK</sub>        |      |  |

| t <sub>v(SO)</sub> (2)                                                     | Data output valid time           | Slave mode                 | -                         | 33                        |      |  |

| t <sub>v(MO)</sub> <sup>(2)</sup>                                          | Data output valid time           | Master mode                | -                         | 6.5                       |      |  |

| t <sub>h(SO)</sub> <sup>(2)</sup>                                          | Data output hold tires           | Slave mode                 | 17                        | -                         |      |  |

| t <sub>h(MO)</sub> <sup>(2)</sup>                                          | Data output hold time            | Master mode                | 0.5                       | -                         |      |  |

| Table 49. SPI characteristics | ble 49. SPI characteristics | (1) |

|-------------------------------|-----------------------------|-----|

|-------------------------------|-----------------------------|-----|

1. The characteristics above are given for voltage Range 1.

2. Guaranteed by characterization results.

3. The maximum SPI clock frequency in slave transmitter mode is given for an SPI slave input clock duty cycle (DuCy(SCK)) ranging between 40 to 60%.

4. Min time is for the minimum time to drive the output and max time is for the maximum time to validate the data.

Figure 22. SPI timing diagram - slave mode and CPHA = 0

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}$

# 6.3.17 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 54* are guaranteed by design.

| Symbol           | Parameter              |         | Conditions                     | Min                                                              | Max   | Unit |     |

|------------------|------------------------|---------|--------------------------------|------------------------------------------------------------------|-------|------|-----|

| f <sub>ADC</sub> |                        |         |                                | $V_{REF+} = V_{DDA}$                                             |       | 16   |     |

|                  | ADC clock<br>frequency | • • • • | 2.4 V ≤V <sub>DDA</sub> ≤3.6 V | $V_{REF+} < V_{DDA}$<br>$V_{REF+} > 2.4 V$                       | 0.480 | 8    | MHz |

|                  |                        |         |                                | V <sub>REF+</sub> < V <sub>DDA</sub><br>V <sub>REF+</sub> ≤2.4 V |       | 4    |     |

|                  |                        |         | 1.8 V ⊴V <sub>DDA</sub> ⊴2.4 V | $V_{REF+} = V_{DDA}$                                             |       | 8    |     |

|                  |                        |         |                                | $V_{REF+} < V_{DDA}$                                             |       | 4    |     |

|                  |                        |         | Voltage Range 3                |                                                                  |       | 4    |     |

Table 53. ADC clock frequency

# Table 54. ADC characteristics

|                                  | 10510 0-                                | +. ADC characteristic                                                                                       |                    |                  |                  |        |

|----------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------|--------------------|------------------|------------------|--------|

| Symbol                           | Parameter                               | Conditions                                                                                                  | Min                | Тур              | Max              | Unit   |

| $V_{DDA}$                        | Power supply                            | -                                                                                                           | 1.8                | -                | 3.6              | V      |

| V <sub>REF+</sub>                | Positive reference voltage              | 2.4 V $\le$ V <sub>DDA</sub> $\le$ 3.6 V<br>V <sub>REF+</sub> must be below<br>or equal to V <sub>DDA</sub> | 1.8 <sup>(1)</sup> | -                | V <sub>DDA</sub> | v      |

| $V_{REF-}$                       | Negative reference voltage              | -                                                                                                           | -                  | $V_{\text{SSA}}$ | -                | V      |

| I <sub>VDDA</sub>                | Current on the $V_{DDA}$ input pin      | -                                                                                                           | -                  | 1000             | 1450             | μA     |

| I <sub>VREF</sub> <sup>(2)</sup> | Current on the V <sub>REF</sub> input   | Peak                                                                                                        | -                  | 400              | 700              | μA     |

|                                  | pin                                     | Average                                                                                                     | -                  | 400              | 450              | μA     |

| V <sub>AIN</sub>                 | Conversion voltage range <sup>(3)</sup> | -                                                                                                           | 0 <sup>(4)</sup>   | -                | $V_{REF}$ +      | V      |

|                                  | 12-bit sampling rate                    | Direct channels                                                                                             | 0.03               | -                | 1                | Msps   |

|                                  | 12-bit sampling rate                    | Multiplexed channels                                                                                        | 0.03               | -                | 0.76             | ivisps |

|                                  | 10 hit compling rate                    | Direct channels                                                                                             | 0.03               | -                | 1.07             | Mana   |

| £                                | 10-bit sampling rate                    | Multiplexed channels                                                                                        | 0.03               | -                | 0.8              | Msps   |

| f <sub>S</sub>                   | 9 hit compling rate                     | Direct channels                                                                                             | 0.03               | -                | 1.23             | Mana   |

|                                  | 8-bit sampling rate                     | Multiplexed channels                                                                                        | 0.03               | -                | 0.89             | Msps   |

|                                  | 6-bit sampling rate                     | Direct channels                                                                                             | 0.03               | -                | 1.45             | Msps   |

|                                  |                                         | Multiplexed channels                                                                                        | 0.03               | -                | 1                | ivisps |

# 6.3.18 DAC electrical specifications

Data guaranteed by design, unless otherwise specified.

| Symbol                          | Parameter                                             | С                                                                                  | onditions                                | Min | Тур              | Мах                         | Unit |

|---------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------|-----|------------------|-----------------------------|------|

| V <sub>DDA</sub>                | Analog supply voltage                                 |                                                                                    | 1.8                                      | -   | 3.6              | V                           |      |

| V <sub>REF+</sub>               | Reference supply voltage                              | V <sub>REF+</sub> must<br>V <sub>DDA</sub>                                         | 1.8                                      | -   | 3.6              | V                           |      |

| V <sub>REF-</sub>               | Lower reference voltage                               |                                                                                    | -                                        | •   | V <sub>SSA</sub> |                             | V    |

| I <sub>DDVREF+</sub> (1)        | Current consumption on                                | No load, mic                                                                       | dle code (0x800)                         | -   | 130              | 220                         | μA   |

|                                 | V <sub>REF+</sub> supply<br>V <sub>REF+</sub> = 3.3 V | No load, wo                                                                        | rst code (0x000)                         | -   | 220              | 350                         | μA   |

| . (1)                           | Current consumption on                                | No load, mic                                                                       | dle code (0x800)                         | -   | 210              | 320                         | μA   |

| I <sub>DDA</sub> <sup>(1)</sup> | V <sub>DDA</sub> supply<br>V <sub>DDA</sub> = 3.3 V   | No load, worst code (0xF1C)                                                        |                                          | -   | 320              | 520                         | μA   |

| RL                              | Resistive load                                        | DAC output                                                                         | Connected to $V_{SSA}$                   | 5   | -                | -                           | kΩ   |

|                                 |                                                       | buffer ON                                                                          | Connected to $\mathrm{V}_{\mathrm{DDA}}$ | 25  | -                | -                           | N32  |

| CL                              | Capacitive load                                       | DAC output                                                                         | buffer ON                                | -   | -                | 50                          | pF   |

| R <sub>O</sub>                  | Output impedance                                      | DAC output                                                                         | buffer OFF                               | 12  | 16               | 20                          | kΩ   |

| V <sub>DAC_OUT</sub>            | Voltage on DAC_OUT                                    | DAC output buffer ON                                                               |                                          | 0.2 | -                | V <sub>DDA</sub> – 0.2      | V    |

|                                 | output                                                | DAC output buffer OFF                                                              |                                          | 0.5 | -                | V <sub>REF+</sub> –<br>1LSB | mV   |

| DNL <sup>(1)</sup>              | Differential non                                      | C <sub>L</sub> ≤ 50 pF, I<br>DAC output                                            | -                                        | -   | 1.5              | 3                           |      |

| DINE                            | linearity <sup>(2)</sup>                              | No $R_{LOAD}$ , $C_{L} \le 50 \text{ pF}$<br>DAC output buffer OFF                 |                                          | -   | 1.5              | 3                           |      |

| INL <sup>(1)</sup>              | Integral non linearity <sup>(3)</sup>                 | $C_L \le 50 \text{ pF}, \text{ R}_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON |                                          | -   | 2                | 4                           |      |

| IINE' '                         | integral non inteanty '                               | No $R_{LOAD}$ , $C_{L} \le 50 \text{ pF}$<br>DAC output buffer OFF                 |                                          | -   | 2                | 4                           | LSB  |

| Offect <sup>(1)</sup>           | Offset error at code                                  | $C_L \le 50 \text{ pF}, \text{ R}_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON |                                          | -   | ±10              | ±25                         |      |

| Offset <sup>(1)</sup>           | 0x800 <sup>(4)</sup>                                  | No R <sub>LOAD</sub> , C <sub>L</sub> ≤50 pF<br>DAC output buffer OFF              |                                          | -   | ±5               | ±8                          |      |

| Offset1 <sup>(1)</sup>          | Offset error at code<br>0x001 <sup>(5)</sup>          | No R <sub>LOAD</sub> , 0<br>DAC output                                             |                                          | -   | ±1.5             | ±5                          |      |

| Table | 57. | DAC | characteristics |

|-------|-----|-----|-----------------|

| Symbol                    | Parameter                                                                                                                                                       | Conditions                                                                         | Min | Тур             | Мах              | Unit   |  |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----|-----------------|------------------|--------|--|

| dOffset/dT <sup>(1)</sup> | Offset error temperature                                                                                                                                        | $V_{DDA} = 3.3V$ , $T_A = 0$ to 50 ° C<br>DAC output buffer OFF                    | -20 | -10             | 0                |        |  |

|                           | coefficient (code 0x800)                                                                                                                                        | $V_{DDA} = 3.3V$ , $T_A = 0$ to 50 ° C<br>DAC output buffer ON                     | 0   | 20              | 50               | -μV/°C |  |

| Gain <sup>(1)</sup>       | Gain error <sup>(6)</sup>                                                                                                                                       | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON         | -   | +0.1 /<br>-0.2% | +0.2 / -<br>0.5% | %      |  |

| Gain                      | Gain enor                                                                                                                                                       | No R <sub>LOAD</sub> , C <sub>L</sub> ≤50 pF<br>DAC output buffer OFF              | -   | +0 / -0.2%      | +0 / -0.4%       | 70     |  |

| dGain/dT <sup>(1)</sup>   | Gain error temperature                                                                                                                                          | $V_{DDA} = 3.3V$ , $T_A = 0$ to 50 ° C<br>DAC output buffer OFF                    | -10 | -2              | 0                | μV/°C  |  |

| dGain/d I                 | coefficient                                                                                                                                                     | $V_{DDA} = 3.3V$ , $T_A = 0$ to 50 ° C<br>DAC output buffer ON                     | -40 | -8              | 0                | μν/ Ο  |  |

| TUE <sup>(1)</sup>        | Total unadjusted error                                                                                                                                          | $C_L \le 50 \text{ pF}, \text{ R}_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON | -   | 12              | 30               | LSB    |  |

|                           |                                                                                                                                                                 | No R <sub>LOAD</sub> , C <sub>L</sub> ≤50 pF<br>DAC output buffer OFF              | -   | 8               | 12               |        |  |

| tSETTLING                 | Settling time (full scale:<br>for a 12-bit code<br>transition between the<br>lowest and the highest<br>input codes till<br>DAC_OUT reaches final<br>value ±1LSB | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                 | -   | 7               | 12               | μs     |  |

| Update rate               | Max frequency for a<br>correct DAC_OUT<br>change (95% of final<br>value) with 1 LSB<br>variation in the input<br>code                                           | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                 | -   | -               | 1                | Msps   |  |

| t <sub>wakeup</sub>       | Wakeup time from off<br>state (setting the ENx bit<br>in the DAC Control<br>register) <sup>(7)</sup>                                                            | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                 | -   | 9               | 15               | μs     |  |

| PSRR+                     | V <sub>DDA</sub> supply rejection<br>ratio (static DC<br>measurement)                                                                                           | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                 | -   | -60             | -35              | dB     |  |

#### Table 57. DAC characteristics (continued)

1. Guaranteed by characterization results.

2. Difference between two consecutive codes - 1 LSB.

3. Difference between measured value at Code i and the value at Code i on a line drawn between Code 0 and last Code 4095.

4. Difference between the value measured at Code (0x800) and the ideal value = V/2.

5. Difference between the value measured at Code (0x001) and the ideal value.

6. Difference between ideal slope of the transfer function and measured slope computed from code 0x000 and 0xFFF when buffer is OFF, and from code giving 0.2 V and ( $V_{DDA} - 0.2$ ) V when buffer is ON.

7. In buffered mode, the output can overshoot above the final value for low input code (starting from min value).

Figure 31. 12-bit buffered /non-buffered DAC

1. The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.

# 6.3.19 Temperature sensor characteristics

| Calibration value name Description |                                                                                | Memory address          |

|------------------------------------|--------------------------------------------------------------------------------|-------------------------|

| TS_CAL1                            | TS ADC raw data acquired at<br>temperature of 30 °C,<br>V <sub>DDA</sub> = 3 V | 0x1FF8 007A-0x1FF8 007B |

| TS_CAL2                            | TS ADC raw data acquired at<br>temperature of 110 °C<br>V <sub>DDA</sub> = 3 V | 0x1FF8 007E-0x1FF8 007F |

## Table 58. Temperature sensor calibration values

| Symbol                                | Parameter                                      | Min  | Тур   | Max       | Unit  |  |

|---------------------------------------|------------------------------------------------|------|-------|-----------|-------|--|

| T <sub>L</sub> <sup>(1)</sup>         | V <sub>SENSE</sub> linearity with temperature  | -    | ±1    | <u>+2</u> | °C    |  |

| Avg_Slope <sup>(1)</sup>              | Average slope                                  | 1.48 | 1.61  | 1.75      | mV/°C |  |

| V <sub>110</sub>                      | Voltage at 110°C ±5°C <sup>(2)</sup>           | 612  | 626.8 | 641.5     | mV    |  |

| I <sub>DDA(TEMP)</sub> <sup>(3)</sup> | Current consumption                            | -    | 3.4   | 6         | μA    |  |

| t <sub>START</sub> <sup>(3)</sup>     | Startup time                                   | -    | -     | 10        |       |  |

| T <sub>S_temp</sub> <sup>(4)(3)</sup> | ADC sampling time when reading the temperature | 10   | -     | -         | μs    |  |

1. Guaranteed by characterization results.

2. Measured at  $V_{DD}$  = 3 V ±10 mV. V110 ADC conversion result is stored in the TS\_CAL2 byte.

- 3. Guaranteed by design.

- 4. Shortest sampling time can be determined in the application by multiple iterations.

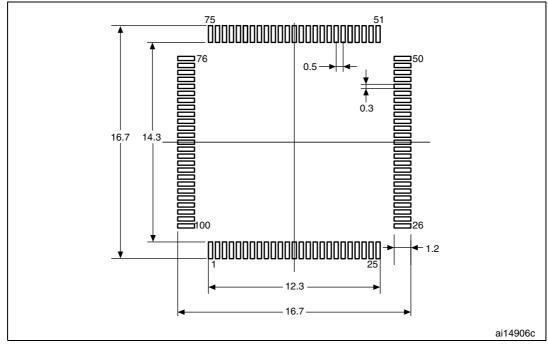

# Figure 33. LQPF100 14 x 14 mm, 100-pin low-profile quad flat package recommended footprint

1. Dimensions are in millimeters.

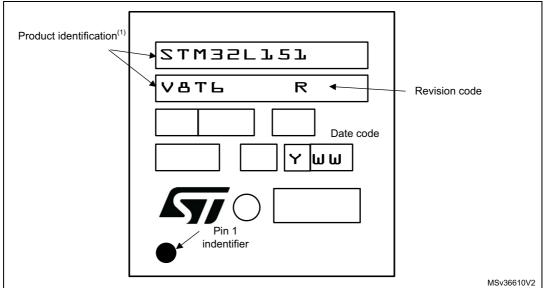

# LQFP100 device marking

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Figure 34. LQFP100 14 x 14 mm, 100-pin package top view example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

| Symbol | millimeters |     | inches <sup>(1)</sup> |     |     |        |

|--------|-------------|-----|-----------------------|-----|-----|--------|

| Symbol | Min         | Тур | Мах                   | Min | Тур | Max    |

| eee    | -           | -   | 0.15                  | -   | -   | 0.0059 |

| fff    | -           | -   | 0.05                  | -   | -   | 0.002  |

#### Table 67. UFBGA100 7 x 7 mm, 0.5 mm pitch, package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

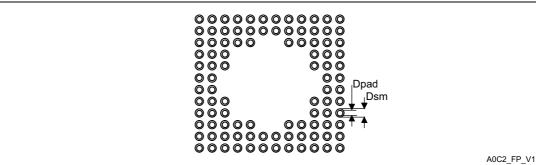

#### Figure 45. UFBGA100 7 x 7 mm, 0.5 mm pitch, package recommended footprint

#### Table 68. UFBGA100 7 x 7 mm, 0.5 mm pitch, recommended PCB design rules

| Dimension         | Recommended values                                               |

|-------------------|------------------------------------------------------------------|

| Pitch             | 0.5                                                              |

| Dpad              | 0.280 mm                                                         |

| Dsm               | 0.370 mm typ. (depends on the soldermask registration tolerance) |

| Stencil opening   | 0.280 mm                                                         |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                    |

| Symbol | millimeters |     | inches <sup>(1)</sup> |     |     |        |

|--------|-------------|-----|-----------------------|-----|-----|--------|

| Symbol | Min         | Тур | Max                   | Min | Тур | Мах    |

| eee    | -           | -   | 0.15                  | -   | -   | 0.0059 |

| fff    | -           | -   | 0.05                  | -   | -   | 0.002  |

#### Table 69. TFBGA64 5 x 5 mm, 0.5 mm pitch, package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

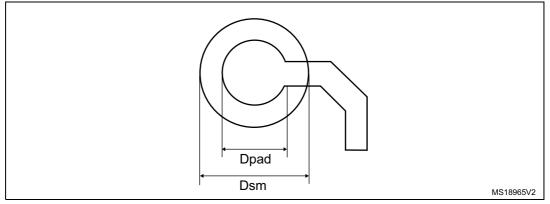

#### Figure 48. TFBGA64, 5 x 5 mm, 0.5 mm pitch, recommended footprint

## Table 70. TFBGA64 5 x 5 mm, 0.5 mm pitch, recommended PCB design rules

| Dimension    | Recommended values                                              |

|--------------|-----------------------------------------------------------------|

| Pitch        | 0.5                                                             |

| Dpad         | 0.27 mm                                                         |

| Dsm          | 0.35 mm typ. (depends on the soldermask registration tolerance) |

| Solder paste | 0.27 mm aperture diameter.                                      |

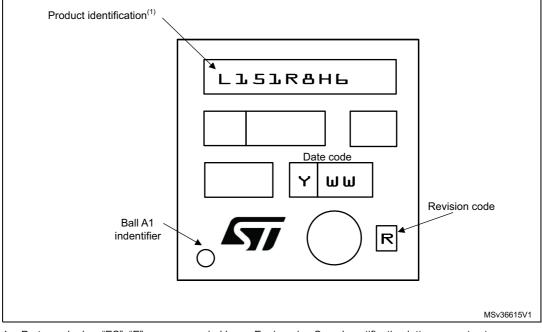

# **TFBGA64** device marking

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Figure 49. TFBGA64 5 x 5 mm, 0.5 mm pitch, package top view example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

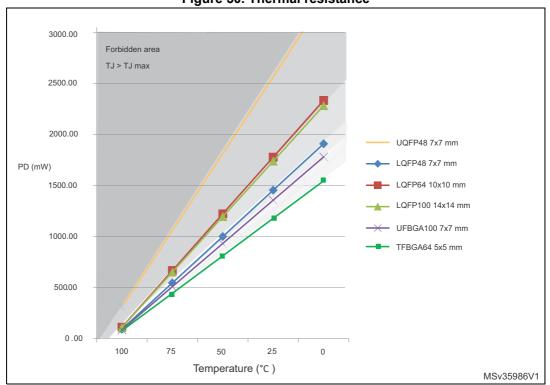

Figure 50. Thermal resistance

# 7.7.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.

| Date        | Revision         | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12-Nov-2013 | 9<br>(continued) | Updated Table 54: ADC characteristics and Figure 27: Typical connection diagram using the ADC.<br>Table 58: Temperature sensor calibration values was previously in Section 3.10.1: Temperature sensor. Updated Table 59:<br>Temperature sensor characteristics.<br>In Table 61: Comparator 2 characteristics, parameter dThreshold/dt, replaced any occurrence of "VREF+" by "V <sub>REFINT</sub> "Updated Table 63: LQPF100 14 x 14 mm, 100-pin low-profile quad flat package mechanical data, Table 64: LQFP64 10 x 10 mm 64-pin low-profile quad flat package mechanical data, Table 65: LQFP48 7 x 7 mm, 48-pin low-profile quad flat package mechanical data.<br>Updated Figure 33: LQFP100 recommended footprint.<br>Updated Figure 46: TFBGA64 - 5.0x5.0x1.2 mm, 0.5 mm pitch, thin fine-pitch dall grid array package outline title.<br>Remove minimum and typical values of A dimension in Table 67: UFBGA100 7 x 7 x 0.6 mm 0.5 mm pitch, ultra thin fine-pitch ball grid array package mechanical data<br>Deleted second footnote in Figure 42: UFQFPN48 recommended footprint.<br>Updated Section 8: Ordering information title and added first sentence.<br>Changed BOR disabled option identifier in Table 72: Ordering information scheme. |

| 22-Jul-2014 | 10               | Updated <i>Figure 14</i> , <i>Figure 15</i> .<br>Updated <i>Table 5</i> .<br>Updated <i>Figure 6.3.4</i> .<br>Updated note 5 inside <i>Table 54</i> .<br>Updated Ro value inside <i>Table 54</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Table 73. | Document revision history (continued) |

|-----------|---------------------------------------|

|           |                                       |

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30-Jan-2015 | 11       | Updated DMIPS features in cover page and Section 2: Description.<br>Updated Table 8: STM32L151x6/8/B and STM32L152x6/8/B pin<br>definitions and Table 9: Alternate function input/output putting<br>additional functions.<br>Updated package top view marking in Section 7.1: Package<br>mechanical data.<br>Updated Figure 9: Memory map.<br>Updated Table 56: Maximum source impedance RAIN max adding<br>note 2.<br>Updated Table 72: Ordering information scheme.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 28-Apr-2016 | 12       | Updated <i>Section 7: Package information</i> structure: Paragraph titles<br>and paragraph heading level.<br>Updated <i>Section 7: Package information</i> for all package device<br>markings, adding text for device orientation versus pin 1/ ball A1<br>identifier.<br>Updated <i>Figure 34: LQFP100 14 x 14 mm, 100-pin package top</i><br><i>view example</i> removing gate mark.<br>Updated <i>Table 64: LQFP64 10 x 10 mm, 64-pin low-profile quad flat</i><br><i>package mechanical data</i> .<br>Updated <i>Section 7.5: UFBGA100 7 x 7 mm, 0.5 mm pitch, ultra thin</i><br><i>fine-pitch ball grid array package information</i> adding <i>Table 68:</i><br><i>UFBGA100 7 x 7 mm, 0.5 mm pitch, recommended PCB design</i><br><i>rules</i> and <i>Figure 45: UFBGA100 7 x 7 mm, 0.5 mm pitch, package</i><br><i>recommended footprint</i> .<br>Updated Section 7.6: <i>TFBGA64 5 x 5 mm, 0.5 mm pitch, thin fine-<br/>pitch ball grid array package information</i> adding <i>Table 70: TFBGA64<br/>5 x 5 mm, 0.5 mm pitch, recommended PCB design rules</i> and<br>changing <i>Figure 48: TFBGA64, 5 x 5 mm, 0.5 mm pitch,</i><br><i>recommended footprint</i> .<br>Updated <i>Table 16: Embedded internal reference voltage</i><br>temperature coefficient at 100ppm/°C.<br>Updated <i>Table 61: Comparator 2 characteristics</i> new maximum<br>threshold voltage temperature coefficient at 100ppm/°C.<br>Updated <i>Table 61: Comparator 2 characteristics</i> new maximum<br>threshold voltage temperature coefficient at 100ppm/°C.<br>Updated <i>Table 61: Comparator 2 characteristics</i> new maximum<br>threshold voltage temperature coefficient at 100ppm/°C.<br>Updated <i>Table 61: Comparator 2 characteristics</i> new maximum<br>threshold voltage temperature coefficient at 100ppm/°C.<br>Updated <i>Table 10: Voltage characteristics</i> adding note about V <sub>REF</sub> .<br>pin.<br>Updated <i>Table 5: Working mode-dependent functionalities</i> (from<br><i>Run/active down to standby</i> ) LSI and LSE functionalities putting "Y"<br>in Standby mode.<br>Removed note 1 below <i>Figure 2: Clock tree</i> .<br>Updated <i>Table 57: DAC characteristics</i> resistive load. |

Table 73. Document revision history (continued)