# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                          |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                              |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                         |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT |

| Number of I/O              | 83                                                                           |

| Program Memory Size        | 64KB (64K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 4K x 8                                                                       |

| RAM Size                   | 10K × 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                        |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 100-LQFP                                                                     |

| Supplier Device Package    | 100-LQFP (14x14)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l152v8t6        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|   |        | 3.15.1    | General-purpose timers (TIM2, TIM3, TIM4, TIM9, TIM10 and TIM11) . | . 28 |

|---|--------|-----------|--------------------------------------------------------------------|------|

|   |        | 3.15.2    | Basic timers (TIM6 and TIM7)                                       | . 28 |

|   |        | 3.15.3    | SysTick timer                                                      | . 28 |

|   |        | 3.15.4    | Independent watchdog (IWDG)                                        | . 28 |

|   |        | 3.15.5    | Window watchdog (WWDG)                                             | . 29 |

|   | 3.16   | Commu     | nication interfaces                                                | 29   |

|   |        | 3.16.1    | I <sup>2</sup> C bus                                               | . 29 |

|   |        | 3.16.2    | Universal synchronous/asynchronous receiver transmitter (USART)    | . 29 |

|   |        | 3.16.3    | Serial peripheral interface (SPI)                                  | . 29 |

|   |        | 3.16.4    | Universal serial bus (USB)                                         | . 29 |

|   | 3.17   | CRC (cy   | clic redundancy check) calculation unit                            | 30   |

|   | 3.18   | Develop   | oment support                                                      | 30   |

|   |        |           |                                                                    |      |

| 4 | Pin de | escripti  | ons                                                                | 31   |

| 5 | Memo   | ory map   | ping                                                               | 48   |

|   |        | <b>,</b>  |                                                                    |      |

| 6 | Electi | rical cha | aracteristics                                                      | 49   |

|   | 6.1    | Parame    | ter conditions                                                     | 49   |

|   |        | 6.1.1     | Minimum and maximum values                                         | . 49 |

|   |        | 6.1.2     | Typical values                                                     | . 49 |

|   |        | 6.1.3     | Typical curves                                                     | . 49 |

|   |        | 6.1.4     | Loading capacitor                                                  | . 49 |

|   |        | 6.1.5     | Pin input voltage                                                  | . 49 |

|   |        | 6.1.6     | Power supply scheme                                                | . 50 |

|   |        | 6.1.7     | Optional LCD power supply scheme                                   |      |

|   |        | 6.1.8     | Current consumption measurement                                    | . 51 |

|   | 6.2    | Absolute  | e maximum ratings                                                  | 52   |

|   | 6.3    | Operatir  | ng conditions                                                      | 53   |

|   |        | 6.3.1     | General operating conditions                                       | . 53 |

|   |        | 6.3.2     | Embedded reset and power control block characteristics             | . 54 |

|   |        | 6.3.3     | Embedded internal reference voltage                                | . 56 |

|   |        | 6.3.4     | Supply current characteristics                                     | . 57 |

|   |        | 6.3.5     | Wakeup time from Low power mode                                    | . 69 |

|   |        | 6.3.6     | External clock source characteristics                              | . 70 |

|   |        | 6.3.7     | Internal clock source characteristics                              | . 75 |

|   |        | 6.3.8     | PLL characteristics                                                | . 77 |

|   |        |           |                                                                    |      |

### 3.1 Low power modes

The ultra-low-power STM32L151x6/8/B and STM32L152x6/8/B devices support dynamic voltage scaling to optimize its power consumption in run mode. The voltage from the internal low-drop regulator that supplies the logic can be adjusted according to the system's maximum operating frequency and the external voltage supply:

- In Range 1 (V<sub>DD</sub> range limited to 1.71-3.6 V), the CPU runs at up to 32 MHz (refer to Table 17 for consumption).

- In Range 2 (full V<sub>DD</sub> range), the CPU runs at up to 16 MHz (refer to *Table 17* for consumption)

- In Range 3 (full V<sub>DD</sub> range), the CPU runs at up to 4 MHz (generated only with the multispeed internal RC oscillator clock source). Refer to *Table 17* for consumption.

Seven low power modes are provided to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

• Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

Sleep mode power consumption: refer to *Table 19*.

Low power run mode

This mode is achieved with the multispeed internal (MSI) RC oscillator set to the minimum clock (65 kHz), execution from SRAM or Flash memory, and internal regulator in low power mode to minimize the regulator's operating current. In the Low power run mode, the clock frequency and the number of enabled peripherals are both limited.

Low power run mode consumption: refer to *Table 20: Current consumption in Low power run mode*.

#### Low power sleep mode

This mode is achieved by entering the Sleep mode with the internal voltage regulator in Low power mode to minimize the regulator's operating current. In the Low power sleep mode, both the clock frequency and the number of enabled peripherals are limited; a typical example would be to have a timer running at 32 kHz.

When wakeup is triggered by an event or an interrupt, the system reverts to the run mode with the regulator on.

Low power sleep mode consumption: refer to *Table 21: Current consumption in Low power sleep mode*.

• Stop mode with RTC

Stop mode achieves the lowest power consumption while retaining the RAM and register contents and real time clock. All clocks in the  $V_{CORE}$  domain are stopped, the PLL, MSI RC, HSI RC and HSE crystal oscillators are disabled. The LSE or LSI is still running. The voltage regulator is in the low power mode.

The device can be woken up from Stop mode by any of the EXTI line, in 8 µs. The EXTI line source can be one of the 16 external lines. It can be the PVD output, the Comparator 1 event or Comparator 2 event (if internal reference voltage is on), it can be the RTC alarm(s), the USB wakeup, the RTC tamper events, the RTC timestamp event or the RTC wakeup.

• **Stop** mode without RTC

Stop mode achieves the lowest power consumption while retaining the RAM and register contents. All clocks are stopped, the PLL, MSI RC, HSI and LSI RC, LSE and

#### Nested vectored interrupt controller (NVIC)

The ultra-low-power STM32L151x6/8/B and STM32L152x6/8/B devices embed a nested vectored interrupt controller able to handle up to 45 maskable interrupt channels (not including the 16 interrupt lines of Cortex<sup>®</sup>-M3) and 16 priority levels.

- Closely coupled NVIC gives low-latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of *late arriving*, higher-priority interrupts

- Support for tail-chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimal interrupt latency.

### 3.3 Reset and supply management

### 3.3.1 **Power supply schemes**

- V<sub>DD</sub> = 1.65 to 3.6 V: external power supply for I/Os and the internal regulator. Provided externally through V<sub>DD</sub> pins.

- $V_{SSA}$ ,  $V_{DDA}$  = 1.65 to 3.6 V: external analog power supplies for ADC, reset blocks, RCs and PLL (minimum voltage to be applied to  $V_{DDA}$  is 1.8 V when the ADC is used).  $V_{DDA}$  and  $V_{SSA}$  must be connected to  $V_{DD}$  and  $V_{SS}$ , respectively.

### 3.3.2 Power supply supervisor

The device has an integrated ZEROPOWER power-on reset (POR)/power-down reset (PDR) that can be coupled with a brownout reset (BOR) circuitry.

The device exists in two versions:

- The version with BOR activated at power-on operates between 1.8 V and 3.6 V.

- The other version without BOR operates between 1.65 V and 3.6 V.

After the  $V_{DD}$  threshold is reached (1.65 V or 1.8 V depending on the BOR which is active or not at power-on), the option byte loading process starts, either to confirm or modify default thresholds, or to disable the BOR permanently: in this case, the  $V_{DD}$  min value becomes 1.65 V (whatever the version, BOR active or not, at power-on).

When BOR is active at power-on, it ensures proper operation starting from 1.8 V whatever the power ramp-up phase before it reaches 1.8 V. When BOR is not active at power-up, the power ramp-up should guarantee that 1.65 V is reached on  $V_{DD}$  at least 1 ms after it exits the POR area.

### 3.5 Low power real-time clock and backup registers

The real-time clock (RTC) is an independent BCD timer/counter. Dedicated registers contain the second, minute, hour (12/24 hour), week day, date, month, year, in BCD (binary-coded decimal) format. Correction for 28, 29 (leap year), 30, and 31 day of the month are made automatically. The RTC provides a programmable alarm and programmable periodic interrupts with wakeup from Stop and Standby modes.

- The programmable wakeup time ranges from 120 µs to 36 hours

- Stop mode consumption with LSI and Auto-wakeup: 1.2  $\mu A$  (at 1.8 V) and 1.4  $\mu A$  (at 3.0 V)

- Stop mode consumption with LSE, calendar and Auto-wakeup: 1.3 μA (at 1.8V), 1.6 μA (at 3.0 V)

The RTC can be calibrated with an external 512 Hz output, and a digital compensation circuit helps reduce drift due to crystal deviation.

There are twenty 32-bit backup registers provided to store 80 bytes of user application data. They are cleared in case of tamper detection.

### **3.6 GPIOs (general-purpose inputs/outputs)**

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions, and can be individually remapped using dedicated AFIO registers. All GPIOs are high current capable. The alternate function configuration of I/Os can be locked if needed following a specific sequence in order to avoid spurious writing to the I/O registers. The I/O controller is connected to the AHB with a toggling speed of up to 16 MHz.

### External interrupt/event controller (EXTI)

The external interrupt/event controller consists of 23 edge detector lines used to generate interrupt/event requests. Each line can be individually configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 83 GPIOs can be connected to the 16 external interrupt lines. The 7 other lines are connected to RTC, PVD, USB or Comparator events.

### 3.10 ADC (analog-to-digital converter)

A 12-bit analog-to-digital converters is embedded into STM32L151x6/8/B and STM32L152x6/8/B devices with up to 24 external channels, performing conversions in single-shot or scan mode. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The events generated by the general-purpose timers (TIMx) can be internally connected to the ADC start trigger and injection trigger, to allow the application to synchronize A/D conversions and timers. An injection mode allows high priority conversions to be done by interrupting a scan mode which runs in as a background task.

The ADC includes a specific low power mode. The converter is able to operate at maximum speed even if the CPU is operating at a very low frequency and has an auto-shutdown function. The ADC's runtime and analog front-end current consumption are thus minimized whatever the MCU operating mode.

### 3.10.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $\mathsf{V}_{\mathsf{SENSE}}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode, see *Table 58: Temperature sensor calibration values*.

### 3.10.2 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC and Comparators.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. It enables accurate monitoring of the  $V_{DD}$  value (when no external voltage, VREF+, is available for ADC). The precise voltage of  $V_{REFINT}$  is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode see *Table 16: Embedded internal reference voltage*.

### 3.11 DAC (digital-to-analog converter)

The two 12-bit buffered DAC channels can be used to convert two digital signals into two analog voltage signal outputs. The chosen design structure is composed of integrated resistor strings and an amplifier in non-inverting configuration.

DocID17659 Rev 12

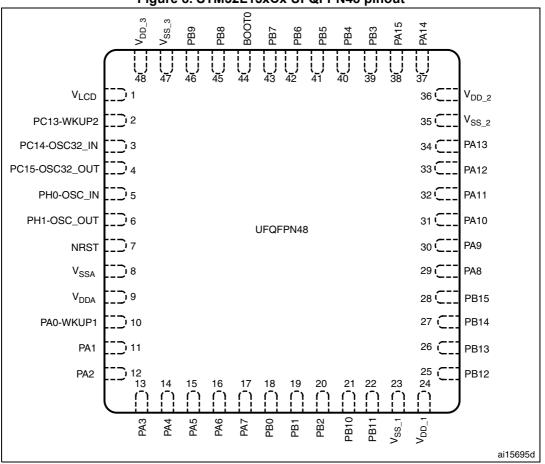

Figure 8. STM32L15xCx UFQFPN48 pinout

1. This figure shows the package top view.

|         |        | Pins      |          | . 01               |                   |                         |               |                                                  | 6/8/B pin definitions (continued) Pins functions |                                    |  |

|---------|--------|-----------|----------|--------------------|-------------------|-------------------------|---------------|--------------------------------------------------|--------------------------------------------------|------------------------------------|--|

|         |        |           | >        |                    |                   |                         |               |                                                  |                                                  |                                    |  |

| LQFP100 | LQFP64 | TFBGA64   | UFBGA100 | LQFP48 or UFQFPN48 | Pin name          | Pin type <sup>(1)</sup> | I/O structure | Main<br>function <sup>(2)</sup><br>(after reset) | Alternate functions                              | Additional<br>functions            |  |

| 19      | 12     | F1        | J1       | 8                  | V <sub>SSA</sub>  | S                       | -             | V <sub>SSA</sub>                                 | -                                                | -                                  |  |

| 20      | -      | -         | K1       | -                  | V <sub>REF-</sub> | S                       | -             | V <sub>REF-</sub>                                | -                                                | -                                  |  |

| 21      | -      | G1<br>(6) | L1       | -                  | V <sub>REF+</sub> | S                       | -             | V <sub>REF+</sub>                                | -                                                | -                                  |  |

| 22      | 13     | H1        | M1       | 9                  | V <sub>DDA</sub>  | S                       | -             | V <sub>DDA</sub>                                 | -                                                | -                                  |  |

| 23      | 14     | G2        | L2       | 10                 | PA0-WKUP1         | I/O                     | FT            | PA0                                              | USART2_CTS/<br>TIM2_CH1_ETR                      | WKUP1/<br>ADC_IN0/<br>COMP1_INP    |  |

| 24      | 15     | H2        | M2       | 11                 | PA1               | I/O                     | FT            | PA1                                              | USART2_RTS/<br>TIM2_CH2/LCD_SEG0                 | ADC_IN1/<br>COMP1_INP              |  |

| 25      | 16     | F3        | K3       | 12                 | PA2               | I/O                     | FT            | PA2                                              | USART2_TX/TIM2_CH3/<br>TIM9_CH1/LCD_SEG1         | ADC_IN2/<br>COMP1_INP              |  |

| 26      | 17     | G3        | L3       | 13                 | PA3               | I/O                     | тс            | PA3                                              | USART2_RX/TIM2_CH4/<br>TIM9_CH2/LCD_SEG2         | ADC_IN3/<br>COMP1_INP              |  |

| 27      | 18     | C2        | E3       | -                  | V <sub>SS_4</sub> | S                       | -             | V <sub>SS_4</sub>                                | -                                                | -                                  |  |

| 28      | 19     | D2        | H3       | -                  | V <sub>DD_4</sub> | S                       | -             | V <sub>DD_4</sub>                                | -                                                | -                                  |  |

| 29      | 20     | H3        | М3       | 14                 | PA4               | I/O                     | тс            | PA4                                              | SPI1_NSS/USART2_CK                               | ADC_IN4/<br>DAC_OUT1/<br>COMP1_INP |  |

| 30      | 21     | F4        | K4       | 15                 | PA5               | I/O                     | тс            | PA5                                              | SPI1_SCK/<br>TIM2_CH1_ETR                        | ADC_IN5/<br>DAC_OUT2/<br>COMP1_INP |  |

| 31      | 22     | G4        | L4       | 16                 | PA6               | I/O                     | FT            | PA6                                              | SPI1_MISO/TIM3_CH1/<br>LCD_SEG3/TIM10_CH1        | ADC_IN6<br>/COMP1_INP              |  |

| 32      | 23     | H4        | M4       | 17                 | PA7               | I/O                     | FT            | PA7                                              | SPI1_MOSI//TIM3_CH2/<br>LCD_SEG4/TIM11_CH1       | ADC_IN7/<br>COMP1_INP              |  |

| 33      | 24     | H5        | K5       | -                  | PC4               | I/O                     | FT            | PC4                                              | LCD_SEG22                                        | ADC_IN14/<br>COMP1_INP             |  |

| 34      | 25     | H6        | L5       | -                  | PC5               | I/O                     | FT            | PC5                                              | LCD_SEG23                                        | ADC_IN15/<br>COMP1_INP             |  |

### Table 8. STM32L151x6/8/B and STM32L152x6/8/B pin definitions (continued)

44/133

| Do  |

|-----|

| сIС |

| 017 |

| 659 |

| 9 F |

| ۲ev |

| 12  |

|           |        |                    |          |            |               | Digital al | ternate fu | nction number |       |       |                           |        |        |          |                      |

|-----------|--------|--------------------|----------|------------|---------------|------------|------------|---------------|-------|-------|---------------------------|--------|--------|----------|----------------------|

| <b>D</b>  | AFIO0  | AFIO1              | AFIO2    | AFIO3      | AFIO4         | AFIO5      | AFOI6      | AFIO7         | AFIO8 | AFIO9 | AFIO11                    | AFIO12 | AFIO13 | AFIO14   | AFIO15               |

| Port name |        | Alternate function |          |            |               |            |            |               |       |       |                           | •      |        |          |                      |

|           | SYSTEM | TIM2               | TIM3/4   | TIM9/10/11 | I2C1/2        | SPI1/2     | N/A        | USART1/2/3    | N/A   | N/A   | LCD                       | N/A    | N/A    | RI       | SYSTEM               |

| PB5       | -      | -                  | TIM3_CH2 | -          | I2C1_<br>SMBA | SPI1_MOSI  | -          | -             | -     | -     | [SEG9]                    | -      | -      | -        | EVENTOU <sup>1</sup> |

| PB6       | -      | -                  | TIM4_CH1 | -          | I2C1_SCL      | -          | -          | USART1_TX     | -     | -     | -                         | -      | -      | -        | EVENTOU              |

| PB7       | -      | -                  | TIM4_CH2 | -          | I2C1_SDA      | -          | -          | USART1_RX     | -     | -     | -                         | -      | -      | -        | EVENTOU"             |

| PB8       | -      | -                  | TIM4_CH3 | TIM10_CH1* | I2C1_SCL      | -          | -          | -             | -     | -     | SEG16                     | -      | -      | -        | EVENTOU"             |

| PB9       | -      | -                  | TIM4_CH4 | TIM11_CH1* | I2C1_SDA      | -          | -          | -             | -     | -     | [COM3]                    | -      | -      | -        | EVENTOU"             |

| PB10      | -      | TIM2_CH3           | -        | -          | I2C2_SCL      | -          | -          | USART3_TX     | -     | -     | SEG10                     | -      | -      | -        | EVENTOU              |

| PB11      | -      | TIM2_CH4           | -        | -          | I2C2_SDA      | -          | -          | USART3_RX     | -     | -     | SEG11                     | -      | -      | -        | EVENTOU              |

| PB12      | -      | -                  | -        | TIM10_CH1  | I2C2_<br>SMBA | SPI2_NSS   | -          | USART3_CK     | -     | -     | SEG12                     | -      | -      | -        | EVENTOU              |

| PB13      | -      | -                  | -        | TIM9_CH1   | -             | SPI2_SCK   | -          | USART3_CTS    | -     | -     | SEG13                     | -      | -      | -        | EVENTOU              |

| PB14      | -      | -                  | -        | TIM9_CH2   | -             | SPI2_MISO  | -          | USART3_RTS    | -     | -     | SEG14                     | -      | -      | -        | EVENTOU              |

| PB15      | -      | -                  | -        | TIM11_CH1  | -             | SPI2_MOSI  | -          | -             | -     | -     | SEG15                     | -      | -      | -        | EVENTOU              |

| PC0       | -      | -                  | -        | -          | -             | -          | -          | -             | -     | -     | SEG18                     | -      | -      | TIMx_IC1 | EVENTOU              |

| PC1       | -      | -                  | -        | -          | -             | -          | -          | -             | -     | -     | SEG19                     | -      | -      | TIMx_IC2 | EVENTOU              |

| PC2       | -      | -                  | -        | -          | -             | -          | -          | -             | -     | -     | SEG20                     | -      | -      | TIMx_IC3 | EVENTOU              |

| PC3       | -      | -                  | -        | -          | -             | -          | -          | -             | -     | -     | SEG21                     | -      | -      | TIMx_IC4 | EVENTOU              |

| PC4       | -      | -                  | -        | -          | -             | -          | -          | -             | -     | -     | SEG22                     | -      | -      | TIMx_IC1 | EVENTOU              |

| PC5       | -      | -                  | -        | -          | -             | -          | -          | -             | -     | -     | SEG23                     | -      | -      | TIMx_IC2 | EVENTOU              |

| PC6       | -      | -                  | TIM3_CH1 | -          | -             | -          | -          | -             | -     | -     | SEG24                     | -      | -      | TIMx_IC3 | EVENTOU              |

| PC7       | -      | -                  | TIM3_CH2 | -          | -             | -          | -          | -             | -     | -     | SEG25                     | -      | -      | TIMx_IC4 | EVENTOU              |

| PC8       | -      | -                  | TIM3_CH3 | -          | -             | -          | -          | -             | -     | -     | SEG26                     | -      | -      | TIMx_IC1 | EVENTOU"             |

| PC9       | -      | -                  | TIM3_CH4 | -          | -             | -          | -          | -             | -     | -     | SEG27                     | -      | -      | TIMx_IC2 | EVENTOU              |

| PC10      | -      | -                  | -        | -          | -             | -          | -          | USART3_TX     | -     | -     | COM4 /<br>SEG28/<br>SEG40 | -      | -      | TIMx_IC3 | EVENTOU              |

Pin descriptions

|                    |        |       |          | Table 9.   | Alterna | te functio | n inpu     | t/output (co   | ntinue | ed)   |                            |        |        |          |       |

|--------------------|--------|-------|----------|------------|---------|------------|------------|----------------|--------|-------|----------------------------|--------|--------|----------|-------|

|                    |        |       |          |            |         | Digital al | ternate fu | inction number |        |       |                            |        |        |          |       |

| Port name          | AFIO0  | AFIO1 | AFIO2    | AFIO3      | AFIO4   | AFIO5      | AFOI6      | AFIO7          | AFIO8  | AFIO9 | AFIO11                     | AFIO12 | AFIO13 | AFIO14   | AFIC  |

| Port name          |        |       |          |            |         | A          | lternate f | unction        |        |       |                            |        |        |          |       |

|                    | SYSTEM | TIM2  | TIM3/4   | TIM9/10/11 | I2C1/2  | SPI1/2     | N/A        | USART1/2/3     | N/A    | N/A   | LCD                        | N/A    | N/A    | RI       | SYS   |

| PC11               | -      | -     | -        | -          | -       | -          | -          | USART3_RX      | -      | -     | COM5 /<br>SEG29 /<br>SEG41 | -      | -      | TIMx_IC4 | EVEN  |

| PC12               | -      | -     | -        | -          | -       | -          | -          | USART3_CK      | -      | -     | COM6 /<br>SEG30 /<br>SEG42 | -      | -      | TIMx_IC1 | EVEN. |

| PC13-<br>WKUP2     | -      | -     | -        | -          | -       | -          | -          | -              | -      | -     | -                          | -      | -      | TIMx_IC2 | EVEN  |

| PC14-<br>OSC32_IN  | -      | -     | -        | _          | -       | -          | -          | -              | -      | -     | -                          | -      | -      | TIMx_IC3 | EVEN  |

| PC15-<br>OSC32_OUT | -      | -     | -        | -          | -       | -          | -          | -              | -      | -     | -                          | -      | -      | TIMx_IC4 | EVEN  |

| PD0                | -      | -     | -        | TIM9_CH1   | -       | SPI2_NSS   | -          | -              | -      | -     | -                          | -      | -      | TIMx_IC1 | EVEN  |

| PD1                | -      | -     | -        | -          | -       | SPI2_SCK   | -          | -              | -      | -     | -                          | -      | -      | TIMx_IC2 | EVEN  |

| PD2                | -      | -     | TIM3_ETR | -          | -       | -          | -          | -              | -      | -     | COM7 /<br>SEG31/<br>SEG43  | -      | -      | TIMx_IC3 | EVEN  |

| PD3                | -      | -     | -        | -          | -       | SPI2_MISO  | -          | USART2_CTS     | -      | -     | -                          | -      | -      | TIMx_IC4 | EVEN  |

| PD4                | -      | -     | -        | -          | -       | SPI2_MOSI  | -          | USART2_RTS     | -      | -     | -                          | -      | -      | TIMx_IC1 | EVEN  |

| PD5                | -      | -     | -        | -          | -       | -          | -          | USART2_TX      | -      | -     | -                          | -      | -      | TIMx_IC2 | EVEN  |

| PD6                | -      | -     | -        | -          | -       | -          | -          | USART2_RX      | -      | -     | -                          | -      | -      | TIMx_IC3 | EVEN  |

| PD7                | -      | -     | -        | TIM9_CH2   | -       | -          | -          | USART2_CK      | -      | -     | -                          | -      | -      | TIMx_IC4 | EVEN  |

| PD8                | -      | -     | -        | -          | -       | -          | -          | USART3_TX      | -      | -     | -                          | -      | -      | TIMx_IC1 | EVEN  |

| PD9                | -      | -     | -        | -          | -       | -          | -          | USART3_RX      | -      | -     | -                          | -      | -      | TIMx_IC2 | EVEN  |

| PD10               | -      | -     | -        | -          | -       | -          | -          | USART3_CK      | -      | -     | -                          | -      | -      | TIMx_IC3 | EVEN  |

| PD11               | -      | -     | -        | -          | -       | -          | -          | USART3_CTS     | -      | -     | -                          | -      | -      | TIMx_IC4 | EVEN  |

| PD12               | -      | -     | TIM4_CH1 | -          | -       | -          | -          | USART3_RTS     | -      | -     | -                          | -      | -      | TIMx_IC1 | EVEN  |

#### Table 9. Alternate function input/output (continued)

45/133

STM32L151x6/8/B STM32L152x6/8/B

Pin descriptions

| Symbol               | Parameter          | Cond                                                | itions                                                | f                 | Тур  |       | Max <sup>(1)</sup> |                    | Unit |

|----------------------|--------------------|-----------------------------------------------------|-------------------------------------------------------|-------------------|------|-------|--------------------|--------------------|------|

| Symbol               | Falailletei        |                                                     |                                                       | f <sub>HCLK</sub> | 'yp  | 55 °C | 85 °C              | 105 °C             | Unit |

|                      |                    |                                                     | Range 3,                                              | 1 MHz             | 200  | 300   | 300                | 300                |      |

|                      | f = f              |                                                     | V <sub>CORE</sub> =1.2 V                              | 2 MHz             | 380  | 500   | 500                | 500                | μA   |

|                      |                    | f <sub>HSE</sub> = f <sub>HCLK</sub>                | VOS[1:0] = 11                                         | 4 MHz             | 720  | 860   | 860                | 860 <sup>(3)</sup> |      |

|                      |                    | up to 16 MHz,                                       | Range 2,                                              | 4 MHz             | 0.9  | 1     | 1                  | 1                  |      |

|                      |                    | included<br>f <sub>HSE</sub> = f <sub>HCLK</sub> /2 | V <sub>CORE</sub> =1.5 V                              | 8 MHz             | 1.65 | 2     | 2                  | 2                  |      |

|                      |                    | above 16 MHz<br>(PLL ON) <sup>(2)</sup>             | VOS[1:0] = 10                                         | 16 MHz            | 3.2  | 3.7   | 3.7                | 3.7                |      |

| Supply curren        | Supply current     |                                                     | Range 1,                                              | 8 MHz             | 2    | 2.5   | 2.5                | 2.5                |      |

| I <sub>DD (Run</sub> | in Run mode.       |                                                     | V <sub>CORE</sub> =1.8 V                              | 16 MHz            | 4    | 4.5   | 4.5                | 4.5                |      |

| from                 | from RAM,          |                                                     | VOS[1:0] = 01                                         | 32 MHz            | 7.7  | 8.5   | 8.5                | 8.5                | mA   |

| RAM)                 | Flash switched off |                                                     | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | 16 MHz            | 3.3  | 3.8   | 3.8                | 3.8                |      |

|                      | (16 MHz)           | (16 MHz)                                            | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | 32 MHz            | 7.8  | 9.2   | 9.2                | 9.2                |      |

|                      |                    | ISI clock, 65 kHz                                   | Range 3,                                              | 65 kHz            | 40   | 60    | 60                 | 80                 |      |

|                      |                    | MSI clock, 524 kHz                                  | V <sub>CORE</sub> =1.2 V                              | 524 kHz           | 110  | 140   | 140                | 160                | μA   |

|                      |                    | MSI clock, 4.2 MHz                                  | VOS[1:0] = 11                                         | 4.2 MHz           | 700  | 800   | 800                | 820                |      |

#### Table 18. Current consumption in Run mode, code with data processing running from RAM

1. Guaranteed by characterization results, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

3. Tested in production.

| 0h.al                                 | Demonster                      | r Conditions                                                   |                                                       |                   | <b>T</b> |       | Max <sup>(1</sup>  | )      | 11   |

|---------------------------------------|--------------------------------|----------------------------------------------------------------|-------------------------------------------------------|-------------------|----------|-------|--------------------|--------|------|

| Symbol                                | Parameter                      | Cond                                                           | litions                                               | f <sub>HCLK</sub> | Тур      | 55 °C | 85 °C              | 105 °C | Unit |

|                                       |                                |                                                                | Range 3,                                              | 1 MHz             | 80       | 140   | 140                | 140    |      |

|                                       |                                |                                                                | V <sub>CORE</sub> =1.2 V                              | 2 MHz             | 150      | 210   | 210                | 210    |      |

|                                       |                                |                                                                | VOS[1:0] = 11 4 MHz 280 330                           |                   | 330      | 330   | 330 <sup>(3)</sup> |        |      |

|                                       |                                | f <sub>HSE</sub> = f <sub>HCLK</sub> up to<br>16 MHz included, | Range 2,                                              | 4 MHz             | 280      | 400   | 400                | 400    |      |

|                                       | Supply                         | $f_{HSE} = f_{HCLK}/2$                                         | V <sub>CORE</sub> =1.5 V                              | 8 MHz             | 450      | 550   | 550                | 550    |      |

|                                       | Supply                         | ON) <sup>(2)</sup><br>Sleep                                    | VOS[1:0] = 10                                         | 16 MHz            | 900      | 1050  | 1050               | 1050   |      |

|                                       | Sleep                          |                                                                | Range 1,                                              | 8 MHz             | 550      | 650   | 650                | 650    |      |

|                                       | mode,<br>code                  |                                                                | V <sub>CORE</sub> =1.8 V                              | 16 MHz            | 1050     | 1200  | 1200               | 1200   |      |

|                                       | executed                       |                                                                | VOS[1:0] = 01                                         | 32 MHz            | 2300     | 2500  | 2500               | 2500   | μA   |

| from RAM,<br>Flash<br>switched<br>OFF | HSI clock source               | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10          | 16 MHz                                                | 1000              | 1100     | 1100  | 1100               |        |      |

|                                       | on                             | (16 MHz)                                                       | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | 32 MHz            | 2300     | 2500  | 2500               | 2500   |      |

|                                       |                                | MSI clock, 65 kHz                                              | Range 3,                                              | 65 kHz            | 30       | 50    | 50                 | 60     |      |

| I <sub>DD</sub><br>(Sleep)            |                                | MSI clock, 524 kHz                                             | V <sub>CORE</sub> =1.2 V                              | 524 kHz           | 50       | 70    | 70                 | 80     |      |

| (Sleep)                               |                                | MSI clock, 4.2 MHz                                             |                                                       | 240               | 240      | 250   |                    |        |      |

|                                       |                                |                                                                |                                                       | 1 MHz             | 80       | 140   | 140                | 140    | -    |

|                                       |                                |                                                                | V <sub>CORE</sub> =1.2 V                              | 2 MHz             | 150      | 210   | 210                | 210    |      |

|                                       |                                |                                                                | VOS[1:0] = 11                                         | 4 MHz             | 290      | 350   | 350                | 350    |      |

|                                       |                                | f <sub>HSE</sub> = f <sub>HCLK</sub> up to<br>16 MHz included, | Range 2,                                              | 4 MHz             | 300      | 400   | 400                | 400    |      |

|                                       | Supply                         | $f_{HSE} = f_{HCLK}/2$                                         | V <sub>CORE</sub> =1.5 V                              | 8 MHz             | 500      | 600   | 600                | 600    |      |

|                                       | current in                     | above 16 MHz (PLL ON) <sup>(2)</sup>                           | VOS[1:0] = 10                                         | 16 MHz            | 1000     | 1100  | 1100               | 1100   |      |

|                                       | Sleep<br>mode,                 |                                                                | Range 1,                                              | 8 MHz             | 550      | 650   | 650                | 650    | μA   |

|                                       | code<br>executed<br>from Flash |                                                                | V <sub>CORE</sub> =1.8 V                              | 16 MHz            | 1050     | 1200  | 1200               | 1200   | •    |

|                                       |                                |                                                                | VOS[1:0] = 01                                         | 32 MHz            | 2300     | 2500  | 2500               | 2500   |      |

|                                       |                                | HSI clock source                                               | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | 16 MHz            | 1000     | 1100  | 1100               | 1100   |      |

|                                       |                                | (16 MHz)                                                       | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | 32 MHz            | 2300     | 2500  | 2500               | 2500   |      |

Table 19. Current consumption in Sleep mode

| Symbol                | Parameter                                                         | Co                                        | onditions                       |                                                                          | <b>Typ</b><br>(1) | Max<br>(1)(2) | Unit |

|-----------------------|-------------------------------------------------------------------|-------------------------------------------|---------------------------------|--------------------------------------------------------------------------|-------------------|---------------|------|

|                       |                                                                   |                                           |                                 | $T_A = -40^{\circ}C \text{ to } 25^{\circ}C$<br>$V_{DD} = 1.8 \text{ V}$ | 1.2               | 2.75          |      |

|                       |                                                                   |                                           | LCD                             | $T_A = -40^{\circ}C$ to $25^{\circ}C$                                    | 1.4               | 4             |      |

|                       |                                                                   |                                           | OFF                             | T <sub>A</sub> = 55°C                                                    | 2.6               | 6             |      |

|                       |                                                                   |                                           |                                 | T <sub>A</sub> = 85°C                                                    | 4.8               | 10            |      |

|                       |                                                                   | RTC clocked by LSI,                       |                                 | T <sub>A</sub> = 105°C                                                   | 10.2              | 23            |      |

|                       |                                                                   | regulator in LP mode,                     |                                 | $T_A = -40^{\circ}C$ to $25^{\circ}C$                                    | 3.3               | 6             |      |

|                       |                                                                   | HSI and HSE OFF<br>(no independent        | LCD ON<br>(static               | T <sub>A</sub> = 55°C                                                    | 4.5               | 8             |      |

|                       |                                                                   | watchdog)                                 | duty) <sup>(3)</sup>            | T <sub>A</sub> = 85°C                                                    | 6.6               | 12            |      |

|                       |                                                                   |                                           |                                 | T <sub>A</sub> = 105°C                                                   | 13.6              | 27            |      |

|                       |                                                                   |                                           |                                 | $T_A = -40^{\circ}C$ to $25^{\circ}C$                                    | 7.7               | 10            |      |

|                       |                                                                   |                                           | LCD ON<br>(1/8                  | T <sub>A</sub> = 55°C                                                    | 8.6               | 12            |      |

|                       |                                                                   |                                           | duty) <sup>(4)</sup>            | T <sub>A</sub> = 85°C                                                    | 10.7              | 16            |      |

|                       |                                                                   |                                           |                                 | T <sub>A</sub> = 105°C                                                   | 19.8              | 40            |      |

|                       | Supply current                                                    |                                           | LCD<br>OFF                      | $T_A$ = -40°C to 25°C                                                    | 1.6               | 4             |      |

| I <sub>DD (Stop</sub> | in Stop mode<br>with RTC                                          |                                           |                                 | T <sub>A</sub> = 55°C                                                    | 2.7               | 6             | μΑ   |

| with RTC)             | enabled                                                           |                                           |                                 | T <sub>A</sub> = 85°C                                                    | 4.8               | 10            |      |

|                       |                                                                   |                                           |                                 | T <sub>A</sub> = 105°C                                                   | 10.3              | 23            |      |

|                       |                                                                   | RTC clocked by LSE external clock (32.768 |                                 | $T_A$ = -40°C to 25°C                                                    | 3.6               | 6             |      |

|                       |                                                                   | kHz), regulator in LP                     | LCD ON                          | T <sub>A</sub> = 55°C                                                    | 4.6               | 8             |      |

|                       |                                                                   | mode, HSI and HSE<br>OFF (no independent  | (static<br>duty) <sup>(3)</sup> | T <sub>A</sub> = 85°C                                                    | 6.7               | 12            |      |

|                       |                                                                   | watchdog)                                 |                                 | T <sub>A</sub> = 105°C                                                   | 10.9              | 23            |      |

|                       |                                                                   |                                           |                                 | $T_A = -40^{\circ}C$ to $25^{\circ}C$                                    | 7.6               | 10            |      |

|                       |                                                                   |                                           | LCD ON<br>(1/8                  | T <sub>A</sub> = 55°C                                                    | 8.6               | 12            |      |

|                       |                                                                   |                                           | duty) <sup>(4)</sup>            | T <sub>A</sub> = 85°C                                                    | 10.7              | 16            |      |

|                       |                                                                   |                                           |                                 | T <sub>A</sub> = 105°C                                                   | 19.8              | 40            |      |

|                       |                                                                   |                                           |                                 | $T_A = -40^{\circ}C \text{ to } 25^{\circ}C$<br>$V_{DD} = 1.8 \text{ V}$ | 1.45              | -             |      |

|                       | RTC clocked by LSE<br>(no independent<br>watchdog) <sup>(5)</sup> |                                           | LCD<br>OFF                      | $T_A = -40^{\circ}C \text{ to } 25^{\circ}C$<br>$V_{DD} = 3.0 \text{ V}$ | 1.9               | -             |      |

|                       |                                                                   | ,                                         |                                 | $T_A = -40^{\circ}C \text{ to } 25^{\circ}C$<br>$V_{DD} = 3.6 \text{ V}$ | 2.2               | -             |      |

Table 22. Typical and maximum current consumptions in Stop mode

|      |                    | Туріса                                                | I consumption,                                        | V <sub>DD</sub> = 3.0 V, T <sub>A</sub>               | = 25 °C                    |                                |

|------|--------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|----------------------------|--------------------------------|

| F    | Peripheral         | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | Range 3,<br>V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | Low power<br>sleep and run | Unit                           |

|      | TIM2               | 13                                                    | 10.5                                                  | 8                                                     | 10.5                       |                                |

|      | TIM3               | 14                                                    | 12                                                    | 9                                                     | 12                         |                                |

|      | TIM4               | 12.5                                                  | 10.5                                                  | 8                                                     | 11                         |                                |

|      | TIM6               | 5.5                                                   | 4.5                                                   | 3.5                                                   | 4.5                        |                                |

|      | TIM7               | 5.5                                                   | 5                                                     | 3.5                                                   | 4.5                        |                                |

|      | LCD                | 5.5                                                   | 5                                                     | 3.5                                                   | 5                          |                                |

|      | WWDG               | 4                                                     | 3.5                                                   | 2.5                                                   | 3.5                        |                                |

| APB1 | SPI2               | 5.5                                                   | 5                                                     | 4                                                     | 5                          | µA/MHz                         |

| APDI | USART2             | 9                                                     | 8                                                     | 5.5                                                   | 8.5                        | (f <sub>HCLK</sub> )           |

|      | USART3             | 10.5                                                  | 9                                                     | 6                                                     | 8                          |                                |

|      | I2C1               | 8.5                                                   | 7                                                     | 5.5                                                   | 7.5                        |                                |

|      | I2C2               | 8.5                                                   | 7                                                     | 5.5                                                   | 6.5                        |                                |

|      | USB                | 12.5                                                  | 10                                                    | 6.5                                                   | 10                         |                                |

|      | PWR                | 4.5                                                   | 4                                                     | 3                                                     | 3.5                        |                                |

|      | DAC                | 9                                                     | 7.5                                                   | 6                                                     | 7                          |                                |

|      | COMP               | 4.5                                                   | 4                                                     | 3.5                                                   | 4.5                        |                                |

|      | SYSCFG & RI        | 3                                                     | 2.5                                                   | 2                                                     | 2.5                        |                                |

|      | TIM9               | 9                                                     | 7.5                                                   | 6                                                     | 7                          |                                |

|      | TIM10              | 6.5                                                   | 5.5                                                   | 4.5                                                   | 5.5                        |                                |

| APB2 | TIM11              | 7                                                     | 6                                                     | 4.5                                                   | 5.5                        | μΑ/ΜΗz<br>(f <sub>HCLK</sub> ) |

|      | ADC <sup>(2)</sup> | 11.5                                                  | 9.5                                                   | 8                                                     | 9                          | ('HCLK/                        |

|      | SPI1               | 5                                                     | 4.5                                                   | 3                                                     | 4                          |                                |

|      | USART1             | 9                                                     | 7.5                                                   | 6                                                     | 7.5                        |                                |

Table 24. Peripheral current consumption<sup>(1)</sup>

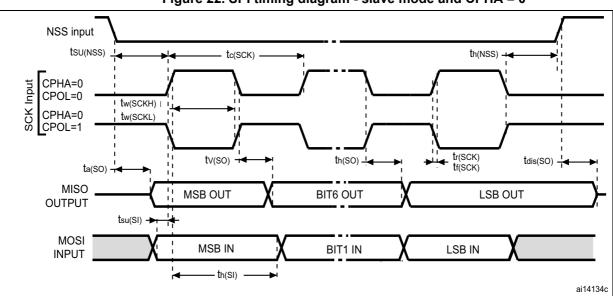

Figure 22. SPI timing diagram - slave mode and CPHA = 0

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}$

| Symbol              | Parameter                                     | Conditions                                                                                                                                | Min | Тур | Max <sup>(1)</sup> | Unit       |

|---------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--------------------|------------|

| V <sub>DDA</sub>    | Analog supply voltage                         | -                                                                                                                                         | 1.  | -   | 3.6                | V          |

| V <sub>IN</sub>     | Comparator 2 input voltage range              | -                                                                                                                                         | 0   | -   | V <sub>DDA</sub>   | V          |

| t                   | Comparator startup time                       | Fast mode                                                                                                                                 | -   | 15  | 20                 |            |

| t <sub>start</sub>  |                                               | Slow mode                                                                                                                                 | -   | 20  | 25                 |            |

| +                   | Propagation delay <sup>(2)</sup> in slow mode | 1. V ≤V <sub>DDA</sub> ≤2.7 V                                                                                                             | -   | 1.8 | 3.5                |            |

| t <sub>d slow</sub> | Fropagation delay fin slow mode               | 2.7 V ≤V <sub>DDA</sub> ≤3.6 V                                                                                                            | -   | 2.5 | 6                  | μs         |

| +                   | Propagation delay <sup>(2)</sup> in fast mode | 1. V ⊴V <sub>DDA</sub> ⊴2.7 V                                                                                                             | -   | 0.8 | 2                  |            |

| t <sub>d fast</sub> | Fropagation delay 7 in last mode              | 2.7 V ≤V <sub>DDA</sub> ≤3.6 V                                                                                                            | -   | 1.2 | 4                  |            |

| V <sub>offset</sub> | Comparator offset error                       | -                                                                                                                                         | -   | ±4  | ±20                | mV         |

| dThreshold/<br>dt   | Threshold voltage temperature coefficient     | $V_{DDA} = 3.3V$<br>$T_{A} = 0 \text{ to } 50 \circ C$<br>$V = V_{REFINT},$<br>$3/4 V_{REFINT},$<br>$1/2 V_{REFINT},$<br>$1/4 V_{REFINT}$ | -   | 15  | 100                | ppm<br>/°C |

|                     | Current consumption <sup>(3)</sup>            | Fast mode                                                                                                                                 | -   | 3.5 | 5                  |            |

| I <sub>COMP2</sub>  |                                               | Slow mode                                                                                                                                 | -   | 0.5 | 2                  | μA         |

| Table 61. | Comparator | 2 characteristics |

|-----------|------------|-------------------|

|-----------|------------|-------------------|

1. Guaranteed by characterization results.

2. The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

3. Comparator consumption only. Internal reference voltage (necessary for comparator operation) is not included.

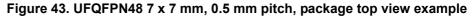

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

|        | Min         | Тур   | Max   | Тур                   | Min    | Мах    |

| E3     | -           | 7.500 | -     | -                     | 0.2953 | -      |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |

| К      | 0°          | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |

| L      | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000 | -     | -                     | 0.0394 | -      |

| CCC    | -           | -     | 0.080 | -                     | -      | 0.0031 |

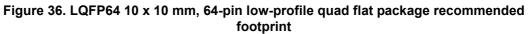

# Table 64. LQFP64 10 x 10 mm, 64-pin low-profile quad flat package mechanicaldata (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are in millimeters.

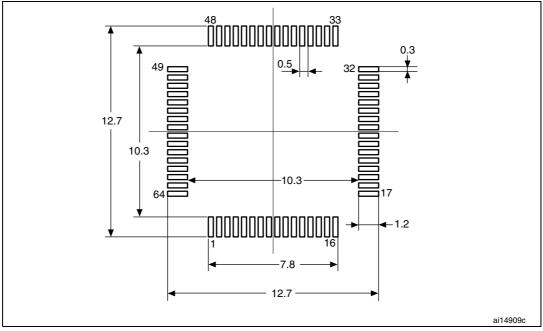

### **UFQFPN48** device marking

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

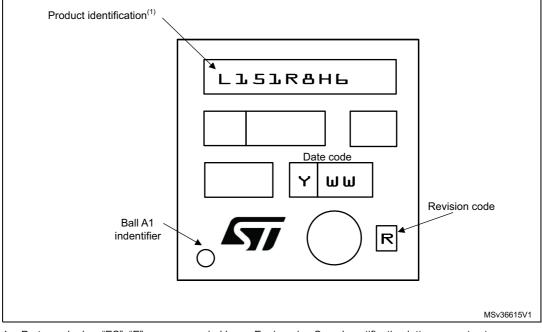

### **TFBGA64** device marking

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Figure 49. TFBGA64 5 x 5 mm, 0.5 mm pitch, package top view example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

## 9 Revision history

| Table 73. Document revision history |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|-------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Date                                | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 02-Jul-2010                         | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 01-Oct-2010                         | 2        | Removed 5 V tolerance (FT) from PA3, PB0 and PC3 in <i>Table 8:</i><br><i>STM32L15xx6/8/B pin definitions</i><br>Updated <i>Table 14: Embedded reset and power control block</i><br><i>characteristics</i><br>Updated <i>Table 16: Embedded internal reference voltage</i><br>Added <i>Table 53: ADC clock frequency</i><br>Updated <i>Table 54: ADC characteristics</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |