Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betails                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 21                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                |

| Data Converters            | A/D 10x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f25j10-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.2 Power Supply Pins

#### 2.2.1 DECOUPLING CAPACITORS

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS, is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A 0.1  $\mu$ F (100 nF), 10-20V capacitor is recommended. The capacitor should be a low-ESR device with a resonance frequency in the range of 200 MHz and higher. Ceramic capacitors are recommended.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is no greater than 0.25 inch (6 mm).

- Handling high-frequency noise: If the board is experiencing high-frequency noise (upward of tens of MHz), add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to each primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible (e.g., 0.1  $\mu$ F in parallel with 0.001  $\mu$ F).

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB trace inductance.

#### 2.2.2 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including microcontrollers to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

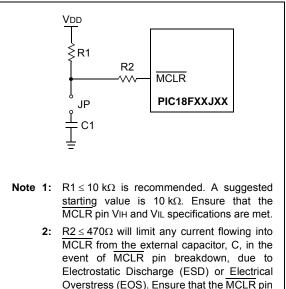

## 2.3 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions: device Reset, and device programming and debugging. If programming and debugging are not required in the end application, a direct connection to VDD may be all that is required. The addition of other components, to help increase the application's resistance to spurious Resets from voltage sags, may be beneficial. A typical configuration is shown in Figure 2-1. Other circuit designs may be implemented depending on the application's requirements.

During programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{\text{MCLR}}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R1 and C1 will need to be adjusted based on the application and PCB requirements. For example, it is recommended that the capacitor, C1, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations by using a jumper (Figure 2-2). The jumper is replaced for normal run-time operations.

Any components associated with the  $\overline{\text{MCLR}}$  pin should be placed within 0.25 inch (6 mm) of the pin.

#### FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

VIH and VIL specifications are met.

## 6.1.4.2 Return Stack Pointer (STKPTR)

The STKPTR register (Register 6-1) contains the Stack Pointer value, the STKFUL (Stack Overflow) status bit and the STKUNF (Stack Underflow) status bits. The value of the Stack Pointer can be 0 through 31. The Stack Pointer increments before values are pushed onto the stack and decrements after values are popped off the stack. On Reset, the Stack Pointer value will be zero. The user may read and write the Stack Pointer value. This feature can be used by a Real-Time Operating System (RTOS) for return stack maintenance.

After the PC is pushed onto the stack 31 times (without popping any values off the stack), the STKFUL bit is set. The STKFUL bit is cleared by software or by a POR.

The action that takes place when the stack becomes full depends on the state of the STVREN (Stack Overflow Reset Enable) Configuration bit. (Refer to **Section 21.1 "Configuration Bits**" for a description of the device Configuration bits.) If STVREN is set (default), the 31st push will push the (PC + 2) value onto the stack, set the STKFUL bit and reset the device. The STKFUL bit will remain set and the Stack Pointer will be set to zero.

If STVREN is cleared, the STKFUL bit will be set on the 31st push and the Stack Pointer will increment to 31. Any additional pushes will not overwrite the 31st push and the STKPTR will remain at 31.

When the stack has been popped enough times to unload the stack, the next pop will return a value of zero to the PC and sets the STKUNF bit, while the Stack Pointer remains at zero. The STKUNF bit will remain set until cleared by software or until a POR occurs.

| Note: | Returning a value of zero to the PC on an<br>underflow has the effect of vectoring the<br>program to the Reset vector, where the<br>stack conditions can be verified and<br>appropriate actions can be taken. This is |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | not the same as a Reset, as the contents of the SFRs are not affected.                                                                                                                                                |

#### 6.1.4.3 PUSH and POP Instructions

Since the Top-of-Stack is readable and writable, the ability to push values onto the stack and pull values off the stack without disturbing normal program execution is a desirable feature. The PIC18 instruction set includes two instructions, PUSH and POP, that permit the TOS to be manipulated under software control. TOSU, TOSH and TOSL can be modified to place data or a return address on the stack.

The PUSH instruction places the current PC value onto the stack. This increments the Stack Pointer and loads the current PC value onto the stack.

The POP instruction discards the current TOS by decrementing the Stack Pointer. The previous value pushed onto the stack then becomes the TOS value.

| R/C-0                     | R/C-0                 | U-0              | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |

|---------------------------|-----------------------|------------------|-------|------------------------------------|-------|-----------------|-------|

| STKFUL <sup>(1)</sup>     | STKUNF <sup>(1)</sup> | —                | SP4   | SP3                                | SP2   | SP1             | SP0   |

| bit 7                     |                       |                  |       |                                    |       |                 | bit 0 |

|                           |                       |                  |       |                                    |       |                 |       |

| Legend: C = Clearable bit |                       |                  |       |                                    |       |                 |       |

| R = Readable              | bit                   | W = Writable I   | oit   | U = Unimplemented bit, read as '0' |       |                 |       |

| -n = Value at F           | POR                   | '1' = Bit is set |       | '0' = Bit is clea                  | ared  | x = Bit is unkr | nown  |

#### REGISTER 6-1: STKPTR: STACK POINTER REGISTER

| bit 7   | STKFUL: Stack Full Flag bit <sup>(1)</sup>      |

|---------|-------------------------------------------------|

|         | 1 = Stack became full or overflowed             |

|         | 0 = Stack has not become full or overflowed     |

| bit 6   | STKUNF: Stack Underflow Flag bit <sup>(1)</sup> |

|         | 1 = Stack underflow occurred                    |

|         | 0 = Stack underflow did not occur               |

| bit 5   | Unimplemented: Read as '0'                      |

| bit 4-0 | SP<4:0>: Stack Pointer Location bits            |

**Note 1:** Bit 7 and bit 6 are cleared by user software or by a POR.

#### 6.4 Data Addressing Modes

| Note: | The execution of some instructions in the  |

|-------|--------------------------------------------|

|       | core PIC18 instruction set are changed     |

|       | when the PIC18 extended instruction set is |

|       | enabled. See Section 6.5 "Data Memory      |

|       | and the Extended Instruction Set" for      |

|       | more information.                          |

While the program memory can be addressed in only one way – through the program counter – information in the data memory space can be addressed in several ways. For most instructions, the addressing mode is fixed. Other instructions may use up to three modes, depending on which operands are used and whether or not the extended instruction set is enabled.

The addressing modes are:

- Inherent

- Literal

- Direct

- Indirect

An additional addressing mode, Indexed Literal Offset, is available when the extended instruction set is enabled (XINST Configuration bit = 1). Its operation is discussed in greater detail in **Section 6.5.1 "Indexed Addressing with Literal Offset**".

## 6.4.1 INHERENT AND LITERAL ADDRESSING

Many PIC18 control instructions do not need any argument at all; they either perform an operation that globally affects the device or they operate implicitly on one register. This addressing mode is known as Inherent Addressing. Examples include SLEEP, RESET and DAW.

Other instructions work in a similar way but require an additional explicit argument in the opcode. This is known as Literal Addressing mode because they require some literal value as an argument. Examples include ADDLW and MOVLW, which respectively, add or move a literal value to the W register. Other examples include CALL and GOTO, which include a 20-bit program memory address.

#### 6.4.2 DIRECT ADDRESSING

Direct Addressing specifies all or part of the source and/or destination address of the operation within the opcode itself. The options are specified by the arguments accompanying the instruction.

In the core PIC18 instruction set, bit-oriented and byteoriented instructions use some version of Direct Addressing by default. All of these instructions include some 8-bit literal address as their Least Significant Byte. This address specifies either a register address in one of the banks of data RAM (Section 6.3.3 "General Purpose Register File") or a location in the Access Bank (Section 6.3.2 "Access Bank") as the data source for the instruction. The Access RAM bit 'a' determines how the address is interpreted. When 'a' is '1', the contents of the BSR (Section 6.3.1 "Bank Select Register (BSR)") are used with the address to determine the complete 12-bit address of the register. When 'a' is '0', the address is interpreted as being a register in the Access Bank. Addressing that uses the Access RAM is sometimes also known as Direct Forced Addressing mode.

A few instructions, such as MOVFF, include the entire 12-bit address (either source or destination) in their opcodes. In these cases, the BSR is ignored entirely.

The destination of the operation's results is determined by the destination bit 'd'. When 'd' is '1', the results are stored back in the source register, overwriting its original contents. When 'd' is '0', the results are stored in the W register. Instructions without the 'd' argument have a destination that is implicit in the instruction; their destination is either the target register being operated on or the W register.

#### 6.4.3 INDIRECT ADDRESSING

Indirect Addressing allows the user to access a location in data memory without giving a fixed address in the instruction. This is done by using File Select Registers (FSRs) as pointers to the locations to be read or written to. Since the FSRs are themselves located in RAM as Special Function Registers, they can also be directly manipulated under program control. This makes FSRs very useful in implementing data structures, such as tables and arrays in data memory.

The registers for Indirect Addressing are also implemented with Indirect File Operands (INDFs) that permit automatic manipulation of the pointer value with auto-incrementing, auto-decrementing or offsetting with another value. This allows for efficient code, using loops, such as the example of clearing an entire RAM bank in Example 6-5.

#### EXAMPLE 6-5: HOW TO CLEAR RAM (BANK 1) USING INDIRECT ADDRESSING

|        | LFSR  | FSR0, 100h | ; |                |

|--------|-------|------------|---|----------------|

| NEXT   | CLRF  | POSTINC0   | ; | Clear INDF     |

|        |       |            | ; | register then  |

|        |       |            | ; | inc pointer    |

|        | BTFSS | FSROH, 1   | ; | All done with  |

|        |       |            | ; | Bank1?         |

|        | BRA   | NEXT       | ; | NO, clear next |

| CONTIN | UE    |            | ; | YES, continue  |

|        |       |            |   |                |

## 9.0 INTERRUPTS

Members of the PIC18F45J10 family of devices have multiple interrupt sources and an interrupt priority feature that allows most interrupt sources to be assigned a high-priority level or a low-priority level. The high-priority interrupt vector is at 0008h and the low-priority interrupt vector is at 0018h. High-priority interrupt events will interrupt any low-priority interrupts that may be in progress.

There are thirteen registers which are used to control interrupt operation. These registers are:

- RCON

- INTCON

- INTCON2

- INTCON3

- PIR1, PIR2, PIR3

- PIE1, PIE2, PIE3

- IPR1, IPR2, IPR3

It is recommended that the Microchip header files supplied with MPLAB<sup>®</sup> IDE be used for the symbolic bit names in these registers. This allows the assembler/compiler to automatically take care of the placement of these bits within the specified register.

In general, interrupt sources have three bits to control their operation. They are:

- Flag bit to indicate that an interrupt event occurred

- Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set

- **Priority bit** to select high priority or low priority

The interrupt priority feature is enabled by setting the IPEN bit (RCON<7>). When interrupt priority is enabled, there are two bits which enable interrupts globally. Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set (high priority). Setting the GIEL bit (INTCON<6>) enables all interrupts that have the priority bit cleared (low priority). When the interrupt flag, enable bit and appropriate global interrupt enable bit are set, the interrupt will vector immediately to address 0008h or 0018h, depending on the priority bit setting. Individual interrupts can be disabled through their corresponding enable bits.

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup> mid-range devices. In Compatibility mode, the interrupt priority bits for each source have no effect. INTCON<6> is the PEIE bit which enables/disables all peripheral interrupt sources. INTCON<7> is the GIE bit which enables/disables all interrupt sources. All interrupts branch to address 0008h in Compatibility mode.

When an interrupt is responded to, the global interrupt enable bit is cleared to disable further interrupts. If the IPEN bit is cleared, this is the GIE bit. If interrupt priority levels are used, this will be either the GIEH or GIEL bit. High-priority interrupt sources can interrupt a low-priority interrupt. Low-priority interrupts are not processed while high-priority interrupts are in progress.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (0008h or 0018h). Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bits must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used) which re-enables interrupts.

For external interrupt events, such as the INTx pins or the PORTB input change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding enable bit or the GIE bit.

Note: Do not use the MOVFF instruction to modify any of the interrupt control registers while any interrupt is enabled. Doing so may cause erratic microcontroller behavior.

#### 15.4.6 PROGRAMMABLE DEAD-BAND DELAY

| Note: | Programmable          | de | ad-band | delay   | is | not  |

|-------|-----------------------|----|---------|---------|----|------|

|       | implemented           | in | 28-pin  | devices | 5  | with |

|       | standard CCP modules. |    |         |         |    |      |

In half-bridge applications, where all power switches are modulated at the PWM frequency at all times, the power switches normally require more time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on and the other turned off), both switches may be on for a short period of time until one switch completely turns off. During this brief interval, a very high current (*shootthrough current*) may flow through both power switches, shorting the bridge supply. To avoid this potentially destructive shoot-through current from flowing during switching, turning on either of the power switches is normally delayed to allow the other switch to completely turn off.

In the Half-Bridge Output mode, a digitally programmable dead-band delay is available to avoid shoot-through current from destroying the bridge power switches. The delay occurs at the signal transition from the nonactive state to the active state. See Figure 15-4 for an illustration. Bits PDC<6:0> of the ECCP1DEL register (Register 15-2) set the delay period in terms of microcontroller instruction cycles (TcY or 4 Tosc). These bits are not available in 28-pin devices as the standard CCP module does not support half-bridge operation.

#### 15.4.7 ENHANCED PWM AUTO-SHUTDOWN

When the ECCP1 is programmed for any of the Enhanced PWM modes, the active output pins may be configured for auto-shutdown. Auto-shutdown immediately places the Enhanced PWM output pins into a defined shutdown state when a shutdown event occurs.

A shutdown event can be caused by either of the comparator modules, a low level on the Fault input pin (FLT0) or any combination of these three sources. The comparators may be used to monitor a voltage input proportional to a current being monitored in the bridge circuit. If the voltage exceeds a threshold, the comparator switches state and triggers a shutdown. Alternatively, a low digital signal on FLT0 can also trigger a shutdown. The auto-shutdown feature can be disabled by not selecting any auto-shutdown sources. The auto-shutdown sources to be used are selected using the ECCPAS<2:0> bits (bits<6:4> of the ECCP1AS register).

When a shutdown occurs, the output pins are asynchronously placed in their shutdown states, specified by the PSSAC<1:0> and PSSBD<1:0> bits (ECCPAS<3:0>). Each pin pair (P1A/P1C and P1B/P1D) may be set to drive high, drive low or be tri-stated (not driving). The ECCPASE bit (ECCP1AS<7>) is also set to hold the Enhanced PWM outputs in their shutdown states.

The ECCPASE bit is set by hardware when a shutdown event occurs. If automatic restarts are not enabled, the ECCPASE bit is cleared by firmware when the cause of the shutdown clears. If automatic restarts are enabled, the ECCPASE bit is automatically cleared when the cause of the auto-shutdown has cleared.

If the ECCPASE bit is set when a PWM period begins, the PWM outputs remain in their shutdown state for that entire PWM period. When the ECCPASE bit is cleared, the PWM outputs will return to normal operation at the beginning of the next PWM period.

**Note:** Writing to the ECCPASE bit is disabled while a shutdown condition is active.

| R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0               |                     |                     |                     |                     |                     |                     |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                              | N/VV-0              | R/W-0               | R/W-0               | R/W-0               | R/W-0               | R/W-0               | R/W-0               |  |

| PRSEN                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PDC6 <sup>(1)</sup> | PDC5 <sup>(1)</sup> | PDC4 <sup>(1)</sup> | PDC3 <sup>(1)</sup> | PDC2 <sup>(1)</sup> | PDC1 <sup>(1)</sup> | PDC0 <sup>(1)</sup> |  |

| bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     |                     |                     |                     |                     |                     | bit 0               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                     |                     |                     |                     |                     |                     |                     |  |

| Legend:                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                     |                     |                     |                     |                     |                     |                     |  |

| R = Readable bit W = Writable bit                                                                                                                                                                                                                                                                                                                                                                                                                            |                     |                     |                     | U = Unimplem        | ented bit, read     | as '0'              |                     |  |

| -n = Value at POR '1' = Bit is set '0' =                                                                                                                                                                                                                                                                                                                                                                                                                     |                     |                     | '0' = Bit is clea   | ared                | x = Bit is unkn     | iown                |                     |  |

| bit 7 PRSEN: PWM Restart Enable bit<br>1 = Upon auto-shutdown, the ECCPASE bit clears automatically once the shutdown event goes away;<br>the PWM restarts automatically<br>0 = Upon auto-shutdown, ECCPASE must be cleared in software to restart the PWM<br>bit 6-0 PDC<6:0>: PWM Delay Count bits <sup>(1)</sup><br>Delay time, in number of FoSc/4 (4 * ToSc) cycles, between the scheduled and actual time for a PWM<br>signal to transition to active. |                     |                     |                     |                     |                     |                     |                     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                     |                     |                     |                     |                     |                     |                     |  |

## REGISTER 15-2: ECCP1DEL: PWM DEAD-BAND DELAY REGISTER

Note 1: Reserved on 28-pin devices; maintain these bits clear.

#### 15.4.9 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the ECCP module for PWM operation:

- 1. Configure the PWM pins, P1A and P1B (and P1C and P1D, if used), as inputs by setting the corresponding TRIS bits.

- 2. Set the PWM period by loading the PR2 register.

- 3. If auto-shutdown is required:

- Disable auto-shutdown (ECCPASE = 0)

- Configure source (FLT0, Comparator 1 or Comparator 2)

- Wait for non-shutdown condition

- Configure the ECCP module for the desired PWM mode and configuration by loading the CCP1CON register with the appropriate values:

- Select one of the available output configurations and direction with the P1M<1:0> bits.

- Select the polarities of the PWM output signals with the CCP1M<3:0> bits.

- 5. Set the PWM duty cycle by loading the CCPR1L register and CCP1CON<5:4> bits.

- 6. For Half-Bridge Output mode, set the deadband delay by loading ECCP1DEL<6:0> with the appropriate value.

- 7. If auto-shutdown operation is required, load the ECCP1AS register:

- Select the auto-shutdown sources using the ECCPAS<2:0> bits.

- Select the shutdown states of the PWM output pins using the PSSAC<1:0> and PSSBD<1:0> bits.

- Set the ECCPASE bit (ECCP1AS<7>).

- Configure the comparators using the CMCON register.

- Configure the comparator inputs as analog inputs.

- 8. If auto-restart operation is required, set the PRSEN bit (ECCP1DEL<7>).

- 9. Configure and start TMR2:

- Clear the TMR2 interrupt flag bit by clearing the TMR2IF bit (PIR1<1>).

- Set the TMR2 prescale value by loading the T2CKPS bits (T2CON<1:0>).

- Enable Timer2 by setting the TMR2ON bit (T2CON<2>).

- 10. Enable PWM outputs after a new PWM cycle has started:

- Wait until TMRx overflows (TMRxIF bit is set).

- Enable the CCP1/P1A, P1B, P1C and/or P1D pin outputs by clearing the respective TRIS bits.

- Clear the ECCPASE bit (ECCP1AS<7>).

## 15.4.10 OPERATION IN POWER-MANAGED MODES

In Sleep mode, all clock sources are disabled. Timer2 will not increment and the state of the module will not change. If the CCP1 pin is driving a value, it will continue to drive that value. When the device wakes up, it will continue from this state. If Two-Speed Start-ups are enabled, the initial start-up frequency from INTOSC and the postscaler may not be stable immediately.

In PRI\_IDLE mode, the primary clock will continue to clock the ECCP module without change. In all other power-managed modes, the selected power-managed mode clock will clock Timer2. Other power-managed mode clocks will most likely be different than the primary clock frequency.

#### 15.4.10.1 Operation with Fail-Safe Clock Monitor

If the Fail-Safe Clock Monitor is enabled, a clock failure will force the device into the power-managed RC\_RUN mode and the OSCFIF bit (PIR2<7>) will be set. The ECCP will then be clocked from the internal oscillator clock source, which may have a different clock frequency than the primary clock.

See the previous section for additional details.

#### 15.4.11 EFFECTS OF A RESET

Both Power-on Reset and subsequent Resets will force all ports to Input mode and the CCP registers to their Reset states.

This forces the Enhanced CCP module to reset to a state compatible with the standard CCP module.

## 17.2 EUSART Asynchronous Mode

The Asynchronous mode of operation is selected by clearing the SYNC bit (TXSTA<4>). In this mode, the EUSART uses standard Non-Return-to-Zero (NRZ) format (one Start bit, eight or nine data bits and one Stop bit). The most common data format is 8 bits. An on-chip, dedicated 8-bit/16-bit Baud Rate Generator can be used to derive standard baud rate frequencies from the oscillator.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent but use the same data format and baud rate. The Baud Rate Generator produces a clock, either x16 or x64 of the bit shift rate depending on the BRGH and BRG16 bits (TXSTA<2> and BAUDCON<3>). Parity is not supported by the hardware but can be implemented in software and stored as the 9th data bit.

When operating in Asynchronous mode, the EUSART module consists of the following important elements:

- Baud Rate Generator

- · Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

- Auto-Wake-up on Sync Break Character

- 12-Bit Break Character Transmit

- Auto-Baud Rate Detection

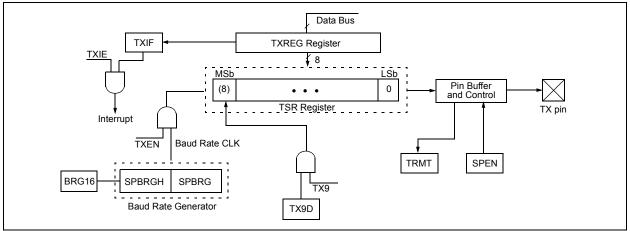

#### 17.2.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 17-3. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The Shift register obtains its data from the Read/Write Transmit Buffer register, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the Stop bit has been transmitted from the previous load. As soon as the Stop bit is transmitted, the TSR is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCY), the TXREG register is empty and the TXIF flag bit (PIR1<4>) is set. This interrupt can be enabled or disabled by setting or clearing the interrupt enable bit, TXIE (PIE1<4>). TXIF will be set regardless of the state of TXIE; it cannot be cleared in software. TXIF is also not cleared immediately upon loading TXREG, but becomes valid in the second instruction cycle following the load instruction. Polling TXIF immediately following a load of TXREG will return invalid results.

While TXIF indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. TRMT is a read-only bit which is set when the TSR register is empty. No interrupt logic is tied to this bit so the user has to poll this bit in order to determine if the TSR register is empty.

**Note 1:** The TSR register is not mapped in data memory so it is not available to the user.

2: Flag bit TXIF is set when enable bit TXEN is set.

To set up an Asynchronous Transmission:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing bit, SYNC, and setting bit, SPEN.

- 3. If interrupts are desired, set enable bit, TXIE.

- 4. If 9-bit transmission is desired, set transmit bit, TX9. Can be used as address/data bit.

- 5. Enable the transmission by setting bit, TXEN, which will also set bit, TXIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Load data to the TXREG register (starts transmission).

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

#### FIGURE 17-3: EUSART TRANSMIT BLOCK DIAGRAM

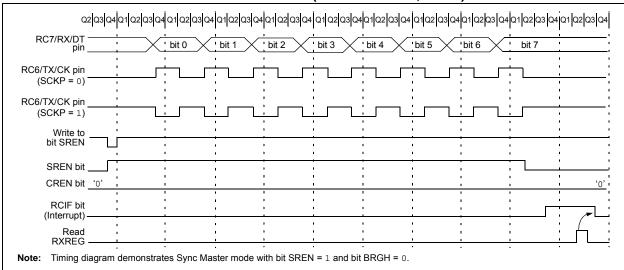

#### 17.3.2 EUSART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either the Single Receive Enable bit, SREN (RCSTA<5>), or the Continuous Receive Enable bit, CREN (RCSTA<4>). Data is sampled on the RX pin on the falling edge of the clock.

If enable bit SREN is set, only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set, then CREN takes precedence.

To set up a Synchronous Master Reception:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRG16 bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 3. Ensure bits, CREN and SREN, are clear.

- 4. If interrupts are desired, set enable bit, RCIE.

- 5. If 9-bit reception is desired, set bit, RX9.

- 6. If a single reception is required, set bit, SREN. For continuous reception, set bit, CREN.

- 7. Interrupt flag bit, RCIF, will be set when reception is complete and an interrupt will be generated if the enable bit, RCIE, was set.

- 8. Read the RCSTA register to get the 9th bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- 10. If any error occurred, clear the error by clearing bit, CREN.

- 11. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

## FIGURE 17-13: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

## TABLE 17-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

| Name                                                 | Bit 7                                                                                                     | Bit 6       | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------|--------|--------|--------|--------|--------|--------|----------------------------|

| INTCON                                               | GIE/GIEH                                                                                                  | PEIE/GIEL   | TMR0IE | INT0IE | RBIE   | TMR0IF | INT0IF | RBIF   | 47                         |

| PIR1                                                 | PSPIF <sup>(1)</sup>                                                                                      | ADIF        | RCIF   | TXIF   | SSP1IF | CCP1IF | TMR2IF | TMR1IF | 49                         |

| PIE1                                                 | PSPIE <sup>(1)</sup>                                                                                      | ADIE        | RCIE   | TXIE   | SSP1IE | CCP1IE | TMR2IE | TMR1IE | 49                         |

| IPR1                                                 | PSPIP <sup>(1)</sup>                                                                                      | ADIP        | RCIP   | TXIP   | SSP1IP | CCP1IP | TMR2IP | TMR1IP | 49                         |

| RCSTA                                                | SPEN                                                                                                      | RX9         | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 49                         |

| RCREG                                                | EUSART R                                                                                                  | eceive Regi | ster   |        |        |        |        |        | 49                         |

| TXSTA                                                | CSRC                                                                                                      | TX9         | TXEN   | SYNC   | SENDB  | BRGH   | TRMT   | TX9D   | 49                         |

| BAUDCON ABDOVF RCIDL - SCKP BRG16 - WUE ABDEN        |                                                                                                           |             |        |        |        |        |        |        | 49                         |

| SPBRGH EUSART Baud Rate Generator Register High Byte |                                                                                                           |             |        |        |        |        |        | 49     |                            |

| SPBRG EUSART Baud Rate Generator Register Low Byte   |                                                                                                           |             |        |        |        |        |        | 49     |                            |

| Legend: -                                            | <b>egend:</b> — = unimplemented, read as '0'. Shaded cells are not used for synchronous master reception. |             |        |        |        |        |        |        |                            |

Legenu. — – unimplemented, read as 0. Shaded cells are not used for synchronous master reco

**Note 1:** These bits are not implemented on 28-pin devices and should be read as '0'.

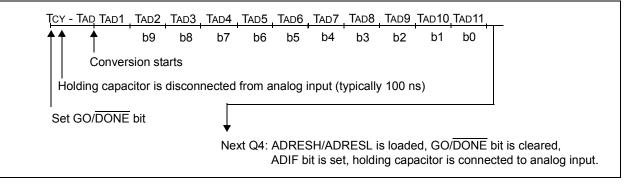

### 18.5 A/D Conversions

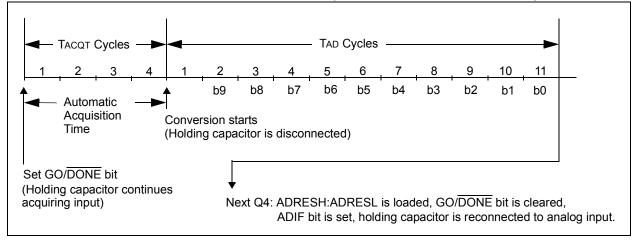

Figure 18-3 shows the operation of the A/D converter after the GO/DONE bit has been set and the ACQT<2:0> bits are cleared. A conversion is started after the following instruction to allow entry into Sleep mode before the conversion begins.

Figure 18-4 shows the operation of the A/D converter after the GO/DONE bit has been set, the ACQT<2:0> bits are set to '010' and selecting a 4 TAD acquisition time before the conversion starts.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The A/D Result register pair will NOT be updated with the partially completed A/D conversion sample. This means the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers).

After the A/D conversion is completed or aborted, a 2 TAD wait is required before the next acquisition can be started. After this wait, acquisition on the selected channel is automatically started.

| Note: | The GO/DONE bit should NOT be set in        |

|-------|---------------------------------------------|

|       | the same instruction that turns on the A/D. |

## 18.6 Use of the ECCP2 Trigger

An A/D conversion can be started by the "Special Event Trigger" of the ECCP2 module. This requires that the CCP2M<3:0> bits (CCP2CON<3:0>) be programmed as '1011' and that the A/D module is enabled (ADON bit is set). When the trigger occurs, the GO/DONE bit will be set, starting the A/D acquisition and conversion and the Timer1 (or Timer3) counter will be reset to zero. Timer1 (or Timer3) is reset to automatically repeat the A/D acquisition period with minimal software overhead (moving ADRESH/ADRESL to the desired location). The appropriate analog input channel must be selected and the minimum acquisition period is either timed by the user, or an appropriate TACQ time is selected before the Special Event Trigger sets the GO/DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), the Special Event Trigger will be ignored by the A/D module but will still reset the Timer1 (or Timer3) counter.

#### FIGURE 18-3: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 000, TACQ = 0)

#### FIGURE 18-4: A/D CONVERSION TAD CYCLES (ACQT<2:0> = 010, TACQ = 4 TAD)

## 20.0 COMPARATOR VOLTAGE REFERENCE MODULE

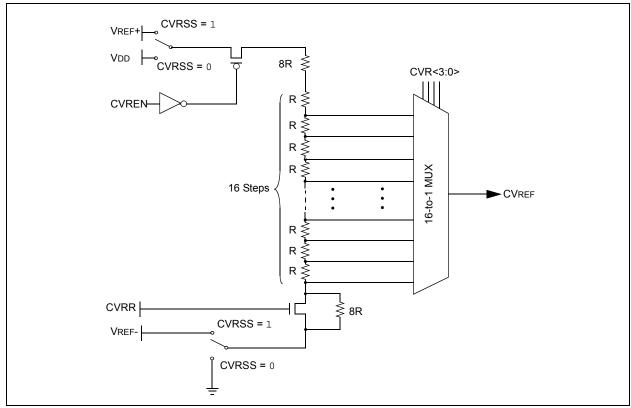

The comparator voltage reference is a 16-tap resistor ladder network that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it may also be used independently of them.

A block diagram of the module is shown in Figure 20-1. The resistor ladder is segmented to provide two ranges of CVREF values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/VSS or an external voltage reference.

#### 20.1 Configuring the Comparator Voltage Reference

-----

The voltage reference module is controlled through the CVRCON register (Register 20-1). The comparator voltage reference provides two ranges of output voltage, each with 16 distinct levels. The range to be

used is selected by the CVRR bit (CVRCON<5>). The primary difference between the ranges is the size of the steps selected by the CVREF Selection bits (CVR<3:0>), with one range offering finer resolution. The equations used to calculate the output of the comparator voltage reference are as follows:

<u>If CVRR = 1:</u> CVREF = ((CVR<3:0>)/24) x CVRSRC <u>If CVRR = 0:</u> CVREF = (CVRSRC x 1/4) + (((CVR<3:0>)/32) x CVRSRC)

The comparator reference supply voltage can come from either VDD and VSS, or the external VREF+ and VREF- that are multiplexed with RA2 and RA3. The voltage source is selected by the CVRSS bit (CVRCON<4>).

The settling time of the comparator voltage reference must be considered when changing the CVREF output (see Table 24-3 in **Section 24.0 "Electrical Characteristics"**).

#### **REGISTER 20-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER**

| R/W-0       | R/W-0                | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------------|----------------------|-------|-------|-------|-------|-------|-------|--|

| CVREN       | CVROE <sup>(1)</sup> | CVRR  | CVRSS | CVR3  | CVR2  | CVR1  | CVR0  |  |

| bit 7 bit 0 |                      |       |       |       |       |       |       |  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 7   | CVREN: Comparator Voltage Reference Enable bit                                                                                                                                                                                     |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = CVREF circuit powered on                                                                                                                                                                                                       |

|         | 0 = CVREF circuit powered down                                                                                                                                                                                                     |

| bit 6   | CVROE: Comparator VREF Output Enable bit <sup>(1)</sup>                                                                                                                                                                            |

|         | <ul> <li>1 = CVREF voltage level is also output on the RA2/AN2/VREF-/CVREF pin</li> <li>0 = CVREF voltage is disconnected from the RA2/AN2/VREF-/CVREF pin</li> </ul>                                                              |

| bit 5   | CVRR: Comparator VREF Range Selection bit                                                                                                                                                                                          |

|         | <ul> <li>1 = 0 to 0.667 CVRsRc, with CVRsRc/24 step size (low range)</li> <li>0 = 0.25 CVRsRc to 0.75 CVRsRc, with CVRsRc/32 step size (high range)</li> </ul>                                                                     |

| bit 4   | CVRSS: Comparator VREF Source Selection bit                                                                                                                                                                                        |

|         | <ul> <li>1 = Comparator reference source, CVRSRC = (VREF+) - (VREF-)</li> <li>0 = Comparator reference source, CVRSRC = VDD - VSS</li> </ul>                                                                                       |

| bit 3-0 | <b>CVR&lt;3:0&gt;:</b> Comparator VREF Value Selection bits $(0 \le (CVR<3:0>) \le 15)$<br><u>When CVRR = 1:</u><br>CVREF = ((CVR<3:0>)/24) • (CVRSRC)<br><u>When CVRR = 0:</u><br>CVREF = (CVRSRC/4) + ((CVR<3:0>)/32) • (CVRSRC) |

|         |                                                                                                                                                                                                                                    |

Note 1: CVROE overrides the TRISA<2> bit setting.

#### FIGURE 20-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

## 20.2 Voltage Reference Accuracy/Error

The full range of voltage reference cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 20-1) keep CVREF from approaching the reference source rails. The voltage reference is derived from the reference source; therefore, the CVREF output changes with fluctuations in that source. The tested absolute accuracy of the voltage reference can be found in **Section 24.0 "Electrical Characteristics"**.

## 20.3 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the CVRCON register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

## 20.4 Effects of a Reset

A device Reset disables the voltage reference by clearing bit, CVREN (CVRCON<7>). This Reset also disconnects the reference from the RA2 pin by clearing bit, CVROE (CVRCON<6>) and selects the high-voltage range by clearing bit, CVRR (CVRCON<5>). The CVR value select bits are also cleared.

## 20.5 Connection Considerations

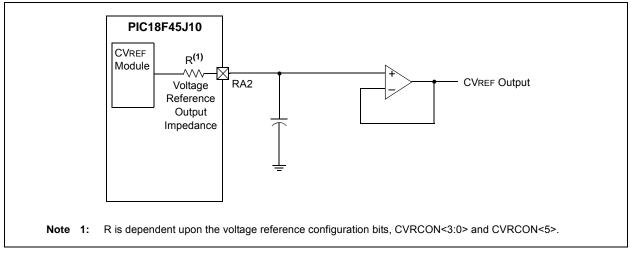

The voltage reference module operates independently of the comparator module. The output of the reference generator may be connected to the RA2 pin if the CVROE bit is set. Enabling the voltage reference output onto RA2 when it is configured as a digital input will increase current consumption. Connecting RA2 as a digital output with CVRSS enabled will also increase current consumption.

The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited current drive capability, a buffer must be used on the voltage reference output for external connections to VREF. Figure 20-2 shows an example buffering technique.

#### FIGURE 20-2: COMPARATOR VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

#### TABLE 20-1: REGISTERS ASSOCIATED WITH COMPARATOR VOLTAGE REFERENCE

| Name   | Bit 7 | Bit 6 | Bit 5  | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|-------|-------|--------|-------|--------|--------|--------|--------|----------------------------|

| CVRCON | CVREN | CVROE | CVRR   | CVRSS | CVR3   | CVR2   | CVR1   | CVR0   | 49                         |

| CMCON  | C2OUT | C10UT | C2INV  | C1INV | CIS    | CM2    | CM1    | CM0    | 49                         |

| TRISA  | _     | _     | TRISA5 | _     | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 50                         |

Legend: Shaded cells are not used with the comparator voltage reference.

#### TABLE 22-2: PIC18FXXXX INSTRUCTION SET

| Mnemonic, |                                 | Description                              | 0          | 16-  | Bit Instr | uction W | ord  | Status          | Neter      |

|-----------|---------------------------------|------------------------------------------|------------|------|-----------|----------|------|-----------------|------------|

| Opera     | nds                             | Description                              | Cycles     | MSb  |           |          | LSb  | Affected        | Notes      |

| BYTE-ORIE | ENTED C                         | OPERATIONS                               |            |      |           |          |      |                 |            |

| ADDWF     | f, d, a                         | Add WREG and f                           | 1          | 0010 | 01da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2       |

| ADDWFC    | f, d, a                         | Add WREG and Carry bit to f              | 1          | 0010 | 00da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2       |

| ANDWF     | f, d, a                         | AND WREG with f                          | 1          | 0001 | 01da      | ffff     | ffff | Z, N            | 1,2        |

| CLRF      | f, a                            | Clear f                                  | 1          | 0110 | 101a      | ffff     | ffff | Z               | 2          |

| COMF      | f, d, a                         | Complement f                             | 1          | 0001 | 11da      | ffff     | ffff | Z, N            | 1, 2       |

| CPFSEQ    | f, a                            | Compare f with WREG, Skip =              | 1 (2 or 3) | 0110 | 001a      | ffff     | ffff | None            | 4          |

| CPFSGT    | f, a                            | Compare f with WREG, Skip >              | 1 (2 or 3) | 0110 | 010a      | ffff     | ffff | None            | 4          |

| CPFSLT    | f, a                            | Compare f with WREG, Skip <              | 1 (2 or 3) | 0110 | 000a      | ffff     | ffff | None            | 1, 2       |

| DECF      | f, d, a                         | Decrement f                              | 1          | 0000 | 01da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| DECFSZ    | f, d, a                         | Decrement f, Skip if 0                   | 1 (2 or 3) | 0010 | 11da      | ffff     | ffff | None            | 1, 2, 3, 4 |

| DCFSNZ    | f, d, a                         | Decrement f, Skip if Not 0               | 1 (2 or 3) | 0100 | 11da      | ffff     | ffff | None            | 1, 2       |

| INCF      | f, d, a                         | Increment f                              | 1          | 0010 | 10da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| INCFSZ    | f, d, a                         | Increment f, Skip if 0                   | 1 (2 or 3) | 0011 | 11da      | ffff     | ffff | None            | 4          |

| INFSNZ    | f, d, a                         | Increment f, Skip if Not 0               | 1 (2 or 3) | 0100 | 10da      | ffff     | ffff | None            | 1, 2       |

| IORWF     | f, d, a                         | Inclusive OR WREG with f                 | 1          | 0001 | 00da      | ffff     | ffff | Z, N            | 1, 2       |

| MOVF      | f, d, a                         | Move f                                   | 1          | 0101 | 00da      | ffff     | ffff | Z, N            | 1          |

| MOVFF     | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st Word | 2          | 1100 | ffff      | ffff     | ffff | None            |            |

|           |                                 | f <sub>d</sub> (destination) 2nd Word    |            | 1111 | ffff      | ffff     | ffff |                 |            |

| MOVWF     | f, a                            | Move WREG to f                           | 1          | 0110 | 111a      | ffff     | ffff | None            |            |

| MULWF     | f, a                            | Multiply WREG with f                     | 1          | 0000 | 001a      | ffff     | ffff | None            | 1, 2       |

| NEGF      | f, a                            | Negate f                                 | 1          | 0110 | 110a      | ffff     | ffff | C, DC, Z, OV, N |            |

| RLCF      | f, d, a                         | Rotate Left f through Carry              | 1          | 0011 | 01da      | ffff     | ffff | C, Z, N         | 1, 2       |

| RLNCF     | f, d, a                         | Rotate Left f (No Carry)                 | 1          | 0100 | 01da      | ffff     | ffff | Z, N            |            |

| RRCF      | f, d, a                         | Rotate Right f through Carry             | 1          | 0011 | 00da      | ffff     | ffff | C, Z, N         |            |

| RRNCF     | f, d, a                         | Rotate Right f (No Carry)                | 1          | 0100 | 00da      | ffff     | ffff | Z, N            |            |

| SETF      | f, a                            | Set f                                    | 1          | 0110 | 100a      | ffff     | ffff | None            | 1, 2       |

| SUBFWB    | f, d, a                         | Subtract f from WREG with<br>Borrow      | 1          | 0101 | 01da      | ffff     | ffff | C, DC, Z, OV, N |            |

| SUBWF     | f, d, a                         | Subtract WREG from f                     | 1          | 0101 | 11da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2       |

| SUBWFB    | f, d, a                         | Subtract WREG from f with                | 1          | 0101 | 10da      | ffff     | ffff | C, DC, Z, OV, N |            |

|           |                                 | Borrow                                   |            |      |           |          |      |                 |            |

| SWAPF     | f, d, a                         | Swap Nibbles in f                        | 1          | 0011 | 10da      | ffff     | ffff | None            | 4          |

| TSTFSZ    | f, a                            | Test f, Skip if 0                        | 1 (2 or 3) | 0110 | 011a      | ffff     | ffff | None            | 1, 2       |

| XORWF     | f, d, a                         | Exclusive OR WREG with f                 | 1          | 0001 | 10da      | ffff     |      | Z, N            |            |

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

3: If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

| Increment f, Skip if 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| INCFSZ f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| $\begin{array}{l} 0 \leq f \leq 255 \\ d \in [0,1] \\ a \in [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 0011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11da f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | fff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Description: The contents of register 'f' are incremented. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is placed back in register 'f' (default). If the result is '0', the next instruction, which is already fetched, is discarded and a NOP is executed instead, making it a two-cycle instruction. If 'a' is '0', the Access Bank is selected If 'a' is '1', the BSR is used to select th GPR bank (default). If 'a' is '0' and the extended instruction set is enabled, this instruction operate in Indexed Literal Offset Addressing mode whenever f ≤ 95 (5Fh). See Section 22.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |