Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuns                     |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 21                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                |                                                                             |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                 |

| Data Converters            | A/D 10x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f25j10t-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 28/40/44-Pin High-Performance, RISC Microcontrollers

#### **Special Microcontroller Features:**

- Operating Voltage Range: 2.0V to 3.6V

- 5.5V Tolerant Input (digital pins only)

- · On-Chip 2.5V Regulator

- 4x Phase Lock Loop (PLL) available for Crystal and Internal Oscillators

- Self-Programmable under Software Control

- Low-Power, High-Speed CMOS Flash Technology

- C Compiler Optimized Architecture:

- Optional extended instruction set designed to optimize re-entrant code

- · Priority Levels for Interrupts

- 8 x 8 Single-Cycle Hardware Multiplier

- Extended Watchdog Timer (WDT):

- Programmable period from 4 ms to 131s

- Single-Supply In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via Two Pins

- In-Circuit Debug (ICD) with Three Breakpoints via Two Pins

- · Power-Managed modes with Clock Switching:

- Run: CPU on, peripherals on

- Idle: CPU off, peripherals on

- Sleep: CPU off, peripherals off

#### **Flexible Oscillator Structure:**

- Two Crystal modes, up to 40 MHz

- Two External Clock modes, up to 40 MHz

- Internal 31 kHz Oscillator

- Secondary Oscillator using Timer1 @ 32 kHz

- Two-Speed Oscillator Start-up

- Fail-Safe Clock Monitor:

- Allows for safe shutdown if peripheral clock stops

#### **Peripheral Highlights:**

- High-Current Sink/Source 25 mA/25 mA (PORTB and PORTC)

- · Three Programmable External Interrupts

- · Four Input Change Interrupts

- · One Capture/Compare/PWM (CCP) module

- One Enhanced Capture/Compare/PWM (ECCP) module:

- One, two or four PWM outputs

- Selectable polarity

- Programmable dead time

- Auto-shutdown and auto-restart

- Two Master Synchronous Serial Port (MSSP) modules supporting 3-Wire SPI (all 4 modes) and I<sup>2</sup>C<sup>™</sup> Master and Slave modes

- One Enhanced Addressable USART module:

- Supports RS-485, RS-232 and LIN/J2602

- Auto-wake-up on Start bit

- Auto-Baud Detect (ABD)

- 10-Bit, up to 13-Channel Analog-to-Digital Converter module (A/D):

- Auto-acquisition capability

- Conversion available during Sleep

- Self-calibration feature

- · Dual Analog Comparators with Input Multiplexing

| Program Memory |                  | ram Memory                    |                                |     |                    |                       | MSSP |     |                             | F     | ors       |                    |

|----------------|------------------|-------------------------------|--------------------------------|-----|--------------------|-----------------------|------|-----|-----------------------------|-------|-----------|--------------------|

| Device         | Flash<br>(bytes) | # Single-Word<br>Instructions | SRAM Data<br>Memory<br>(bytes) | I/O | 10-Bit<br>A/D (ch) | CCP/<br>ECCP<br>(PWM) |      | SPI | Master<br>I <sup>2</sup> C™ | EUSAR | Comparato | Timers<br>8/16-Bit |

| PIC18F24J10    | 16K              | 8192                          | 1024                           | 21  | 10                 | 2/0                   | 1    | Y   | Y                           | 1     | 2         | 1/2                |

| PIC18F25J10    | 32K              | 16384                         | 1024                           | 21  | 10                 | 2/0                   | 1    | Y   | Y                           | 1     | 2         | 1/2                |

| PIC18F44J10    | 16K              | 8192                          | 1024                           | 32  | 13                 | 1/1                   | 2    | Y   | Y                           | 1     | 2         | 1/2                |

| PIC18F45J10    | 32K              | 16384                         | 1024                           | 32  | 13                 | 1/1                   | 2    | Y   | Y                           | 1     | 2         | 1/2                |

| Pin Name                | Pi      | n Numb     | er      | Pin    | Buffer | Description                                                                               |

|-------------------------|---------|------------|---------|--------|--------|-------------------------------------------------------------------------------------------|

| Fininame                | PDIP    | QFN        | TQFP    | Туре   | Туре   | Description                                                                               |

|                         |         |            |         |        |        | PORTE is a bidirectional I/O port.                                                        |

| RE0/RD/AN5              | 8       | 25         | 25      |        |        |                                                                                           |

| RE0                     |         |            |         | I/O    | ST     | Digital I/O.                                                                              |

| RD                      |         |            |         | I      | TTL    | Read control for Parallel Slave Port (see also $\overline{WR}$ and $\overline{CS}$ pins). |

| AN5                     |         |            |         | Ι      | Analog | Analog input 5.                                                                           |

| RE1/WR/AN6              | 9       | 26         | 26      |        | 0      |                                                                                           |

| RE1                     | Ū       |            |         | I/O    | ST     | Digital I/O.                                                                              |

| WR                      |         |            |         | Ι      | TTL    | Write control for Parallel Slave Port                                                     |

| 410                     |         |            |         |        | A      | (see CS and RD pins).                                                                     |

| AN6                     |         |            |         | I      | Analog | Analog input 6.                                                                           |

| RE2/CS/AN7<br>RE2       | 10      | 27         | 27      | I/O    | ST     | Digital I/O                                                                               |

| CS                      |         |            |         | 1/0    | TTL    | Digital I/O.<br>Chip Select control for Parallel Slave Port                               |

|                         |         |            |         | •      |        | (see related $\overline{RD}$ and $\overline{WR}$ pins).                                   |

| AN7                     |         |            |         | -      | Analog | Analog input 7.                                                                           |

| Vss                     | 12, 31  |            | 6, 29   | Р      | —      | Ground reference for logic and I/O pins.                                                  |

|                         |         | 31         |         |        |        |                                                                                           |

| Vdd                     | 11, 32  |            | 7, 28   | Р      | —      | Positive supply for logic and I/O pins.                                                   |

| N/                      |         | 28, 29     |         |        |        |                                                                                           |

| VDDCORE/VCAP<br>VDDCORE | 6       | 23         | 23      | Р      |        | Positive supply for logic and I/O pins.                                                   |

| VCAP                    |         |            |         | P      | _      | Ground reference for logic and I/O pins.                                                  |

| NC                      |         | 13         | 12, 13, |        |        | No connect.                                                                               |

| -                       |         |            | 33, 34  |        |        |                                                                                           |

| Legend: TTL = TTL co    | mpatibl | e input    |         |        | C      | MOS = CMOS compatible input or output                                                     |

| ST = Schmit             |         | er input v | with CM | OS lev |        | = Input                                                                                   |

| O = Output              | t       |            |         |        | P      | = Power                                                                                   |

Note 1: Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

#### 6.1.3 PROGRAM COUNTER

The Program Counter (PC) specifies the address of the instruction to fetch for execution. The PC is 21 bits wide and is contained in three separate 8-bit registers. The low byte, known as the PCL register, is both readable and writable. The high byte, or PCH register, contains the PC<15:8> bits; it is not directly readable or writable. Updates to the PCH register are performed through the PCLATH register. The upper byte is called PCU. This register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCH register. Updates to the PCU register are performed through the PCLATH register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCU register are performed through the PCLATU register.

The contents of PCLATH and PCLATU are transferred to the program counter by any operation that writes PCL. Similarly, the upper two bytes of the program counter are transferred to PCLATH and PCLATU by an operation that reads PCL. This is useful for computed offsets to the PC (see **Section 6.1.6.1 "Computed GOTO"**).

The PC addresses bytes in the program memory. To prevent the PC from becoming misaligned with word instructions, the Least Significant bit of PCL is fixed to a value of '0'. The PC increments by 2 to address sequential instructions in the program memory.

The CALL, RCALL, GOTO and program branch instructions write to the program counter directly. For these instructions, the contents of PCLATH and PCLATU are not transferred to the program counter.

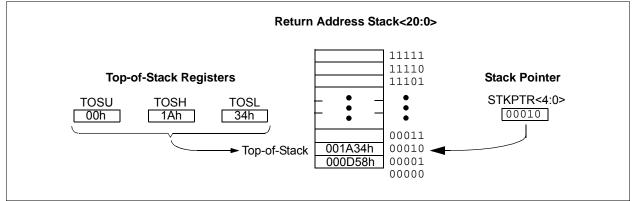

#### 6.1.4 RETURN ADDRESS STACK

The return address stack allows any combination of up to 31 program calls and interrupts to occur. The PC is pushed onto the stack when a CALL or RCALL instruction is executed or an interrupt is Acknowledged. The PC value is pulled off the stack on a RETURN, RETLW or RETFIE instruction. PCLATU and PCLATH are not affected by any of the RETURN or CALL instructions.

The stack operates as a 31-word by 21-bit RAM and a 5-bit Stack Pointer, STKPTR. The stack space is not part of either program or data space. The Stack Pointer is readable and writable and the address on the top of the stack is readable and writable through the top-of-stack Special Function Registers. Data can also be pushed to, or popped from the stack, using these registers.

A CALL type instruction causes a push onto the stack; the Stack Pointer is first incremented and the location pointed to by the Stack Pointer is written with the contents of the PC (already pointing to the instruction following the CALL). A RETURN type instruction causes a pop from the stack; the contents of the location pointed to by the STKPTR are transferred to the PC and then the Stack Pointer is decremented.

The Stack Pointer is initialized to '00000' after all Resets. There is no RAM associated with the location corresponding to a Stack Pointer value of '00000'; this is only a Reset value. Status bits indicate if the stack is full or has overflowed or has underflowed.

#### 6.1.4.1 Top-of-Stack Access

Only the top of the return address stack (TOS) is readable and writable. A set of three registers, TOSU:TOSH:TOSL, hold the contents of the stack location pointed to by the STKPTR register (Figure 6-3). This allows users to implement a software stack if necessary. After a CALL, RCALL or interrupt, the software can read the pushed value by reading the TOSU:TOSH:TOSL registers. These values can be placed on a user-defined software stack. At return time, the software can return these values to TOSU:TOSH:TOSL and do a return.

The user must disable the global interrupt enable bits while accessing the stack to prevent inadvertent stack corruption.

#### FIGURE 6-3: RETURN ADDRESS STACK AND ASSOCIATED REGISTERS

#### 6.3.5 STATUS REGISTER

The STATUS register, shown in Register 6-2, contains the arithmetic status of the ALU. As with any other SFR, it can be the operand for any instruction.

If the STATUS register is the destination for an instruction that affects the Z, DC, C, OV or N bits, the results of the instruction are not written; instead, the STATUS register is updated according to the instruction performed. Therefore, the result of an instruction with the STATUS register as its destination may be different than intended. As an example, CLRF STATUS will set the Z bit and leave the remaining Status bits unchanged ('000u u1uu'). It is recommended that only BCF, BSF, SWAPF, MOVFF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C, DC, OV or N bits in the STATUS register.

For other instructions that do not affect Status bits, see the instruction set summaries in Table 22-2 and Table 22-3.

Note: The C and DC bits operate as the borrow and digit borrow bits, respectively, in subtraction.

#### REGISTER 6-2: STATUS REGISTER

| U-0       | U-0                          | U-0                                        | R/W-x           | R/W-x             | R/W-x           | R/W-x              | R/W-x            |

|-----------|------------------------------|--------------------------------------------|-----------------|-------------------|-----------------|--------------------|------------------|

| _         | _                            | —                                          | Ν               | OV                | Z               | DC <sup>(1)</sup>  | C <sup>(2)</sup> |

| bit 7     |                              |                                            |                 |                   |                 |                    | bit (            |

| Legend:   |                              |                                            |                 |                   |                 |                    |                  |

| R = Read  |                              | W = Writable b                             | oit             | U = Unimplen      | nented bit, rea | ad as '0'          |                  |

| -n = Valu | e at POR                     | '1' = Bit is set                           |                 | '0' = Bit is cle  |                 | x = Bit is unkr    | nown             |

| bit 7-5   | Unimpleme                    | nted: Read as '0                           | 3               |                   |                 |                    |                  |

| bit 4     | N: Negative                  | bit                                        |                 |                   |                 |                    |                  |

|           | This bit is us<br>(ALU MSB = | sed for signed ari<br>= 1).                | thmetic (2's co | omplement). It i  | ndicates whe    | ther the result wa | as negative      |

|           | 1 = Result w<br>0 = Result w | vas negative<br>vas positive               |                 |                   |                 |                    |                  |

| bit 3     | OV: Overflor                 | w bit                                      |                 |                   |                 |                    |                  |

|           | which cause                  | sed for signed ari<br>es the sign bit (bit | 7) to change    | state.            |                 |                    | bit magnitude    |

|           |                              | v occurred for sig<br>flow occurred        | ned arithmeti   | c (in this arithm | etic operation  | )                  |                  |

| bit 2     | Z: Zero bit                  |                                            |                 |                   |                 |                    |                  |

|           |                              | ult of an arithmeti<br>ult of an arithmeti |                 |                   | 0               |                    |                  |

| bit 1     | •                            | arry/Borrow bit <sup>(1)</sup>             |                 |                   |                 |                    |                  |

|           |                              | ADDLW, SUBLW ar<br>out from the 4th l      |                 |                   | urrod           |                    |                  |

|           |                              | -out from the 4th                          |                 |                   | uneu            |                    |                  |

| bit 0     | C: Carry/Bo                  |                                            |                 |                   |                 |                    |                  |

|           |                              | ADDLW, SUBLW ar                            | nd SUBWF inst   | ructions:         |                 |                    |                  |

|           |                              | out from the Mos                           |                 |                   |                 |                    |                  |

|           | 0 = No carry                 | -out from the Mo                           | st Significant  | bit of the result | occurred        |                    |                  |

| Note 1:   |                              | polarity is reverse<br>ate (RRF, RLF) ins  |                 |                   |                 |                    |                  |

| 2:        | For borrow, the              | polarity is reverse<br>tate (RRF, RLF) in  | d. A subtracti  | on is executed l  | by adding the   | 2's complement     | of the second    |

| Pin                     | Function | TRIS<br>Setting | I/O | I/O<br>Type | Description                                                                                                       |

|-------------------------|----------|-----------------|-----|-------------|-------------------------------------------------------------------------------------------------------------------|

| RA0/AN0                 | RA0      | 0               | 0   | DIG         | LATA<0> data output; not affected by analog input.                                                                |

|                         |          | 1               | I   | TTL         | PORTA<0> data input; disabled when analog input enabled.                                                          |

|                         | AN0      | 1               | Ι   | ANA         | A/D Input Channel 0 and Comparator C1- input. Default input configuration on POR; does not affect digital output. |

| RA1/AN1                 | RA1      | 0               | 0   | DIG         | LATA<1> data output; not affected by analog input.                                                                |

|                         |          | 1               | Ι   | TTL         | PORTA<1> data input; disabled when analog input enabled.                                                          |

|                         | AN1      | 1               | I   | ANA         | A/D Input Channel 1 and Comparator C2- input. Default input configuration on POR; does not affect digital output. |

| RA2/AN2/<br>Vref-/CVref | RA2      | 0               | 0   | DIG         | LATA<2> data output; not affected by analog input. Disabled when CVREF output enabled.                            |

|                         |          | 1               | Ι   | TTL         | PORTA<2> data input. Disabled when analog functions enabled; disabled when CVREF output enabled.                  |

|                         | AN2      | 1               | Ι   | ANA         | A/D Input Channel 2 and Comparator C2+ input. Default input configuration on POR; not affected by analog output.  |

|                         | VREF-    | 1               | Ι   | ANA         | A/D and comparator voltage reference low input.                                                                   |

|                         | CVREF    | x               | 0   | ANA         | Comparator voltage reference output. Enabling this feature disables digital I/O.                                  |

| RA3/AN3/VREF+           | RA3      | 0               | 0   | DIG         | LATA<3> data output; not affected by analog input.                                                                |

|                         |          | 1               | Ι   | TTL         | PORTA<3> data input; disabled when analog input enabled.                                                          |

|                         | AN3      | 1               | Ι   | ANA         | A/D Input Channel 3 and Comparator C1+ input. Default input configuration on POR.                                 |

|                         | VREF+    | 1               | Ι   | ANA         | A/D and comparator voltage reference high input.                                                                  |

| RA5/AN4/SS1/            | RA5      | 0               | 0   | DIG         | LATA<5> data output; not affected by analog input.                                                                |

| C2OUT                   |          | 1               | Ι   | TTL         | PORTA<5> data input; disabled when analog input enabled.                                                          |

|                         | AN4      | 1               | Ι   | ANA         | A/D Input Channel 4. Default configuration on POR.                                                                |

|                         | SS1      | 1               | Ι   | TTL         | Slave select input for MSSP1 (MSSP1 module).                                                                      |

|                         | C2OUT    | 0               | 0   | DIG         | Comparator 2 output; takes priority over port data.                                                               |

| OSC2/CLKO               | OSC2     | x               | 0   | ANA         | Main oscillator feedback output connection (HS mode).                                                             |

|                         | CLKO     | x               | 0   | DIG         | System cycle clock output (Fosc/4) in RC and EC Oscillator modes.                                                 |

| OSC1/CLKI               | OSC1     | x               | Ι   | ANA         | Main oscillator input connection.                                                                                 |

|                         | CLKI     | x               | Ι   | ANA         | Main clock input connection.                                                                                      |

#### TABLE 10-3: PORTA I/O SUMMARY

Legend: DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output; x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

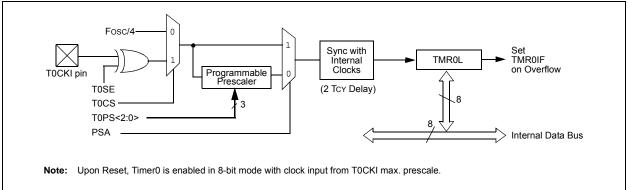

#### 11.1 Timer0 Operation

Timer0 can operate as either a timer or a counter; the mode is selected with the TOCS bit (TOCON<5>). In Timer mode (TOCS = 0), the module increments on every clock by default unless a different prescaler value is selected (see **Section 11.3 "Prescaler"**). If the TMR0 register is written to, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

The Counter mode is selected by setting the T0CS bit (= 1). In this mode, Timer0 increments either on every rising or falling edge of pin RB5/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit, T0SE (T0CON<4>); clearing this bit selects the rising edge. Restrictions on the external clock input are discussed below.

An external clock source can be used to drive Timer0; however, it must meet certain requirements to ensure that the external clock can be synchronized with the internal phase clock (Tosc). There is a delay between synchronization and the onset of incrementing the timer/counter.

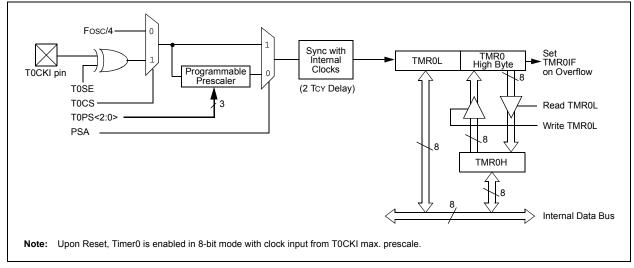

#### 11.2 Timer0 Reads and Writes in 16-Bit Mode

TMR0H is not the actual high byte of Timer0 in 16-bit mode. It is actually a buffered version of the real high byte of Timer0 which is not directly readable nor writable (refer to Figure 11-2). TMR0H is updated with the contents of the high byte of Timer0 during a read of TMR0L. This provides the ability to read all 16 bits of Timer0 without having to verify that the read of the high and low byte were valid, due to a rollover between successive reads of the high and low byte.

Similarly, a write to the high byte of Timer0 must also take place through the TMR0H Buffer register. The high byte is updated with the contents of TMR0H when a write occurs to TMR0L. This allows all 16 bits of Timer0 to be updated at once.

#### FIGURE 11-1: TIMER0 BLOCK DIAGRAM (8-BIT MODE)

#### FIGURE 11-2: TIMER0 BLOCK DIAGRAM (16-BIT MODE)

#### 16.4.3.2 Address Masking

Masking an address bit causes that bit to become a "don't care". When one address bit is masked, two addresses will be Acknowledged and cause an interrupt. It is possible to mask more than one address bit at a time, which makes it possible to Acknowledge up to 31 addresses in 7-Bit Addressing mode and up to 63 addresses in 10-Bit Addressing mode (see Example 16-2).

The I<sup>2</sup>C Slave behaves the same way, whether address masking is used or not. However, when address masking is used, the I<sup>2</sup>C slave can Acknowledge multiple addresses and cause interrupts. When this occurs, it is necessary to determine which address caused the interrupt by checking SSPxBUF.

In 7-Bit Addressing mode, Address Mask bits, ADMSK<5:1> (SSPxCON2<5:1>), mask the corresponding address bits in the SSPxADD register. For any ADMSK bits that are set (ADMSK<n> = 1), the corresponding address bit is ignored (SSPxADD<n> = x). For the module to issue an address Acknowledge, it is sufficient to match only on addresses that do not have an active address mask.

In 10-Bit Addressing mode, ADMSK<5:2> bits mask the corresponding address bits in the SSPxADD register. In addition, ADMSK1 simultaneously masks the two LSbs of the address (SSPxADD<1:0>). For any ADMSK bits that are active (ADMSK<n> = 1), the corresponding address bit is ignored (SSPxADD<n> = x). Also note that although in 10-Bit Addressing mode, the upper address bits reuse part of the SSPxADD register bits, the address mask bits do not interact with those bits. They only affect the lower address bits.

**Note 1:** ADMSK1 masks the two Least Significant bits of the address.

The two Most Significant bits of the address are not affected by address masking.

#### EXAMPLE 16-2: ADDRESS MASKING EXAMPLES

#### 7-Bit Addressing:

SSPxADD<7:1>= A0h (1010000) (SSPxADD<0> is assumed to be '0')

ADMSK<5:1> = 00111

Addresses Acknowledged: A0h, A2h, A4h, A6h, A8h, AAh, ACh, AEh

#### 10-Bit Addressing:

SSPxADD<7:0>= A0h (10100000) (the two MSbs of the address are ignored in this example, since they are not affected by masking)

ADMSK<5:1> = 00111

Addresses Acknowledged: A0h, A1h, A2h, A3h, A4h, A5h, A6h, A7h, A8h, A9h, AAh, ABh, ACh, ADh, AEh, AFh

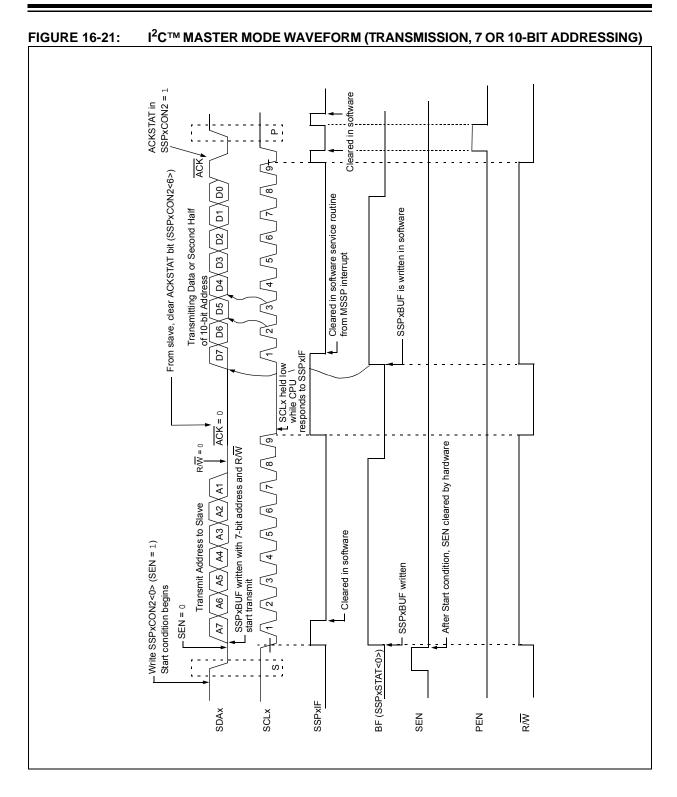

#### 16.4.6.1 I<sup>2</sup>C Master Mode Operation

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDAx, while SCLx outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the  $R/\overline{W}$  bit. In this case, the  $R/\overline{W}$  bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDAx, while SCLx outputs the serial clock. Serial data is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

The Baud Rate Generator used for the SPI mode operation is used to set the SCLx clock frequency for either 100 kHz, 400 kHz or 1 MHz I<sup>2</sup>C operation. See **Section 16.4.7 "Baud Rate"** for more detail.

A typical transmit sequence would go as follows:

- 1. The user generates a Start condition by setting the Start Enable bit, SEN (SSPxCON2<0>).

- SSPxIF is set. The MSSP module will wait the required start time before any other operation takes place.

- 3. The user loads the SSPxBUF with the slave address to transmit.

- 4. Address is shifted out the SDAx pin until all 8 bits are transmitted.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPxCON2 register (SSPxCON2<6>).

- 6. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 7. The user loads the SSPxBUF with eight bits of data.

- 8. Data is shifted out the SDAx pin until all 8 bits are transmitted.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPxCON2 register (SSPxCON2<6>).

- 10. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 11. The user generates a Stop condition by setting the Stop Enable bit, PEN (SSPxCON2<2>).

- 12. Interrupt is generated once the Stop condition is complete.

#### 18.2 Selecting and Configuring Automatic Acquisition Time

The ADCON2 register allows the user to select an acquisition time that occurs each time the GO/DONE bit is set.

When the GO/DONE bit is set, sampling is stopped and a conversion begins. The user is responsible for ensuring the required acquisition time has passed between selecting the desired input channel and setting the GO/DONE bit. This occurs when the ACQT<2:0> bits (ADCON2<5:3>) remain in their Reset state ('000') and is compatible with devices that do not offer programmable acquisition times.

If desired, the ACQT bits can be set to select a programmable acquisition time for the A/D module. When the GO/DONE bit is set, the A/D module continues to sample the input for the selected acquisition time, then automatically begins a conversion. Since the acquisition time is programmed, there may be no need to wait for an acquisition time between selecting a channel and setting the GO/DONE bit.

In either case, when the conversion is completed, the GO/DONE bit is cleared, the ADIF flag is set and the A/D begins sampling the currently selected channel again. If an acquisition time is programmed, there is nothing to indicate if the acquisition time has ended or if the conversion has begun.

#### 18.3 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 11 TAD per 10-bit conversion. The source of the A/D conversion clock is software selectable.

There are seven possible options for TAD:

- 2 Tosc

- 4 Tosc

- 8 Tosc

- 16 Tosc

- 32 Tosc

- 64 Tosc

- Internal RC Oscillator

For correct A/D conversions, the A/D conversion clock (TAD) must be as short as possible but greater than the minimum TAD (see parameter 130 in Table 24-25 for more information).

Table 18-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

#### TABLE 18-1: TAD vs. DEVICE OPERATING FREQUENCIES

| AD Clock S        | Maximum   |                         |

|-------------------|-----------|-------------------------|

| Operation         | ADCS<2:0> | Device<br>Frequency     |

| 2 Tosc            | 000       | 2.86 MHz                |

| 4 Tosc            | 100       | 5.71 MHz                |

| 8 Tosc            | 001       | 11.43 MHz               |

| 16 Tosc           | 101       | 22.86 MHz               |

| 32 Tosc           | 010       | 40.0 MHz                |

| 64 Tosc           | 110       | 40.0 MHz                |

| RC <sup>(2)</sup> | x11       | 1.00 MHz <sup>(1)</sup> |

Note 1: The RC source has a typical TAD time of  $4 \ \mu s$ .

2: For device frequencies above 1 MHz, the device must be in Sleep mode for the entire conversion or the A/D accuracy may be out of specification.

#### 18.4 Configuring Analog Port Pins

The ADCON1, TRISA, TRISF and TRISH registers control the operation of the A/D port pins. The port pins needed as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS<3:0> bits and the TRIS bits.

- Note 1: When reading the PORT register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as digital inputs will convert an analog input. Analog levels on a digitally configured input will be accurately converted.

- 2: Analog levels on any pin defined as a digital input may cause the digital input buffer to consume current out of the device's specification limits.

NOTES:

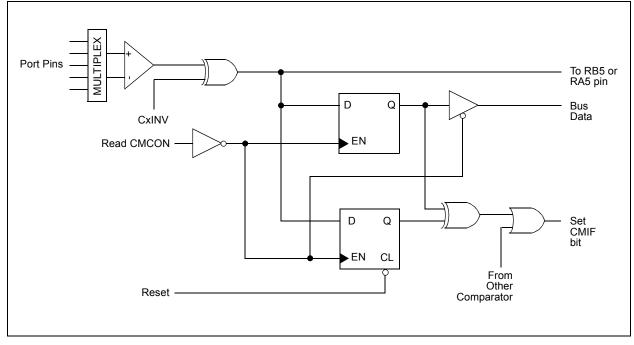

#### FIGURE 19-3: COMPARATOR OUTPUT BLOCK DIAGRAM

#### 19.6 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that occurred. The CMIF bit (PIR2<6>) is the Comparator Interrupt Flag. The CMIF bit must be reset by clearing it. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

Both the CMIE bit (PIE2<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit (INTCON<7>) must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit, CMIF. Reading CMCON will end the mismatch condition and allow flag bit, CMIF, to be cleared.

#### 19.7 Comparator Operation During Sleep

When a comparator is active and the device is placed in Sleep mode, the comparator remains active and the interrupt is functional, if enabled. This interrupt will wake-up the device from Sleep mode, when enabled. Each operational comparator will consume additional current, as shown in the comparator specifications. To minimize power consumption while in Sleep mode, turn off the comparators (CM<2:0> = 111) before entering Sleep. If the device wakes up from Sleep, the contents of the CMCON register are not affected.

#### 19.8 Effects of a Reset

A device Reset forces the CMCON register to its Reset state, causing the comparator modules to be turned off (CM<2:0> = 111). However, the input pins (RA0 through RA3) are configured as analog inputs by default on device Reset. The I/O configuration for these pins is determined by the setting of the PCFG<3:0> bits (ADCON1<3:0>). Therefore, device current is minimized when analog inputs are present at Reset time.

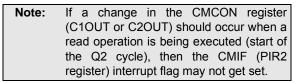

#### 21.5 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the microcontroller to continue operation in the event of an external oscillator failure by automatically switching the device clock to the internal oscillator block. The FSCM function is enabled by setting the FCMEN Configuration bit.

When FSCM is enabled, the INTRC oscillator runs at all times to monitor clocks to peripherals and provide a backup clock in the event of a clock failure. Clock monitoring (shown in Figure 21-4) is accomplished by creating a sample clock signal which is the INTRC output divided by 64. This allows ample time between FSCM sample clocks for a peripheral clock edge to occur. The peripheral device clock and the sample clock are presented as inputs to the Clock Monitor latch (CM). The CM is set on the falling edge of the device clock source but cleared on the rising edge of the sample clock.

Clock failure is tested for on the falling edge of the sample clock. If a sample clock falling edge occurs while CM is still set, a clock failure has been detected (Figure 21-5). This causes the following:

- the FSCM generates an oscillator fail interrupt by setting bit, OSCFIF (PIR2<7>);

- the device clock source is switched to the internal oscillator block (OSCCON is not updated to show the current clock source – this is the fail-safe condition); and

- the WDT is reset.

During switchover, the postscaler frequency from the internal oscillator block may not be sufficiently stable for timing sensitive applications. In these cases, it may be desirable to select another clock configuration and enter an alternate power-managed mode. This can be done to attempt a partial recovery or execute a controlled shutdown. See Section 4.1.4 "Multiple Sleep Commands" and Section 21.4.1 "Special Considerations for Using Two-Speed Start-up" for more details. To use a higher clock speed on wake-up, the INTOSC or postscaler clock sources can be selected to provide a higher clock speed by setting bits IRCF<2:0> immediately after Reset. For wake-ups from Sleep, the INTOSC or postscaler clock sources can be selected by setting IRCF<2:0> prior to entering Sleep mode.

The FSCM will detect failures of the primary or secondary clock sources only. If the internal oscillator block fails, no failure would be detected, nor would any action be possible.

#### 21.5.1 FSCM AND THE WATCHDOG TIMER

Both the FSCM and the WDT are clocked by the INTRC oscillator. Since the WDT operates with a separate divider and counter, disabling the WDT has no effect on the operation of the INTRC oscillator when the FSCM is enabled.

As already noted, the clock source is switched to the INTRC clock when a clock failure is detected; this may mean a substantial change in the speed of code execution. If the WDT is enabled with a small prescale value, a decrease in clock speed allows a WDT time-out to occur and a subsequent device Reset. For this reason, Fail-Safe Clock Monitor events also reset the WDT and postscaler, allowing it to start timing from when execution speed was changed and decreasing the likelihood of an erroneous time-out.

#### 21.5.2 EXITING FAIL-SAFE OPERATION

The fail-safe condition is terminated by either a device Reset or by entering a power-managed mode. On Reset, the controller starts the primary clock source specified in Configuration Register 2H (with the OST oscillator, start-up delays if running in HS mode). The INTRC oscillator provides the device clock until the primary clock source becomes ready (similar to a Two-Speed Start-up). The clock source is then switched to the primary clock (indicated by the OSTS bit in the OSCCON register becoming set). The Fail-Safe Clock Monitor then resumes monitoring the peripheral clock.

The primary clock source may never become ready during start-up. In this case, operation is clocked by the INTRC oscillator. The OSCCON register will remain in its Reset state until a power-managed mode is entered.

<sup>© 2009</sup> Microchip Technology Inc.

| CLRF                      | Clear f               |                                     |                                     | CLRV     | /DT                       | Clear Wat                                 | chdog Time       | er        |

|---------------------------|-----------------------|-------------------------------------|-------------------------------------|----------|---------------------------|-------------------------------------------|------------------|-----------|

| Syntax:                   | CLRF f{,a             | a}                                  |                                     | Syntax   | :                         | CLRWDT                                    |                  |           |

| Operands:                 | $0 \leq f \leq 255$   |                                     |                                     | Opera    | nds:                      | None                                      |                  |           |

|                           | $a \in [0,1]$         |                                     |                                     | Operat   | ion:                      | 000h $\rightarrow$ WE                     | DT,              |           |

| Operation:                | 000h $\rightarrow$ f, |                                     |                                     | ·        |                           |                                           | DT postscaler,   |           |

|                           | $1 \rightarrow Z$     |                                     |                                     |          |                           | $1 \rightarrow TO,$<br>$1 \rightarrow PD$ |                  |           |

| Status Affected:          | Z                     |                                     |                                     | <u> </u> |                           |                                           |                  |           |

| Encoding:                 | 0110                  | 101a ff                             | ff ffff                             |          | Affected:                 | TO, PD                                    |                  |           |

| Description:              | Clears the c          | contents of the                     | e specified                         | Encod    | ng:                       | 0000                                      | 0000 00          | 00 0100   |

|                           | register.             |                                     |                                     | Descri   | ption:                    |                                           | truction resets  |           |

|                           | ,                     |                                     | nk is selected.<br>ed to select the |          |                           | 0                                         | Timer. It also r |           |

|                           | GPR bank (            |                                     |                                     |          |                           | and PD, are                               |                  |           |

|                           |                       |                                     | ed instruction                      | Words    |                           | 1                                         |                  |           |

|                           |                       | ed, this instru<br>₋iteral Offset / | ction operates                      | Cycles   |                           | 1                                         |                  |           |

|                           |                       | ever f $\leq$ 95 (5                 | 0                                   | ,        | le Activity:              |                                           |                  |           |

|                           |                       | 2.3 "Byte-Or                        | ,                                   | QOY      | Q1                        | Q2                                        | Q3               | Q4        |

|                           |                       |                                     | is in Indexed                       |          | Decode                    | No                                        | Process          | No        |

|                           |                       | et Mode" for                        | details.                            |          | 200040                    | operation                                 | Data             | operation |

| Words:                    | 1                     |                                     |                                     |          |                           |                                           |                  |           |

| Cycles:                   | 1                     |                                     |                                     | Examp    | le:                       | CLRWDT                                    |                  |           |

| Q Cycle Activity:         |                       |                                     |                                     | В        | efore Instruc             | ction                                     |                  |           |

| Q1                        | Q2                    | Q3                                  | Q4                                  |          | WDT Co                    |                                           | ?                |           |

| Decode                    | Read                  | Process                             | Write                               | A        | fter Instructio<br>WDT Co |                                           | 00h              |           |

|                           | register 'f'          | Data                                | register 'f'                        |          | WDT Co<br>WDT Po          |                                           | 0011             |           |

| <b>-</b>                  |                       |                                     |                                     |          | TO                        | =                                         | 1                |           |

| Example:                  | CLRF                  | FLAG_REG,                           | Ţ                                   |          | PD                        | =                                         | 1                |           |

| Before Instruc<br>FLAG RI |                       | h                                   |                                     |          |                           |                                           |                  |           |

| After Instructio          |                       | 11                                  |                                     |          |                           |                                           |                  |           |

| FLAG_RI                   |                       | n                                   |                                     |          |                           |                                           |                  |           |

| RETFIE                  | Return from Inter                                                      | rupt           | RETLW                 | Return Li                                                                      | teral to W                         |                           |  |

|-------------------------|------------------------------------------------------------------------|----------------|-----------------------|--------------------------------------------------------------------------------|------------------------------------|---------------------------|--|

| Syntax:                 | RETFIE {s}                                                             |                | Syntax:               | RETLW k                                                                        |                                    |                           |  |

| Operands:               | <b>S</b> ∈ [0,1]                                                       |                | Operands:             | $0 \le k \le 255$                                                              |                                    |                           |  |

| Operation:              | $(TOS) \rightarrow PC,$<br>1 $\rightarrow$ GIE/GIEH or PE<br>if s = 1, | IE/GIEL;       | Operation:            | $k \rightarrow W$ ,<br>(TOS) $\rightarrow$ PC,<br>PCLATU, PCLATH are unchanged |                                    |                           |  |

|                         | $(WS) \rightarrow W,$                                                  | 10             | Status Affected:      | None                                                                           |                                    |                           |  |

|                         | $(STATUSS) \rightarrow STATU$<br>(BSRS) $\rightarrow$ BSR,             | 53,            | Encoding:             | 0000                                                                           | 1100 kk                            | kk kkkk                   |  |

|                         | PCLATU, PCLATH a                                                       | e unchanged    | Description:          | W is loaded                                                                    | d with the eigh                    | t-bit literal 'k'.        |  |

| Status Affected:        | GIE/GIEH, PEIE/GIE                                                     | L              |                       |                                                                                |                                    | baded from the            |  |

| Encoding:               | 0000 0000                                                              | 0001 000s      |                       | •                                                                              | tack (the retur<br>ddress latch (F | ,                         |  |

| Description:            | Return from interrupt                                                  |                |                       | remains un                                                                     | •                                  | ,                         |  |

|                         | and Top-of-Stack (TC the PC. Interrupts are                            |                | Words:                | 1                                                                              |                                    |                           |  |

|                         | setting either the high                                                | •              | Cycles:               | 2                                                                              |                                    |                           |  |

|                         | global interrupt enabl                                                 |                | Q Cycle Activity:     |                                                                                |                                    |                           |  |

|                         | contents of the shade<br>STATUSS and BSRS                              | -              | Q1                    | Q2                                                                             | Q3                                 | Q4                        |  |

|                         | their corresponding re                                                 | egisters, W,   | Decode                | Read                                                                           | Process                            | POP PC                    |  |

|                         | STATUS and BSR. If                                                     |                |                       | literal 'k'                                                                    | Data                               | from stack,<br>Write to W |  |

| Words:                  | of these registers occ<br>1                                            | uis (delauit). | No                    | No                                                                             | No                                 | No                        |  |

| Cycles:                 | 2                                                                      |                | operation             | operation                                                                      | operation                          | operation                 |  |

|                         |                                                                        |                | <b>-</b> .            |                                                                                |                                    |                           |  |

| Q Cycle Activity:<br>Q1 | Q2 Q3                                                                  | Q4             | Example:              |                                                                                |                                    |                           |  |

| Decode                  | No No                                                                  | POP PC         | CALL TABLE            | ; W conta:                                                                     | ins table                          |                           |  |

|                         | operation operati                                                      | on from stack  |                       | ; offset y                                                                     |                                    |                           |  |

|                         |                                                                        | Set GIEH or    |                       | ; W now ha<br>; table va                                                       |                                    |                           |  |

| No                      | No No                                                                  | GIEL           | :                     |                                                                                |                                    |                           |  |

| operation               | operation operati                                                      | -              | TABLE<br>ADDWF PCL    | ; W = off:                                                                     | 20t                                |                           |  |

|                         |                                                                        | <u>.</u>       | RETLW k0              | ; Begin ta                                                                     |                                    |                           |  |

| Example:                | RETFIE 1                                                               |                | RETLW kl<br>:         | ;                                                                              |                                    |                           |  |

| After Interru           |                                                                        |                | :                     |                                                                                |                                    |                           |  |

| PC<br>W                 | = VV                                                                   |                | RETLW kn              | ; End of t                                                                     | table                              |                           |  |

| BSR<br>STATU<br>GIE/GI  |                                                                        | SRS<br>FATUSS  | Before Instruc        |                                                                                |                                    |                           |  |

|                         | ,                                                                      |                | W<br>After Instructio | = 07h<br>on                                                                    |                                    |                           |  |

|                         |                                                                        |                | W                     | = value of                                                                     | f kn                               |                           |  |

| TST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | FSZ                                              | Test f, Skip if 0        |                 |                 |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------|-----------------|-----------------|--|--|--|--|--|

| Synta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ax:                                              | TSTFSZ f {               | ,a}             |                 |  |  |  |  |  |

| Opera                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ands:                                            | 0 ≤ f ≤ 255<br>a ∈ [0,1] |                 |                 |  |  |  |  |  |

| Oper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ation:                                           | skip if f = 0            |                 |                 |  |  |  |  |  |

| Statu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | s Affected:                                      | None                     |                 |                 |  |  |  |  |  |

| Enco                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ding:                                            | 0110                     | 011a fff        | f ffff          |  |  |  |  |  |

| Description:<br>If 'f' = 0, the next instruction fetched<br>during the current instruction executio<br>is discarded and a NOP is executed,<br>making this a two-cycle instruction.<br>If 'a' is '0', the Access Bank is selecte<br>If 'a' is '1', the BSR is used to select th<br>GPR bank (default).<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operate<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 22.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                                                  |                          |                 |                 |  |  |  |  |  |

| Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | s:                                               | 1                        |                 |                 |  |  |  |  |  |

| Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | es:                                              | •                        |                 |                 |  |  |  |  |  |

| QC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ycle Activity:                                   | ,                        |                 |                 |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Q1                                               | Q2                       | Q3              | Q4              |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Decode                                           | Read                     | Process         | No              |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                  | register 'f'             | Data            | operation       |  |  |  |  |  |

| lf ski                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ip:<br>Q1                                        | Q2                       | 03              | Q4              |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | No                                               | No                       | Q3<br>No        | No              |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | operation                                        | operation                | operation       | operation       |  |  |  |  |  |

| lf sk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ip and followed                                  |                          | struction:      |                 |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Q1                                               | Q2                       | Q3              | Q4              |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | No                                               | No                       | No              | No              |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | operation                                        | operation                | operation       | operation       |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | No<br>operation                                  | No<br>operation          | No<br>operation | No<br>operation |  |  |  |  |  |

| <u>Exam</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <u>nple:</u>                                     | NZERO                    | NZERO :         |                 |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Before Instruc<br>PC                             | = Ad                     | dress (HERE     | )               |  |  |  |  |  |