Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 32                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                |

| Data Converters            | A/D 13x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f44j10-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

FIGURE 1-1: PIC18F24J10/25J10 (28-PIN) BLOCK DIAGRAM Data Bus<8> Table Pointer<21> Data Latch 8 8 inc/dec logic X RA0/AN0 Data Memory RA1/AN1 (1 Kbyte) PCLATU PCLATH 21 RA2/AN2/VREF-/CVREF Address Latch RA3/AN3/VREF+ 20 PCU PCH PCL Program Counter RA5/AN4/SS1/C2OUT Data Address<12> 31 Level Stack Address Latch 12 BSR Access Program Memory (16/32 Kbytes) FSR0 STKPTR Bank FSR1 FSR2 Data Latch 12 **PORTB** RB0/INT0/FLT0/AN12 inc/de RB1/INT1/AN10 logic Table Latch RB2/INT2/AN8 RB3/AN9/CCP2<sup>(1)</sup> RB4/KBI0/AN11 Address RB5/KBI1/T0CKI/C1OUT Decode Instruction Bus <16> RB6/KBI2/PGC RB7/KBI3/PGD IR 8 State Machine Instruction Control Signals Decode and Control PRODH PRODL **PORTC** RC0/T1OSO/T1CKI RC1/T1OSI/CCP2<sup>(1)</sup> 8 x 8 Multiply RC2/CCP1 **BITOP** W RC3/SCK1/SCL1 RC4/SDI1/SDA1 RC5/SDO1 VDDCORE X Internal Power-up RC6/TX/CK Oscillator 8 RC7/RX/DT Block OSC1  $\boxtimes$ Oscillator ALÚ<8> Start-up Timei INTRC  $\boxtimes$ -OSC2 Oscillator Power-on 8 Reset T10SI Watchdog T10S0 🔀 Precision Brown-out(2) Single-Supply  $\boxtimes$ MCLR Reset Programming Reference Fail-Safe In-Circuit VDD, VSS Clock Monitor Debugger ADC BOR<sup>(2)</sup> Timer0 Timer1 Timer2 10-Bit MSSP CCP1 CCP2 **EUSART** Comparator Note 1: CCP2 is multiplexed with RC1 when Configuration bit, CCP2MX, is set, or RB3 when CCP2MX is not set. Brown-out Reset is not available in PIC18LF2XJ10/4XJ10 devices.

TABLE 1-3: PIC18F44J10/45J10 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name                                          | Piı  | n Numb | oer  | Pin               | Buffer                | Description                                                                                                                                                              |

|---------------------------------------------------|------|--------|------|-------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| riii Naiile                                       | PDIP | QFN    | TQFP | Type              | Type                  | Description                                                                                                                                                              |

| RD0/PSP0/SCK2/                                    | 19   | 38     | 38   |                   |                       | PORTD is a bidirectional I/O port or a Parallel Slave Port (PSP) for interfacing to a microprocessor port. These pins have TTL input buffers when PSP module is enabled. |

| SCL2                                              | 10   | 50     |      |                   |                       |                                                                                                                                                                          |

| RD0<br>PSP0<br>SCK2                               |      |        |      | I/O<br>I/O<br>I/O | ST<br>TTL<br>ST       | Digital I/O. Parallel Slave Port data. Synchronous serial clock input/output for SPI mode.                                                                               |

| SCL2                                              |      |        |      | I/O               | ST                    | Synchronous serial clock input/output for I <sup>2</sup> C™ mode.                                                                                                        |

| RD1/PSP1/SDI2/SDA2<br>RD1<br>PSP1<br>SDI2<br>SDA2 | 20   | 39     | 39   | I/O<br>I/O<br>I   | ST<br>TTL<br>ST<br>ST | Digital I/O. Parallel Slave Port data. SPI data in. I <sup>2</sup> C data I/O.                                                                                           |

| RD2/PSP2/SDO2<br>RD2<br>PSP2<br>SDO2              | 21   | 40     | 40   | I/O<br>I/O<br>O   | ST<br>TTL<br>—        | Digital I/O.<br>Parallel Slave Port data.<br>SPI data out.                                                                                                               |

| RD3/PSP3/SS2<br>RD3<br>PSP3<br>SS2                | 22   | 41     | 41   | I/O<br>I/O<br>I   | ST<br>TTL<br>TTL      | Digital I/O.<br>Parallel Slave Port data.<br>SPI slave select input.                                                                                                     |

| RD4/PSP4<br>RD4<br>PSP4                           | 27   | 2      | 2    | I/O<br>I/O        | ST<br>TTL             | Digital I/O.<br>Parallel Slave Port data.                                                                                                                                |

| RD5/PSP5/P1B<br>RD5<br>PSP5<br>P1B                | 28   | 3      | 3    | I/O<br>I/O<br>O   | ST<br>TTL<br>—        | Digital I/O. Parallel Slave Port data. Enhanced CCP1 output.                                                                                                             |

| RD6/PSP6/P1C<br>RD6<br>PSP6<br>P1C                | 29   | 4      | 4    | I/O<br>I/O<br>O   | ST<br>TTL<br>—        | Digital I/O. Parallel Slave Port data. Enhanced CCP1 output.                                                                                                             |

| RD7/PSP7/P1D<br>RD7<br>PSP7<br>P1D                | 30   | 5      | 5    | I/O<br>I/O<br>O   | ST<br>TTL<br>—        | Digital I/O. Parallel Slave Port data. Enhanced CCP1 output.                                                                                                             |

Legend: TTL = TTL compatible input

CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels

I = Input

O = Output

P = Power

Note 1: Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

**NOTES:**

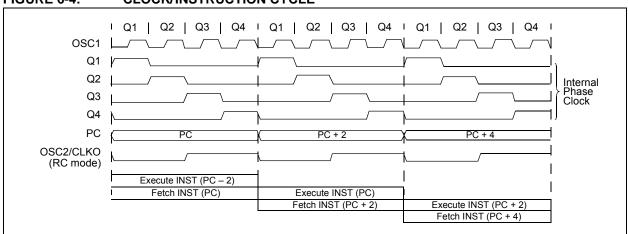

### 6.2 PIC18 Instruction Cycle

### 6.2.1 CLOCKING SCHEME

The microcontroller clock input, whether from an internal or external source, is internally divided by four to generate four non-overlapping quadrature clocks (Q1, Q2, Q3 and Q4). Internally, the program counter is incremented on every Q1; the instruction is fetched from the program memory and latched into the instruction register during Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 6-4.

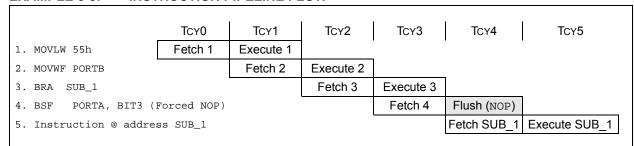

### 6.2.2 INSTRUCTION FLOW/PIPELINING

An "Instruction Cycle" consists of four Q cycles: Q1 through Q4. The instruction fetch and execute are pipelined in such a manner that a fetch takes one instruction cycle, while the decode and execute take another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 6-3).

A fetch cycle begins with the Program Counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

### **EXAMPLE 6-3: INSTRUCTION PIPELINE FLOW**

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

### REGISTER 9-8: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

| R/W-0  | R/W-0 | U-0 | U-0 | R/W-0  | U-0 | U-0 | R/W-0  |

|--------|-------|-----|-----|--------|-----|-----|--------|

| OSCFIE | CMIE  | _   | _   | BCL1IE | _   | _   | CCP2IE |

| bit 7  |       |     |     |        |     |     | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 OSCFIE: Oscillator Fail Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 6 CMIE: Comparator Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 5-4 **Unimplemented:** Read as '0'

bit 3 **BCL1IE:** Bus Collision Interrupt Enable bit (MSSP1 module)

1 = Enabled

0 = Disabled

bit 2-1 Unimplemented: Read as '0'

bit 0 CCP2IE: CCP2 Interrupt Enable bit

1 = Enabled

0 = Disabled

### REGISTER 9-9: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

| R/W-0  | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|--------|-----|-----|-----|-----|-----|-------|

| SSP2IE | BCL2IE | _   | _   | _   | _   | _   | _     |

| bit 7  |        |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 SSP2IE: Master Synchronous Serial Port 2 Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 6 BCL2IE: Bus Collision Interrupt Enable bit (MSSP2 module)

1 = Enabled

0 = Disabled

bit 5-0 **Unimplemented:** Read as '0'

TABLE 10-9: PORTD I/O SUMMARY

|                |          |                 |     | IIII III             |                                                                                                                                                   |  |  |

|----------------|----------|-----------------|-----|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin            | Function | TRIS<br>Setting | I/O | I/O<br>Type          | Description                                                                                                                                       |  |  |

| RD0/PSP0/SCK2/ | RD0      | 0               | 0   | DIG                  | LATD<0> data output.                                                                                                                              |  |  |

| SCL2           |          | 1               |     | ST                   | PORTD<0> data input.                                                                                                                              |  |  |

|                | PSP0     | x               | 0   | DIG                  | PSP read data output (LATD<0>); takes priority over port data.                                                                                    |  |  |

|                |          | x               | ı   | TTL                  | PSP write data input.                                                                                                                             |  |  |

|                | SCK2     | 0               | 0   | DIG                  | SPI clock output (MSSP2 module); takes priority over port data.                                                                                   |  |  |

|                |          | 1               | - 1 | ST                   | SPI clock input (MSSP2 module).                                                                                                                   |  |  |

|                | SCL2     | 0               | 0   | DIG                  | I <sup>2</sup> C™ clock output (MSSP2 module); takes priority over port data.                                                                     |  |  |

|                |          | 1               | I   | I <sup>2</sup> C/SMB | I <sup>2</sup> C clock input (MSSP2 module); input type depends on module setting.                                                                |  |  |

| RD1/PSP1/SDI2/ | RD1      | 0               | 0   | DIG                  | LATD<1> data output.                                                                                                                              |  |  |

| SDA2           |          | 1               | ı   | ST                   | PORTD<1> data input.                                                                                                                              |  |  |

|                | PSP1     | х               | 0   | DIG                  | PSP read data output (LATD<1>); takes priority over port data.                                                                                    |  |  |

|                |          | х               | ı   | TTL                  | PSP write data input.                                                                                                                             |  |  |

|                | SDI2     | 1               | I   | ST                   | SPI data input (MSSP2 module).                                                                                                                    |  |  |

|                | SDA2     | 1               | 0   | DIG                  | I <sup>2</sup> C data output (MSSP2 module); takes priority over port data.                                                                       |  |  |

|                |          | 1               | I   | I <sup>2</sup> C/SMB | I <sup>2</sup> C data input (MSSP2 module); input type depends on module setting.                                                                 |  |  |

| RD2/PSP2/SDO2  | RD2      | 0               | 0   | DIG                  | LATD<2> data output.                                                                                                                              |  |  |

|                |          | 1               | I   | ST                   | PORTD<2> data input.                                                                                                                              |  |  |

|                | PSP2     | х               | 0   | DIG                  | PSP read data output (LATD<2>); takes priority over port data.                                                                                    |  |  |

|                |          | х               | I   | TTL                  | PSP write data input.                                                                                                                             |  |  |

|                | SDO2     | 0               | 0   | DIG                  | SPI data output (MSSP2 module); takes priority over port data.                                                                                    |  |  |

| RD3/PSP3/SS2   | RD3      | 0               | 0   | DIG                  | LATD<3> data output.                                                                                                                              |  |  |

|                |          | 1               | ı   | ST                   | PORTD<3> data input.                                                                                                                              |  |  |

|                | PSP3     | x               | 0   | DIG                  | PSP read data output (LATD<3>); takes priority over port data.                                                                                    |  |  |

|                |          | x               | ı   | TTL                  | PSP write data input.                                                                                                                             |  |  |

|                | SS2      | 1               | ı   | TTL                  | Slave select input for MSSP2 (MSSP2 module).                                                                                                      |  |  |

| RD4/PSP4       | RD4      | 0               | 0   | DIG                  | LATD<4> data output.                                                                                                                              |  |  |

|                |          | 1               | I   | ST                   | PORTD<4> data input.                                                                                                                              |  |  |

|                | PSP4     | х               | 0   | DIG                  | PSP read data output (LATD<4>); takes priority over port data.                                                                                    |  |  |

|                |          | х               | I   | TTL                  | PSP write data input.                                                                                                                             |  |  |

| RD5/PSP5/P1B   | RD5      | 0               | 0   | DIG                  | LATD<5> data output.                                                                                                                              |  |  |

|                |          | 1               | ı   | ST                   | PORTD<5> data input.                                                                                                                              |  |  |

|                | PSP5     | х               | 0   | DIG                  | PSP read data output (LATD<5>); takes priority over port data.                                                                                    |  |  |

|                |          | х               | I   | TTL                  | PSP write data input.                                                                                                                             |  |  |

|                | P1B      | 0               | 0   | DIG                  | ECCP1 Enhanced PWM output, Channel B; takes priority over port and PSP data. May be configured for tri-state during Enhanced PWM shutdown events. |  |  |

| RD6/PSP6/P1C   | RD6      | 0               | 0   | DIG                  | LATD<6> data output.                                                                                                                              |  |  |

|                |          | 1               | ı   | ST                   | PORTD<6> data input.                                                                                                                              |  |  |

|                | PSP6     | х               | 0   | DIG                  | PSP read data output (LATD<6>); takes priority over port data.                                                                                    |  |  |

|                |          | х               | ı   | TTL                  | PSP write data input.                                                                                                                             |  |  |

|                | P1C      | 0               | 0   | DIG                  | ECCP1 Enhanced PWM output, Channel C; takes priority over port and PSP data. May be configured for tri-state during Enhanced PWM shutdown events. |  |  |

| RD7/PSP7/P1D   | RD7      | 0               | 0   | DIG                  | LATD<7> data output.                                                                                                                              |  |  |

|                |          | 1               | 1   | ST                   | PORTD<7> data input.                                                                                                                              |  |  |

|                | PSP7     | x               | 0   | DIG                  | PSP read data output (LATD<7>); takes priority over port data.                                                                                    |  |  |

|                |          | x               | ı   | TTL                  | PSP write data input.                                                                                                                             |  |  |

|                | P1D      | 0               | 0   | DIG                  | ECCP1 Enhanced PWM output, Channel D; takes priority over port and PSP data. May be configured for tri-state during Enhanced PWM shutdown events. |  |  |

**Legend:** DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer;  ${}^{1}C^{TM}/SMB = {}^{1}C/SMBus$  input buffer; x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

#### **FIGURE 12-2:** TIMER1 BLOCK DIAGRAM (16-BIT READ/WRITE MODE) Timer1 Oscillator Timer1 Clock Input T10S0/T1CKI Synchronize Prescaler 0 Fosc/4 ■ Detect 1, 2, 4, 8 Internal Clock T10SI 2 Sleep Input T10SCEN<sup>(1)</sup> Timer1 TMR1CS On/Off T1CKPS<1:0> T1SYNC TMR10N TMR1 Clear TMR1 TMR1L TMR1IF High Byte on Overflow (CCP Special Event Trigger) Read TMR1L Write TMR1L 8 TMR1H Internal Data Bus Note 1: When enable bit, T1OSCEN, is cleared, the inverter and feedback resistor are turned off to eliminate power drain.

### 12.2 Timer1 16-Bit Read/Write Mode

Timer1 can be configured for 16-bit reads and writes (see Figure 12-2). When the RD16 control bit (T1CON<7>) is set, the address for TMR1H is mapped to a buffer register for the high byte of Timer1. A read from TMR1L will load the contents of the high byte of Timer1 into the Timer1 High Byte Buffer register. This provides the user with the ability to accurately read all 16 bits of Timer1 without having to determine whether a read of the high byte, followed by a read of the low byte, has become invalid due to a rollover between reads.

A write to the high byte of Timer1 must also take place through the TMR1H Buffer register. The Timer1 high byte is updated with the contents of TMR1H when a write occurs to TMR1L. This allows a user to write all 16 bits to both the high and low bytes of Timer1 at once.

The high byte of Timer1 is not directly readable or writable in this mode. All reads and writes must take place through the Timer1 High Byte Buffer register. Writes to TMR1H do not clear the Timer1 prescaler. The prescaler is only cleared on writes to TMR1L.

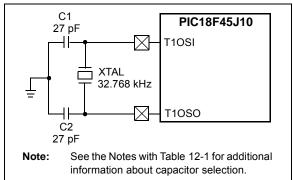

### 12.3 Timer1 Oscillator

An on-chip crystal oscillator circuit is incorporated between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting the Timer1 Oscillator Enable bit, T1OSCEN (T1CON<3>). The oscillator is a low-power circuit rated for 32 kHz crystals. It will continue to run during all power-managed modes. The circuit for a typical oscillator is shown in Figure 12-3. Table 12-1 shows the capacitor selection for the Timer1 oscillator.

The user must provide a software time delay to ensure proper start-up of the Timer1 oscillator.

FIGURE 12-3: EXTERNAL COMPONENTS FOR THE TIMER1 OSCILLATOR

### 14.1 CCP Module Configuration

Each Capture/Compare/PWM module is associated with a control register (generically, CCPxCON) and a data register (CCPRx). The data register, in turn, is comprised of two 8-bit registers: CCPRxL (low byte) and CCPRxH (high byte). All registers are both readable and writable.

# 14.1.1 CCP MODULES AND TIMER RESOURCES

The CCP modules utilize Timers 1 or 2, depending on the mode selected. Timer1 is available to modules in Capture or Compare modes, while Timer2 is available for modules in PWM mode.

TABLE 14-1: ECCP/CCP MODE – TIMER RESOURCE

| ECCP/CCP Mode      | Timer Resource   |

|--------------------|------------------|

| Capture<br>Compare | Timer1<br>Timer1 |

| PWM                | Timer2           |

Both modules may be active at any given time and may share the same timer resource if they are configured to operate in the same mode (Capture/Compare or PWM) at the same time. The interactions between the two modules are summarized in Figure 14-1 and Figure 14-2. In Timer1 in Asynchronous Counter mode, the capture operation will not work.

### 14.1.2 CCP2 PIN ASSIGNMENT

The pin assignment for CCP2 (Capture input, Compare and PWM output) can change, based on device configuration. The CCP2MX Configuration bit determines which pin CCP2 is multiplexed to. By default, it is assigned to RC1 (CCP2MX = 1). If the Configuration bit is cleared, CCP2 is multiplexed with RB3.

Changing the pin assignment of CCP2 does not automatically change any requirements for configuring the port pin. Users must always verify that the appropriate TRIS register is configured correctly for CCP2 operation regardless of where it is located.

TABLE 14-2: INTERACTIONS BETWEEN ECCP1/CCP1 AND CCP2 FOR TIMER RESOURCES

| CCP1 Mode          | CCP2 Mode          | Interaction                                                                                                                                                                    |

|--------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Capture            | Capture            | Each module uses TMR1 as the time base.                                                                                                                                        |

| Capture            | Compare            | CCP2 can be configured for the Special Event Trigger to reset TMR1. Automatic A/D conversions on the trigger event can also be done. Operation of ECCP1/CCP1 will be affected. |

| Compare            | Capture            | ECCP1/CCP1 can be configured for the Special Event Trigger to reset TMR1. Operation of CCP2 will be affected.                                                                  |

| Compare            | Compare            | Either module can be configured for the Special Event Trigger to reset TMR1. Automatic A/D conversions on the CCP2 trigger event can be done.                                  |

| Capture            | PWM <sup>(1)</sup> | None                                                                                                                                                                           |

| Compare            | PWM <sup>(1)</sup> | None                                                                                                                                                                           |

| PWM <sup>(1)</sup> | Capture            | None                                                                                                                                                                           |

| PWM <sup>(1)</sup> | Compare            | None                                                                                                                                                                           |

| PWM <sup>(1)</sup> | PWM                | Both PWMs will have the same frequency and update rate (TMR2 interrupt).                                                                                                       |

**Note 1:** Includes standard and Enhanced PWM operation.

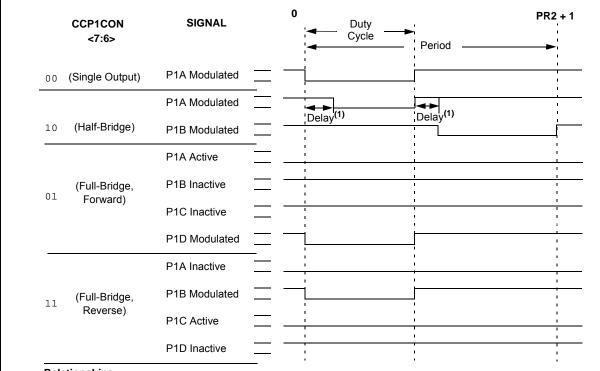

0 PR2 + 1 **SIGNAL** Duty CCP1CON Cycle <7:6> Period P1A Modulated (Single Output) 00 Delay<sup>(1)</sup> Delay<sup>(1)</sup> P1A Modulated (Half-Bridge) 10 P1B Modulated P1A Active P1B Inactive (Full-Bridge, Forward) P1C Inactive P1D Modulated P1A Inactive P1B Modulated (Full-Bridge, 11 Reverse) P1C Active P1D Inactive

FIGURE 15-2: PWM OUTPUT RELATIONSHIPS (ACTIVE-HIGH STATE)

FIGURE 15-3: PWM OUTPUT RELATIONSHIPS (ACTIVE-LOW STATE)

### Relationships:

- Period = 4 \* Tosc \* (PR2 + 1) \* (TMR2 Prescale Value)

- Duty Cycle = Tosc \* (CCPR1L<7:0>:CCP1CON<5:4>) \* (TMR2 Prescale Value)

- Delay = 4 \* Tosc \* (ECCP1DEL<6:0>)

Note 1: Dead-band delay is programmed using the ECCP1DEL register (see Section 15.4.6 "Programmable Dead-Band Delay").

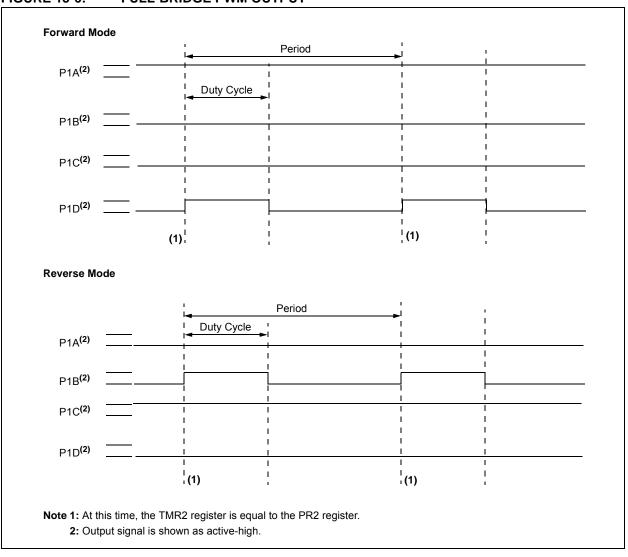

### 15.4.5 FULL-BRIDGE MODE

In Full-Bridge Output mode, four pins are used as outputs; however, only two outputs are active at a time. In the Forward mode, pin P1A is continuously active and pin P1D is modulated. In the Reverse mode, pin P1C is continuously active and pin P1B is modulated. These are illustrated in Figure 15-6.

P1A, P1B, P1C and P1D outputs are multiplexed with the PORTC<2> and PORTD<7:5> data latches. The TRISC<2> and TRISD<7:5> bits must be cleared to make the P1A, P1B, P1C and P1D pins outputs.

FIGURE 15-6: FULL-BRIDGE PWM OUTPUT

# REGISTER 15-3: ECCP1AS: ENHANCED CAPTURE/COMPARE/PWM AUTO-SHUTDOWN CONTROL REGISTER

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0                 | R/W-0                 |

|---------|---------|---------|---------|--------|--------|-----------------------|-----------------------|

| ECCPASE | ECCPAS2 | ECCPAS1 | ECCPAS0 | PSSAC1 | PSSAC0 | PSSBD1 <sup>(1)</sup> | PSSBD0 <sup>(1)</sup> |

| bit 7   |         |         |         |        |        |                       | bit 0                 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 **ECCPASE:** ECCP Auto-Shutdown Event Status bit

1 = A shutdown event has occurred; ECCP outputs are in shutdown state

0 = ECCP outputs are operating

bit 6-4 ECCPAS<2:0>: ECCP Auto-Shutdown Source Select bits

111 = FLT0. Comparator 1 or Comparator 2

110 = FLT0 or Comparator 2

101 = FLT0 or Comparator 1

100 = FLT0

011 = Either Comparator 1 or 2

010 = Comparator 2 output

001 = Comparator 1 output

000 = Auto-shutdown is disabled

bit 3-2 **PSSAC<1:0>:** Pins A and C Shutdown State Control bits

1x = Pins A and C are tri-state (40/44-pin devices); PWM output is tri-state (28-pin devices)

01 = Drive Pins A and C to '1'

00 = Drive Pins A and C to '0'

bit 1-0 **PSSBD<1:0>:** Pins B and D Shutdown State Control bits<sup>(1)</sup>

1x = Pins B and D tri-state

01 = Drive Pins B and D to '1'

00 = Drive Pins B and D to '0'

Note 1: Reserved on 28-pin devices; maintain these bits clear.

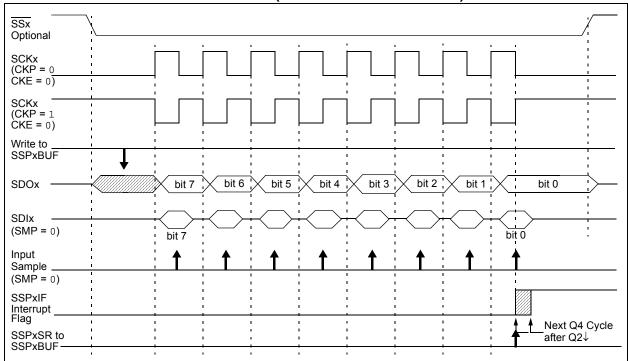

FIGURE 16-5: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 0)

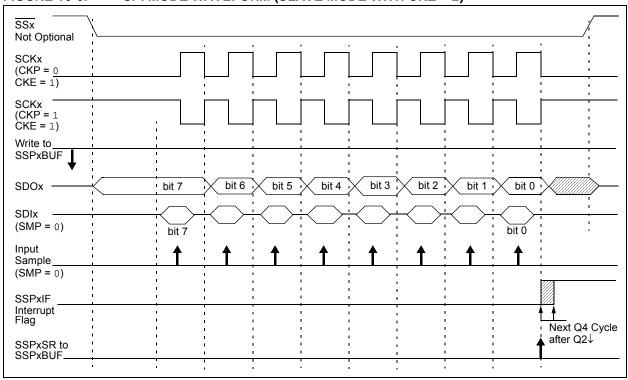

FIGURE 16-6: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

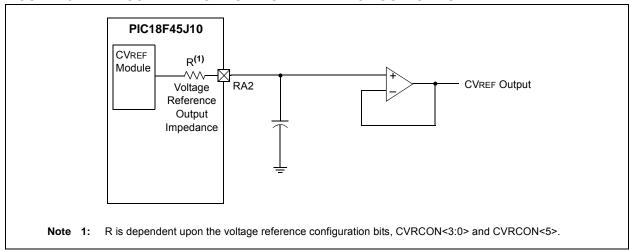

### FIGURE 20-2: COMPARATOR VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

TABLE 20-1: REGISTERS ASSOCIATED WITH COMPARATOR VOLTAGE REFERENCE

| Name   | Bit 7 | Bit 6 | Bit 5  | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|-------|-------|--------|-------|--------|--------|--------|--------|----------------------------|

| CVRCON | CVREN | CVROE | CVRR   | CVRSS | CVR3   | CVR2   | CVR1   | CVR0   | 49                         |

| CMCON  | C2OUT | C1OUT | C2INV  | C1INV | CIS    | CM2    | CM1    | CM0    | 49                         |

| TRISA  | _     | _     | TRISA5 | -     | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 50                         |

Legend: Shaded cells are not used with the comparator voltage reference.

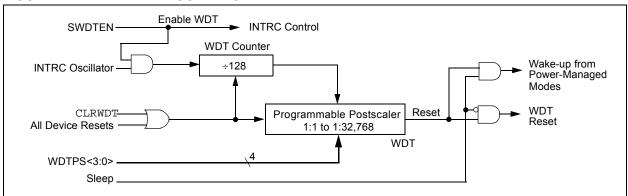

### 21.2 Watchdog Timer (WDT)

For PIC18F45J10 family devices, the WDT is driven by the INTRC oscillator. When the WDT is enabled, the clock source is also enabled. The nominal WDT period is 4 ms and has the same stability as the INTRC oscillator.

The 4 ms period of the WDT is multiplied by a 16-bit postscaler. Any output of the WDT postscaler is selected by a multiplexor, controlled by the WDTPS bits in Configuration Register 2H. Available periods range from about 4 ms to 135 seconds (2.25 minutes) depending on voltage, temperature and Watchdog postscaler. The WDT and postscaler are cleared whenever a SLEEP or CLRWDT instruction is executed, or a clock failure (primary or Timer1 oscillator) has occurred.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and postscaler counts when executed.

- **2:** When a CLRWDT instruction is executed, the postscaler count will be cleared.

### 21.2.1 CONTROL REGISTER

The WDTCON register (Register 21-9) is a readable and writable register. The SWDTEN bit enables or disables WDT operation.

### FIGURE 21-1: WDT BLOCK DIAGRAM

### REGISTER 21-9: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| u-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0                 |

|-------|-----|-----|-----|-----|-----|-----|-----------------------|

| _     | _   | _   | _   | _   | _   | _   | SWDTEN <sup>(1)</sup> |

| bit 7 |     |     |     |     |     |     | bit 0                 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-1 **Unimplemented**: Read as '0'

bit 0 **SWDTEN:** Software Controlled Watchdog Timer Enable bit<sup>(1)</sup>

1 = Watchdog Timer is on0 = Watchdog Timer is off

Note 1: This bit has no effect if the Configuration bit, WDTEN, is enabled.

### TABLE 21-2: SUMMARY OF WATCHDOG TIMER REGISTERS

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Reset Values on page |

|--------|-------|-------|-------|-------|-------|-------|-------|--------|----------------------|

| RCON   | IPEN  | _     | CM    | RI    | TO    | PD    | POR   | BOR    | 48                   |

| WDTCON | _     | _     | _     | _     | _     | _     | _     | SWDTEN | 48                   |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the Watchdog Timer.

| BCF              | Bit Clear f                                                                                                                                                                                                                              |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | BCF f, b {,a}                                                                                                                                                                                                                            |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 255$<br>$0 \le b \le 7$<br>$a \in [0, 1]$                                                                                                                                                                                   |  |  |  |  |  |  |

| Operation:       | $0 \rightarrow f < b >$                                                                                                                                                                                                                  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| Encoding:        | 1001 bbba ffff ffff                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Description:     | Bit 'b' in register 'f' is cleared.  If 'a' is '0', the Access Bank is selected.  If 'a' is '1', the BSR is used to select the GPR bank (default).  If 'a' is '0' and the extended instruction set is enabled, this instruction operates |  |  |  |  |  |  |

**Bit-Oriented Instructions in Indexed** Literal Offset Mode" for details. Words:

Q Cycle Activity:

Cycles:

| Q1     | Q2           | Q3      | Q4           |

|--------|--------------|---------|--------------|

| Decode | Read         | Process | Write        |

|        | register 'f' | Data    | register 'f' |

in Indexed Literal Offset Addressing

Section 22.2.3 "Byte-Oriented and

mode whenever  $f \le 95$  (5Fh). See

Example: BCF FLAG\_REG, 7, 0

Before Instruction

FLAG\_REG = C7h

After Instruction

FLAG\_REG = 47h BN **Branch if Negative**

Syntax: BN n

$-128 \le n \le 127$ Operands:

Operation: if Negative bit is '1',  $(PC) + 2 + 2n \rightarrow PC$

Status Affected: None

Encoding: 1110 0110 nnnn nnnn

If the Negative bit is '1', then the Description:

program will branch.

The 2's complement number, '2n', is added to the PC. Since the PC will have incremented to fetch the next

instruction, the new address will be PC + 2 + 2n. This instruction is then a

two-cycle instruction.

Words: Cycles: 1(2)

Q Cycle Activity:

If Jump:

| Q1        | Q2           | Q3        | Q4          |

|-----------|--------------|-----------|-------------|

| Decode    | Read literal | Process   | Write to PC |

|           | ʻn'          | Data      |             |

| No        | No           | No        | No          |

| operation | operation    | operation | operation   |

If No Jump:

| Q1     | Q2           | Q3      | Q4        |

|--------|--------------|---------|-----------|

| Decode | Read literal | Process | No        |

|        | ʻn'          | Data    | operation |

Example: HERE BN Jump

Before Instruction

PC address (HERE)

After Instruction

If Negative PC

address (Jump)

address (HERE + 2)

| CLRF             | Clear f                                                                                                                                  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | CLRF f {,a}                                                                                                                              |

| Operands:        | $0 \le f \le 255$<br>$a \in [0, 1]$                                                                                                      |

| Operation:       | $000h \to f,$ $1 \to Z$                                                                                                                  |

| Status Affected: | Z                                                                                                                                        |

| Encoding:        | 0110 101a ffff ffff                                                                                                                      |

| Description:     | Clears the contents of the specified register.  If 'a' is '0', the Access Bank is selected.  If 'a' is '1' the BSR is used to select the |

If 'a' is '1', the BSR is used to select the GPR bank (default). If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever  $f \le 95$  (5Fh). See Section 22.2.3 "Byte-Oriented and

Bit-Oriented Instructions in Indexed Literal Offset Mode" for details.

Words: 1 Cycles: 1

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4           |

|--------|--------------|---------|--------------|

| Decode | Read         | Process | Write        |

|        | register 'f' | Data    | register 'f' |

Example: CLRF FLAG\_REG, 1

Before Instruction

FLAG\_REG = 5Ah

After Instruction

FLAG\_REG = 00h

### CLRWDT Clear Watchdog Timer

Syntax: CLRWDT Operands: None

Operation:  $000h \rightarrow WDT$ ,

000h → WDT postscaler,

$1 \to \overline{\frac{\text{TO}}{\text{PD}}},$

Status Affected:  $\overline{\text{TO}}$ ,  $\overline{\text{PD}}$

**Encoding**: 0000 0000 0000 0100

Description: CLRWDT instruction resets the Watchdog Timer. It also resets the postscaler of the WDT. Status bits, TO

and PD, are set.

Words: 1

Cycles: 1

Q Cycle Activity:

| Q1     | Q2        | Q3      | Q4        |

|--------|-----------|---------|-----------|

| Decode | No        | Process | No        |

|        | operation | Data    | operation |

Example: CLRWDT

Before Instruction

WDT Counter = ?

After Instruction

$\begin{array}{llll} \text{WDT Counter} & = & 00h \\ \underline{\text{WDT Postscaler}} & = & 0 \\ \underline{\overline{\text{TO}}} & = & 1 \\ \hline{\text{PD}} & = & 1 \end{array}$

© 2009 Microchip Technology Inc.

### TSTFSZ Test f, Skip if 0

Syntax: TSTFSZ f  $\{,a\}$  Operands:  $0 \le f \le 255$

$a \in [0, 1]$ skip if f = 0

Status Affected: None

Operation:

Encoding: 0110

Description:

If 'f' = 0, the next instruction fetched during the current instruction execution is discarded and a NOP is executed, making this a two-cycle instruction.

If 'a' is '0', the Access Bank is selected.

If 'a' is '1', the BSR is used to select the

011a

ffff

ffff

GPR bank (default). If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever f  $\leq$  95 (5Fh). See

Section 22.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details.

Words: 1

Cycles: 1(2)

Note: 3 cycles if skip and followed

by a 2-word instruction.

### Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4        |

|--------|--------------|---------|-----------|

| Decode | Read         | Process | No        |

|        | register 'f' | Data    | operation |

### If skip:

| Q1        | Q2        | Q3        | Q4        |

|-----------|-----------|-----------|-----------|

| No        | No        | No        | No        |

| operation | operation | operation | operation |

If skip and followed by 2-word instruction:

| Q1        | Q2        | Q3        | Q4        |

|-----------|-----------|-----------|-----------|

| No        | No        | No        | No        |

| operation | operation | operation | operation |

| No        | No        | No        | No        |

| operation | operation | operation | operation |

Example: HERE TSTFSZ CNT, 1

NZERO :

Before Instruction

PC = Address (HERE)

After Instruction

If CNT = 00h,

PC = Address (ZERO)

If CNT ≠ 00h,

PC = Address (NZERO)

### XORLW Exclusive OR Literal with W

Status Affected: N, Z

Encoding: 0000 1010 kkkk kkkk

Description: The contents of W are XORed with the 8-bit literal 'k'. The result is placed

in W.

Words: 1

Cycles: 1

Q Cycle Activity:

| Q1     | Q2          | Q3      | Q4         |

|--------|-------------|---------|------------|

| Decode | Read        | Process | Write to W |

|        | literal 'k' | Data    |            |

Example: XORLW 0AFh

Before Instruction

W = B5h

After Instruction

W = 1Ah

### 22.2.2 EXTENDED INSTRUCTION SET

| ADD               | FSR         | Add Lite                        | Add Literal to FSR |     |    |          |

|-------------------|-------------|---------------------------------|--------------------|-----|----|----------|

| Synta             | ax:         | ADDFSR                          | ADDFSR f, k        |     |    |          |

| Oper              | ands:       | $0 \le k \le 63$                | $0 \leq k \leq 63$ |     |    |          |

|                   |             | $f \in [0, 1, 2]$               |                    |     |    |          |

| Oper              | ation:      | $FSR(f) + k \rightarrow FSR(f)$ |                    |     |    |          |

| Statu             | s Affected: | None                            | None               |     |    |          |

| Enco              | ding:       | 1110                            | 1000               | ffk | .k | kkkk     |

| Desc              | ription:    | The 6-bit contents              |                    |     |    |          |

| Word              | s:          | 1                               | 1                  |     |    |          |

| Cycle             | es:         | 1                               | 1                  |     |    |          |

| Q Cycle Activity: |             |                                 |                    |     |    |          |

|                   | Q1          | Q2                              | Q3                 |     |    | Q4       |

|                   | Decode      | Read                            | Proce              | SS  | W  | /rite to |

Example: ADDFSR 2, 23h

literal 'k'

Data

**FSR**

Before Instruction

FSR2 = 03FFh

After Instruction

FSR2 = 0422h

| ADDULNK          | Add Literal to FSR2 and Return                                                                                                                                                                                                                                                                                                        |      |      |      |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|--|

| Syntax:          | ADDULN                                                                                                                                                                                                                                                                                                                                | K k  |      |      |  |

| Operands:        | $0 \le k \le 63$                                                                                                                                                                                                                                                                                                                      |      |      |      |  |

| Operation:       | $FSR2 + k \rightarrow FSR2$ ,                                                                                                                                                                                                                                                                                                         |      |      |      |  |

|                  | $(TOS) \rightarrow PC$                                                                                                                                                                                                                                                                                                                |      |      |      |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                  |      |      |      |  |

| Encoding:        | 1110                                                                                                                                                                                                                                                                                                                                  | 1000 | 11kk | kkkk |  |

| Description:     | The 6-bit literal 'k' is added to the contents of FSR2. A RETURN is then executed by loading the PC with the TOS.  The instruction takes two cycles to execute; a NOP is performed during the second cycle.  This may be thought of as a special case of the ADDFSR instruction, where f = 3 (binary '11'); it operates only on FSR2. |      |      |      |  |

| Words:           | 1                                                                                                                                                                                                                                                                                                                                     |      |      |      |  |

Q Cycle Activity:

Cycles:

| Q1        | Q2          | Q3        | Q4        |

|-----------|-------------|-----------|-----------|

| Decode    | Read        | Process   | Write to  |

|           | literal 'k' | Data      | FSR       |

| No        | No          | No        | No        |

| Operation | Operation   | Operation | Operation |

Example: ADDULNK 23h

Before Instruction

FSR2 = 03FFh PC = 0100h

After Instruction

FSR2 = 0422hPC = (TOS)

**Note:** All PIC18 instructions may take an optional label argument preceding the instruction mnemonic for use in symbolic addressing. If a label is used, the instruction syntax then becomes: {label} instruction argument(s).

#### MOVSS Move Indexed to Indexed

$\label{eq:syntax} \begin{array}{lll} \text{Syntax:} & \text{MOVSS} & [z_s], [z_d] \\ \text{Operands:} & 0 \leq z_s \leq 127 \\ & 0 \leq z_d \leq 127 \end{array}$

Operation:  $((FSR2) + z_s) \rightarrow ((FSR2) + z_d)$

Status Affected: None

Encoding: 1st word (source) 2nd word (dest.) Description

| 1110 | 1011 | 1zzz | zzzzs             |

|------|------|------|-------------------|

| 1111 | xxxx | XZZZ | zzzz <sub>d</sub> |

The contents of the source register are moved to the destination register. The addresses of the source and destination registers are determined by adding the 7-bit literal offsets ' $z_s$ ' or ' $z_d$ ',

respectively, to the value of FSR2. Both registers can be located anywhere in the 4096-byte data memory space (000h to FFFh).

The MOVSS instruction cannot use the PCL, TOSU, TOSH or TOSL as the

destination register.

If the resultant source address points to an indirect addressing register, the value returned will be 00h. If the resultant destination address points to an indirect addressing register, the instruction will execute as a NOP.

Words: 2 Cycles: 2

Q Cycle Activity:

| Q1     | Q2          | Q3          | Q4          |

|--------|-------------|-------------|-------------|

| Decode | Determine   | Determine   | Read        |

|        | source addr | source addr | source reg  |

| Decode | Determine   | Determine   | Write       |

|        | dest addr   | dest addr   | to dest reg |

Example: MOVSS [05h], [06h]

Before Instruction

FSR2 = 80h

Contents

of 85h = 33h

Contents

of 86h = 11h

After Instruction

FSR2 = 80h Contents of 85h = 33h Contents of 86h = 33h

### PUSHL Store Literal at FSR2, Decrement FSR2

Syntax: PUSHL k

Operands:  $0 \le k \le 255$ Operation:  $k \to (FSR2)$ ,

$FSR2 - 1 \rightarrow FSR2$

Status Affected: None

Encoding: 1111 1010 kkkk kkkk

Description: The 8-bit literal 'k' is written to the data memory address specified by FSR2. FSR2 is decremented by 1 after the operation.

This instruction allows users to push values

onto a software stack.

Words: 1

Cycles: 1

Q Cycle Activity:

| Q1     | Q2       | Q3      | Q4          |

|--------|----------|---------|-------------|

| Decode | Read 'k' | Process | Write to    |

|        |          | data    | destination |

Example: PUSHL 08h

Before Instruction

FSR2H:FSR2L = 01ECh Memory (01ECh) = 00h

After Instruction

FSR2H:FSR2L = 01EBh Memory (01ECh) = 08h

| PORTA                                         |     | Program Memory                                |        |      |

|-----------------------------------------------|-----|-----------------------------------------------|--------|------|

| Associated Registers                          | 100 | and Extended Instruction Set                  |        |      |

| LATA Register                                 | 98  | Flash Configuration Words                     |        | 52   |

| PORTA Register                                | 98  | Instructions                                  |        | 57   |

| TRISA Register                                | 98  | Two-Word                                      |        | 57   |

| PORTB                                         |     | Interrupt Vector                              | 51     | , 52 |

| Associated Registers                          | 103 | Look-up Tables                                |        | 55   |

| LATB Register                                 | 101 | Map and Stack (diagram)                       |        | 51   |

| PORTB Register                                | 101 | Memory Maps                                   |        |      |

| RB7:RB4 Interrupt-on-Change Flag (RBIF Bit) . | 101 | Hard Vectors and Configuration Words          |        | 52   |

| TRISB Register                                |     | Reset Vector                                  |        |      |

| PORTC                                         |     | Program Verification and Code Protection      |        | 247  |

| Associated Registers                          | 106 | Programming, Device Instructions              |        |      |

| LATC Register                                 |     | PSP. See Parallel Slave Port.                 |        |      |

| PORTC Register                                |     | Pulse-Width Modulation. See PWM (CCP Module)  |        |      |

| RC3/SCK1/SCL1 Pin                             |     | and PWM (ECCP Module).                        |        |      |

| TRISC Register                                |     | PUSH                                          |        | 278  |

| PORTD                                         |     | PUSH and POP Instructions                     |        |      |

| Associated Registers                          | 109 | PUSHL                                         |        |      |

| LATD Register                                 |     | PWM (CCP Module)                              |        |      |

| Parallel Slave Port (PSP) Function            |     | Associated Registers                          |        | 134  |

| PORTD Register                                |     | Auto-Shutdown (CCP1 Only)                     |        |      |

| TRISD Register                                |     | CCPR1H:CCPR1L Registers                       |        |      |

| PORTE                                         | 107 | Duty Cycle                                    |        |      |

| Associated Registers                          | 112 | Example Frequencies/Resolutions               |        |      |

| LATE Register                                 |     | Period                                        |        |      |

|                                               |     | Setup for Operation                           |        |      |

| PORTE Register                                |     |                                               |        |      |

| PSP Mode Select (PSPMODE Bit)                 |     | TMR2-to-PR2 Match                             |        |      |

| TRISE Register                                |     | PWM (ECCP Module)                             |        |      |

| Power-Managed Modes                           |     | Direction Change in Full-Bridge Output Mode . |        |      |

| and EUSART Operation                          |     | Effects of a Reset                            |        |      |

| and Multiple Sleep Commands                   |     | Enhanced PWM Auto-Shutdown                    |        |      |

| and PWM Operation                             |     | Full-Bridge Application Example               |        |      |

| and SPI Operation                             |     | Full-Bridge Mode                              |        |      |

| Clock Transitions and Status Indicators       |     | Half-Bridge Mode                              |        |      |

| Entering                                      |     | Half-Bridge Output Mode Applications Example  |        |      |

| Exiting Idle and Sleep Modes                  |     | Operation in Power-Managed Modes              |        |      |

| by Reset                                      |     | Operation with Fail-Safe Clock Monitor        |        |      |

| by WDT Time-out                               |     | Output Configurations                         |        |      |

| Without an Oscillator Start-up Delay          |     | Output Relationships (Active-High)            |        |      |

| Idle Modes                                    |     | Output Relationships (Active-Low)             |        |      |

| PRI_IDLE                                      |     | Programmable Dead-Band Delay                  |        |      |

| RC_IDLE                                       |     | Setup for PWM Operation                       |        |      |

| SEC_IDLE                                      |     | Start-up Considerations                       |        | 146  |

| Run Modes                                     |     | 0                                             |        |      |

| PRI_RUN                                       | 36  | Q                                             |        |      |

| RC_RUN                                        | 37  | Q Clock                                       | . 133, | 138  |

| SEC_RUN                                       | 36  | R                                             |        |      |

| Selecting                                     | 35  | N                                             |        |      |

| Sleep Mode                                    | 38  | RAM. See Data Memory.                         |        |      |

| Summary (table)                               | 35  | RBIF Bit                                      |        |      |

| Power-on Reset (POR)                          |     | RC_IDLE Mode                                  |        |      |

| Power-up Timer (PWRT)                         | 44  | RC_RUN Mode                                   |        |      |

| Time-out Sequence                             | 44  | RCALL                                         |        | 279  |

| Power-up Delays                               |     | RCON Register                                 |        |      |

| Power-up Timer (PWRT)                         |     | Bit Status During Initialization              |        | 46   |

| Prescaler                                     |     | Reader Response                               |        | 364  |

| Timer2                                        | 138 | Register File                                 |        |      |

| Prescaler, Timer0                             |     | Register File Summary                         |        |      |

| Prescaler, Timer2                             |     | Registers                                     |        |      |

| PRI IDLE Mode                                 |     | ADCON0 (A/D Control 0)                        |        | 215  |

| PRI_RUN Mode                                  |     | ADCON1 (A/D Control 1)                        |        |      |

| Program Counter                               |     | ADCON2 (A/D Control 2)                        |        |      |

| •                                             |     | BAUDCON (Baud Rate Control)                   |        |      |

| PCL, PCH and PCU Registers                    |     | CCP1CON (ECCP1 Control)                       |        |      |

| PCLATH and PCLATU Registers                   | 33  | CCPxCON (CCPx Control)                        |        |      |

|                                               |     | 001 A0014 (001 A 00111101)                    |        | . 21 |