Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 32                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                               |

| Data Converters            | A/D 13x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f44j10-i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

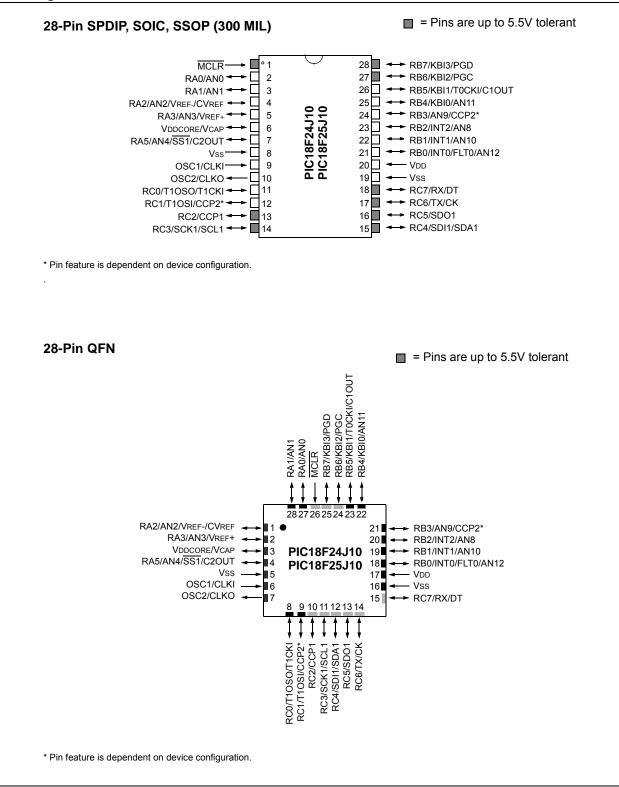

#### **Pin Diagrams**

| IABLE 1-1: DEVICE FEATURES              |                                                                                                                        |                                                                                                                        |                                                                                                                        |                                                                                                                        |  |  |  |  |  |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Features                                | PIC18F24J10                                                                                                            | PIC18F25J10                                                                                                            | PIC18F44J10                                                                                                            | PIC18F45J10                                                                                                            |  |  |  |  |  |

| Operating Frequency                     | DC – 40 MHz                                                                                                            |  |  |  |  |  |

| Program Memory (Bytes)                  | 16384                                                                                                                  | 32768                                                                                                                  | 16384                                                                                                                  | 32768                                                                                                                  |  |  |  |  |  |

| Program Memory<br>(Instructions)        | 8192                                                                                                                   | 16384                                                                                                                  | 8192                                                                                                                   | 16384                                                                                                                  |  |  |  |  |  |

| Data Memory (Bytes)                     | 1024                                                                                                                   | 1024                                                                                                                   | 1024                                                                                                                   | 1024                                                                                                                   |  |  |  |  |  |

| Interrupt Sources                       | 19                                                                                                                     | 19                                                                                                                     | 20                                                                                                                     | 20                                                                                                                     |  |  |  |  |  |

| I/O Ports                               | Ports A, B, C                                                                                                          | Ports A, B, C                                                                                                          | Ports A, B, C, D, E                                                                                                    | Ports A, B, C, D, E                                                                                                    |  |  |  |  |  |

| Timers                                  | 3                                                                                                                      | 3                                                                                                                      | 3                                                                                                                      | 3                                                                                                                      |  |  |  |  |  |

| Capture/Compare/PWM Modules             | 2                                                                                                                      | 2                                                                                                                      | 1                                                                                                                      | 1                                                                                                                      |  |  |  |  |  |

| Enhanced<br>Capture/Compare/PWM Modules | 0                                                                                                                      | 0                                                                                                                      | 1                                                                                                                      | 1                                                                                                                      |  |  |  |  |  |

| Serial Communications                   | MSSP,<br>Enhanced USART                                                                                                | MSSP,<br>Enhanced USART                                                                                                | MSSP,<br>Enhanced USART                                                                                                | MSSP,<br>Enhanced USART                                                                                                |  |  |  |  |  |

| Parallel Communications (PSP)           | No                                                                                                                     | No                                                                                                                     | Yes                                                                                                                    | Yes                                                                                                                    |  |  |  |  |  |

| 10-Bit Analog-to-Digital Module         | 10 Input Channels                                                                                                      | 10 Input Channels                                                                                                      | 13 Input Channels                                                                                                      | 13 Input Channels                                                                                                      |  |  |  |  |  |

| Resets (and Delays)                     | POR, BOR <sup>(1)</sup> ,<br>RESET Instruction,<br>Stack Full, Stack<br>Underflow (PWRT,<br><u>OS</u> T),<br>MCLR, WDT | POR, BOR <sup>(1)</sup> ,<br>RESET Instruction,<br>Stack Full, Stack<br>Underflow (PWRT,<br><u>OS</u> T),<br>MCLR, WDT | POR, BOR <sup>(1)</sup> ,<br>RESET Instruction,<br>Stack Full, Stack<br>Underflow (PWRT,<br><u>OS</u> T),<br>MCLR, WDT | POR, BOR <sup>(1)</sup> ,<br>RESET Instruction,<br>Stack Full, Stack<br>Underflow (PWRT,<br><u>OS</u> T),<br>MCLR, WDT |  |  |  |  |  |

| Programmable Brown-out Reset            | Yes                                                                                                                    | Yes                                                                                                                    | Yes                                                                                                                    | Yes                                                                                                                    |  |  |  |  |  |

| Instruction Set                         | 75 Instructions;<br>83 with Extended<br>Instruction Set enabled                                                        |  |  |  |  |  |

| Packages                                | 28-pin SPDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN                                                               | 28-pin SPDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN                                                               | 40-pin PDIP<br>44-pin QFN<br>44-pin TQFP                                                                               | 40-pin PDIP<br>44-pin QFN<br>44-pin TQFP                                                                               |  |  |  |  |  |

#### TABLE 1-1: DEVICE FEATURES

**Note 1:** BOR is not available in PIC18LF2XJ10/4XJ10 devices.

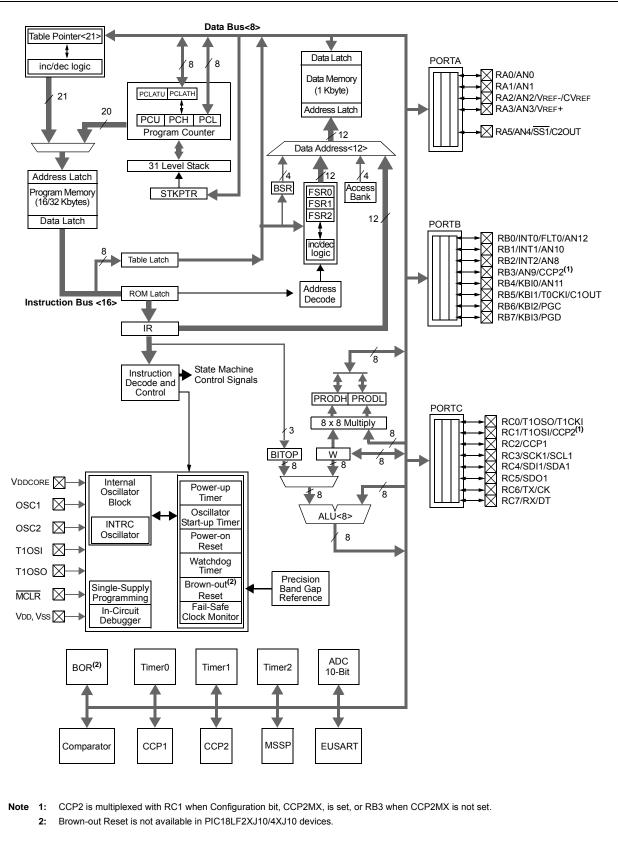

#### FIGURE 1-1: PIC18F24J10/25J10 (28-PIN) BLOCK DIAGRAM

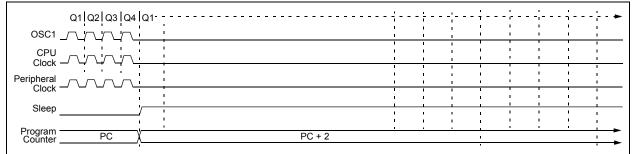

#### 4.3 Sleep Mode

The power-managed Sleep mode is identical to the legacy Sleep mode offered in all other PIC microcontrollers. It is entered by clearing the IDLEN bit (the default state on device Reset) and executing the SLEEP instruction. This shuts down the selected oscillator (Figure 4-4). All clock source status bits are cleared.

Entering the Sleep mode from any other mode does not require a clock switch. This is because no clocks are needed once the controller has entered Sleep. If the WDT is selected, the INTRC source will continue to operate. If the Timer1 oscillator is enabled, it will also continue to run.

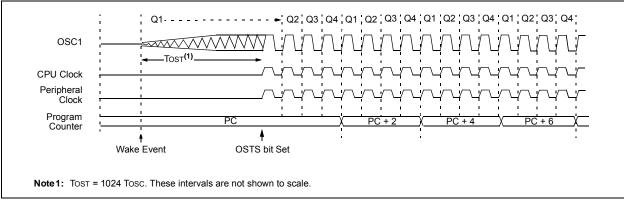

When a wake event occurs in Sleep mode (by interrupt, Reset or WDT time-out), the device will not be clocked until the clock source selected by the SCS<1:0> bits becomes ready (see Figure 4-5), or it will be clocked from the internal oscillator if either the Two-Speed Start-up or the Fail-Safe Clock Monitor are enabled (see **Section 21.0 "Special Features of the CPU"**). In either case, the OSTS bit is set when the primary clock is providing the device clocks. The IDLEN and SCS bits are not affected by the wake-up.

#### 4.4 Idle Modes

The Idle modes allow the controller's CPU to be selectively shut down while the peripherals continue to operate. Selecting a particular Idle mode allows users to further manage power consumption.

If the IDLEN bit is set to a '1' when a SLEEP instruction is executed, the peripherals will be clocked from the clock source selected using the SCS<1:0> bits; however, the CPU will not be clocked. The clock source status bits are not affected. Setting IDLEN and executing a SLEEP instruction provides a quick method of switching from a given Run mode to its corresponding Idle mode.

If the WDT is selected, the INTRC source will continue to operate. If the Timer1 oscillator is enabled, it will also continue to run.

Since the CPU is not executing instructions, the only exits from any of the Idle modes are by interrupt, WDT time-out or a Reset. When a wake event occurs, CPU execution is delayed by an interval of TCSD (parameter 38, Table 24-10) while it becomes ready to execute code. When the CPU begins executing code, it resumes with the same clock source for the current Idle mode. For example, when waking from RC\_IDLE mode, the internal oscillator block will clock the CPU and peripherals (in other words, RC\_RUN mode). The IDLEN and SCS bits are not affected by the wake-up.

While in any Idle mode or the Sleep mode, a WDT time-out will result in a WDT wake-up to the Run mode currently specified by the SCS<1:0> bits.

#### FIGURE 4-4: TRANSITION TIMING FOR ENTRY TO SLEEP MODE

| File Name | Bit 7                                                                                                                    | Bit 6               | Bit 5                 | Bit 4                 | Bit 3               | Bit 2               | Bit 1                 | Bit 0                 | Value on<br>POR, BOR | Details<br>on page: |

|-----------|--------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------|-----------------------|---------------------|---------------------|-----------------------|-----------------------|----------------------|---------------------|

| TMR0H     | Timer0 Regis                                                                                                             | ter High Byte       |                       |                       |                     |                     |                       |                       | 0000 0000            | 48, 117             |

| TMR0L     | Timer0 Regis                                                                                                             | ter Low Byte        | _                     | _                     |                     |                     |                       |                       | xxxx xxxx            | 48, 117             |

| T0CON     | TMR0ON                                                                                                                   | T08BIT              | TOCS                  | T0SE                  | PSA                 | T0PS2               | T0PS1                 | T0PS0                 | 1111 1111            | 48, 115             |

| OSCCON    | IDLEN                                                                                                                    | _                   | _                     | _                     | OSTS                | _                   | SCS1                  | SCS0                  | 0 q-00               | 32, 48              |

| WDTCON    | —                                                                                                                        | —                   |                       |                       | —                   | —                   | —                     | SWDTEN                | 0                    | 48, 242             |

| RCON      | IPEN                                                                                                                     | _                   | CM                    | RI                    | TO                  | PD                  | POR                   | BOR <sup>(1)</sup>    | 0-11 11q0            | 42, 46, 94          |

| TMR1H     | Timer1 Regis                                                                                                             | ster High Byte      |                       |                       |                     |                     |                       |                       | xxxx xxxx            | 48, 124             |

| TMR1L     | Timer1 Regis                                                                                                             | ster Low Byte       |                       |                       |                     |                     |                       |                       | xxxx xxxx            | 48, 124             |

| T1CON     | RD16                                                                                                                     | T1RUN               | T1CKPS1               | T1CKPS0               | T1OSCEN             | T1SYNC              | TMR1CS                | TMR10N                | 0000 0000            | 48, 119             |

| TMR2      | Timer2 Regis                                                                                                             | ster                |                       |                       | •                   |                     | •                     | •                     | 0000 0000            | 48, 126             |

| PR2       | Timer2 Perio                                                                                                             | d Register          |                       |                       |                     |                     |                       |                       | 1111 1111            | 48, 126             |

| T2CON     | _                                                                                                                        | T2OUTPS3            | T2OUTPS2              | T2OUTPS1              | T2OUTPS0            | TMR2ON              | T2CKPS1               | T2CKPS0               | -000 0000            | 48, 125             |

| SSP1BUF   | MSSP1 Rece                                                                                                               | eive Buffer/Tra     | nsmit Register        |                       |                     |                     |                       |                       | xxxx xxxx            | 48, 158             |

| SSP1ADD   | MSSP1 Address Register in I <sup>2</sup> C™ Slave mode. MSSP1 Baud Rate Reload Register in I <sup>2</sup> C Master mode. |                     |                       |                       |                     |                     |                       | 0000 0000             | 48, 159              |                     |

| SSP1STAT  | SMP                                                                                                                      | CKE                 | D/Ā                   | Р                     | S                   | R/W                 | UA                    | BF                    | 0000 0000            | 48, 150,<br>160     |

| SSP1CON1  | WCOL                                                                                                                     | SSPOV               | SSPEN                 | СКР                   | SSPM3               | SSPM2               | SSPM1                 | SSPM0                 | 0000 0000            | 48, 151,<br>161     |

| SSP1CON2  | GCEN                                                                                                                     | ACKSTAT             | ACKDT                 | ACKEN                 | RCEN                | PEN                 | RSEN                  | SEN                   | 0000 0000            | 48, 162             |

|           | GCEN                                                                                                                     | ACKSTAT             | ADMSK5 <sup>(3)</sup> | ADMSK4 <sup>(3)</sup> | ADMSK3(3)           | ADMSK2(3)           | ADMSK1(3)             | SEN                   | 0000 0000            | 48, 163             |

| ADRESH    | A/D Result R                                                                                                             | egister High B      | yte                   |                       |                     |                     |                       |                       | xxxx xxxx            | 48, 223             |

| ADRESL    | A/D Result R                                                                                                             | egister Low By      | /te                   |                       |                     |                     |                       |                       | xxxx xxxx            | 48, 223             |

| ADCON0    | ADCAL                                                                                                                    | _                   | CHS3                  | CHS2                  | CHS1                | CHS0                | GO/DONE               | ADON                  | 0-00 0000            | 48, 218             |

| ADCON1    | _                                                                                                                        | _                   | VCFG1                 | VCFG0                 | PCFG3               | PCFG2               | PCFG1                 | PCFG0                 | 00 0qqq              | 48, 218             |

| ADCON2    | ADFM                                                                                                                     | _                   | ACQT2                 | ACQT1                 | ACQT0               | ADCS2               | ADCS1                 | ADCS0                 | 0-00 0000            | 48, 218             |

| CCPR1H    | Capture/Com                                                                                                              | pare/PWM Re         | gister 1 High I       | Byte                  |                     |                     |                       |                       | xxxx xxxx            | 49, 128             |

| CCPR1L    | Capture/Com                                                                                                              | pare/PWM Re         | gister 1 Low E        | Byte                  |                     |                     |                       |                       | xxxx xxxx            | 49, 128             |

| CCP1CON   | P1M1 <sup>(2)</sup>                                                                                                      | P1M0 <sup>(2)</sup> | DC1B1                 | DC1B0                 | CCP1M3              | CCP1M2              | CCP1M1                | CCP1M0                | 0000 0000            | 49, 128,            |

| CCPR2H    | Capture/Com                                                                                                              | pare/PWM Re         | gister 2 High I       | Byte                  |                     |                     |                       |                       | xxxx xxxx            | 49, 128             |

| CCPR2L    | Capture/Compare/PWM Register 2 Low Byte                                                                                  |                     |                       |                       |                     |                     |                       |                       | xxxx xxxx            | 49, 128             |

| CCP2CON   | _                                                                                                                        | _                   | DC2B1                 | DC2B0                 | CCP2M3              | CCP2M2              | CCP2M1                | CCP2M0                | 00 0000              | 49, 128             |

| BAUDCON   | ABDOVF                                                                                                                   | RCIDL               | _                     | SCKP                  | BRG16               | _                   | WUE                   | ABDEN                 | 01-0 0-00            | 49, 196             |

| ECCP1DEL  | PRSEN                                                                                                                    | PDC6 <sup>(2)</sup> | PDC5 <sup>(2)</sup>   | PDC4 <sup>(2)</sup>   | PDC3 <sup>(2)</sup> | PDC2 <sup>(2)</sup> | PDC1 <sup>(2)</sup>   | PDC0 <sup>(2)</sup>   | 0000 0000            | 49, 144             |

| ECCP1AS   | ECCPASE                                                                                                                  | ECCPAS2             | ECCPAS1               | ECCPAS0               | PSSAC1              | PSSAC0              | PSSBD1 <sup>(2)</sup> | PSSBD0 <sup>(2)</sup> | 0000 0000            | 49, 146             |

| CVRCON    | CVREN                                                                                                                    | CVROE               | CVRR                  | CVRSS                 | CVR3                | CVR2                | CVR1                  | CVR0                  | 0000 0000            | 49, 232             |

| CMCON     | C2OUT                                                                                                                    | C10UT               | C2INV                 | C1INV                 | CIS                 | CM2                 | CM1                   | CM0                   | 0000 0111            | 49, 226             |

| TABLE 6-3: REGISTER FILE SUMMARY (PIC18F24J10/25J10/44J10/45J10) (CONT |

|------------------------------------------------------------------------|

|------------------------------------------------------------------------|

Legend: x = unknown, u = unchanged, – = unimplemented, q = value depends on condition Note

See Section 5.4 "Brown-out Reset (BOR) (PIC18F2XJ10/4XJ10 Devices Only)". 1:

2: These registers and/or bits are not implemented on 28-pin devices and are read as '0'. Reset values are shown for 40/44-pin devices; individual unimplemented bits should be interpreted as '-

Alternate names and definitions for these bits when the MSSP module is operating in  $I^2C^{TM}$  Slave mode. See Section 16.4.3.2 "Address Masking" for details. 3:

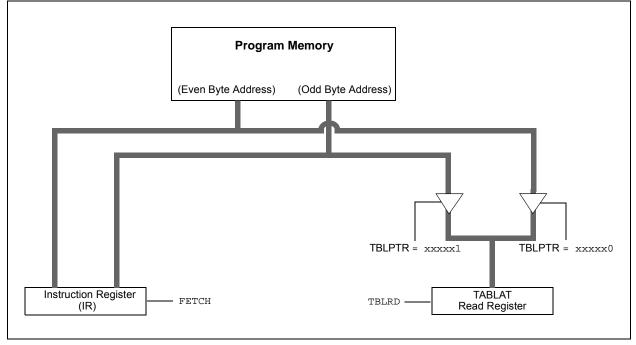

#### 7.3 Reading the Flash Program Memory

The TBLRD instruction is used to retrieve data from program memory and places it into data RAM. Table reads from program memory are performed one byte at a time.

TBLPTR points to a byte address in program space. Executing TBLRD places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next table read operation.

The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 7-4 shows the interface between the internal program memory and the TABLAT.

#### FIGURE 7-4: READS FROM FLASH PROGRAM MEMORY

#### EXAMPLE 7-1: READING A FLASH PROGRAM MEMORY WORD

|           | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>MOVLW | CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE_ADDR_LOW |   | Load TBLPTR with the base<br>address of the word |

|-----------|-------------------------------------------|--------------------------------------------------------------------------|---|--------------------------------------------------|

|           | MOVWF                                     | TBLPTRL                                                                  |   |                                                  |

| READ_WORD |                                           |                                                                          |   |                                                  |

|           | TBLRD*+                                   |                                                                          | ; | read into TABLAT and increment                   |

|           | MOVF                                      | TABLAT, W                                                                | ; | get data                                         |

|           | MOVWF                                     | WORD_EVEN                                                                |   |                                                  |

|           | TBLRD*+                                   |                                                                          | ; | read into TABLAT and increment                   |

|           | MOVF                                      | TABLAT, W                                                                | ; | get data                                         |

|           | MOVWF                                     | WORD_ODD                                                                 |   |                                                  |

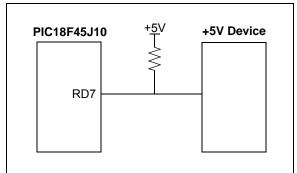

#### 10.1.3 INTERFACING TO A 5V SYSTEM

Though the VDDMAX of the PIC18F45J10 family is 3.6V, these devices are still capable of interfacing with 5V systems, even if the VIH of the target system is above 3.6V. This is accomplished by adding a pull-up resistor to the port pin (Figure 10-2), clearing the LAT bit for that pin and manipulating the corresponding TRIS bit (Figure 10-1) to either allow the line to be pulled high or to drive the pin low. Only port pins that are tolerant of voltages up to 5.5V can be used for this type of interface (refer to Section 10.1.2 "Input Pins and Voltage Considerations").

FIGURE 10-2: +5V SYSTEM HARDWARE INTERFACE

#### EXAMPLE 10-1: COMMUNICATING WITH THE +5V SYSTEM

| BCF | LATD, ' | 7 | ; | set up LAT register so    |

|-----|---------|---|---|---------------------------|

|     |         |   | ; | changing TRIS bit will    |

|     |         |   | ; | drive line low            |

| BCF | TRISD,  | 7 | ; | send a 0 to the 5V system |

| BCF | TRISD,  | 7 | ; | send a 1 to the 5V system |

|     |         |   |   |                           |

#### 10.2 PORTA, TRISA and LATA Registers

PORTA is a 5-bit wide, bidirectional port. The corresponding Data Direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it, will write to the port latch.

The Data Latch (LATA) register is also memory mapped. Read-modify-write operations on the LATA register read and write the latched output value for PORTA.

The other PORTA pins are multiplexed with analog inputs, the analog VREF+ and VREF- inputs and the comparator voltage reference output. The operation of pins RA<3:0> and RA5 as A/D converter inputs is selected by clearing or setting the control bits in the ADCON1 register (A/D Control Register 1).

Pins RA0 and RA3 may also be used as comparator inputs and RA5 may be used as the C2 comparator output by setting the appropriate bits in the CMCON register. To use RA<3:0> as digital inputs, it is also necessary to turn off the comparators.

| Note: | On a Power-on Reset, RA5 and RA<3:0>     |

|-------|------------------------------------------|

|       | are configured as analog inputs and read |

|       | as '0'.                                  |

All PORTA pins have TTL input levels and full CMOS output drivers.

The TRISA register controls the direction of the PORTA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

#### EXAMPLE 10-2: INITIALIZING PORTA

| CLRF  | PORTA  | ; | Initialize PORTA by   |

|-------|--------|---|-----------------------|

|       |        | ; | clearing output       |

|       |        | ; | data latches          |

| CLRF  | LATA   | ; | Alternate method      |

|       |        | ; | to clear output       |

|       |        | ; | data latches          |

| MOVLW | 07h    | ; | Configure A/D         |

| MOVWF | ADCON1 | ; | for digital inputs    |

| MOVWF | 07h    | ; | Configure comparators |

| MOVWF | CMCON  | ; | for digital input     |

| MOVLW | 0CFh   | ; | Value used to         |

|       |        | ; | initialize data       |

|       |        | ; | direction             |

| MOVWF | TRISA  | ; | Set RA<3:0> as inputs |

|       |        | ; | RA<5:4> as outputs    |

|       |        |   |                       |

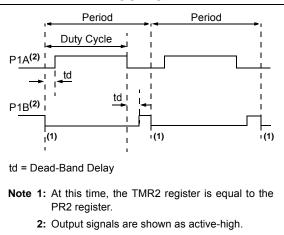

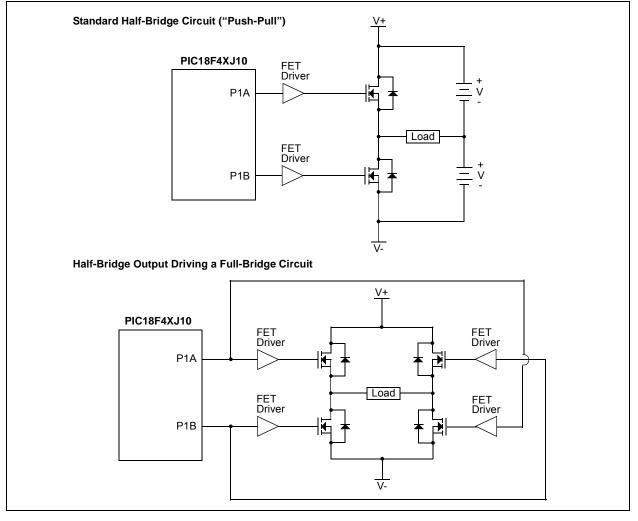

#### 15.4.4 HALF-BRIDGE MODE

In the Half-Bridge Output mode, two pins are used as outputs to drive push-pull loads. The PWM output signal is output on the P1A pin, while the complementary PWM output signal is output on the P1B pin (Figure 15-4). This mode can be used for half-bridge applications, as shown in Figure 15-5, or for full-bridge applications where four power switches are being modulated with two PWM signals.

In Half-Bridge Output mode, the programmable deadband delay can be used to prevent shoot-through current in half-bridge power devices. The value of bits, PDC<6:0>, sets the number of instruction cycles before the output is driven active. If the value is greater than the duty cycle, the corresponding output remains inactive during the entire cycle. See **Section 15.4.6 "Programmable Dead-Band Delay"** for more details of the dead-band delay operations.

Since the P1A and P1B outputs are multiplexed with the PORTC<2> and PORTD<5> data latches, the TRISC<2> and TRISD<5> bits must be cleared to configure P1A and P1B as outputs.

#### FIGURE 15-4: HALF-BRIDGE PWM OUTPUT

#### FIGURE 15-5: EXAMPLES OF HALF-BRIDGE OUTPUT MODE APPLICATIONS

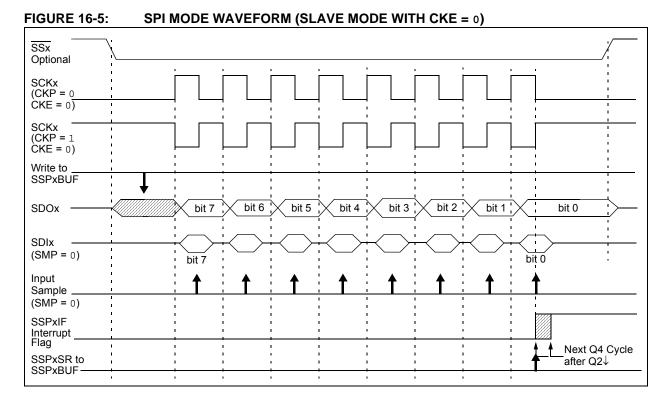

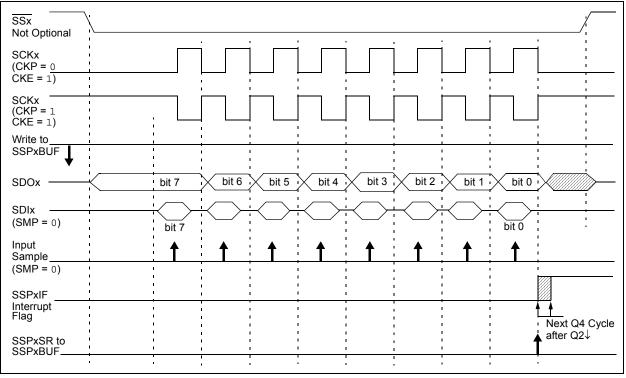

#### FIGURE 16-6: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

#### 16.4.10 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPxBUF register. This action will set the Buffer Full flag bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDAx pin after the falling edge of SCLx is asserted (see data hold time specification parameter 106). SCLx is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCLx is released high (see data setup time specification parameter 107). When the SCLx pin is released high, it is held that way for TBRG. The data on the SDAx pin must remain stable for that duration and some hold time after the next falling edge of SCLx. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDAx. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurred, or if data was received properly. The status of ACK is written into the ACKDT bit on the falling edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared; if not, the bit is set. After the ninth clock, the SSPxIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPxBUF, leaving SCLx low and SDAx unchanged (Figure 16-21).

After the write to the SSPxBUF, each bit of the address will be shifted out on the falling edge of SCLx until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will deassert the SDAx pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDAx pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT status bit (SSPxCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPxIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPxBUF takes place, holding SCLx low and allowing SDAx to float.

#### 16.4.10.1 BF Status Flag

In Transmit mode, the BF bit (SSPxSTAT<0>) is set when the CPU writes to SSPxBUF and is cleared when all 8 bits are shifted out.

#### 16.4.10.2 WCOL Status Flag

If the user writes to the SSPxBUF when a transmit is already in progress (i.e., SSPxSR is still shifting out a data byte), the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur) after 2 TcY after the SSPxBUF write. If SSPxBUF is rewritten within 2 TcY, the WCOL bit is set and SSPxBUF is updated. This may result in a corrupted transfer. The user should verify that the WCOL is clear after each write to SSPxBUF to ensure the transfer is correct. In all cases, WCOL must be cleared in software.

#### 16.4.10.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit (SSPxCON2<6>) is cleared when the slave has sent an Acknowledge  $(\overline{ACK} = 0)$  and is set when the slave does not Acknowledge  $(\overline{ACK} = 1)$ . A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

#### 16.4.11 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (SSPxCON2<3>).

| Note: | The MSSP module must be in an Idle state   |

|-------|--------------------------------------------|

|       | before the RCEN bit is set or the RCEN bit |

|       | will be disregarded.                       |

The Baud Rate Generator begins counting, and on each rollover, the state of the SCLx pin changes (high-to-low/low-to-high) and data is shifted into the SSPxSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPxSR are loaded into the SSPxBUF, the BF flag bit is set, the SSPxIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCLx low. The MSSP is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable bit, ACKEN (SSPxCON2<4>).

#### 16.4.11.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPxBUF from SSPxSR. It is cleared when the SSPxBUF register is read.

#### 16.4.11.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPxSR and the BF flag bit is already set from a previous reception.

#### 16.4.11.3 WCOL Status Flag

If the user writes the SSPxBUF when a receive is already in progress (i.e., SSPxSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

| R/W-0        | U-0                                                                                                                                                                                                                                                                                                                | R/W-0            | R/W-0         | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------|-------------------|------------------|-----------------|-------|

| ADFM         | —                                                                                                                                                                                                                                                                                                                  | ACQT2            | ACQT1         | ACQT0             | ADCS2            | ADCS1           | ADCS0 |

| bit 7        |                                                                                                                                                                                                                                                                                                                    | · · ·            |               |                   |                  | •               | bit C |

| Legend:      |                                                                                                                                                                                                                                                                                                                    |                  |               |                   |                  |                 |       |

| R = Readal   | ble bit                                                                                                                                                                                                                                                                                                            | W = Writable b   | it            | U = Unimplem      | nented bit, read | d as '0'        |       |

| -n = Value a | at POR                                                                                                                                                                                                                                                                                                             | '1' = Bit is set |               | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

| bit 7        | <b>ADFM:</b> A/D R<br>1 = Right justi<br>0 = Left justifie                                                                                                                                                                                                                                                         |                  | elect bit     |                   |                  |                 |       |

| bit 6        | Unimplement                                                                                                                                                                                                                                                                                                        | ted: Read as '0  | ,             |                   |                  |                 |       |

| bit 5-3      | 111 = 20 TAD<br>110 = 16 TAD<br>101 = 12 TAD<br>100 = 8 TAD<br>011 = 6 TAD<br>010 = 4 TAD<br>001 = 2 TAD                                                                                                                                                                                                           |                  | Time Select I | pits              |                  |                 |       |

| bit 2-0      | 000 = 0 TAD <sup>(1)</sup><br>ADCS<2:0>: A/D Conversion Clock Select bits<br>111 = FRC (clock derived from A/D RC oscillator) <sup>(1)</sup><br>110 = Fosc/64<br>101 = Fosc/16<br>100 = Fosc/4<br>011 = FRC (clock derived from A/D RC oscillator) <sup>(1)</sup><br>010 = Fosc/32<br>001 = Fosc/8<br>000 = Fosc/2 |                  |               |                   |                  |                 |       |

#### REGISTER 18-3: ADCON2: A/D CONTROL REGISTER 2

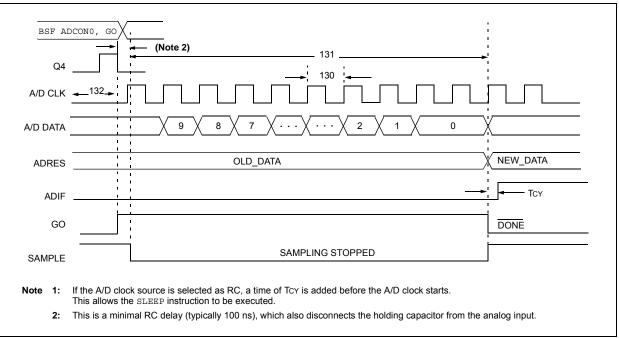

**Note 1:** If the A/D FRC clock source is selected, a delay of one TcY (instruction cycle) is added before the A/D clock starts. This allows the SLEEP instruction to be executed before starting a conversion.

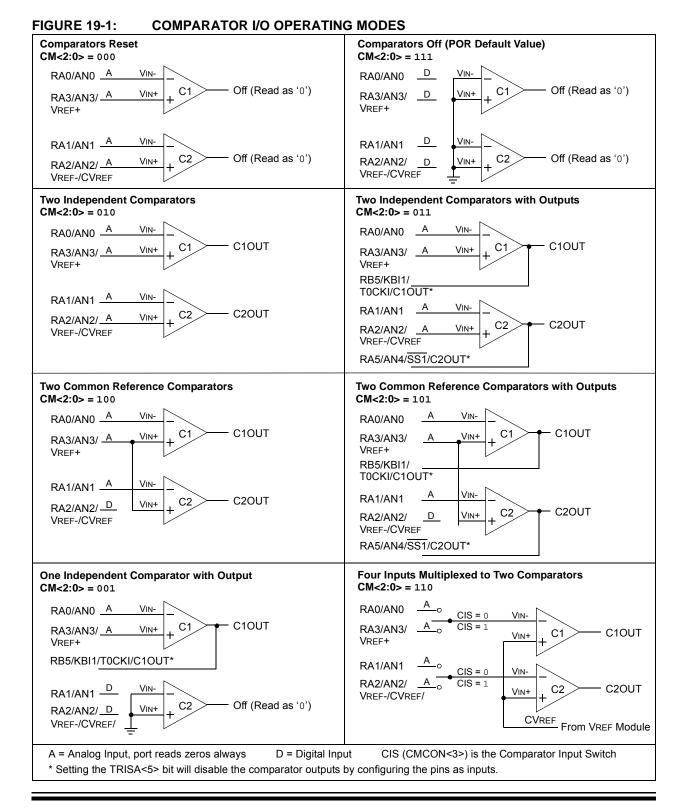

#### 19.1 Comparator Configuration

There are eight modes of operation for the comparators, shown in Figure 19-1. Bits, CM<2:0> of the CMCON register, are used to select these modes. The TRISA register controls the data direction of the comparator pins for each mode. If the Comparator mode is changed, the comparator output level may not be valid for the specified mode change delay shown in **Section 24.0 "Electrical Characteristics"**.

Note: Comparator interrupts should be disabled during a Comparator mode change; otherwise, a false interrupt may occur.

#### REGISTER 21-4: CONFIG2H: CONFIGURATION REGISTER 2 HIGH (BYTE ADDRESS 300003h)

|                                                                                                                                                 |                      |                  |               |              | -                |          | -      |

|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------|---------------|--------------|------------------|----------|--------|

| U-0                                                                                                                                             | U-0                  | U-0              | U-0           | R/WO-1       | R/WO-1           | R/WO-1   | R/WO-1 |

| _(1)                                                                                                                                            | (1)                  | (1)              | (1)           | WDTPS3       | WDTPS2           | WDTPS1   | WDTPS0 |

| bit 7                                                                                                                                           |                      |                  |               |              |                  | •        | bit 0  |

| Legend:                                                                                                                                         |                      |                  |               |              |                  |          |        |

| R = Readat                                                                                                                                      | ole bit              | WO = Write C     | nce bit       | U = Unimplem | nented bit, read | l as '0' |        |

| R = Readable bitWO = Write Once bitU = Unimplemented bit, read as '0'-n = Value when device is unprogrammed'1' = Bit is set'0' = Bit is cleared |                      |                  |               |              |                  |          |        |

| bit 7-4                                                                                                                                         | Unimplemer           | nted: Read as ': | լ՝ <b>(1)</b> |              |                  |          |        |

| bit 3-0                                                                                                                                         | WDTPS<3:0            | >: Watchdog Ti   | mer Postscale | Select bits  |                  |          |        |

|                                                                                                                                                 | 1111 <b>= 1:32</b> , | 768              |               |              |                  |          |        |

|                                                                                                                                                 | 1110 <b>= 1:16</b> , | 384              |               |              |                  |          |        |

|                                                                                                                                                 | 1101 <b>= 1:8,1</b>  | 92               |               |              |                  |          |        |

|                                                                                                                                                 | 1100 <b>= 1:4,0</b>  | 96               |               |              |                  |          |        |

|                                                                                                                                                 | 1011 <b>= 1:2,0</b>  | -                |               |              |                  |          |        |

|                                                                                                                                                 | 1010 = 1:1,0         |                  |               |              |                  |          |        |

|                                                                                                                                                 | 1001 = 1:512         |                  |               |              |                  |          |        |

|                                                                                                                                                 | 1000 = 1:256         | -                |               |              |                  |          |        |

|                                                                                                                                                 | 0111 = 1:128         |                  |               |              |                  |          |        |

|                                                                                                                                                 | 0110 <b>= 1:64</b>   |                  |               |              |                  |          |        |

|                                                                                                                                                 | 0101 = 1:32          |                  |               |              |                  |          |        |

|                                                                                                                                                 | 0100 = 1:16          |                  |               |              |                  |          |        |

|                                                                                                                                                 | 0011 = 1:8           |                  |               |              |                  |          |        |

|                                                                                                                                                 | 0010 = 1:4           |                  |               |              |                  |          |        |

|                                                                                                                                                 | 0001 = 1:2           |                  |               |              |                  |          |        |

|                                                                                                                                                 | 0000 = 1:1           |                  |               |              |                  |          |        |

|                                                                                                                                                 |                      |                  |               |              |                  |          |        |

**Note 1:** The value of these bits in program memory should always be '1'. This ensures that the location is executed as a NOP if it is accidentally executed.

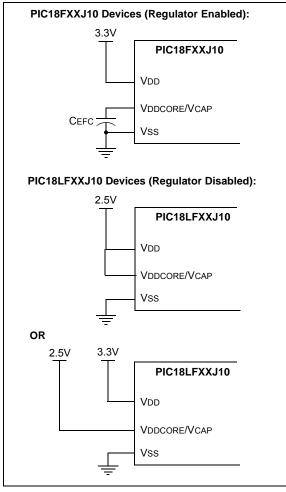

#### 21.3 On-Chip Voltage Regulator

| Note: | The on-chip voltage regulator is only      |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|

|       | available in parts designated with an "F", |  |  |  |  |  |  |  |

|       | such as PIC18F45J10.                       |  |  |  |  |  |  |  |

In parts designated "LF", the microcontroller core is powered from an external source that is separate from VDD. This voltage is supplied on the VDDCORE pin.

In "F" devices, a low-ESR capacitor must be connected to the VDDCORE/VCAP pin for proper device operation. In parts designated with an "LF" part number (i.e., PIC18**LF**45J10), power to the core must be supplied on VDDCORE/VCAP. It is always good design practice to have sufficient capacitance on all supply pins. Examples are shown in Figure 21-2.

Note: In parts designated with an "LF", such as PIC18LF45J10, VDDCORE must never exceed VDD.

The specifications for core voltage and capacitance are listed inTable 24-4 of **Section 24.0** "**Electrical Characteristics**".

### FIGURE 21-2: CONNECTIONS FOR THE ON-CHIP REGULATOR

#### 21.3.1 ON-CHIP REGULATOR AND BOR

When the on-chip regulator is enabled, PIC18F45J10 family devices also have a simple brown-out capability. If the voltage supplied to the regulator is inadequate to maintain a regulated level, the regulator Reset circuitry will generate a BOR Reset. This event is captured by the BOR flag bit (RCON<0>).

The operation of the BOR is described in more detail in Section 5.4 "Brown-out Reset (BOR) (PIC18F2XJ10/4XJ10 Devices Only)" and Section 5.4.1 "Detecting BOR". The brown-out voltage levels are specific in Section 23.1 "DC Characteristics: Supply Voltage".

#### 21.3.2 POWER-UP REQUIREMENTS

The on-chip regulator is designed to meet the power-up requirements for the device. While powering up, VDDCORE must never exceed VDD by 0.3 volts.

#### 21.5 Fail-Safe Clock Monitor

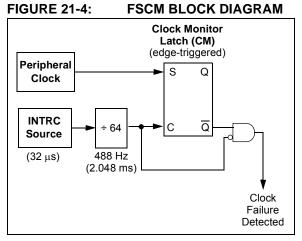

The Fail-Safe Clock Monitor (FSCM) allows the microcontroller to continue operation in the event of an external oscillator failure by automatically switching the device clock to the internal oscillator block. The FSCM function is enabled by setting the FCMEN Configuration bit.

When FSCM is enabled, the INTRC oscillator runs at all times to monitor clocks to peripherals and provide a backup clock in the event of a clock failure. Clock monitoring (shown in Figure 21-4) is accomplished by creating a sample clock signal which is the INTRC output divided by 64. This allows ample time between FSCM sample clocks for a peripheral clock edge to occur. The peripheral device clock and the sample clock are presented as inputs to the Clock Monitor latch (CM). The CM is set on the falling edge of the device clock source but cleared on the rising edge of the sample clock.

Clock failure is tested for on the falling edge of the sample clock. If a sample clock falling edge occurs while CM is still set, a clock failure has been detected (Figure 21-5). This causes the following:

- the FSCM generates an oscillator fail interrupt by setting bit, OSCFIF (PIR2<7>);

- the device clock source is switched to the internal oscillator block (OSCCON is not updated to show the current clock source – this is the fail-safe condition); and

- the WDT is reset.

During switchover, the postscaler frequency from the internal oscillator block may not be sufficiently stable for timing sensitive applications. In these cases, it may be desirable to select another clock configuration and enter an alternate power-managed mode. This can be done to attempt a partial recovery or execute a controlled shutdown. See Section 4.1.4 "Multiple Sleep Commands" and Section 21.4.1 "Special Considerations for Using Two-Speed Start-up" for more details. To use a higher clock speed on wake-up, the INTOSC or postscaler clock sources can be selected to provide a higher clock speed by setting bits IRCF<2:0> immediately after Reset. For wake-ups from Sleep, the INTOSC or postscaler clock sources can be selected by setting IRCF<2:0> prior to entering Sleep mode.

The FSCM will detect failures of the primary or secondary clock sources only. If the internal oscillator block fails, no failure would be detected, nor would any action be possible.

#### 21.5.1 FSCM AND THE WATCHDOG TIMER

Both the FSCM and the WDT are clocked by the INTRC oscillator. Since the WDT operates with a separate divider and counter, disabling the WDT has no effect on the operation of the INTRC oscillator when the FSCM is enabled.

As already noted, the clock source is switched to the INTRC clock when a clock failure is detected; this may mean a substantial change in the speed of code execution. If the WDT is enabled with a small prescale value, a decrease in clock speed allows a WDT time-out to occur and a subsequent device Reset. For this reason, Fail-Safe Clock Monitor events also reset the WDT and postscaler, allowing it to start timing from when execution speed was changed and decreasing the likelihood of an erroneous time-out.

#### 21.5.2 EXITING FAIL-SAFE OPERATION

The fail-safe condition is terminated by either a device Reset or by entering a power-managed mode. On Reset, the controller starts the primary clock source specified in Configuration Register 2H (with the OST oscillator, start-up delays if running in HS mode). The INTRC oscillator provides the device clock until the primary clock source becomes ready (similar to a Two-Speed Start-up). The clock source is then switched to the primary clock (indicated by the OSTS bit in the OSCCON register becoming set). The Fail-Safe Clock Monitor then resumes monitoring the peripheral clock.

The primary clock source may never become ready during start-up. In this case, operation is clocked by the INTRC oscillator. The OSCCON register will remain in its Reset state until a power-managed mode is entered.

<sup>© 2009</sup> Microchip Technology Inc.

| Mnemonic,<br>Operands |         | Description                     | Cycles | 16-Bit Instruction Word |      |      |      | Status          | Natas |

|-----------------------|---------|---------------------------------|--------|-------------------------|------|------|------|-----------------|-------|

|                       |         | Description                     | Cycles | MSb                     |      |      | LSb  | Affected        | Notes |

| LITERAL (             | OPERA   | TIONS                           |        |                         |      |      |      |                 |       |

| ADDLW                 | k       | Add Literal and WREG            | 1      | 0000                    | 1111 | kkkk | kkkk | C, DC, Z, OV, N |       |

| ANDLW                 | k       | AND Literal with WREG           | 1      | 0000                    | 1011 | kkkk | kkkk | Z, N            |       |

| IORLW                 | k       | Inclusive OR Literal with WREG  | 1      | 0000                    | 1001 | kkkk | kkkk | Z, N            |       |

| LFSR                  | f, k    | Move Literal (12-bit) 2nd Word  | 2      | 1110                    | 1110 | 00ff | kkkk | None            |       |

|                       |         | to FSR(f) 1st Word              |        | 1111                    | 0000 | kkkk | kkkk |                 |       |

| MOVLB                 | k       | Move Literal to BSR<3:0>        | 1      | 0000                    | 0001 | 0000 | kkkk | None            |       |

| MOVLW                 | k       | Move Literal to WREG            | 1      | 0000                    | 1110 | kkkk | kkkk | None            |       |

| MULLW                 | k       | Multiply Literal with WREG      | 1      | 0000                    | 1101 | kkkk | kkkk | None            |       |

| RETLW                 | k       | Return with Literal in WREG     | 2      | 0000                    | 1100 | kkkk | kkkk | None            |       |

| SUBLW                 | k       | Subtract WREG from Literal      | 1      | 0000                    | 1000 | kkkk | kkkk | C, DC, Z, OV, N |       |

| XORLW                 | k       | Exclusive OR Literal with WREG  | 1      | 0000                    | 1010 | kkkk | kkkk | Z, N            |       |

| DATA MEN              | /IORY ← | > PROGRAM MEMORY OPERATIO       | NS     |                         |      |      |      |                 |       |

| TBLRD*                |         | Table Read                      | 2      | 0000                    | 0000 | 0000 | 1000 | None            |       |

| TBLRD*+               |         | Table Read with Post-Increment  |        | 0000                    | 0000 | 0000 | 1001 | None            |       |

| TBLRD*-               |         | Table Read with Post-Decrement  |        | 0000                    | 0000 | 0000 | 1010 | None            |       |

| TBLRD+*               |         | Table Read with Pre-Increment   |        | 0000                    | 0000 | 0000 | 1011 | None            |       |

| TBLWT*                |         | Table Write                     | 2      | 0000                    | 0000 | 0000 | 1100 | None            |       |

| TBLWT*+               |         | Table Write with Post-Increment |        | 0000                    | 0000 | 0000 | 1101 | None            |       |

| TBLWT*-               |         | Table Write with Post-Decrement |        | 0000                    | 0000 | 0000 | 1110 | None            |       |

| TBLWT+*               |         | Table Write with Pre-Increment  |        | 0000                    | 0000 | 0000 | 1111 | None            |       |

#### TABLE 22-2: PIC18FXXXX INSTRUCTION SET (CONTINUED)

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

**3:** If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

| TBLRD             |                 | Table Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |      |                          |    |                                           |  |

|-------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|--------------------------|----|-------------------------------------------|--|

| Synta             | ax:             | TBLRD ( *; *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | (*;*+;*-;+*) |      |                          |    |                                           |  |

| Oper              | ands:           | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |      |                          |    |                                           |  |

| Operation:        |                 | if TBLRD *,<br>(Prog Mem (TBLPTR)) $\rightarrow$ TABLAT,<br>TBLPTR – No Change;<br>if TBLRD *+,<br>(Prog Mem (TBLPTR)) $\rightarrow$ TABLAT,<br>(TBLPTR) + 1 $\rightarrow$ TBLPTR;<br>if TBLRD *-,<br>(Prog Mem (TBLPTR)) $\rightarrow$ TABLAT,<br>(TBLPTR) – 1 $\rightarrow$ TBLPTR;<br>if TBLRD +*,<br>(TBLPTR) + 1 $\rightarrow$ TBLPTR,<br>(Prog Mem (TBLPTR)) $\rightarrow$ TABLAT                                                                                                                        |              |      |                          |    |                                           |  |

| Statu             | s Affected:     | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |      |                          |    |                                           |  |

| Encoding:         |                 | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 000          | 0    | 0000                     |    | 10nn<br>nn=0 *<br>=1 *+<br>=2 *-<br>=3 +* |  |

| Description:      |                 | of Program Memory (P.M.). To address the<br>program memory, a pointer called Table<br>Pointer (TBLPTR) is used.<br>The TBLPTR (a 21-bit pointer) points to<br>each byte in the program memory. TBLPTR<br>has a 2-Mbyte address range.<br>TBLPTR[0] = 0: Least Significant Byte<br>of Program Memory<br>Word<br>TBLPTR[0] = 1: Most Significant Byte<br>of Program Memory<br>Word<br>The TBLRD instruction can modify the value<br>of TBLPTR as follows:<br>• no change<br>• post-increment<br>• post-decrement |              |      |                          |    |                                           |  |

|                   |                 | • pre-increment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |      |                          |    |                                           |  |

| Words:<br>Cycles: |                 | 1 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |      |                          |    |                                           |  |

| Q Cycle Activity: |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |      |                          |    |                                           |  |

|                   | Q1              | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |      | Q3                       |    | Q4                                        |  |

|                   | Decode          | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | n            | 0.00 | No                       |    | No                                        |  |

|                   | No<br>operation | operatic<br>No operat<br>(Read Prog<br>Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ion<br>gram  |      | eration<br>No<br>eration | No | operation<br>operation<br>ite TABLAT)     |  |

#### TBLRD Table Read (Continued)

| Example 1:                                                 | TBLRD *+               | ;           |                |

|------------------------------------------------------------|------------------------|-------------|----------------|

| Before Instruction                                         | on                     |             |                |

| TABLAT                                                     |                        | =           | 55h            |

|                                                            | (00A356h)              | =           | 00A356h<br>34h |

| After Instruction                                          | · /                    | -           | 3411           |

| TABLAT                                                     |                        | =           | 34h            |

| TBLPTR                                                     |                        | =           | 00A357h        |

| Example 2:                                                 |                        |             |                |

| Example 2.                                                 | TBLRD +*               | ;           |                |

| Before Instruction                                         | IDDIND .               | ;           |                |

| Before Instruction                                         | IDDIND .               | ;<br>=      | AAh            |

| Before Instruction<br>TABLAT<br>TBLPTR                     | on                     | =           | 01A357h        |

| Before Instruction<br>TABLAT<br>TBLPTR<br>MEMORY           | (01A357h)              | =           |                |

| Before Instruction<br>TABLAT<br>TBLPTR<br>MEMORY           | (01A357h)<br>(01A358h) | =<br>=<br>= | 01A357h<br>12h |

| Before Instruction<br>TABLAT<br>TBLPTR<br>MEMORY<br>MEMORY | (01A357h)<br>(01A358h) | =<br>=<br>= | 01A357h<br>12h |

| Param<br>No. | Symbol        | Characteristic                                    | Min        | Тур      | Max              | Units    | Conditions                                                  |

|--------------|---------------|---------------------------------------------------|------------|----------|------------------|----------|-------------------------------------------------------------|

| A01          | NR            | Resolution                                        | _          |          | 10               | bit      | $\Delta \text{VREF} \geq 3.0 \text{V}$                      |

| A03          | EIL           | Integral Linearity Error                          | —          | _        | <±1              | LSb      | $\Delta VREF \ge 3.0V$                                      |

| A04          | Edl           | Differential Linearity Error                      | —          | _        | <±1              | LSb      | $\Delta VREF \ge 3.0V$                                      |

| A06          | EOFF          | Offset Error                                      | _          | _        | <±3              | LSb      | $\Delta VREF \ge 3.0V$                                      |

| A07          | Egn           | Gain Error                                        | _          | _        | <±3              | LSb      | $\Delta VREF \ge 3.0V$                                      |

| A10          | _             | Monotonicity                                      | G          | uarantee | d <sup>(1)</sup> | _        | $VSS \le VAIN \le VREF$                                     |

| A20          | $\Delta VREF$ | Reference Voltage Range<br>(VREFH – VREFL)        | 1.8<br>3   | _        |                  | V<br>V   | $\begin{array}{l} VDD < 3.0V \\ VDD \geq 3.0V \end{array}$  |

| A21          | Vrefh         | Reference Voltage High                            | Vss        | _        | Vrefh            | V        |                                                             |

| A22          | Vrefl         | Reference Voltage Low                             | Vss – 0.3V | _        | Vdd - 3.0V       | V        |                                                             |

| A25          | VAIN          | Analog Input Voltage                              | VREFL      | _        | VREFH            | V        |                                                             |

| A30          | ZAIN          | Recommended Impedance of<br>Analog Voltage Source | —          |          | 2.2              | kΩ       |                                                             |