Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 32                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                 |

| Data Converters            | A/D 13x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f45j10t-e-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

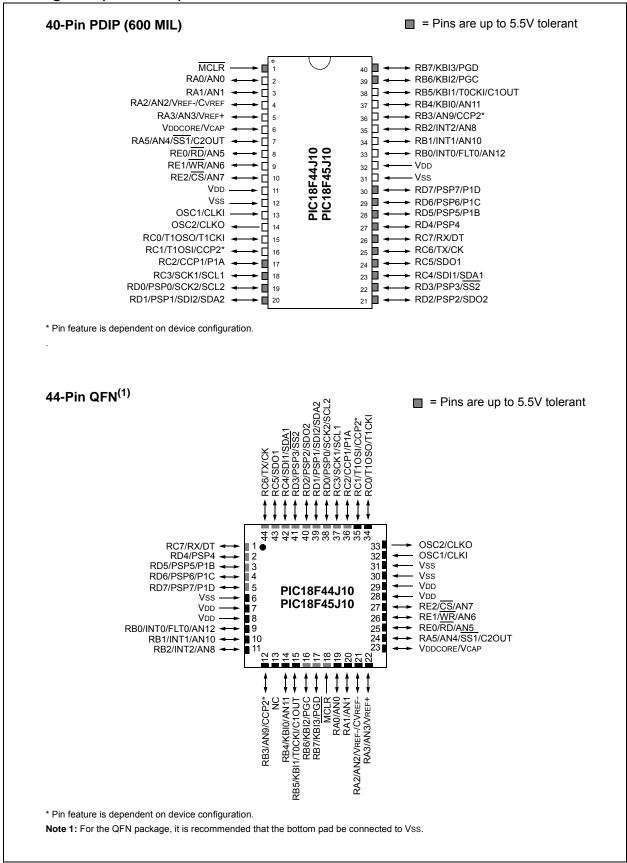

#### **Pin Diagrams (Continued)**

# 4.0 POWER-MANAGED MODES

The PIC18F45J10 family devices provide the ability to manage power consumption by simply managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. For the sake of managing power in an application, there are three primary modes of operation:

- Run mode

- Idle mode

- · Sleep mode

These modes define which portions of the device are clocked and at what speed. The Run and Idle modes may use any of the three available clock sources (primary, secondary or internal oscillator block); the Sleep mode does not use a clock source.

The power-managed modes include several power-saving features offered on previous PIC<sup>®</sup> microcontrollers. One is the clock switching feature, offered in other PIC18 devices, allowing the controller to use the Timer1 oscillator in place of the primary oscillator. Also included is the Sleep mode, offered by all PIC microcontrollers, where all device clocks are stopped.

### 4.1 Selecting Power-Managed Modes

Selecting a power-managed mode requires two decisions: if the CPU is to be clocked or not and which clock source is to be used. The IDLEN bit (OSCCON<7>) controls CPU clocking, while the SCS<1:0> bits (OSCCON<1:0>) select the clock source. The individual modes, bit settings, clock sources and affected modules are summarized in Table 4-1.

## 4.1.1 CLOCK SOURCES

The SCS<1:0> bits allow the selection of one of three clock sources for power-managed modes. They are:

- the primary clock, as defined by the FOSC<1:0> Configuration bits

- the secondary clock (Timer1 oscillator)

- · the internal oscillator

#### 4.1.2 ENTERING POWER-MANAGED MODES

Switching from one power-managed mode to another begins by loading the OSCCON register. The SCS<1:0> bits select the clock source and determine which Run or Idle mode is to be used. Changing these bits causes an immediate switch to the new clock source, assuming that it is running. The switch may also be subject to clock transition delays. These are discussed in **Section 4.1.3 "Clock Transitions and Status Indicators"** and subsequent sections.

Entry to the power-managed Idle or Sleep modes is triggered by the execution of a SLEEP instruction. The actual mode that results depends on the status of the IDLEN bit.

Depending on the current mode and the mode being switched to, a change to a power-managed mode does not always require setting all of these bits. Many transitions may be done by changing the oscillator select bits, or changing the IDLEN bit, prior to issuing a SLEEP instruction. If the IDLEN bit is already configured correctly, it may only be necessary to perform a SLEEP instruction to switch to the desired mode.

| Mada     | oso                     | OSCCON bits |                 | e Clocking | Ausilable Clask and Ossillator Source                             |

|----------|-------------------------|-------------|-----------------|------------|-------------------------------------------------------------------|

| Mode     | IDLEN<7> <sup>(1)</sup> | SCS<1:0>    | CPU Peripherals |            | Available Clock and Oscillator Source                             |

| Sleep    | 0                       | N/A         | Off             | Off        | None – All clocks are disabled                                    |

| PRI_RUN  | N/A                     | 10          | Clocked         | Clocked    | Primary – HS, EC;<br>this is the normal full-power execution mode |

| SEC_RUN  | N/A                     | 01          | Clocked         | Clocked    | Secondary – Timer1 Oscillator                                     |

| RC_RUN   | N/A                     | 11          | Clocked         | Clocked    | Internal Oscillator                                               |

| PRI_IDLE | 1                       | 10          | Off             | Clocked    | Primary – HS, EC                                                  |

| SEC_IDLE | 1                       | 01          | Off             | Clocked    | Secondary – Timer1 Oscillator                                     |

| RC_IDLE  | 1                       | 11          | Off             | Clocked    | Internal Oscillator                                               |

TABLE 4-1: POWER-MANAGED MODES

**Note 1:** IDLEN reflects its value when the **SLEEP** instruction is executed.

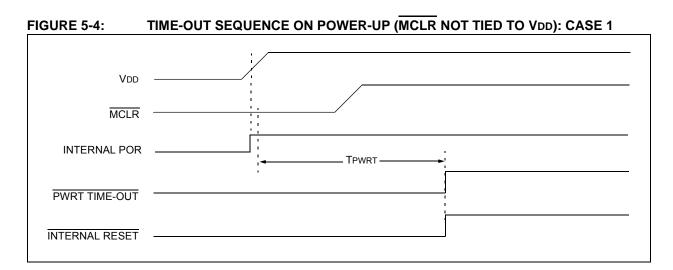

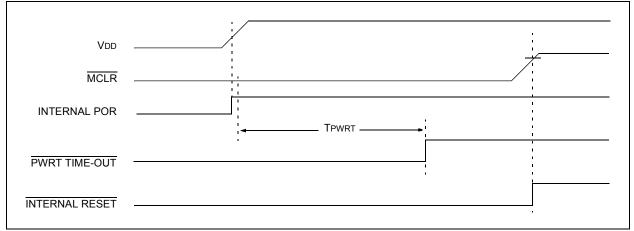

## FIGURE 5-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

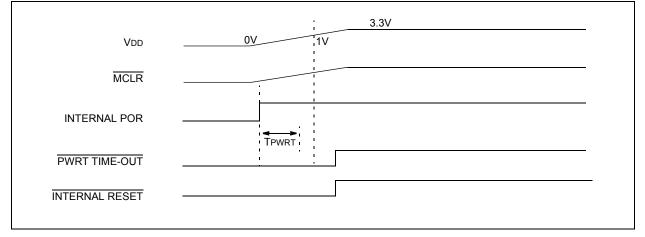

#### FIGURE 5-6: SLOW RISE TIME (MCLR TIED TO VDD, VDD RISE > TPWRT)

## 6.1.4.2 Return Stack Pointer (STKPTR)

The STKPTR register (Register 6-1) contains the Stack Pointer value, the STKFUL (Stack Overflow) status bit and the STKUNF (Stack Underflow) status bits. The value of the Stack Pointer can be 0 through 31. The Stack Pointer increments before values are pushed onto the stack and decrements after values are popped off the stack. On Reset, the Stack Pointer value will be zero. The user may read and write the Stack Pointer value. This feature can be used by a Real-Time Operating System (RTOS) for return stack maintenance.

After the PC is pushed onto the stack 31 times (without popping any values off the stack), the STKFUL bit is set. The STKFUL bit is cleared by software or by a POR.

The action that takes place when the stack becomes full depends on the state of the STVREN (Stack Overflow Reset Enable) Configuration bit. (Refer to **Section 21.1 "Configuration Bits**" for a description of the device Configuration bits.) If STVREN is set (default), the 31st push will push the (PC + 2) value onto the stack, set the STKFUL bit and reset the device. The STKFUL bit will remain set and the Stack Pointer will be set to zero.

If STVREN is cleared, the STKFUL bit will be set on the 31st push and the Stack Pointer will increment to 31. Any additional pushes will not overwrite the 31st push and the STKPTR will remain at 31.

When the stack has been popped enough times to unload the stack, the next pop will return a value of zero to the PC and sets the STKUNF bit, while the Stack Pointer remains at zero. The STKUNF bit will remain set until cleared by software or until a POR occurs.

| Note: | Returning a value of zero to the PC on an<br>underflow has the effect of vectoring the<br>program to the Reset vector, where the<br>stack conditions can be verified and<br>appropriate actions can be taken. This is |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | not the same as a Reset, as the contents of the SFRs are not affected.                                                                                                                                                |

#### 6.1.4.3 PUSH and POP Instructions

Since the Top-of-Stack is readable and writable, the ability to push values onto the stack and pull values off the stack without disturbing normal program execution is a desirable feature. The PIC18 instruction set includes two instructions, PUSH and POP, that permit the TOS to be manipulated under software control. TOSU, TOSH and TOSL can be modified to place data or a return address on the stack.

The PUSH instruction places the current PC value onto the stack. This increments the Stack Pointer and loads the current PC value onto the stack.

The POP instruction discards the current TOS by decrementing the Stack Pointer. The previous value pushed onto the stack then becomes the TOS value.

| R/C-0                 | R/C-0                 | U-0              | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------------|-----------------------|------------------|-------|-------------------|------------------|-----------------|-------|

| STKFUL <sup>(1)</sup> | STKUNF <sup>(1)</sup> | —                | SP4   | SP3               | SP2              | SP1             | SP0   |

| bit 7                 |                       |                  |       |                   |                  |                 | bit 0 |

|                       |                       |                  |       |                   |                  |                 |       |

| Legend:               |                       | C = Clearable    | bit   |                   |                  |                 |       |

| R = Readable          | bit                   | W = Writable I   | oit   | U = Unimplem      | nented bit, read | l as '0'        |       |

| -n = Value at F       | POR                   | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

#### REGISTER 6-1: STKPTR: STACK POINTER REGISTER

| bit 7   | STKFUL: Stack Full Flag bit <sup>(1)</sup>      |

|---------|-------------------------------------------------|

|         | 1 = Stack became full or overflowed             |

|         | 0 = Stack has not become full or overflowed     |

| bit 6   | STKUNF: Stack Underflow Flag bit <sup>(1)</sup> |

|         | 1 = Stack underflow occurred                    |

|         | 0 = Stack underflow did not occur               |

| bit 5   | Unimplemented: Read as '0'                      |

| bit 4-0 | SP<4:0>: Stack Pointer Location bits            |

**Note 1:** Bit 7 and bit 6 are cleared by user software or by a POR.

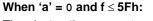

#### FIGURE 6-9: COMPARING ADDRESSING OPTIONS FOR BIT-ORIENTED AND BYTE-ORIENTED INSTRUCTIONS (EXTENDED INSTRUCTION SET ENABLED)

Example Instruction: ADDWF, f, d, a (Opcode: 0010 01da ffff ffff)

#### When 'a' = 0 and $f \ge 60h$ :

The instruction executes in Direct Forced mode. 'f' is interpreted as a location in the Access RAM between 060h and 0FFh. This is the same as locations 060h to 07Fh (Bank 0) and F80h to FFFh (Bank 15) of data memory.

Locations below 60h are not available in this addressing mode.

The instruction executes in Indexed Literal Offset mode. 'f' is interpreted as an offset to the address value in FSR2. The two are added together to obtain the address of the target register for the instruction. The address can be anywhere in the data memory space.

Note that in this mode, the correct syntax is now: ADDWF [k], d where 'k' is the same as 'f'.

#### When 'a' = 1 (all values of f):

The instruction executes in Direct mode (also known as Direct Long mode). 'f' is interpreted as a location in one of the 16 banks of the data memory space. The bank is designated by the Bank Select Register (BSR). The address can be in any implemented bank in the data memory space.

### 9.2 PIR Registers

The PIR registers contain the individual flag bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are three Peripheral Interrupt Request (Flag) registers (PIR1, PIR2, PIR3).

- Note 1: Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE (INTCON<7>).

- 2: User software should ensure the appropriate interrupt flag bits are cleared prior to enabling an interrupt and after servicing that interrupt.

#### REGISTER 9-4: PIR1: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 1

| R/W-0                | R/W-0 | R-0  | R-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|----------------------|-------|------|------|--------|--------|--------|--------|

| PSPIF <sup>(1)</sup> | ADIF  | RCIF | TXIF | SSP1IF | CCP1IF | TMR2IF | TMR1IF |

| bit 7                |       |      |      |        |        |        | bit 0  |

|                      |       |      |      |        |        |        |        |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

|                   |                  |                       |                    |

| bit 7 | PSPIF: Parallel Slave Port Read/Write Interrupt Flag bit <sup>(1)</sup>                                                                             |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = A read or a write operation has taken place (must be cleared in software)</li> <li>0 = No read or write has occurred</li> </ul>        |

| bit 6 | ADIF: A/D Converter Interrupt Flag bit                                                                                                              |

|       | <ul> <li>1 = An A/D conversion completed (must be cleared in software)</li> <li>0 = The A/D conversion is not complete</li> </ul>                   |

| bit 5 | RCIF: EUSART Receive Interrupt Flag bit                                                                                                             |

|       | <ul> <li>1 = The EUSART receive buffer, RCREG, is full (cleared when RCREG is read)</li> <li>0 = The EUSART receive buffer is empty</li> </ul>      |

| bit 4 | TXIF: EUSART Transmit Interrupt Flag bit                                                                                                            |

|       | <ul> <li>1 = The EUSART transmit buffer, TXREG, is empty (cleared when TXREG is written)</li> <li>0 = The EUSART transmit buffer is full</li> </ul> |

| bit 3 | SSP1IF: Master Synchronous Serial Port 1 Interrupt Flag bit                                                                                         |

|       | <ul> <li>1 = The transmission/reception is complete (must be cleared in software)</li> <li>0 = Waiting to transmit/receive</li> </ul>               |

| bit 2 | CCP1IF: ECCP1/CCP1 Interrupt Flag bit                                                                                                               |

|       | <u>Capture mode:</u><br>1 = A TMR1 register capture occurred (must be cleared in software)<br>0 = No TMR1 register capture occurred                 |

|       | Compare mode:                                                                                                                                       |

|       | <ul> <li>1 = A TMR1 register compare match occurred (must be cleared in software)</li> <li>0 = No TMR1 register compare match occurred</li> </ul>   |

|       | <u>PWM mode:</u><br>Unused in this mode.                                                                                                            |

| bit 1 | TMR2IF: TMR2 to PR2 Match Interrupt Flag bit                                                                                                        |

|       | <ul> <li>1 = TMR2 to PR2 match occurred (must be cleared in software)</li> <li>0 = No TMR2 to PR2 match occurred</li> </ul>                         |

| bit 0 | TMR1IF: TMR1 Overflow Interrupt Flag bit                                                                                                            |

|       | <ul> <li>1 = TMR1 register overflowed (must be cleared in software)</li> <li>0 = TMR1 register did not overflow</li> </ul>                          |

|       |                                                                                                                                                     |

Note 1: This bit is not implemented on 28-pin devices and should be read as '0'.

#### REGISTER 9-5: PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2

| R/W-0       | R/W-0                                                                                                                       | U-0                              | U-0           | R/W-0             | U-0             | U-0              | R/W-0    |

|-------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------|---------------|-------------------|-----------------|------------------|----------|

| OSCFIF      | CMIF                                                                                                                        |                                  | —             | BCLIF             | —               | _                | CCP2IF   |

| oit 7       |                                                                                                                             |                                  |               |                   |                 |                  | bit 0    |

|             |                                                                                                                             |                                  |               |                   |                 |                  |          |

| _egend:     |                                                                                                                             |                                  |               |                   |                 |                  |          |

| R = Readab  | le bit                                                                                                                      | W = Writable b                   | bit           | U = Unimplem      | nented bit, rea | ad as '0'        |          |

| n = Value a | t POR                                                                                                                       | '1' = Bit is set                 |               | '0' = Bit is clea | ared            | x = Bit is unk   | nown     |

|             |                                                                                                                             |                                  |               |                   |                 |                  |          |

| oit 7       |                                                                                                                             | cillator Fail Interi             |               |                   |                 |                  |          |

|             |                                                                                                                             | oscillator failed, o             | lock input ha | s changed to IN   | TOSC (must      | be cleared in so | oftware) |

|             |                                                                                                                             | clock operating                  |               |                   |                 |                  |          |

| oit 6       |                                                                                                                             | parator Interrupt I              | •             |                   |                 |                  |          |

|             |                                                                                                                             | ator input has ch                | <b>U</b> (    | be cleared in sc  | oftware)        |                  |          |

|             |                                                                                                                             | ator input has no                | •             |                   |                 |                  |          |

| oit 5-4     | -                                                                                                                           | nted: Read as '0                 |               |                   |                 |                  |          |

| oit 3       | <b>BCLIF:</b> Bus Collision Interrupt Flag bit (MSSP1 module)<br>1 = A bus collision occurred (must be cleared in software) |                                  |               |                   |                 |                  |          |

|             |                                                                                                                             | collision occurred               |               | ared in software) |                 |                  |          |

| oit 2-1     | Unimplemented: Read as '0'                                                                                                  |                                  |               |                   |                 |                  |          |

| oit 0       | CCP2IF: CC                                                                                                                  | P2 Interrupt Flag                | g bit         |                   |                 |                  |          |

|             | Capture mod                                                                                                                 | de:                              |               |                   |                 |                  |          |

|             |                                                                                                                             | I register capture               |               | ust be cleared ir | i software)     |                  |          |

|             |                                                                                                                             | R1 register captur               | e occurred    |                   |                 |                  |          |

|             | $\frac{\text{Compare model}}{1 - A \text{ TMP}}$                                                                            | <u>ode:</u><br>I register compar | o motob oco   | urrod (must bo o  | oarad in coff   | woro)            |          |

|             |                                                                                                                             | R1 register compar               |               |                   |                 | wale)            |          |

|             | PWM mode:                                                                                                                   | •                                |               |                   |                 |                  |          |

|             | Unused in th                                                                                                                | -                                |               |                   |                 |                  |          |

#### REGISTER 9-6: PIR3: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 3

| R/W-0  | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|--------|-----|-----|-----|-----|-----|-------|

| SSP2IF | BCL2IF | —   | —   | —   | —   | —   | —     |

| bit 7  |        |     |     |     |     |     | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

|                   |                  |                       |                    |

| bit 7   | SSP2IF: Master Synchronous Serial Port 2 Interrupt Flag bit                                                                        |

|---------|------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul><li>1 = The transmission/reception is complete (must be cleared in software)</li><li>0 = Waiting to transmit/receive</li></ul> |

| bit 6   | BCL2IF: Bus Collision Interrupt Flag bit (MSSP2 module)                                                                            |

|         | 1 = A bus collision occurred (must be cleared in software)                                                                         |

|         | 0 = No bus collision occurred                                                                                                      |

| bit 5-0 | Unimplemented: Read as '0'                                                                                                         |

|         |                                                                                                                                    |

#### EXAMPLE 12-1: IMPLEMENTING A REAL-TIME CLOCK USING A TIMER1 INTERRUPT SERVICE

| RTCinit |        |              |                                               |

|---------|--------|--------------|-----------------------------------------------|

|         | MOVLW  | 80h          | ; Preload TMR1 register pair                  |

|         | MOVWF  | TMR1H        | ; for 1 second overflow                       |

|         | CLRF   | TMR1L        |                                               |

|         | MOVLW  | b'00001111'  | ; Configure for external clock,               |

|         | MOVWF  | T1CON        | ; Asynchronous operation, external oscillator |

|         | CLRF   | secs         | ; Initialize timekeeping registers            |

|         | CLRF   | mins         | i                                             |

|         | MOVLW  | .12          |                                               |

|         | MOVWF  | hours        |                                               |

|         | BSF    | PIE1, TMR1IE | ; Enable Timer1 interrupt                     |

|         | RETURN |              |                                               |

| RTCisr  |        |              |                                               |

|         | BSF    | TMR1H, 7     | ; Preload for 1 sec overflow                  |

|         | BCF    | PIR1, TMR1IF | ; Clear interrupt flag                        |

|         | INCF   | secs, F      | ; Increment seconds                           |

|         | MOVLW  | .59          | ; 60 seconds elapsed?                         |

|         | CPFSGT | secs         |                                               |

|         | RETURN |              | ; No, done                                    |

|         | CLRF   | secs         | ; Clear seconds                               |

|         | INCF   | mins, F      | ; Increment minutes                           |

|         | MOVLW  | .59          | ; 60 minutes elapsed?                         |

|         | CPFSGT | mins         |                                               |

|         | RETURN |              | ; No, done                                    |

|         | CLRF   | mins         | ; clear minutes                               |

|         | INCF   | hours, F     | ; Increment hours                             |

|         | MOVLW  | .23          | ; 24 hours elapsed?                           |

|         | CPFSGT | hours        |                                               |

|         | RETURN |              | ; No, done                                    |

|         | CLRF   | hours        | ; Reset hours                                 |

|         | RETURN |              | ; Done                                        |

|         |        |              |                                               |

#### TABLE 12-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Name   | Bit 7                     | Bit 6     | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|---------------------------|-----------|---------|---------|---------|--------|--------|--------|----------------------------|

| INTCON | GIE/GIEH                  | PEIE/GIEL | TMR0IE  | INT0IE  | RBIE    | TMR0IF | INT0IF | RBIF   | 47                         |

| PIR1   | PSPIF <sup>(1)</sup>      | ADIF      | RCIF    | TXIF    | SSP1IF  | CCP1IF | TMR2IF | TMR1IF | 49                         |

| PIE1   | PSPIE <sup>(1)</sup>      | ADIE      | RCIE    | TXIE    | SSP1IE  | CCP1IE | TMR2IE | TMR1IE | 49                         |

| IPR1   | PSPIP <sup>(1)</sup>      | ADIP      | RCIP    | TXIP    | SSP1IP  | CCP1IP | TMR2IP | TMR1IP | 49                         |

| TMR1L  | Timer1 Register Low Byte  |           |         |         |         |        |        | 48     |                            |

| TMR1H  | Timer1 Register High Byte |           |         |         |         |        | 48     |        |                            |

| T1CON  | RD16                      | T1RUN     | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 48                         |

**Legend:** Shaded cells are not used by the Timer1 module.

Note 1: These bits are not implemented on 28-pin devices and should be read as '0'.

The CCPRxH register and a 2-bit internal latch are used to double-buffer the PWM duty cycle. This double-buffering is essential for glitchless PWM operation.

When the CCPRxH and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCPx pin is cleared.

The maximum PWM resolution (bits) for a given PWM frequency is given by the equation:

#### **EQUATION 14-3:**

PWM Resolution (max) =

$$\frac{\log(\frac{Fosc}{FPWM})}{\log(2)}$$

bits

Note: If the PWM duty cycle value is longer than the PWM period, the CCP2 pin will not be cleared.

| <b>TABLE 14-4</b> : | EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 40 MHz |

|---------------------|---------------------------------------------------|

|                     |                                                   |

| PWM Frequency              | 2.44 kHz | 9.77 kHz | 39.06 kHz | 156.25 kHz | 312.50 kHz | 416.67 kHz |

|----------------------------|----------|----------|-----------|------------|------------|------------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1          | 1          | 1          |

| PR2 Value                  | FFh      | FFh      | FFh       | 3Fh        | 1Fh        | 17h        |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8          | 7          | 6.58       |

#### 14.4.3 PWM AUTO-SHUTDOWN (CCP1 ONLY)

The PWM auto-shutdown features of the Enhanced CCP module are also available to CCP1 in 28-pin devices. The operation of this feature is discussed in detail in **Section 15.4.7 "Enhanced PWM Auto-Shutdown"**.

Auto-shutdown features are not available for CCP2.

### 14.4.4 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPRxL register and CCPxCON<5:4> bits.

- 3. Make the CCPx pin an output by clearing the appropriate TRIS bit.

- 4. Set the TMR2 prescale value, then enable Timer2 by writing to T2CON.

- 5. Configure the CCPx module for PWM operation.

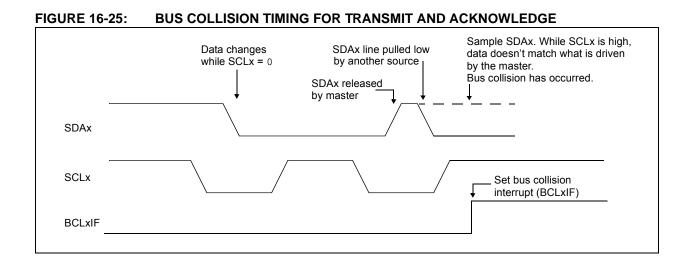

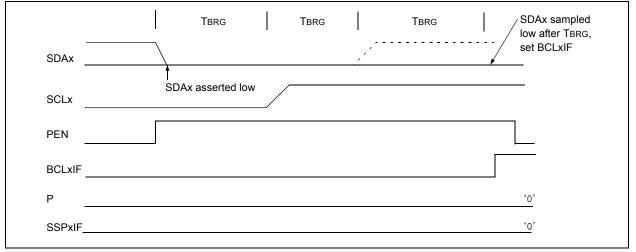

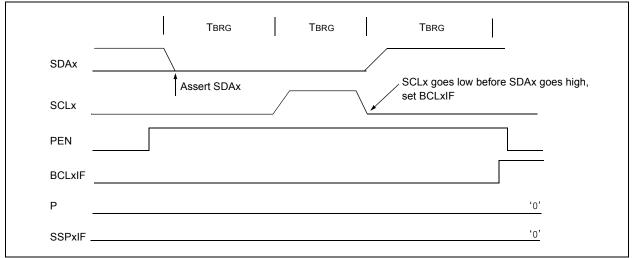

#### 16.4.17.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDAx pin has been deasserted and allowed to float high, SDAx is sampled low after the BRG has timed out.

- b) After the SCLx pin is deasserted, SCLx is sampled low before SDAx goes high.

The Stop condition begins with SDAx asserted low. When SDAx is sampled low, the SCLx pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPxADD<6:0> and counts down to 0. After the BRG times out, SDAx is sampled. If SDAx is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 16-31). If the SCLx pin is sampled low before SDAx is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 16-32).

#### FIGURE 16-31: BUS COLLISION DURING A STOP CONDITION (CASE 1)

FIGURE 16-32: BUS COLLISION DURING A STOP CONDITION (CASE 2)

NOTES:

# 20.0 COMPARATOR VOLTAGE REFERENCE MODULE

The comparator voltage reference is a 16-tap resistor ladder network that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it may also be used independently of them.

A block diagram of the module is shown in Figure 20-1. The resistor ladder is segmented to provide two ranges of CVREF values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/VSS or an external voltage reference.

#### 20.1 Configuring the Comparator Voltage Reference

-----

The voltage reference module is controlled through the CVRCON register (Register 20-1). The comparator voltage reference provides two ranges of output voltage, each with 16 distinct levels. The range to be

used is selected by the CVRR bit (CVRCON<5>). The primary difference between the ranges is the size of the steps selected by the CVREF Selection bits (CVR<3:0>), with one range offering finer resolution. The equations used to calculate the output of the comparator voltage reference are as follows:

<u>If CVRR = 1:</u> CVREF = ((CVR<3:0>)/24) x CVRSRC <u>If CVRR = 0:</u> CVREF = (CVRSRC x 1/4) + (((CVR<3:0>)/32) x CVRSRC)

The comparator reference supply voltage can come from either VDD and VSS, or the external VREF+ and VREF- that are multiplexed with RA2 and RA3. The voltage source is selected by the CVRSS bit (CVRCON<4>).

The settling time of the comparator voltage reference must be considered when changing the CVREF output (see Table 24-3 in **Section 24.0 "Electrical Characteristics"**).

#### **REGISTER 20-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER**

| R/W-0 | R/W-0                | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|----------------------|-------|-------|-------|-------|-------|-------|

| CVREN | CVROE <sup>(1)</sup> | CVRR  | CVRSS | CVR3  | CVR2  | CVR1  | CVR0  |

| bit 7 |                      |       |       |       |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 7   | CVREN: Comparator Voltage Reference Enable bit                                                                                                                                                                                     |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = CVREF circuit powered on                                                                                                                                                                                                       |

|         | 0 = CVREF circuit powered down                                                                                                                                                                                                     |

| bit 6   | CVROE: Comparator VREF Output Enable bit <sup>(1)</sup>                                                                                                                                                                            |

|         | <ul> <li>1 = CVREF voltage level is also output on the RA2/AN2/VREF-/CVREF pin</li> <li>0 = CVREF voltage is disconnected from the RA2/AN2/VREF-/CVREF pin</li> </ul>                                                              |

| bit 5   | CVRR: Comparator VREF Range Selection bit                                                                                                                                                                                          |

|         | <ul> <li>1 = 0 to 0.667 CVRsRc, with CVRsRc/24 step size (low range)</li> <li>0 = 0.25 CVRsRc to 0.75 CVRsRc, with CVRsRc/32 step size (high range)</li> </ul>                                                                     |

| bit 4   | CVRSS: Comparator VREF Source Selection bit                                                                                                                                                                                        |

|         | <ul> <li>1 = Comparator reference source, CVRSRC = (VREF+) – (VREF-)</li> <li>0 = Comparator reference source, CVRSRC = VDD – VSS</li> </ul>                                                                                       |

| bit 3-0 | <b>CVR&lt;3:0&gt;:</b> Comparator VREF Value Selection bits $(0 \le (CVR<3:0>) \le 15)$<br><u>When CVRR = 1:</u><br>CVREF = ((CVR<3:0>)/24) • (CVRSRC)<br><u>When CVRR = 0:</u><br>CVREF = (CVRSRC/4) + ((CVR<3:0>)/32) • (CVRSRC) |

|         |                                                                                                                                                                                                                                    |

Note 1: CVROE overrides the TRISA<2> bit setting.

#### TABLE 22-2: PIC18FXXXX INSTRUCTION SET

| Mnemonic,<br>Operands |                                 | Description                              | 0          | 16-Bit Instruction Word |      |      |      | Status          | Netes      |

|-----------------------|---------------------------------|------------------------------------------|------------|-------------------------|------|------|------|-----------------|------------|

|                       |                                 | Description                              | Cycles     | MSb                     |      |      | LSb  | Affected        | Notes      |

| BYTE-ORIE             | ENTED C                         | OPERATIONS                               |            |                         |      |      |      |                 |            |

| ADDWF                 | f, d, a                         | Add WREG and f                           | 1          | 0010                    | 01da | ffff | ffff | C, DC, Z, OV, N | 1, 2       |

| ADDWFC                | f, d, a                         | Add WREG and Carry bit to f              | 1          | 0010                    | 00da | ffff | ffff | C, DC, Z, OV, N | 1, 2       |

| ANDWF                 | f, d, a                         | AND WREG with f                          | 1          | 0001                    | 01da | ffff | ffff | Z, N            | 1,2        |

| CLRF                  | f, a                            | Clear f                                  | 1          | 0110                    | 101a | ffff | ffff | Z               | 2          |

| COMF                  | f, d, a                         | Complement f                             | 1          | 0001                    | 11da | ffff | ffff | Z, N            | 1, 2       |

| CPFSEQ                | f, a                            | Compare f with WREG, Skip =              | 1 (2 or 3) | 0110                    | 001a | ffff | ffff | None            | 4          |

| CPFSGT                | f, a                            | Compare f with WREG, Skip >              | 1 (2 or 3) | 0110                    | 010a | ffff | ffff | None            | 4          |

| CPFSLT                | f, a                            | Compare f with WREG, Skip <              | 1 (2 or 3) | 0110                    | 000a | ffff | ffff | None            | 1, 2       |

| DECF                  | f, d, a                         | Decrement f                              | 1          | 0000                    | 01da | ffff | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| DECFSZ                | f, d, a                         | Decrement f, Skip if 0                   | 1 (2 or 3) | 0010                    | 11da | ffff | ffff | None            | 1, 2, 3, 4 |

| DCFSNZ                | f, d, a                         | Decrement f, Skip if Not 0               | 1 (2 or 3) | 0100                    | 11da | ffff | ffff | None            | 1, 2       |

| INCF                  | f, d, a                         | Increment f                              | 1          | 0010                    | 10da | ffff | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| INCFSZ                | f, d, a                         | Increment f, Skip if 0                   | 1 (2 or 3) | 0011                    | 11da | ffff | ffff | None            | 4          |

| INFSNZ                | f, d, a                         | Increment f, Skip if Not 0               | 1 (2 or 3) | 0100                    | 10da | ffff | ffff | None            | 1, 2       |

| IORWF                 | f, d, a                         | Inclusive OR WREG with f                 | 1          | 0001                    | 00da | ffff | ffff | Z, N            | 1, 2       |

| MOVF                  | f, d, a                         | Move f                                   | 1          | 0101                    | 00da | ffff | ffff | Z, N            | 1          |

| MOVFF                 | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st Word | 2          | 1100                    | ffff | ffff | ffff | None            |            |

|                       |                                 | f <sub>d</sub> (destination) 2nd Word    |            | 1111                    | ffff | ffff | ffff |                 |            |

| MOVWF                 | f, a                            | Move WREG to f                           | 1          | 0110                    | 111a | ffff | ffff | None            |            |

| MULWF                 | f, a                            | Multiply WREG with f                     | 1          | 0000                    | 001a | ffff | ffff | None            | 1, 2       |

| NEGF                  | f, a                            | Negate f                                 | 1          | 0110                    | 110a | ffff | ffff | C, DC, Z, OV, N |            |

| RLCF                  | f, d, a                         | Rotate Left f through Carry              | 1          | 0011                    | 01da | ffff | ffff | C, Z, N         | 1, 2       |

| RLNCF                 | f, d, a                         | Rotate Left f (No Carry)                 | 1          | 0100                    | 01da | ffff | ffff | Z, N            |            |

| RRCF                  | f, d, a                         | Rotate Right f through Carry             | 1          | 0011                    | 00da | ffff | ffff | C, Z, N         |            |

| RRNCF                 | f, d, a                         | Rotate Right f (No Carry)                | 1          | 0100                    | 00da | ffff | ffff | Z, N            |            |

| SETF                  | f, a                            | Set f                                    | 1          | 0110                    | 100a | ffff | ffff | None            | 1, 2       |

| SUBFWB                | f, d, a                         | Subtract f from WREG with<br>Borrow      | 1          | 0101                    | 01da | ffff | ffff | C, DC, Z, OV, N |            |

| SUBWF                 | f, d, a                         | Subtract WREG from f                     | 1          | 0101                    | 11da | ffff | ffff | C, DC, Z, OV, N | 1, 2       |

| SUBWFB                | f, d, a                         | Subtract WREG from f with                | 1          | 0101                    | 10da | ffff | ffff | C, DC, Z, OV, N |            |

|                       |                                 | Borrow                                   |            |                         |      |      |      |                 |            |

| SWAPF                 | f, d, a                         | Swap Nibbles in f                        | 1          | 0011                    | 10da | ffff | ffff | None            | 4          |

| TSTFSZ                | f, a                            | Test f, Skip if 0                        | 1 (2 or 3) | 0110                    | 011a | ffff | ffff | None            | 1, 2       |

| XORWF                 | f, d, a                         | Exclusive OR WREG with f                 | 1          | 0001                    | 10da | ffff |      | Z, N            |            |

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

3: If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

#### 22.1.1 STANDARD INSTRUCTION SET

| ADDLW                                                         |               | ADD Liter               | ADD Literal to W                                                                          |      |           |  |  |  |

|---------------------------------------------------------------|---------------|-------------------------|-------------------------------------------------------------------------------------------|------|-----------|--|--|--|

| Syntax                                                        | x:            | ADDLW I                 | ADDLW k                                                                                   |      |           |  |  |  |

| Opera                                                         | nds:          | $0 \leq k \leq 255$     |                                                                                           |      |           |  |  |  |

| Opera                                                         | tion:         | $(W) + k \rightarrow V$ | N                                                                                         |      |           |  |  |  |

| Status                                                        | Affected:     | N, OV, C, D             | C, Z                                                                                      |      |           |  |  |  |

| Encod                                                         | ling:         | 0000                    | 1111                                                                                      | kkkk | kkkk      |  |  |  |

| Descri                                                        | iption:       |                         | The contents of W are added to the<br>8-bit literal 'k' and the result is placed in<br>W. |      |           |  |  |  |

| Words:                                                        |               | 1                       | 1                                                                                         |      |           |  |  |  |

| Cycles                                                        | s:            | 1                       |                                                                                           |      |           |  |  |  |

| Q Cy                                                          | cle Activity: |                         |                                                                                           |      |           |  |  |  |

|                                                               | Q1            | Q2                      | Q3                                                                                        |      | Q4        |  |  |  |

|                                                               | Decode        | Read<br>literal 'k'     | Proce<br>Data                                                                             |      | rite to W |  |  |  |

| Example:ADDLW15hBefore InstructionW=10hAfter InstructionW=25h |               |                         |                                                                                           |      |           |  |  |  |

| ADDWF            | ADD W to f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | ADDWF f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in [0,1] \\ a \in [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Operation:       | (W) + (f) $\rightarrow$ dest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Status Affected: | N, OV, C, DC, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Encoding:        | 0010 01da ffff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Description:     | Add W to register 'f'. If 'd' is '0', the<br>result is stored in W. If 'd' is '1', the<br>result is stored back in register 'f'<br>(default).<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 22.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |

| Words:           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Cycles:          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| QC | ycle Activity:               |                      |              |                 |      |                      |

|----|------------------------------|----------------------|--------------|-----------------|------|----------------------|

|    | Q1                           |                      | Q2           | Q3              |      | Q4                   |

|    | Decode                       | Read<br>register 'f' |              | Process<br>Data |      | Write to destination |

|    | Example:<br>Before Instruc   |                      | DDWF         | REG,            | 0, 0 |                      |

|    | W<br>REG<br>After Instructio | =<br>=               | 17h<br>0C2h  |                 |      |                      |

|    | W<br>REG                     | =<br>=               | 0D9h<br>0C2h |                 |      |                      |

| Note: | All PIC18 instructions may take an optional label argument preceding the instruction mnemonic for use in       |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | symbolic addressing. If a label is used, the instruction format then becomes: {label} instruction argument(s). |

| POP                                      |             | Рор Тор                                                               | Pop Top of Return Stack                                                                                                                                                                                                                                                                    |                 |    |         |  |  |  |

|------------------------------------------|-------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----|---------|--|--|--|

| Syntax:                                  |             | POP                                                                   |                                                                                                                                                                                                                                                                                            |                 |    |         |  |  |  |

| Operand                                  | ds:         | None                                                                  |                                                                                                                                                                                                                                                                                            |                 |    |         |  |  |  |

| Operatio                                 | on:         | $(TOS) \rightarrow b$                                                 | it bucket                                                                                                                                                                                                                                                                                  |                 |    |         |  |  |  |

| Status A                                 | ffected:    | None                                                                  | None                                                                                                                                                                                                                                                                                       |                 |    |         |  |  |  |

| Encodin                                  | g:          | 0000                                                                  | 0000                                                                                                                                                                                                                                                                                       | 000             | 00 | 0110    |  |  |  |

| Descript                                 | ion:        | stack and i<br>then becor<br>was pushe<br>This instru-<br>the user to | The TOS value is pulled off the return<br>stack and is discarded. The TOS value<br>then becomes the previous value that<br>was pushed onto the return stack.<br>This instruction is provided to enable<br>the user to properly manage the return<br>stack to incorporate a software stack. |                 |    |         |  |  |  |

| Words:                                   |             | 1                                                                     |                                                                                                                                                                                                                                                                                            |                 |    |         |  |  |  |

| Cycles:                                  |             | 1                                                                     |                                                                                                                                                                                                                                                                                            |                 |    |         |  |  |  |

| Q Cycle                                  | e Activity: |                                                                       |                                                                                                                                                                                                                                                                                            |                 |    |         |  |  |  |

|                                          | Q1          | Q2                                                                    | Q3                                                                                                                                                                                                                                                                                         | 5               |    | Q4      |  |  |  |

|                                          | Decode      | No                                                                    | POP 1                                                                                                                                                                                                                                                                                      | OS              |    | No      |  |  |  |

|                                          |             | operation                                                             | valu                                                                                                                                                                                                                                                                                       | le              | ор | eration |  |  |  |

| <u>Example</u>                           | <u>):</u>   | POP<br>GOTO                                                           | NEW                                                                                                                                                                                                                                                                                        |                 |    |         |  |  |  |

| Before Instructio<br>TOS<br>Stack (1 lev |             |                                                                       |                                                                                                                                                                                                                                                                                            | 031A2<br>014332 |    |         |  |  |  |

| After Instruction<br>TOS<br>PC           |             | on                                                                    |                                                                                                                                                                                                                                                                                            | )14332<br>NEW   | 2h |         |  |  |  |

| PUS                            | H                                          | Push Top                                                                                  | Push Top of Return Stack            |                                              |                                |                                     |  |  |  |

|--------------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------|--------------------------------|-------------------------------------|--|--|--|

| Synta                          | ax:                                        | PUSH                                                                                      | PUSH                                |                                              |                                |                                     |  |  |  |

| Oper                           | ands:                                      | None                                                                                      | None                                |                                              |                                |                                     |  |  |  |

| Oper                           | ation:                                     | $(PC + 2) \rightarrow$                                                                    | TOS                                 |                                              |                                |                                     |  |  |  |

| Statu                          | is Affected:                               | None                                                                                      |                                     |                                              |                                |                                     |  |  |  |

| Enco                           | oding:                                     | 0000                                                                                      | 0000                                | 000                                          | 00                             | 0101                                |  |  |  |

| Desc                           | ription:                                   | The PC + 2<br>the return s<br>value is pus<br>This instruc<br>software sta<br>then pushin | tack.<br>shed d<br>tion a<br>ack by | The prev<br>lown on<br>llows imp<br>modifyii | ious<br>the s<br>blem<br>ng T( | TOS<br>stack.<br>enting a<br>OS and |  |  |  |

| Word                           | ls:                                        | 1                                                                                         |                                     |                                              |                                |                                     |  |  |  |

| Cycle                          | es:                                        | 1                                                                                         |                                     |                                              |                                |                                     |  |  |  |

| QC                             | ycle Activity:                             |                                                                                           |                                     |                                              |                                |                                     |  |  |  |

|                                | Q1                                         | Q2                                                                                        |                                     | Q3                                           |                                | Q4                                  |  |  |  |

|                                | Decode                                     | PUSH<br>PC + 2 onto<br>return stack                                                       | No<br>operation                     |                                              | op                             | No<br>peration                      |  |  |  |

| Exan                           | nple:                                      | PUSH                                                                                      |                                     |                                              |                                |                                     |  |  |  |

| Before Instructio<br>TOS<br>PC |                                            | tion                                                                                      | =<br>=                              | 345Ah<br>0124h                               |                                |                                     |  |  |  |

|                                | After Instruction<br>PC<br>TOS<br>Stack (1 | on<br>level down)                                                                         | =<br>=<br>=                         | 0126h<br>0126h<br>345Ah                      |                                |                                     |  |  |  |

| RRM                                                                                      | NCF                          | Rotate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Rotate Right f (No Carry)                                                     |                    |     |                         |  |  |  |  |

|------------------------------------------------------------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------|-----|-------------------------|--|--|--|--|

| Synt                                                                                     | ax:                          | RRNCF f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                               |                    |     |                         |  |  |  |  |

| Oper                                                                                     | rands:                       | $0 \le f \le 255$<br>$d \in [0, 1]$<br>$a \in [0, 1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                               |                    |     |                         |  |  |  |  |

| Ope                                                                                      | ration:                      | . ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $(f < n >) \rightarrow dest < n - 1 >,$<br>$(f < 0 >) \rightarrow dest < 7 >$ |                    |     |                         |  |  |  |  |

| Statu                                                                                    | us Affected:                 | N, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | N, Z                                                                          |                    |     |                         |  |  |  |  |