Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuils                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 32                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                 |

| Data Converters            | A/D 13x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 44-QFN (8x8)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f45j10t-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

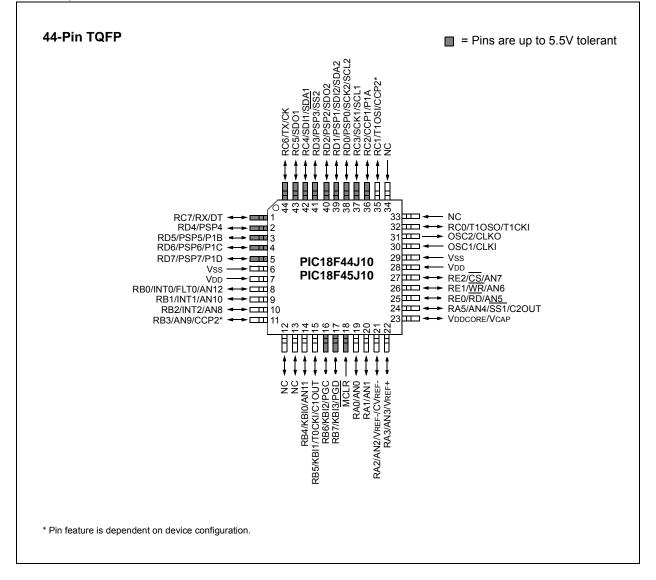

## **Pin Diagrams (Continued)**

## 4.2.3 RC\_RUN MODE

In RC\_RUN mode, the CPU and peripherals are clocked from the internal oscillator; the primary clock is shut down. This mode provides the best power conservation of all the Run modes, while still executing code. It works well for user applications which are not highly timing-sensitive or do not require high-speed clocks at all times.

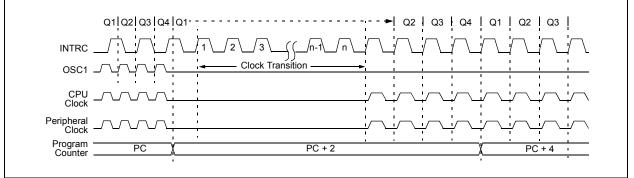

This mode is entered by setting SCS<1:0> to '11'. When the clock source is switched to the INTRC (see Figure 4-2), the primary oscillator is shut down and the OSTS bit is cleared.

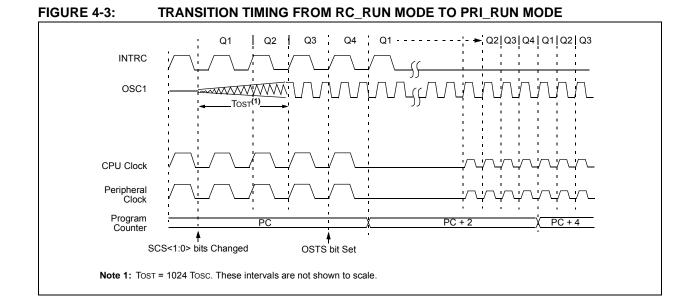

On transitions from RC\_RUN mode to PRI\_RUN mode, the device continues to be clocked from the INTRC while the primary clock is started. When the primary clock becomes ready, a clock switch to the primary clock occurs (see Figure 4-3). When the clock switch is complete, the OSTS bit is set and the primary clock is providing the device clock. The IDLEN and SCS bits are not affected by the switch. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

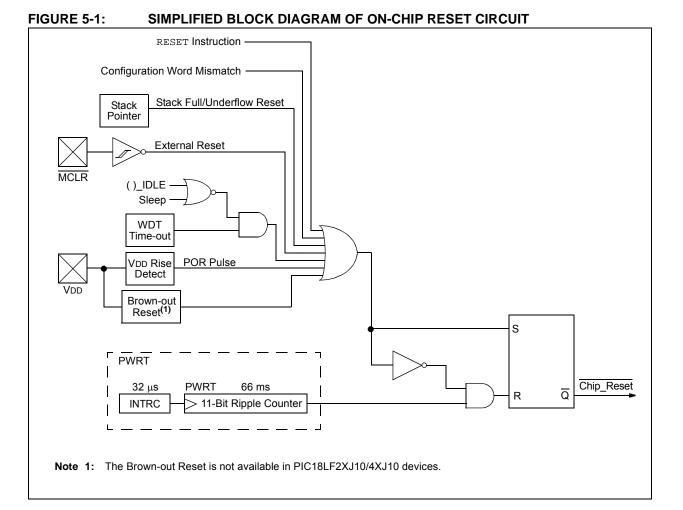

# 5.0 RESET

The PIC18F45J10 family of devices differentiate between various kinds of Reset:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during power-managed modes

- d) Watchdog Timer (WDT) Reset (during execution)

- e) Configuration Mismatch (CM)

- f) Brown-out Reset (BOR)

- g) RESET Instruction

- h) Stack Full Reset

- i) Stack Underflow Reset

This section discusses Resets generated by MCLR, POR and BOR and covers the operation of the various start-up timers. Stack Reset events are covered in Section 6.1.4.4 "Stack Full and Underflow Resets". WDT Resets are covered in Section 21.2 "Watchdog Timer (WDT)".

A simplified block diagram of the on-chip Reset circuit is shown in Figure 5-1.

# 5.1 RCON Register

Device Reset events are tracked through the RCON register (Register 5-1). The lower six bits of the register indicate that a specific Reset event has occurred. In most cases, these bits can only be set by the event and must be cleared by the application after the event. The state of these flag bits, taken together, can be read to indicate the type of Reset that just occurred. This is described in more detail in **Section 5.7** "**Reset State of Registers**".

The RCON register also has a control bit for setting interrupt priority (IPEN). Interrupt priority is discussed in **Section 9.0 "Interrupts"**.

| TABLE 5-2: |             | TION CONDIT | IONS FOR ALL RE                    | INS FOR ALL REGISTERS (CONTINUED)                                              |                                 |  |  |  |

|------------|-------------|-------------|------------------------------------|--------------------------------------------------------------------------------|---------------------------------|--|--|--|

| Register   | Applicable  | e Devices   | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets,<br>CM Resets | Wake-up via WDT<br>or Interrupt |  |  |  |

| CCPR1H     | PIC18F2XJ10 | PIC18F4XJ10 | XXXX XXXX                          | uuuu uuuu                                                                      | uuuu uuuu                       |  |  |  |

| CCPR1L     | PIC18F2XJ10 | PIC18F4XJ10 | XXXX XXXX                          | uuuu uuuu                                                                      | uuuu uuuu                       |  |  |  |

| CCP1CON    | PIC18F2XJ10 | PIC18F4XJ10 | 0000 0000                          | 0000 0000                                                                      | uuuu uuuu                       |  |  |  |

| CCPR2H     | PIC18F2XJ10 | PIC18F4XJ10 | XXXX XXXX                          | uuuu uuuu                                                                      | uuuu uuuu                       |  |  |  |

| CCPR2L     | PIC18F2XJ10 | PIC18F4XJ10 | XXXX XXXX                          | uuuu uuuu                                                                      | uuuu uuuu                       |  |  |  |

| CCP2CON    | PIC18F2XJ10 | PIC18F4XJ10 | 00 0000                            | 00 0000                                                                        | uu uuuu                         |  |  |  |

| BAUDCON    | PIC18F2XJ10 | PIC18F4XJ10 | 01-0 0-00                          | 01-0 0-00                                                                      | uu-u u-uu                       |  |  |  |

| ECCP1DEL   | PIC18F2XJ10 | PIC18F4XJ10 | 0000 0000                          | 0000 0000                                                                      | uuuu uuuu                       |  |  |  |

| ECCP1AS    | PIC18F2XJ10 | PIC18F4XJ10 | 0000 0000                          | 0000 0000                                                                      | uuuu uuuu                       |  |  |  |

| CVRCON     | PIC18F2XJ10 | PIC18F4XJ10 | 0000 0000                          | 0000 0000                                                                      | uuuu uuuu                       |  |  |  |

| CMCON      | PIC18F2XJ10 | PIC18F4XJ10 | 0000 0111                          | 0000 0111                                                                      | uuuu uuuu                       |  |  |  |

| SPBRGH     | PIC18F2XJ10 | PIC18F4XJ10 | 0000 0000                          | 0000 0000                                                                      | uuuu uuuu                       |  |  |  |

| SPBRG      | PIC18F2XJ10 | PIC18F4XJ10 | 0000 0000                          | 0000 0000                                                                      | uuuu uuuu                       |  |  |  |

| RCREG      | PIC18F2XJ10 | PIC18F4XJ10 | 0000 0000                          | 0000 0000                                                                      | uuuu uuuu                       |  |  |  |

| TXREG      | PIC18F2XJ10 | PIC18F4XJ10 | xxxx xxxx                          | սսսս սսսս                                                                      | uuuu uuuu                       |  |  |  |

| TXSTA      | PIC18F2XJ10 | PIC18F4XJ10 | 0000 0010                          | 0000 0010                                                                      | uuuu uuuu                       |  |  |  |

| RCSTA      | PIC18F2XJ10 | PIC18F4XJ10 | x000 0000                          | 0000 000x                                                                      | uuuu uuuu                       |  |  |  |

| EECON2     | PIC18F2XJ10 | PIC18F4XJ10 | 0000 0000                          | 0000 0000                                                                      | uuuu uuuu                       |  |  |  |

| EECON1     | PIC18F2XJ10 | PIC18F4XJ10 | 0 x00-                             | 0 x00-                                                                         | u uuu-                          |  |  |  |

| IPR3       | PIC18F2XJ10 | PIC18F4XJ10 | 11                                 | 11                                                                             | uu                              |  |  |  |

| PIR3       | PIC18F2XJ10 | PIC18F4XJ10 | 00                                 | 00                                                                             | uu(3)                           |  |  |  |

| PIE3       | PIC18F2XJ10 | PIC18F4XJ10 | 00                                 | 00                                                                             | uu                              |  |  |  |

| IPR2       | PIC18F2XJ10 | PIC18F4XJ10 | 11 11                              | 11 11                                                                          | uu uu                           |  |  |  |

| PIR2       | PIC18F2XJ10 | PIC18F4XJ10 | 0000                               | 00 00                                                                          | uu uu <b>(3)</b>                |  |  |  |

| PIE2       | PIC18F2XJ10 | PIC18F4XJ10 | 00 00                              | 00 00                                                                          | uu uu                           |  |  |  |

| IPR1       | PIC18F2XJ10 | PIC18F4XJ10 | 1111 1111                          | 1111 1111                                                                      | uuuu uuuu                       |  |  |  |

| PIR1       | PIC18F2XJ10 | PIC18F4XJ10 | 0000 0000                          | 0000 0000                                                                      | uuuu uuuu <sup>(3)</sup>        |  |  |  |

| PIE1       | PIC18F2XJ10 | PIC18F4XJ10 | 0000 0000                          | 0000 0000                                                                      | uuuu uuuu                       |  |  |  |

| <b>TABLE 5-2:</b> | INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |

|-------------------|---------------------------------------------------------|

|                   |                                                         |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

3: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

4: See Table 5-1 for Reset value for specific condition.

## 7.4 Erasing Flash Program Memory

The minimum erase block is 1024 bytes. Only through the use of an external programmer, or through ICSP control, can larger blocks of program memory be Bulk Erased. Word Erase in the Flash array is not supported.

When initiating an erase sequence from the microcontroller itself, a block of 1024 bytes of program memory is erased. The Most Significant 7 bits of the TBLPTR<21:10> point to the block being erased. TBLPTR<9:0> are ignored.

The EECON1 register commands the erase operation. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation.

For protection, the write initiate sequence for EECON2 must be used.

A long write is necessary for erasing the internal Flash. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

### 7.4.1 FLASH PROGRAM MEMORY ERASE SEQUENCE

The sequence of events for erasing a block of internal program memory location is:

- 1. Load Table Pointer register with address of the block being erased.

- 2. Set the WREN and FREE bits (EECON1<2,4>) to enable the erase operation.

- 3. Disable interrupts.

- 4. Write 55h to EECON2.

- 5. Write 0AAh to EECON2.

- 6. Set the WR bit. This will begin the erase cycle.

- The CPU will stall for duration of the erase for TIE (see parameter D133B).

- 8. Re-enable interrupts.

| EXAMPLE 7-2: | ERASING A FLASH PROGRAM MEMORY BLOCK |

|--------------|--------------------------------------|

|           | MOVLW | CODE_ADDR_UPPER | ; load TBLPTR with the base   |

|-----------|-------|-----------------|-------------------------------|

|           | MOVWF | TBLPTRU         | ; address of the memory block |

|           | MOVLW | CODE_ADDR_HIGH  |                               |

|           | MOVWF | TBLPTRH         |                               |

|           | MOVLW | CODE_ADDR_LOW   |                               |

|           | MOVWF | TBLPTRL         |                               |

| ERASE_ROW |       |                 |                               |

|           | BSF   | EECON1, WREN    | ; enable write to memory      |

|           | BSF   | EECON1, FREE    | ; enable Erase operation      |

|           | BCF   | INTCON, GIE     | ; disable interrupts          |

| Required  | MOVLW | 55h             |                               |

| Sequence  | MOVWF | EECON2          | ; write 55h                   |

|           | MOVLW | 0AAh            |                               |

|           | MOVWF | EECON2          | ; write OAAh                  |

|           | BSF   | EECON1, WR      | ; start erase (CPU stall)     |

|           | BSF   | INTCON, GIE     | ; re-enable interrupts        |

|           |       |                 |                               |

| R/W-1      | R/W-1                                                          | U-0                                                  | R/W-0            | R/W-0                  | U-0             | R/W-0           | R/W-0  |

|------------|----------------------------------------------------------------|------------------------------------------------------|------------------|------------------------|-----------------|-----------------|--------|

| INT2IP     | INT1IP                                                         | _                                                    | INT2IE           | INT1IE                 | _               | INT2IF          | INT1IF |

| bit 7      |                                                                |                                                      |                  |                        |                 |                 | bit C  |

|            |                                                                |                                                      |                  |                        |                 |                 |        |

| Legend:    |                                                                |                                                      |                  |                        |                 |                 |        |

| R = Reada  | able bit                                                       | W = Writable                                         | bit              | U = Unimplem           | ented bit, read | d as '0'        |        |

| -n = Value | at POR                                                         | '1' = Bit is set                                     |                  | '0' = Bit is clea      | ired            | x = Bit is unkr | Iown   |

| bit 7      |                                                                | External Interr                                      | unt Driarity hit |                        |                 |                 |        |

|            | 1 = High prio<br>0 = Low prior                                 | rity                                                 | αρι Εποπιγ διι   |                        |                 |                 |        |

| bit 6      | <b>INT1IP:</b> INT1<br>1 = High prio<br>0 = Low prior          | ,                                                    | upt Priority bit |                        |                 |                 |        |

| bit 5      | Unimplemen                                                     | ted: Read as '                                       | כ'               |                        |                 |                 |        |

| bit 4      | INT2IE: INT2                                                   | External Interr                                      | upt Enable bit   |                        |                 |                 |        |

|            |                                                                | the INT2 exterr<br>the INT2 exter                    |                  |                        |                 |                 |        |

| bit 3      | 1 = Enables                                                    | External Interr<br>the INT1 exterr<br>the INT1 exter | nal interrupt    |                        |                 |                 |        |

| bit 2      |                                                                | ted: Read as '                                       | •                |                        |                 |                 |        |

| bit 1      | -                                                              | External Interr                                      |                  |                        |                 |                 |        |

|            | 1 = The INT2                                                   |                                                      | upt occurred (   | must be cleared<br>cur | in software)    |                 |        |

| bit 0      | INT1IF: INT1                                                   | External Interr                                      | upt Flag bit     |                        |                 |                 |        |

|            |                                                                | external interr<br>external interr                   |                  | must be cleared<br>cur | in software)    |                 |        |

| Note:      | Interrupt flag bits<br>enable bit or the<br>are clear prior to | global interrupt                                     | enable bit. Us   | er software shou       | uld ensure the  | appropriate int |        |

### REGISTER 9-3: INTCON3: INTERRUPT CONTROL REGISTER 3

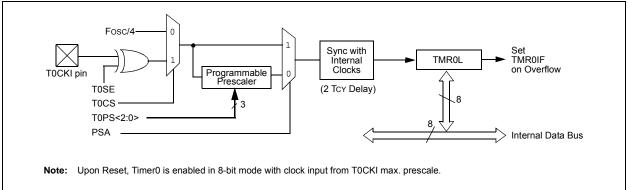

# 11.1 Timer0 Operation

Timer0 can operate as either a timer or a counter; the mode is selected with the TOCS bit (TOCON<5>). In Timer mode (TOCS = 0), the module increments on every clock by default unless a different prescaler value is selected (see **Section 11.3 "Prescaler"**). If the TMR0 register is written to, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

The Counter mode is selected by setting the T0CS bit (= 1). In this mode, Timer0 increments either on every rising or falling edge of pin RB5/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit, T0SE (T0CON<4>); clearing this bit selects the rising edge. Restrictions on the external clock input are discussed below.

An external clock source can be used to drive Timer0; however, it must meet certain requirements to ensure that the external clock can be synchronized with the internal phase clock (Tosc). There is a delay between synchronization and the onset of incrementing the timer/counter.

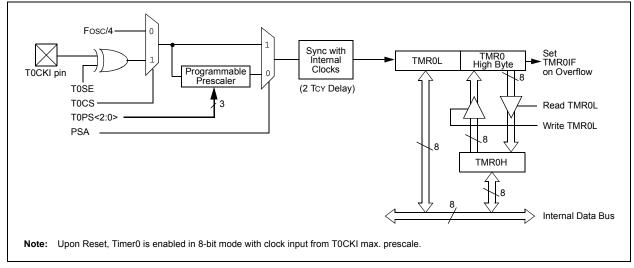

### 11.2 Timer0 Reads and Writes in 16-Bit Mode

TMR0H is not the actual high byte of Timer0 in 16-bit mode. It is actually a buffered version of the real high byte of Timer0 which is not directly readable nor writable (refer to Figure 11-2). TMR0H is updated with the contents of the high byte of Timer0 during a read of TMR0L. This provides the ability to read all 16 bits of Timer0 without having to verify that the read of the high and low byte were valid, due to a rollover between successive reads of the high and low byte.

Similarly, a write to the high byte of Timer0 must also take place through the TMR0H Buffer register. The high byte is updated with the contents of TMR0H when a write occurs to TMR0L. This allows all 16 bits of Timer0 to be updated at once.

### FIGURE 11-1: TIMER0 BLOCK DIAGRAM (8-BIT MODE)

### FIGURE 11-2: TIMER0 BLOCK DIAGRAM (16-BIT MODE)

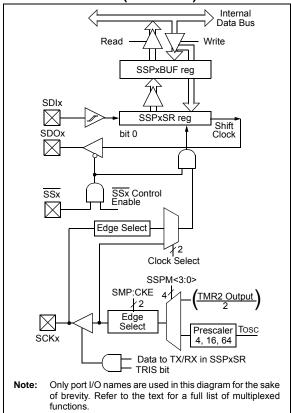

# 16.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

### 16.1 Master SSP (MSSP) Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

- Full Master mode

- Slave mode (with general address call)

The I<sup>2</sup>C interface supports the following modes in hardware:

- Master mode

- Multi-Master mode

- · Slave mode

PIC18F24J10/25J10 (28-pin) devices have one MSSP module designated as MSSP1. PIC18F44J10/45J10 (40/44-pin) devices have two MSSP modules, designated as MSSP1 and MSSP2. Each module operates independently of the other.

| Note: | Throughout this section, generic refer-<br>ences to an MSSP module in any of its<br>operating modes may be interpreted as<br>being equally applicable to MSSP1 or<br>MSSP2. Register names and module I/O<br>signals use the generic designator 'x' to<br>indicate the use of a numeral to distinguish<br>a particular module, when required.<br>Control bit names are not individuated. |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

## 16.2 Control Registers

Each MSSP module has three associated control registers. These include a status register (SSPxSTAT) and two control registers (SSPxCON1 and SSPxCON2). The use of these registers and their individual configuration bits differ significantly depending on whether the MSSP module is operated in SPI or  $I^2C$  mode.

Additional details are provided under the individual sections.

Note: Disabling the MSSP module by clearing the SSPEN (SSPxCON1<5>) bit may not reset the module. It is recommended to clear the SSPxSTAT, SSPxCON1 and SSPxCON2 registers and select the mode prior to setting the SSPEN bit to enable the MSSP module. Note: In devices with more than one MSSP module, it is very important to pay close attention to SSPxCON register names. SSP1CON1 and SSP1CON2 control different operational aspects of the same module, while SSP1CON1 and SSP2CON1 control the same features for two different modules.

## 16.3 SPI Mode

The SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDOx) RC5/SDO1 or RD2/PSP2/SDO2

- Serial Data In (SDIx) RC4/SDI1/SDA1 or RD1/PSP1/SDI2/SDA2

- Serial Clock (SCKx) RC3/SCK1/SCL1 or RD0/PSP0/SCK2/SCL2

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SSx) – RA5/AN4/SS1/C2OUT or RD3/PSP3/SS2

Figure 16-1 shows the block diagram of the MSSP module when operating in SPI mode.

#### FIGURE 16-1: MSSP BLOCK DIAGRAM (SPI MODE)

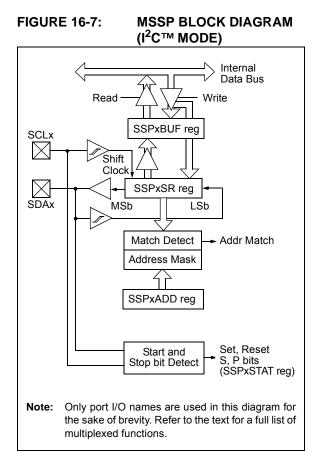

# 16.4 I<sup>2</sup>C Mode

The MSSP module in I<sup>2</sup>C mode fully implements all master and slave functions (including general call support) and provides interrupts on Start and Stop bits in hardware to determine a free bus (multi-master function). The MSSP module implements the standard mode specifications, as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer:

- Serial clock (SCLx) RC3/SCK1/SCL1 or RD6/SCK2/SCL2

- Serial data (SDAx) RC4/SDI1/SDA1 or RD5/SDI2/SDA2

The user must configure these pins as inputs by setting the associated TRIS bits.

### 16.4.1 REGISTERS

The MSSP module has six registers for  $\mathsf{I}^2\mathsf{C}$  operation. These are:

- MSSP Control Register 1 (SSPxCON1)

- MSSP Control Register 2 (SSPxCON2)

- MSSP Status Register (SSPxSTAT)

- Serial Receive/Transmit Buffer Register (SSPxBUF)

- MSSP Shift Register (SSPxSR) Not directly accessible

- MSSP Address Register (SSPxADD)

SSPxCON1, SSPxCON2 and SSPxSTAT are the control and status registers in I<sup>2</sup>C mode operation. The SSPxCON1 and SSPxCON2 registers are readable and writable. The lower 6 bits of the SSPxSTAT are read-only. The upper two bits of the SSPxSTAT are read/write.

Many of the bits in SSPxCON2 assume different functions, depending on whether the module is operating in Master or Slave mode; bits<5:2> also assume different names in Slave mode. The different aspects of SSPxCON2 are shown in Register 16-5 (for Master mode) and Register 16-6 (Slave mode).

SSPxSR is the shift register used for shifting data in or out. SSPxBUF is the buffer register to which data bytes are written to or read from.

SSPxADD register holds the slave device address when the MSSP is configured in I<sup>2</sup>C Slave mode. When the MSSP is configured in Master mode, the lower seven bits of SSPxADD act as the Baud Rate Generator reload value.

In receive operations, SSPxSR and SSPxBUF together create a double-buffered receiver. When SSPxSR receives a complete byte, it is transferred to SSPxBUF and the SSPxIF interrupt is set.

During transmission, the SSPxBUF is not double-buffered. A write to SSPxBUF will write to both SSPxBUF and SSPxSR.

Note: Disabling the MSSP module by clearing the SSPEN (SSPxCON1<5>) bit may not reset the module. It is recommended to clear the SSPxSTAT, SSPxCON1 and SSPxCON2 registers and select the mode prior to setting the SSPEN bit to enable the MSSP module.

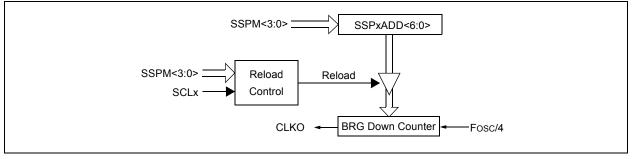

### 16.4.7 BAUD RATE

In I<sup>2</sup>C Master mode, the Baud Rate Generator (BRG) reload value is placed in the lower 7 bits of the SSPxADD register (Figure 16-17). When a write occurs to SSPxBUF, the Baud Rate Generator will automatically begin counting. The BRG counts down to '0' and stops until another reload has taken place. The BRG count is decremented twice per instruction cycle (TCY) on the Q2 and Q4 clocks. In I<sup>2</sup>C Master mode, the BRG is reloaded automatically.

Once the given operation is complete (i.e., transmission of the last data bit is followed by ACK), the internal clock will automatically stop counting and the SCLx pin will remain in its last state.

Table 16-3 demonstrates clock rates based on instruction cycles and the BRG value loaded into SSPxADD.

### 16.4.7.1 Baud Rate and Module Interdependence

Because MSSP1 and MSSP2 are independent, they can operate simultaneously in I<sup>2</sup>C Master mode at different baud rates. This is done by using different BRG reload values for each module.

Because this mode derives its basic clock source from the system clock, any changes to the clock will affect both modules in the same proportion. It may be possible to change one or both baud rates back to a previous value by changing the BRG reload value.

### FIGURE 16-17: BAUD RATE GENERATOR BLOCK DIAGRAM

### TABLE 16-3: I<sup>2</sup>C<sup>™</sup> CLOCK RATE w/BRG

| Fcy    | Fcy * 2 | BRG Value | Fsc∟<br>(2 Rollovers of BRG) |

|--------|---------|-----------|------------------------------|

| 10 MHz | 20 MHz  | 18h       | 400 kHz <sup>(1)</sup>       |

| 10 MHz | 20 MHz  | 1Fh       | 312.5 kHz                    |

| 10 MHz | 20 MHz  | 63h       | 100 kHz                      |

| 4 MHz  | 8 MHz   | 09h       | 400 kHz <sup>(1)</sup>       |

| 4 MHz  | 8 MHz   | 0Ch       | 308 kHz                      |

| 4 MHz  | 8 MHz   | 27h       | 100 kHz                      |

| 1 MHz  | 2 MHz   | 02h       | 333 kHz <sup>(1)</sup>       |

| 1 MHz  | 2 MHz   | 09h       | 100 kHz                      |

| 1 MHz  | 2 MHz   | 00h       | 1 MHz <sup>(1)</sup>         |

**Note 1:** The I<sup>2</sup>C<sup>™</sup> interface does not conform to the 400 kHz I<sup>2</sup>C specification (which applies to rates greater than 100 kHz) in all details, but may be used with care where higher rates are required by the application.

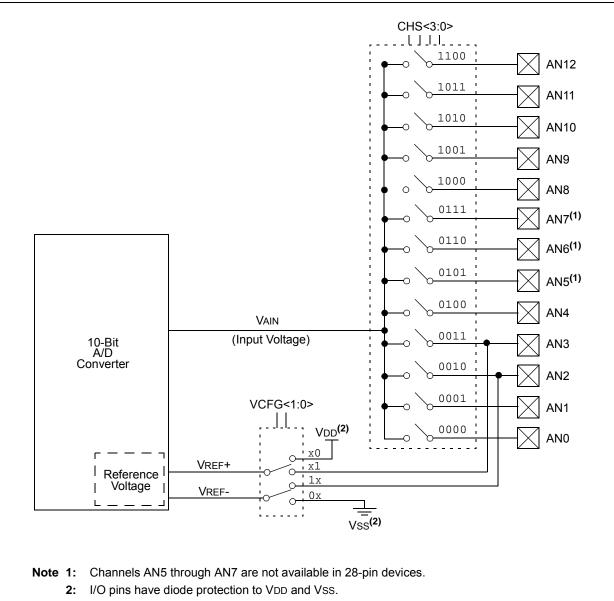

The analog reference voltage is software selectable to either the device's positive and negative supply voltage (VDD and Vss), or the voltage level on the RA3/AN3/ VREF+ and RA2/AN2/VREF-/CVREF pins.

The A/D converter has a unique feature of being able to operate while the device is in Sleep mode. To operate in Sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

The output of the sample and hold is the input into the converter, which generates the result via successive approximation.

### FIGURE 18-1: A/D BLOCK DIAGRAM

A device Reset forces all registers to their Reset state. This forces the A/D module to be turned off and any conversion in progress is aborted.

Each port pin associated with the A/D converter can be configured as an analog input, or as a digital I/O. The ADRESH and ADRESL registers contain the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the ADRESH:ADRESL register pair, the GO/DONE bit (ADCON0 register) is cleared and A/D Interrupt Flag bit, ADIF, is set. The block diagram of the A/D module is shown in Figure 18-1.

### REGISTER 21-5: CONFIG3L: CONFIGURATION REGISTER 3 LOW (BYTE ADDRESS 300004h)

| U-0          | U-0   | U-0          | U-0     | U-0          | U-0             | U-0             | U-0   |

|--------------|-------|--------------|---------|--------------|-----------------|-----------------|-------|

| _            | —     | —            | —       | —            |                 | —               | —     |

| bit 7        |       |              |         |              |                 |                 | bit 0 |

|              |       |              |         |              |                 |                 |       |

| Legend:      |       |              |         |              |                 |                 |       |

|              |       |              |         |              |                 |                 |       |

| R = Readable | e bit | WO = Write C | nce bit | U = Unimplem | ented bit, read | <b>l as</b> '0' |       |

bit 7-0 Unimplemented: Read as '0'

# REGISTER 21-6: CONFIG3H: CONFIGURATION REGISTER 3 HIGH (BYTE ADDRESS 300005h)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/WO-1 |

|-------|-----|-----|-----|-----|-----|-----|--------|

| (1)   | (1) | (1) | (1) | —   | —   |     | CCP2MX |

| bit 7 |     |     |     |     |     |     | bit 0  |

| Legend:                |                     |                     |                      |

|------------------------|---------------------|---------------------|----------------------|

| R = Readable bit       | WO = Write Once bit | U = Unimplemented b | bit, read as '0'     |

| -n = Value when device | is unprogrammed     | '1' = Bit is set    | '0' = Bit is cleared |

| bit 7-1 | Unimplemented: Read as ' | 1,' <b>(1)</b> |

|---------|--------------------------|----------------|

|         |                          |                |

bit 0 CCP2MX: CCP2 MUX bit

1 = CCP2 is multiplexed with RC1

0 = CCP2 is multiplexed with RB3

**Note 1:** The value of these bits in program memory should always be '1'. This ensures that the location is executed as a NOP if it is accidentally executed.

### TABLE 22-2: PIC18FXXXX INSTRUCTION SET

| Mnemonic,<br>Operands |                                 | Description                              | Cycles     | 16-Bit Instruction Word |      |      | Status |                 |            |

|-----------------------|---------------------------------|------------------------------------------|------------|-------------------------|------|------|--------|-----------------|------------|

|                       |                                 | Description                              |            | MSb                     |      |      | LSb    | Affected        | Notes      |

| BYTE-ORIE             | ENTED O                         | OPERATIONS                               |            |                         |      |      |        |                 |            |

| ADDWF                 | f, d, a                         | Add WREG and f                           | 1          | 0010                    | 01da | ffff | ffff   | C, DC, Z, OV, N | 1, 2       |

| ADDWFC                | f, d, a                         | Add WREG and Carry bit to f              | 1          | 0010                    | 00da | ffff | ffff   | C, DC, Z, OV, N | 1, 2       |

| ANDWF                 | f, d, a                         | AND WREG with f                          | 1          | 0001                    | 01da | ffff | ffff   | Z, N            | 1,2        |

| CLRF                  | f, a                            | Clear f                                  | 1          | 0110                    | 101a | ffff | ffff   | Z               | 2          |

| COMF                  | f, d, a                         | Complement f                             | 1          | 0001                    | 11da | ffff | ffff   | Z, N            | 1, 2       |

| CPFSEQ                | f, a                            | Compare f with WREG, Skip =              | 1 (2 or 3) | 0110                    | 001a | ffff | ffff   | None            | 4          |

| CPFSGT                | f, a                            | Compare f with WREG, Skip >              | 1 (2 or 3) | 0110                    | 010a | ffff | ffff   | None            | 4          |

| CPFSLT                | f, a                            | Compare f with WREG, Skip <              | 1 (2 or 3) | 0110                    | 000a | ffff | ffff   | None            | 1, 2       |

| DECF                  | f, d, a                         | Decrement f                              | 1          | 0000                    | 01da | ffff | ffff   | C, DC, Z, OV, N | 1, 2, 3, 4 |

| DECFSZ                | f, d, a                         | Decrement f, Skip if 0                   | 1 (2 or 3) | 0010                    | 11da | ffff | ffff   | None            | 1, 2, 3, 4 |

| DCFSNZ                | f, d, a                         | Decrement f, Skip if Not 0               | 1 (2 or 3) | 0100                    | 11da | ffff | ffff   | None            | 1, 2       |

| INCF                  | f, d, a                         | Increment f                              | 1          | 0010                    | 10da | ffff | ffff   | C, DC, Z, OV, N | 1, 2, 3, 4 |

| INCFSZ                | f, d, a                         | Increment f, Skip if 0                   | 1 (2 or 3) | 0011                    | 11da | ffff | ffff   | None            | 4          |

| INFSNZ                | f, d, a                         | Increment f, Skip if Not 0               | 1 (2 or 3) | 0100                    | 10da | ffff | ffff   | None            | 1, 2       |

| IORWF                 | f, d, a                         | Inclusive OR WREG with f                 | 1          | 0001                    | 00da | ffff | ffff   | Z, N            | 1, 2       |

| MOVF                  | f, d, a                         | Move f                                   | 1          | 0101                    | 00da | ffff | ffff   | Z, N            | 1          |

| MOVFF                 | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st Word | 2          | 1100                    | ffff | ffff | ffff   | None            |            |

|                       |                                 | f <sub>d</sub> (destination) 2nd Word    |            | 1111                    | ffff | ffff | ffff   |                 |            |

| MOVWF                 | f, a                            | Move WREG to f                           | 1          | 0110                    | 111a | ffff | ffff   | None            |            |

| MULWF                 | f, a                            | Multiply WREG with f                     | 1          | 0000                    | 001a | ffff | ffff   | None            | 1, 2       |

| NEGF                  | f, a                            | Negate f                                 | 1          | 0110                    | 110a | ffff | ffff   | C, DC, Z, OV, N |            |

| RLCF                  | f, d, a                         | Rotate Left f through Carry              | 1          | 0011                    | 01da | ffff | ffff   | C, Z, N         | 1, 2       |

| RLNCF                 | f, d, a                         | Rotate Left f (No Carry)                 | 1          | 0100                    | 01da | ffff | ffff   | Z, N            |            |

| RRCF                  | f, d, a                         | Rotate Right f through Carry             | 1          | 0011                    | 00da | ffff | ffff   | C, Z, N         |            |

| RRNCF                 | f, d, a                         | Rotate Right f (No Carry)                | 1          | 0100                    | 00da | ffff | ffff   | Z, N            |            |

| SETF                  | f, a                            | Set f                                    | 1          | 0110                    | 100a | ffff | ffff   | None            | 1, 2       |

| SUBFWB                | f, d, a                         | Subtract f from WREG with<br>Borrow      | 1          | 0101                    | 01da | ffff | ffff   | C, DC, Z, OV, N |            |

| SUBWF                 | f, d, a                         | Subtract WREG from f                     | 1          | 0101                    | 11da | ffff | ffff   | C, DC, Z, OV, N | 1, 2       |

| SUBWFB                | f, d, a                         | Subtract WREG from f with                | 1          | 0101                    | 10da | ffff | ffff   | C, DC, Z, OV, N |            |

|                       |                                 | Borrow                                   |            |                         |      |      |        |                 |            |

| SWAPF                 | f, d, a                         | Swap Nibbles in f                        | 1          | 0011                    | 10da | ffff | ffff   | None            | 4          |

| TSTFSZ                | f, a                            | Test f, Skip if 0                        | 1 (2 or 3) | 0110                    | 011a | ffff | ffff   | None            | 1, 2       |

| XORWF                 | f, d, a                         | Exclusive OR WREG with f                 | 1 ′        | 0001                    | 10da | ffff | ffff   | Z, N            |            |

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

3: If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

| BCF                                          | Bit Clear f                                                                                                                                                                                                                                                                                                                                                                                  | BN                                                                                          | Branch if Negative                                                                                                                                                                                                                                                                                        |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                      | BCF f, b {,a}                                                                                                                                                                                                                                                                                                                                                                                | Syntax:                                                                                     | BN n                                                                                                                                                                                                                                                                                                      |

| Operands:                                    | $0 \leq f \leq 255$                                                                                                                                                                                                                                                                                                                                                                          | Operands:                                                                                   | $-128 \le n \le 127$                                                                                                                                                                                                                                                                                      |

|                                              | $\begin{array}{l} 0 \leq b \leq 7 \\ a \in [0, 1] \end{array}$                                                                                                                                                                                                                                                                                                                               | Operation:                                                                                  | if Negative bit is '1',<br>(PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                                                                                                 |

| Operation:                                   | $0 \rightarrow f \le b >$                                                                                                                                                                                                                                                                                                                                                                    | Status Affected:                                                                            | None                                                                                                                                                                                                                                                                                                      |

| Status Affected:                             | None                                                                                                                                                                                                                                                                                                                                                                                         | Encoding:                                                                                   | 1110 0110 nnnn nnnn                                                                                                                                                                                                                                                                                       |

| Encoding:<br>Description:                    | 1001bbbaffffffffBit 'b' in register 'f' is cleared.If 'a' is '0', the Access Bank is selected.If 'a' is '1', the BSR is used to select theGPR bank (default).If 'a' is '0' and the extended instructionset is enabled, this instruction operatesin Indexed Literal Offset Addressingmode whenever $f \le 95$ (5Fh). SeeSection 22.2.3 "Byte-Oriented andBit-Oriented Instructions in Indexed | Description:<br>Words:<br>Cycles:                                                           | If the Negative bit is '1', then the<br>program will branch.<br>The 2's complement number, '2n', is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>two-cycle instruction.<br>1<br>1(2) |

|                                              | Literal Offset Mode" for details.                                                                                                                                                                                                                                                                                                                                                            | Q Cycle Activity:                                                                           |                                                                                                                                                                                                                                                                                                           |

| Words:                                       | 1                                                                                                                                                                                                                                                                                                                                                                                            | If Jump:                                                                                    |                                                                                                                                                                                                                                                                                                           |

| Cycles:                                      | 1                                                                                                                                                                                                                                                                                                                                                                                            | Q1                                                                                          | Q2 Q3 Q4                                                                                                                                                                                                                                                                                                  |

| Q Cycle Activity:                            |                                                                                                                                                                                                                                                                                                                                                                                              | Decode                                                                                      | Read literal Process Write to PC<br>'n' Data                                                                                                                                                                                                                                                              |

| Q1<br>Decode                                 | Q2 Q3 Q4<br>Read Process Write<br>register 'f' Data register 'f'                                                                                                                                                                                                                                                                                                                             | No<br>operation                                                                             | No No No<br>operation operation                                                                                                                                                                                                                                                                           |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                              | If No Jump:                                                                                 | 02 02 04                                                                                                                                                                                                                                                                                                  |

| <u>Example</u> :<br>Before Instruc<br>FLAG_R |                                                                                                                                                                                                                                                                                                                                                                                              | Q1<br>Decode                                                                                | Q2Q3Q4Read literalProcessNo'n'Dataoperation                                                                                                                                                                                                                                                               |

| After Instruction<br>FLAG_R                  | n                                                                                                                                                                                                                                                                                                                                                                                            | Example:<br>Before Instruct<br>PC<br>After Instructio<br>If Negati<br>PC<br>If Negati<br>PC | = address (HERE)<br>on<br>ve = 1;<br>= address (Jump)                                                                                                                                                                                                                                                     |

| RETURN            | Return fro                         | om Subrouti                           | ne           | RLCF             | Rotate Le                                              | eft f through                        | n Carry                  |

|-------------------|------------------------------------|---------------------------------------|--------------|------------------|--------------------------------------------------------|--------------------------------------|--------------------------|

| Syntax:           | RETURN                             | {s}                                   |              | Syntax:          | RLCF f                                                 | {,d {,a}}                            |                          |

| Operands:         | <b>S</b> ∈ [0,1]                   |                                       |              | Operands:        | $0 \leq f \leq 255$                                    |                                      |                          |

| Operation:        | $(TOS) \rightarrow P$              | C;                                    |              |                  | $d \in [0, 1]$                                         |                                      |                          |

|                   | if $s = 1$ ,                       |                                       |              | Onenetien        | $\mathbf{a} \in [0, 1]$                                |                                      |                          |

|                   | $(WS) \rightarrow W,$<br>(STATUSS) | $\rightarrow$ STATUS,                 |              | Operation:       | $(f < f >) \rightarrow d$<br>$(f < 7 >) \rightarrow C$ | est <n +="" 1="">,</n>               |                          |

|                   | $(BSRS) \rightarrow$               | BSR,                                  |              |                  | $(C) \rightarrow dest$                                 |                                      |                          |

|                   |                                    | CLATH are un                          | changed      | Status Affected: | C, N, Z                                                |                                      |                          |

| Status Affected:  | None                               | I                                     |              | Encoding:        | 0011                                                   | 01da ff                              | ff ffff                  |

| Encoding:         | 0000                               | 0000 000                              | 001s         | Description:     |                                                        |                                      | 'f' are rotated          |

| Description:      |                                    | n subroutine. T                       |              |                  |                                                        | ne left through                      |                          |

|                   |                                    | the top of the top the to the program |              |                  | •                                                      | 6 '0', the resul<br>1', the result i | s stored back            |

|                   | 's'= 1, the c                      | contents of the                       | shadow       |                  | in register '                                          | . ,                                  |                          |

|                   | -                                  | /S, STATUSS<br>into their corre       |              |                  |                                                        | he Access Ba                         | ank is<br>3SR is used to |

|                   |                                    | I, STATUS and                         |              |                  |                                                        | GPR bank (de                         |                          |

|                   |                                    | pdate of these                        | e registers  |                  |                                                        |                                      | led instruction          |

|                   | occurs (def                        | ault).                                |              |                  |                                                        | led, this instru<br>Indexed Lite     |                          |

| Words:            | 1                                  |                                       |              |                  | Addressing                                             | mode whene                           | ever                     |

| Cycles:           | 2                                  |                                       |              |                  |                                                        | ). See Sectio<br>nted and Bit-       |                          |

| Q Cycle Activity: | 00                                 | 00                                    | 04           |                  |                                                        |                                      | Literal Offset           |

| Q1<br>Decode      | Q2<br>No                           | Q3<br>Process                         | Q4<br>POP PC |                  | Mode" for                                              | details.                             |                          |

| Decoude           | operation                          | Data                                  | from stack   |                  | C C                                                    | <ul> <li>register</li> </ul>         | erf <mark>≁</mark>       |

| No                | No                                 | No                                    | No           |                  |                                                        |                                      |                          |

| operation         | operation                          | operation                             | operation    | Words:           | 1                                                      |                                      |                          |

|                   |                                    |                                       |              | Cycles:          | 1                                                      |                                      |                          |

| Example:          | RETURN                             |                                       |              | Q Cycle Activity |                                                        | 00                                   | 04                       |

| After Instruc     |                                    |                                       |              | Q1<br>Decode     | Q2<br>Read                                             | Q3<br>Process                        | Q4<br>Write to           |

| PC =              |                                    |                                       |              | Decode           | register 'f'                                           | Data                                 | destination              |

|                   |                                    |                                       |              |                  | · -                                                    |                                      |                          |

|                   |                                    |                                       |              | Example:         | RLCF                                                   | REG, 0,                              | 0                        |

|                   |                                    |                                       |              | Before Instr     | uction                                                 |                                      |                          |

|                   |                                    |                                       |              | REG<br>C         | = 1110 C<br>= 0                                        | 110                                  |                          |

|                   |                                    |                                       |              | After Instruc    |                                                        |                                      |                          |

|                   |                                    |                                       |              | REG<br>W         | = 1110 C<br>= 1100 1                                   |                                      |                          |

|                   |                                    |                                       |              | С                | = 1                                                    |                                      |                          |

|                   |                                    |                                       |              |                  |                                                        |                                      |                          |

|                   |                                    |                                       |              |                  |                                                        |                                      |                          |

|                   |                                    |                                       |              |                  |                                                        |                                      |                          |

|                   |                                    |                                       |              |                  |                                                        |                                      |                          |

# 22.2.5 SPECIAL CONSIDERATIONS WITH MICROCHIP MPLAB<sup>®</sup> IDE TOOLS

The latest versions of Microchip's software tools have been designed to fully support the extended instruction set of the PIC18F45J10 family of devices. This includes the MPLAB C18 C compiler, MPASM assembly language and MPLAB Integrated Development Environment (IDE).

When selecting a target device for software development, MPLAB IDE will automatically set default Configuration bits for that device. The default setting for the XINST Configuration bit is '0', disabling the extended instruction set and Indexed Literal Offset Addressing mode. For proper execution of applications developed to take advantage of the extended instruction set, XINST must be set during programming.

To develop software for the extended instruction set, the user must enable support for the instructions and the Indexed Addressing mode in their language tool(s). Depending on the environment being used, this may be done in several ways:

- A menu option, or dialog box within the environment, that allows the user to configure the language tool and its settings for the project

- · A command line option

- · A directive in the source code

These options vary between different compilers, assemblers and development environments. Users are encouraged to review the documentation accompanying their development systems for the appropriate information.

### 23.7 MPLAB ICE 2000 High-Performance In-Circuit Emulator

The MPLAB ICE 2000 In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PIC microcontrollers. Software control of the MPLAB ICE 2000 In-Circuit Emulator is advanced by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The architecture of the MPLAB ICE 2000 In-Circuit Emulator allows expansion to support new PIC microcontrollers.

The MPLAB ICE 2000 In-Circuit Emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows<sup>®</sup> 32-bit operating system were chosen to best make these features available in a simple, unified application.

# 23.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The MPLAB REAL ICE probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with the popular MPLAB ICD 2 system (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

MPLAB REAL ICE is field upgradeable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added, such as software breakpoints and assembly code trace. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, real-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 23.9 MPLAB ICD 2 In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD 2, is a powerful, low-cost, run-time development tool, connecting to the host PC via an RS-232 or high-speed USB interface. This tool is based on the Flash PIC MCUs and can be used to develop for these and other PIC MCUs and dsPIC DSCs. The MPLAB ICD 2 utilizes the in-circuit debugging capability built into the Flash devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) protocol, offers costeffective, in-circuit Flash debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by setting breakpoints, single stepping and watching variables, and CPU status and peripheral registers. Running at full speed enables testing hardware and applications in real time. MPLAB ICD 2 also serves as a development programmer for selected PIC devices.

# 23.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an SD/MMC card for file storage and secure data applications.

NOTES:

| TIME  | er0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Associated Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 117                                                                                                                                                            |

|       | Clock Source Select (T0CS Bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                |

|       | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                |