Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

EXF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 21                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 10x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf24j10-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

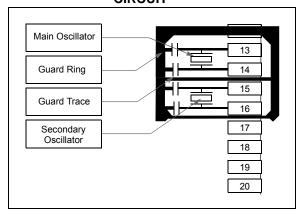

#### 2.6 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 3.0** "Oscillator Configurations" for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-4.

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

#### FIGURE 2-4: SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

#### 2.7 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1 k $\Omega$  to 10 k $\Omega$  resistor to Vss on unused pins and drive the output to logic low.

NOTES:

### 4.0 POWER-MANAGED MODES

The PIC18F45J10 family devices provide the ability to manage power consumption by simply managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. For the sake of managing power in an application, there are three primary modes of operation:

- Run mode

- Idle mode

- · Sleep mode

These modes define which portions of the device are clocked and at what speed. The Run and Idle modes may use any of the three available clock sources (primary, secondary or internal oscillator block); the Sleep mode does not use a clock source.

The power-managed modes include several power-saving features offered on previous PIC<sup>®</sup> microcontrollers. One is the clock switching feature, offered in other PIC18 devices, allowing the controller to use the Timer1 oscillator in place of the primary oscillator. Also included is the Sleep mode, offered by all PIC microcontrollers, where all device clocks are stopped.

#### 4.1 Selecting Power-Managed Modes

Selecting a power-managed mode requires two decisions: if the CPU is to be clocked or not and which clock source is to be used. The IDLEN bit (OSCCON<7>) controls CPU clocking, while the SCS<1:0> bits (OSCCON<1:0>) select the clock source. The individual modes, bit settings, clock sources and affected modules are summarized in Table 4-1.

#### 4.1.1 CLOCK SOURCES

The SCS<1:0> bits allow the selection of one of three clock sources for power-managed modes. They are:

- the primary clock, as defined by the FOSC<1:0> Configuration bits

- the secondary clock (Timer1 oscillator)

- · the internal oscillator

#### 4.1.2 ENTERING POWER-MANAGED MODES

Switching from one power-managed mode to another begins by loading the OSCCON register. The SCS<1:0> bits select the clock source and determine which Run or Idle mode is to be used. Changing these bits causes an immediate switch to the new clock source, assuming that it is running. The switch may also be subject to clock transition delays. These are discussed in **Section 4.1.3 "Clock Transitions and Status Indicators"** and subsequent sections.

Entry to the power-managed Idle or Sleep modes is triggered by the execution of a SLEEP instruction. The actual mode that results depends on the status of the IDLEN bit.

Depending on the current mode and the mode being switched to, a change to a power-managed mode does not always require setting all of these bits. Many transitions may be done by changing the oscillator select bits, or changing the IDLEN bit, prior to issuing a SLEEP instruction. If the IDLEN bit is already configured correctly, it may only be necessary to perform a SLEEP instruction to switch to the desired mode.

| Mode     | oso                     | CON bits | Modul         | e Clocking | Ausilable Clask and Ossillator Source                             |  |  |  |  |  |

|----------|-------------------------|----------|---------------|------------|-------------------------------------------------------------------|--|--|--|--|--|

|          | IDLEN<7> <sup>(1)</sup> | SCS<1:0> | CPU Periphera |            | Available Clock and Oscillator Source                             |  |  |  |  |  |

| Sleep    | 0                       | N/A      | Off           | Off        | None – All clocks are disabled                                    |  |  |  |  |  |

| PRI_RUN  | N/A                     | 10       | Clocked       | Clocked    | Primary – HS, EC;<br>this is the normal full-power execution mode |  |  |  |  |  |

| SEC_RUN  | N/A                     | 01       | Clocked       | Clocked    | Secondary – Timer1 Oscillator                                     |  |  |  |  |  |

| RC_RUN   | N/A                     | 11       | Clocked       | Clocked    | Internal Oscillator                                               |  |  |  |  |  |

| PRI_IDLE | 1                       | 10       | Off           | Clocked    | Primary – HS, EC                                                  |  |  |  |  |  |

| SEC_IDLE | 1                       | 01       | Off           | Clocked    | Secondary – Timer1 Oscillator                                     |  |  |  |  |  |

| RC_IDLE  | 1                       | 11       | Off           | Clocked    | Internal Oscillator                                               |  |  |  |  |  |

TABLE 4-1: POWER-MANAGED MODES

**Note 1:** IDLEN reflects its value when the **SLEEP** instruction is executed.

#### 6.3.4 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. SFRs start at the top of data memory (FFFh) and extend downward to occupy the top half of Bank 15 (F80h to FFFh). A list of these registers is given in Table 6-2 and Table 6-3. The SFRs can be classified into two sets: those associated with the "core" device functionality (ALU, Resets and interrupts) and those related to the peripheral functions. The Reset and Interrupt registers are described in their respective chapters, while the ALU's STATUS register is described later in this section. Registers related to the operation of a peripheral feature are described in the chapter for that peripheral.

The SFRs are typically distributed among the peripherals whose functions they control. Unused SFR locations are unimplemented and read as '0's.

#### TABLE 6-2: SPECIAL FUNCTION REGISTER MAP FOR PIC18F45J10 FAMILY DEVICES

| Address | Name                    | Address | Name                    | Address | Name                    | Address | Name                    |

|---------|-------------------------|---------|-------------------------|---------|-------------------------|---------|-------------------------|

| FFFh    | TOSU                    | FDFh    | INDF2 <sup>(1)</sup>    | FBFh    | CCPR1H                  | F9Fh    | IPR1                    |

| FFEh    | TOSH                    | FDEh    | POSTINC2 <sup>(1)</sup> | FBEh    | CCPR1L                  | F9Eh    | PIR1                    |

| FFDh    | TOSL                    | FDDh    | POSTDEC2 <sup>(1)</sup> | FBDh    | CCP1CON                 | F9Dh    | PIE1                    |

| FFCh    | STKPTR                  | FDCh    | PREINC2 <sup>(1)</sup>  | FBCh    | CCPR2H                  | F9Ch    | (2)                     |

| FFBh    | PCLATU                  | FDBh    | PLUSW2 <sup>(1)</sup>   | FBBh    | CCPR2L                  | F9Bh    | (2)                     |

| FFAh    | PCLATH                  | FDAh    | FSR2H                   | FBAh    | CCP2CON                 | F9Ah    | (2)                     |

| FF9h    | PCL                     | FD9h    | FSR2L                   | FB9h    | (2)                     | F99h    | (2)                     |

| FF8h    | TBLPTRU                 | FD8h    | STATUS                  | FB8h    | BAUDCON                 | F98h    | (2)                     |

| FF7h    | TBLPTRH                 | FD7h    | TMR0H                   | FB7h    | ECCP1DEL <sup>(3)</sup> | F97h    | (2)                     |

| FF6h    | TBLPTRL                 | FD6h    | TMR0L                   | FB6h    | ECCP1AS <sup>(3)</sup>  | F96h    | TRISE <sup>(3)</sup>    |

| FF5h    | TABLAT                  | FD5h    | TOCON                   | FB5h    | CVRCON                  | F95h    | TRISD <sup>(3)</sup>    |

| FF4h    | PRODH                   | FD4h    | (2)                     | FB4h    | CMCON                   | F94h    | TRISC                   |

| FF3h    | PRODL                   | FD3h    | OSCCON                  | FB3h    | (2)                     | F93h    | TRISB                   |

| FF2h    | INTCON                  | FD2h    | (2)                     | FB2h    | (2)                     | F92h    | TRISA                   |

| FF1h    | INTCON2                 | FD1h    | WDTCON                  | FB1h    | (2)                     | F91h    | (2)                     |

| FF0h    | INTCON3                 | FD0h    | RCON                    | FB0h    | SPBRGH                  | F90h    | (2)                     |

| FEFh    | INDF0 <sup>(1)</sup>    | FCFh    | TMR1H                   | FAFh    | SPBRG                   | F8Fh    | (2)                     |

| FEEh    | POSTINC0 <sup>(1)</sup> | FCEh    | TMR1L                   | FAEh    | RCREG                   | F8Eh    | SSP2BUF                 |

| FEDh    | POSTDEC0 <sup>(1)</sup> | FCDh    | T1CON                   | FADh    | TXREG                   | F8Dh    | LATE <sup>(3)</sup>     |

| FECh    | PREINC0 <sup>(1)</sup>  | FCCh    | TMR2                    | FACh    | TXSTA                   | F8Ch    | LATD <sup>(3)</sup>     |

| FEBh    | PLUSW0 <sup>(1)</sup>   | FCBh    | PR2                     | FABh    | RCSTA                   | F8Bh    | LATC                    |

| FEAh    | FSR0H                   | FCAh    | T2CON                   | FAAh    | (2)                     | F8Ah    | LATB                    |

| FE9h    | FSR0L                   | FC9h    | SSP1BUF                 | FA9h    | (2)                     | F89h    | LATA                    |

| FE8h    | WREG                    | FC8h    | SSP1ADD                 | FA8h    | (2)                     | F88h    | SSP2ADD <sup>(3)</sup>  |

| FE7h    | INDF1 <sup>(1)</sup>    | FC7h    | SSP1STAT                | FA7h    | EECON2 <sup>(1)</sup>   | F87h    | SSP2STAT <sup>(3)</sup> |

| FE6h    | POSTINC1 <sup>(1)</sup> | FC6h    | SSP1CON1                | FA6h    | EECON1                  | F86h    | SSP2CON1 <sup>(3)</sup> |

| FE5h    | POSTDEC1 <sup>(1)</sup> | FC5h    | SSP1CON2                | FA5h    | IPR3                    | F85h    | SSP2CON2 <sup>(3)</sup> |

| FE4h    | PREINC1 <sup>(1)</sup>  | FC4h    | ADRESH                  | FA4h    | PIR3                    | F84h    | PORTE <sup>(3)</sup>    |

| FE3h    | PLUSW1 <sup>(1)</sup>   | FC3h    | ADRESL                  | FA3h    | PIE3                    | F83h    | PORTD <sup>(3)</sup>    |

| FE2h    | FSR1H                   | FC2h    | ADCON0                  | FA2h    | IPR2                    | F82h    | PORTC                   |

| FE1h    | FSR1L                   | FC1h    | ADCON1                  | FA1h    | PIR2                    | F81h    | PORTB                   |

| FE0h    | BSR                     | FC0h    | ADCON2                  | FA0h    | PIE2                    | F80h    | PORTA                   |

Note 1: This is not a physical register.

2: Unimplemented registers are read as '0'.

3: This register is not available in 28-pin devices.

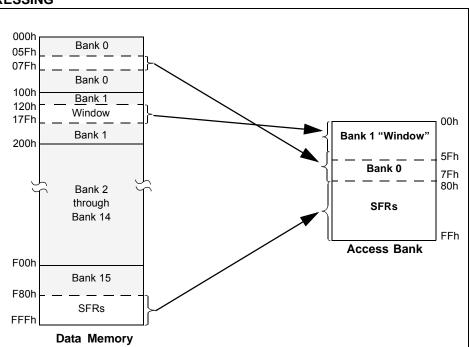

#### 6.5.3 MAPPING THE ACCESS BANK IN INDEXED LITERAL OFFSET MODE

The use of Indexed Literal Offset Addressing mode effectively changes how the first 96 locations of Access RAM (00h to 5Fh) are mapped. Rather than containing just the contents of the bottom half of Bank 0, this mode maps the contents from Bank 0 and a user-defined "window" that can be located anywhere in the data memory space. The value of FSR2 establishes the lower boundary of the addresses mapped into the window, while the upper boundary is defined by FSR2 plus 95 (5Fh). Addresses in the Access RAM above 5Fh are mapped as previously described (see **Section 6.3.2 "Access Bank**"). An example of Access Bank remapping in this addressing mode is shown in Figure 6-10.

Remapping of the Access Bank applies *only* to operations using the Indexed Literal Offset mode. Operations that use the BSR (Access RAM bit is '1') will continue to use Direct Addressing as before.

### 6.6 PIC18 Instruction Execution and the Extended Instruction Set

Enabling the extended instruction set adds eight additional commands to the existing PIC18 instruction set. These instructions are executed as described in **Section 22.2 "Extended Instruction Set**".

#### FIGURE 6-10: REMAPPING THE ACCESS BANK WITH INDEXED LITERAL OFFSET ADDRESSING

#### Example Situation:

ADDWF f, d, a FSR2H:FSR2L = 120h

Locations in the region from the FSR2 Pointer (120h) to the pointer plus 05Fh (17Fh) are mapped to the bottom of the Access RAM (000h-05Fh).

Locations in Bank 0 from 060h to 07Fh are mapped, as usual, to the middle half of the Access Bank.

Special Function Registers at F80h through FFFh are mapped to 80h through FFh, as usual.

Bank 0 addresses below 5Fh can still be addressed by using the BSR.

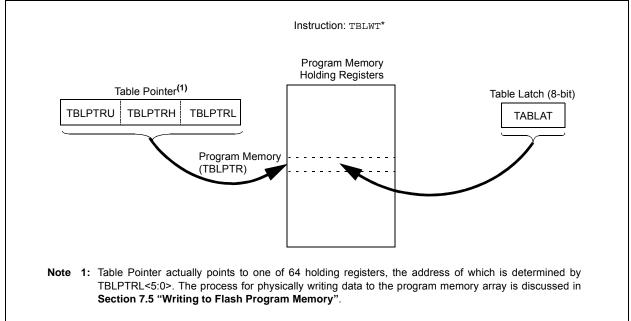

#### FIGURE 7-2: TABLE WRITE OPERATION

### 7.2 Control Registers

Several control registers are used in conjunction with the  ${\tt TBLRD}$  and  ${\tt TBLWT}$  instructions. These include the:

- EECON1 register

- · EECON2 register

- TABLAT register

- TBLPTR registers

#### 7.2.1 EECON1 AND EECON2 REGISTERS

The EECON1 register (Register 7-1) is the control register for memory accesses. The EECON2 register is not a physical register; it is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

The FREE bit, when set, will allow a program memory erase operation. When FREE is set, the erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled. The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set in hardware when the WR bit is set and cleared when the internal programming timer expires and the write operation is complete.

| Note: | During normal operation, the WRERR is       |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|

|       | read as '1'. This can indicate that a write |  |  |  |  |  |  |  |

|       | operation was prematurely terminated by     |  |  |  |  |  |  |  |

|       | a Reset, or a write operation was           |  |  |  |  |  |  |  |

|       | attempted improperly.                       |  |  |  |  |  |  |  |

The WR control bit initiates write operations. The bit cannot be cleared, only set, in software; it is cleared in hardware at the completion of the write operation.

#### 7.2.2 TABLAT – TABLE LATCH REGISTER

The Table Latch (TABLAT) is an 8-bit register mapped into the SFR space. The Table Latch register is used to hold 8-bit data during data transfers between program memory and data RAM.

#### 7.2.3 TBLPTR – TABLE POINTER REGISTER

The Table Pointer (TBLPTR) register addresses a byte within the program memory. The TBLPTR is comprised of three SFR registers: Table Pointer Upper Byte, Table Pointer High Byte and Table Pointer Low Byte (TBLPTRU:TBLPTRH:TBLPTRL). These three registers join to form a 22-bit wide pointer. The low-order 21 bits allow the device to address up to 2 Mbytes of program memory space. The 22nd bit allows access to the device ID, the user ID and the Configuration bits.

The Table Pointer register, TBLPTR, is used by the TBLRD and TBLWT instructions. These instructions can update the TBLPTR in one of four ways based on the table operation. These operations are shown in Table 7-1. These operations on the TBLPTR only affect the low-order 21 bits.

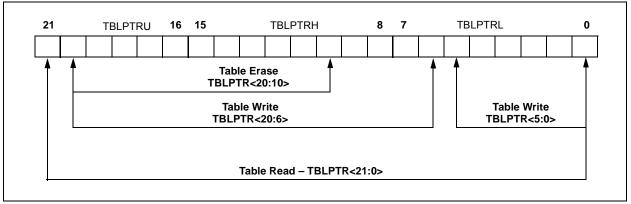

#### 7.2.4 TABLE POINTER BOUNDARIES

TBLPTR is used in reads, writes and erases of the Flash program memory.

When a TBLRD is executed, all 22 bits of the TBLPTR determine which byte is read from program memory into TABLAT.

When a TBLWT is executed, the six LSbs of the Table Pointer register (TBLPTR<5:0>) determine which of the 64 program memory holding registers is written to. When the timed write to program memory begins (via the WR bit), the 16 MSbs of the TBLPTR (TBLPTR<20:6>) determine which program memory block of 64 bytes is written to. For more detail, see **Section 7.5 "Writing to Flash Program Memory"**.

When an erase of program memory is executed, the 7 MSbs of the Table Pointer register (TBLPTR<20:10>) point to the 1024-byte block that will be erased. The Least Significant bits (TBLPTR<9:0>) are ignored.

Figure 7-3 describes the relevant boundaries of TBLPTR based on Flash program memory operations.

| TABLE 7-1: | TABLE POINTER OPERATIONS WITH TBLRD AND TBLWT INSTRUCTIONS |

|------------|------------------------------------------------------------|

| IADLL /-I. |                                                            |

| Example            | Operation on Table Pointer                  |

|--------------------|---------------------------------------------|

| TBLRD*<br>TBLWT*   | TBLPTR is not modified                      |

| TBLRD*+<br>TBLWT*+ | TBLPTR is incremented after the read/write  |

| TBLRD*-<br>TBLWT*- | TBLPTR is decremented after the read/write  |

| TBLRD+*<br>TBLWT+* | TBLPTR is incremented before the read/write |

#### FIGURE 7-3: TABLE POINTER BOUNDARIES BASED ON OPERATION

#### 7.5.2 WRITE VERIFY

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

### 7.5.3 UNEXPECTED TERMINATION OF WRITE OPERATION

If a write is terminated by an unplanned event, such as loss of power or an unexpected Reset, the memory location just programmed should be verified and reprogrammed if needed. If the write operation is interrupted by a MCLR Reset or a WDT Time-out Reset during normal operation, the user can check the WRERR bit and rewrite the location(s) as needed.

#### 7.5.4 PROTECTION AGAINST SPURIOUS WRITES

To protect against spurious writes to Flash program memory, the write initiate sequence must also be followed. See **Section 21.0** "**Special Features of the CPU**" for more detail.

#### 7.6 Flash Program Operation During Code Protection

See Section 21.6 "Program Verification and Code Protection" for details on code protection of Flash program memory.

| Name    | Bit 7                                                   | Bit 6     | Bit 5  | Bit 4      | Bit 3         | Bit 2        | Bit 1         | Bit 0      | Reset<br>Values on<br>page |

|---------|---------------------------------------------------------|-----------|--------|------------|---------------|--------------|---------------|------------|----------------------------|

| TBLPTRU | _                                                       |           | bit 21 | Program Me | emory Table F | Pointer Uppe | r Byte (TBLP  | TR<20:16>) | 47                         |

| TBPLTRH | H Program Memory Table Pointer High Byte (TBLPTR<15:8>) |           |        |            |               |              |               | 47         |                            |

| TBLPTRL | Program Memory Table Pointer Low Byte (TBLPTR<7:0>)     |           |        |            |               |              | 47            |            |                            |

| TABLAT  | Program Memory Table Latch                              |           |        |            |               |              |               | 47         |                            |

| INTCON  | GIE/GIEH                                                | PEIE/GIEL | TMR0IE | INT0IE     | RBIE          | TMR0IF       | <b>INT0IF</b> | RBIF       | 47                         |

| EECON2  | EEPROM Control Register 2 (not a physical register)     |           |        |            |               |              |               | 49         |                            |

| EECON1  | _                                                       | _         | _      | FREE       | WRERR         | WREN         | WR            | _          | 49                         |

| IPR2    | OSCFIP                                                  | CMIP      | _      | _          | BCL1IP        | _            |               | CCP2IP     | 49                         |

| PIR2    | OSCFIF                                                  | CMIF      |        | _          | BCL1IF        |              |               | CCP2IF     | 49                         |

| PIE2    | OSCFIE                                                  | CMIE      | _      | _          | BCL1IE        |              |               | CCP2IE     | 49                         |

#### TABLE 7-2: REGISTERS ASSOCIATED WITH PROGRAM FLASH MEMORY

Legend: — = unimplemented, read as '0'. Shaded cells are not used during Flash/EEPROM access.

### 12.0 TIMER1 MODULE

The Timer1 timer/counter module incorporates these features:

- Software selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR1H and TMR1L)

- Selectable clock source (internal or external) with device clock or Timer1 oscillator internal options

- Interrupt-on-overflow

- Reset on CCP Special Event Trigger

- Device clock status flag (T1RUN)

A simplified block diagram of the Timer1 module is shown in Figure 12-1. A block diagram of the module's operation in Read/Write mode is shown in Figure 12-2.

The module incorporates its own low-power oscillator to provide an additional clocking option. The Timer1 oscillator can also be used as a low-power clock source for the microcontroller in power-managed operation.

Timer1 can also be used to provide Real-Time Clock (RTC) functionality to applications with only a minimal addition of external components and code overhead.

Timer1 is controlled through the T1CON Control register (Register 12-1). It also contains the Timer1 Oscillator Enable bit (T1OSCEN). Timer1 can be enabled or disabled by setting or clearing control bit, TMR1ON (T1CON<0>).

| R/W-0 | R-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|---------|---------|---------|--------|--------|--------|

| RD16  | T1RUN | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7 |       |         |         |         |        |        | bit 0  |

#### REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

| Legend:    |                       |                                                                  |                                                              |                    |

|------------|-----------------------|------------------------------------------------------------------|--------------------------------------------------------------|--------------------|

| R = Reada  | ble bit               | W = Writable bit                                                 | U = Unimplemented bit                                        | , read as '0'      |

| -n = Value | at POR                | '1' = Bit is set                                                 | '0' = Bit is cleared                                         | x = Bit is unknowr |

| bit 7      | <b>RD16:</b> 16       | -Bit Read/Write Mode Enab                                        | le bit                                                       |                    |

|            |                       | les register read/write of TIr<br>les register read/write of Tir | mer1 in one 16-bit operation<br>ner1 in two 8-bit operations |                    |

| bit 6      | T1RUN:                | Fimer1 System Clock Status                                       | bit                                                          |                    |

|            |                       | ce clock is derived from Tim<br>ce clock is derived from ano     |                                                              |                    |

| bit 5-4    | T1CKPS                | <1:0>: Timer1 Input Clock P                                      | rescale Select bits                                          |                    |

|            |                       | Prescale value                                                   |                                                              |                    |

|            |                       | Prescale value                                                   |                                                              |                    |

|            |                       | Prescale value<br>Prescale value                                 |                                                              |                    |

| bit 3      |                       | N: Timer1 Oscillator Enable                                      | bit                                                          |                    |

|            | 1 = Timer             | 1 oscillator is enabled                                          |                                                              |                    |

|            |                       | 1 oscillator is shut off                                         |                                                              |                    |

|            |                       |                                                                  | esistor are turned off to elimina                            | ate power drain.   |

| bit 2      |                       |                                                                  | it Synchronization Select bit                                |                    |

|            |                       | <u>R1CS = 1:</u><br>et evrebrenize externel cleal                | < input                                                      |                    |

|            |                       | ot synchronize external clock<br>nronize external clock input    | ( input                                                      |                    |

|            |                       | R1CS = 0:                                                        |                                                              |                    |

|            |                       |                                                                  | ternal clock when TMR1CS =                                   | 0.                 |

| bit 1      | TMR1CS                | Timer1 Clock Source Sele                                         | ct bit                                                       |                    |

|            |                       | nal clock from pin RC0/T1C<br>nal clock (Fosc/4)                 | OSO/T13CKI (on the rising edge                               | e)                 |

| bit 0      | TMR1ON                | : Timer1 On bit                                                  |                                                              |                    |

|            | 1 = Enab<br>0 = Stops | les Timer1<br>s Timer1                                           |                                                              |                    |

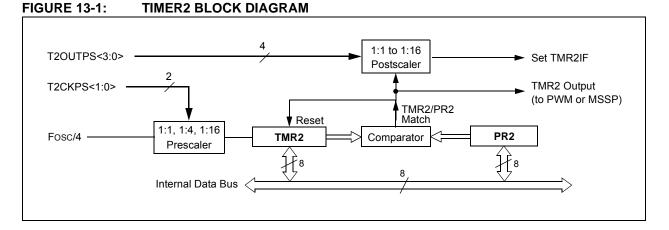

#### 13.2 Timer2 Interrupt

Timer2 can also generate an optional device interrupt. The Timer2 output signal (TMR2 to PR2 match) provides the input for the 4-bit output counter/postscaler. This counter generates the TMR2 match interrupt flag which is latched in TMR2IF (PIR1<1>). The interrupt is enabled by setting the TMR2 Match Interrupt Enable bit, TMR2IE (PIE1<1>).

A range of 16 postscale options (from 1:1 through 1:16 inclusive) can be selected with the postscaler control bits, T2OUTPS<3:0> (T2CON<6:3>).

#### 13.3 Timer2 Output

The unscaled output of TMR2 is available primarily to the CCP modules, where it is used as a time base for operations in PWM mode.

Timer2 can be optionally used as the shift clock source for the MSSP module operating in SPI mode. Additional information is provided in Section 16.0 "Master Synchronous Serial Port (MSSP) Module".

#### TABLE 13-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Name   | Bit 7                | Bit 6        | Bit 5    | Bit 4         | Bit 3    | Bit 2  | Bit 1   | Bit 0   | Reset<br>Values<br>on page |

|--------|----------------------|--------------|----------|---------------|----------|--------|---------|---------|----------------------------|

| INTCON | GIE/GIEH             | PEIE/GIEL    | TMR0IE   | <b>INTOIE</b> | RBIE     | TMR0IF | INT0IF  | RBIF    | 47                         |

| PIR1   | PSPIF <sup>(1)</sup> | ADIF         | RCIF     | TXIF          | SSP1IF   | CCP1IF | TMR2IF  | TMR1IF  | 49                         |

| PIE1   | PSPIE <sup>(1)</sup> | ADIE         | RCIE     | TXIE          | SSP1IE   | CCP1IE | TMR2IE  | TMR1IE  | 49                         |

| IPR1   | PSPIP <sup>(1)</sup> | ADIP         | RCIP     | TXIP          | SSP1IP   | CCP1IP | TMR2IP  | TMR1IP  | 49                         |

| TMR2   | Timer2 Register      |              |          |               |          |        |         |         |                            |

| T2CON  | _                    | T2OUTPS3     | T2OUTPS2 | T2OUTPS1      | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | 48                         |

| PR2    | Timer2 Peri          | iod Register |          |               |          |        |         |         | 48                         |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

Note 1: These bits are not implemented on 28-pin devices and should be read as '0'.

#### 14.0 CAPTURE/COMPARE/PWM (CCP) MODULES

PIC18F45J10 family devices all have two CCP (Capture/Compare/PWM) modules. Each module contains a 16-bit register which can operate as a 16-bit Capture register, a 16-bit Compare register or a PWM Master/Slave Duty Cycle register.

In 28-pin devices, the two standard CCP modules (CCP1 and CCP2) operate as described in this chapter. In 40/44-pin devices, CCP1 is implemented as an Enhanced CCP module (ECCP1) with standard Capture and Compare modes and Enhanced PWM modes. The Enhanced CCP implementation is discussed in **Section 15.0 "Enhanced Capture/Compare/PWM** (ECCP) Module".

The Capture and Compare operations described in this chapter apply to all standard and Enhanced CCP modules.

Note: Throughout this section and Section 15.0 "Enhanced Capture/Compare/PWM (ECCP) Module", references to the register and bit names for CCP modules are referred to generically by the use of 'x' or 'y' in place of the specific module number. Thus, "CCPxCON" might refer to the control register for CCP1, CCP2 or ECCP1. "CCPxCON" is used throughout these sections to refer to the module control register regardless of whether the CCP module is a standard or Enhanced implementation.

| REGISTER 14-1: | CCPxCON: CCP1/CCP2 CONTROL REGISTER IN 28-PIN DEVICES |

|----------------|-------------------------------------------------------|

|                |                                                       |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-------|-------|--------|--------|--------|--------|

| _     | —   | DCxB1 | DCxB0 | CCPxM3 | CCPxM2 | CCPxM1 | CCPxM0 |

| bit 7 |     |       |       |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                    |  |  |  |  |  |  |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| bit 5-4 | DCxB<1:0>: PWM Duty Cycle bit 1 and bit 0                                                                                                     |  |  |  |  |  |  |  |  |

|         | Capture mode:<br>Unused.                                                                                                                      |  |  |  |  |  |  |  |  |

|         | <u>Compare mode</u> :<br>Unused.                                                                                                              |  |  |  |  |  |  |  |  |

|         | PWM mode:                                                                                                                                     |  |  |  |  |  |  |  |  |

|         | These bits are the two LSbs (bit 1 and bit 0) of the 10-bit PWM duty cycle. The eight MSbs (DCxB<9:2>) of the duty cycle are found in CCPRxL. |  |  |  |  |  |  |  |  |

| bit 3-0 | CCPxM<3:0>: CCPx Mode Select bits                                                                                                             |  |  |  |  |  |  |  |  |

|         | 0000 = Capture/Compare/PWM disabled (resets CCPx module)                                                                                      |  |  |  |  |  |  |  |  |

|         | 0001 = Reserved                                                                                                                               |  |  |  |  |  |  |  |  |

|         | 0010 = Compare mode, toggle output on match (CCPxIF bit is set)                                                                               |  |  |  |  |  |  |  |  |

|         | 0011 = Reserved                                                                                                                               |  |  |  |  |  |  |  |  |

|         | 0100 = Capture mode, every falling edge                                                                                                       |  |  |  |  |  |  |  |  |

|         | 0101 = Capture mode, every rising edge                                                                                                        |  |  |  |  |  |  |  |  |

|         | 0110 = Capture mode, every 4th rising edge                                                                                                    |  |  |  |  |  |  |  |  |

|         | 0111 = Capture mode, every 16th rising edge                                                                                                   |  |  |  |  |  |  |  |  |

|         | 1000 = Compare mode: initialize CCPx pin low; on compare match, force CCPx pin high<br>(CCPxIF bit is set)                                    |  |  |  |  |  |  |  |  |

|         | 1001 = Compare mode: initialize CCPx pin high; on compare match, force CCPx pin low<br>(CCPxIF bit is set)                                    |  |  |  |  |  |  |  |  |

|         | 1010 = Compare mode: generate software interrupt on compare match (CCPxIF bit is set,<br>CCPx pin reflects I/O state)                         |  |  |  |  |  |  |  |  |

|         | 1011 = Compare mode: trigger special event, reset timer, start A/D conversion on CCPx match (CCPxIF bit is set)                               |  |  |  |  |  |  |  |  |

|         | 11xx = PWM mode                                                                                                                               |  |  |  |  |  |  |  |  |

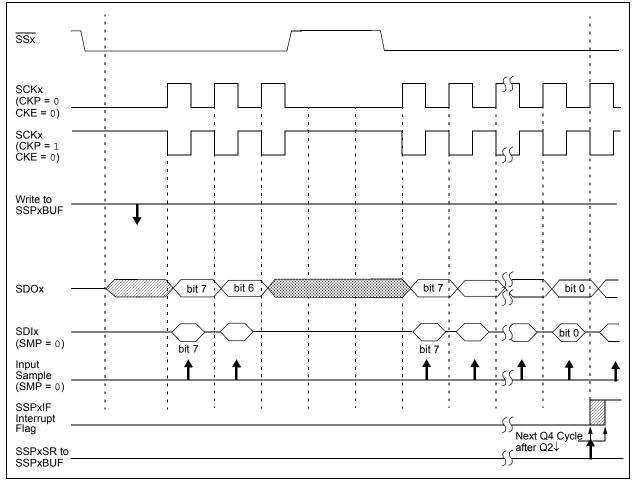

#### 16.3.2 OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPxCON1<5:0> and SSPxSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCKx is the clock output)

- Slave mode (SCKx is the clock input)

- Clock Polarity (Idle state of SCKx)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCKx)

- Clock Rate (Master mode only)

- · Slave Select mode (Slave mode only)

Each MSSP consists of a transmit/receive shift register (SSPxSR) and a buffer register (SSPxBUF). The SSPxSR shifts the data in and out of the device, MSb first. The SSPxBUF holds the data that was written to the SSPxSR until the received data is ready. Once the 8 bits of data have been received, that byte is moved to the SSPxBUF register. Then, the Buffer Full detect bit, BF (SSPxSTAT<0>), and the interrupt flag bit, SSPxIF, are set. This double-buffering of the received data (SSPxBUF) allows the next byte to start reception before reading the data that was just received. Any write to the

SSPxBUF register during transmission/reception of data will be ignored and the Write Collision detect bit, WCOL (SSPxCON1<7>), will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPxBUF register completed successfully.

When the application software is expecting to receive valid data, the SSPxBUF should be read before the next byte of data to transfer is written to the SSPxBUF. The Buffer Full bit, BF (SSPxSTAT<0>), indicates when SSPxBUF has been loaded with the received data (transmission is complete). When the SSPxBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. The SSPxBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 16-1 shows the loading of the SSP1BUF (SSP1SR) for data transmission.

The SSPxSR is not directly readable or writable and can only be accessed by addressing the SSPxBUF register. Additionally, the SSPxSTAT register indicates the various status conditions.

#### EXAMPLE 16-1: LOADING THE SSP1BUF (SSP1SR) REGISTER

| LOOP | BTFSS | SSP1STAT, BF | ;Has data been received (transmit complete)? |

|------|-------|--------------|----------------------------------------------|

|      | BRA   | LOOP         | ;No                                          |

|      | MOVF  | SSP1BUF, W   | ;WREG reg = contents of SSP1BUF              |

|      | MOVWF | RXDATA       | ;Save in user RAM, if data is meaningful     |

|      | MOVF  | TXDATA, W    | ;W reg = contents of TXDATA                  |

|      | MOVWF | SSP1BUF      | ;New data to xmit                            |

#### 16.3.6 SLAVE MODE

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCKx. When the last bit is latched, the SSPxIF interrupt flag bit is set.

Before enabling the module in SPI Slave mode, the clock line must match the proper Idle state. The clock line can be observed by reading the SCKx pin. The Idle state is determined by the CKP bit (SSPxCON1<4>).

While in Slave mode, the external clock is supplied by the external clock source on the SCKx pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. When a byte is received, the device will wake-up from Sleep.

#### 16.3.7 SLAVE SELECT SYNCHRONIZATION

The  $\overline{SSx}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with  $\overline{SSx}$  pin control enabled (SSPxCON1<3:0> = 04h). When the  $\overline{SSx}$  pin is low, transmission and reception are enabled and the

SDOx pin is driven. When the SSx pin goes high, the SDOx pin is no longer driven, even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable depending on the application.

- Note 1: When the SPI is in Slave mode with SSx pin control enabled (SSPxCON1<3:0> = 0100), the SPI module will reset if the SSx pin is set to VDD.

- 2: If the SPI is used in Slave mode with CKE set, then the SSx pin control must be enabled.

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the SSx pin to a high level or clearing the SSPEN bit.

To emulate two-wire communication, the SDOx pin can be connected to the SDIx pin. When the SPI needs to operate as a receiver, the SDOx pin can be configured as an input. This disables transmissions from the SDOx. The SDIx can always be left as an input (SDIx function) since it cannot create a bus conflict.

#### FIGURE 16-4: SLAVE SYNCHRONIZATION WAVEFORM

| Name                 | Bit 7                | Bit 6                       | Bit 5                                         | Bit 4                                             | Bit 3     | Bit 2     | Bit 1                 | Bit 0  | Reset<br>Values<br>on Page |

|----------------------|----------------------|-----------------------------|-----------------------------------------------|---------------------------------------------------|-----------|-----------|-----------------------|--------|----------------------------|

| INTCON               | GIE/GIEH             | PEIE/GIEL                   | TMR0IE                                        | INT0IE                                            | RBIE      | TMR0IF    | <b>INT0IF</b>         | RBIF   | 47                         |

| PIR1                 | PSPIF <sup>(1)</sup> | ADIF                        | RCIF                                          | TXIF                                              | SSP1IF    | CCP1IF    | TMR2IF                | TMR1IF | 49                         |

| PIE1                 | PSPIE <sup>(1)</sup> | ADIE                        | RCIE                                          | TXIE                                              | SSP1IE    | CCP1IE    | TMR2IE                | TMR1IE | 49                         |

| IPR1                 | PSPIP <sup>(1)</sup> | ADIP                        | RCIP                                          | TXIP                                              | SSP1IP    | CCP1IP    | TMR2IP                | TMR1IP | 49                         |

| PIR2                 | OSCFIF               | CMIF                        | _                                             | _                                                 | BCL1IF    | _         | _                     | CCP2IF | 49                         |

| PIE2                 | OSCFIE               | CMIE                        | _                                             | _                                                 | BCL1IE    |           |                       | CCP2IE | 49                         |

| IPR2                 | OSCFIP               | CMIP                        | _                                             | _                                                 | BCL1IP    | _         | _                     | CCP2IP | 49                         |

| PIR3                 | SSP2IF               | BCL2IF                      | _                                             | _                                                 | _         | _         | _                     | _      | 49                         |

| PIE3                 | SSP2IE               | BCL2IE                      | —                                             | _                                                 | —         | _         | —                     | _      | 49                         |

| IPR3                 | SSP2IP               | BCL2IP                      | _                                             | _                                                 | _         | _         | _                     | _      | 49                         |

| TRISC                | TRISC7               | TRISC6                      | TRISC5                                        | TRISC4                                            | TRISC3    | TRISC2    | TRISC1                | TRISC0 | 50                         |

| TRISD <sup>(1)</sup> | TRISD7               | TRISD6                      | TRISD5                                        | TRISD4                                            | TRISD3    | TRISD2    | TRISD1                | TRISD0 | 50                         |

| SSP1BUF              | MSSP1 Re             | eceive Buffer               | r/Transmit Re                                 | gister                                            |           |           |                       |        | 48                         |

| SSP1ADD              |                      |                             | ster (I <sup>2</sup> C™ Sla<br>load Register  |                                                   | mode).    |           |                       |        | 48                         |

| SSP1CON1             | WCOL                 | SSPOV                       | SSPEN                                         | CKP                                               | SSPM3     | SSPM2     | SSPM1                 | SSPM0  | 48                         |

| SSP1CON2             | GCEN                 | ACKSTAT                     | ACKDT                                         | ACKEN                                             | RCEN      | PEN       | RSEN                  | SEN    | 48                         |

|                      | GCEN                 | ACKSTAT                     | ADMSK5(2)                                     | ADMSK4 <sup>(2)</sup>                             | ADMSK3(2) | ADMSK2(2) | ADMSK1(2)             | SEN    | 48                         |

| SSP1STAT             | SMP                  | CKE                         | D/Ā                                           | Р                                                 | S         | R/W       | UA                    | BF     | 48                         |

| SSP2BUF              | MSSP2 Re             | eceive Buffer               | /Transmit Re                                  | gister                                            |           |           |                       |        | 50                         |

| SSP2ADD              | MSSP2 Ac<br>MSSP2 Ba | ldress Regis<br>aud Rate Re | ster (I <sup>2</sup> C Slave<br>load Register | e mode).<br><sup>.</sup> (I <sup>2</sup> C Master | mode).    |           |                       |        | 50                         |

| SSP2CON1             | WCOL                 | SSPOV                       | SSPEN                                         | CKP                                               | SSPM3     | SSPM2     | SSPM1                 | SSPM0  | 50                         |

| SSP2CON2             | GCEN                 | ACKSTAT                     | ACKDT                                         | ACKEN                                             | RCEN      | PEN       | RSEN                  | SEN    | 50                         |

|                      | GCEN                 | ACKSTAT                     | ADMSK5 <sup>(2)</sup>                         | ADMSK4 <sup>(2)</sup>                             | ADMSK3(2) | ADMSK2(2) | ADMSK1 <sup>(2)</sup> | SEN    | 48                         |

| SSP2STAT             | SMP                  | CKE                         | D/Ā                                           | Р                                                 | S         | R/W       | UA                    | BF     | 50                         |

#### TABLE 16-4: REGISTERS ASSOCIATED WITH I<sup>2</sup>C<sup>™</sup> OPERATION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the MSSP module in  $I^2C^{TM}$  mode.

Note 1: These registers and/or bits are not implemented on 28-pin devices and should be read as '0'.

2: Alternate names and definitions for these bits when the MSSP module is operating in I<sup>2</sup>C Slave mode. See Section 16.4.3.2 "Address Masking" for details.

|       |                       | SYNC = 0, BRGH = 0, BRG16 = 1 |                             |                       |            |                             |                       |            |                             |                       |            |                             |  |  |  |

|-------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|--|

| BAUD  | Fosc = 40.000 MHz     |                               |                             | Fosc                  | = 20.000   | ) MHz                       | Fosc = 10.000 MHz     |            |                             | Fosc = 8.000 MHz      |            |                             |  |  |  |

| (K)   | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |

| 0.3   | 0.300                 | 0.00                          | 8332                        | 0.300                 | 0.02       | 4165                        | 0.300                 | 0.02       | 2082                        | 0.300                 | -0.04      | 1665                        |  |  |  |

| 1.2   | 1.200                 | 0.02                          | 2082                        | 1.200                 | -0.03      | 1041                        | 1.200                 | -0.03      | 520                         | 1.201                 | -0.16      | 415                         |  |  |  |

| 2.4   | 2.402                 | 0.06                          | 1040                        | 2.399                 | -0.03      | 520                         | 2.404                 | 0.16       | 259                         | 2.403                 | -0.16      | 207                         |  |  |  |

| 9.6   | 9.615                 | 0.16                          | 259                         | 9.615                 | 0.16       | 129                         | 9.615                 | 0.16       | 64                          | 9.615                 | -0.16      | 51                          |  |  |  |

| 19.2  | 19.231                | 0.16                          | 129                         | 19.231                | 0.16       | 64                          | 19.531                | 1.73       | 31                          | 19.230                | -0.16      | 25                          |  |  |  |

| 57.6  | 58.140                | 0.94                          | 42                          | 56.818                | -1.36      | 21                          | 56.818                | -1.36      | 10                          | 55.555                | 3.55       | 8                           |  |  |  |

| 115.2 | 113.636               | -1.36                         | 21                          | 113.636               | -1.36      | 10                          | 125.000               | 8.51       | 4                           | —                     | _          | _                           |  |  |  |

| <b>TABLE 17-3</b> : | BAUD RATES FOR ASYNCHRONOUS MODES ( | CONTINUED) |  |

|---------------------|-------------------------------------|------------|--|

|---------------------|-------------------------------------|------------|--|

|              |                       | SYNC = 0, BRGH = 0, BRG16 = 1 |                             |                       |            |                             |                       |            |                             |  |  |  |  |  |

|--------------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|--|--|--|

| BAUD<br>RATE | Foso                  | c = 4.000                     | MHz                         | Fos                   | c = 2.000  | MHz                         | Fosc = 1.000 MHz      |            |                             |  |  |  |  |  |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |  |  |

| 0.3          | 0.300                 | 0.04                          | 832                         | 0.300                 | -0.16      | 415                         | 0.300                 | -0.16      | 207                         |  |  |  |  |  |

| 1.2          | 1.202                 | 0.16                          | 207                         | 1.201                 | -0.16      | 103                         | 1.201                 | -0.16      | 51                          |  |  |  |  |  |

| 2.4          | 2.404                 | 0.16                          | 103                         | 2.403                 | -0.16      | 51                          | 2.403                 | -0.16      | 25                          |  |  |  |  |  |

| 9.6          | 9.615                 | 0.16                          | 25                          | 9.615                 | -0.16      | 12                          | —                     | _          | _                           |  |  |  |  |  |

| 19.2         | 19.231                | 0.16                          | 12                          | —                     | _          | _                           | —                     | _          | _                           |  |  |  |  |  |

| 57.6         | 62.500                | 8.51                          | 3                           | —                     | _          | _                           | —                     | _          | _                           |  |  |  |  |  |

| 115.2        | 125.000               | 8.51                          | 1                           | _                     | _          | _                           | —                     | _          | _                           |  |  |  |  |  |

|              |                       | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |                             |                       |            |                             |                       |            |                             |                       |            |                             |  |  |  |  |

|--------------|-----------------------|------------------------------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|--|--|

| BAUD<br>RATE | Fosc = 40.000 MHz     |                                                      |                             | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |            |                             | Fosc = 8.000 MHz      |            |                             |  |  |  |  |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                                           | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |  |

| 0.3          | 0.300                 | 0.00                                                 | 33332                       | 0.300                 | 0.00       | 16665                       | 0.300                 | 0.00       | 8332                        | 0.300                 | -0.01      | 6665                        |  |  |  |  |

| 1.2          | 1.200                 | 0.00                                                 | 8332                        | 1.200                 | 0.02       | 4165                        | 1.200                 | 0.02       | 2082                        | 1.200                 | -0.04      | 1665                        |  |  |  |  |

| 2.4          | 2.400                 | 0.02                                                 | 4165                        | 2.400                 | 0.02       | 2082                        | 2.402                 | 0.06       | 1040                        | 2.400                 | -0.04      | 832                         |  |  |  |  |

| 9.6          | 9.606                 | 0.06                                                 | 1040                        | 9.596                 | -0.03      | 520                         | 9.615                 | 0.16       | 259                         | 9.615                 | -0.16      | 207                         |  |  |  |  |

| 19.2         | 19.193                | -0.03                                                | 520                         | 19.231                | 0.16       | 259                         | 19.231                | 0.16       | 129                         | 19.230                | -0.16      | 103                         |  |  |  |  |

| 57.6         | 57.803                | 0.35                                                 | 172                         | 57.471                | -0.22      | 86                          | 58.140                | 0.94       | 42                          | 57.142                | 0.79       | 34                          |  |  |  |  |

| 115.2        | 114.943               | -0.22                                                | 86                          | 116.279               | 0.94       | 42                          | 113.636               | -1.36      | 21                          | 117.647               | -2.12      | 16                          |  |  |  |  |

|       |                       | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |                             |                       |                  |                             |                       |            |                             |  |  |  |  |  |

|-------|-----------------------|------------------------------------------------------|-----------------------------|-----------------------|------------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|--|--|--|

| BAUD  | Fosc = 4.000 MHz      |                                                      |                             | Fos                   | Fosc = 2.000 MHz |                             |                       | c = 1.000  | MHz                         |  |  |  |  |  |

| (K)   | Actual<br>Rate<br>(K) | %<br>Error                                           | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |  |  |

| 0.3   | 0.300                 | 0.01                                                 | 3332                        | 0.300                 | -0.04            | 1665                        | 0.300                 | -0.04      | 832                         |  |  |  |  |  |

| 1.2   | 1.200                 | 0.04                                                 | 832                         | 1.201                 | -0.16            | 415                         | 1.201                 | -0.16      | 207                         |  |  |  |  |  |

| 2.4   | 2.404                 | 0.16                                                 | 415                         | 2.403                 | -0.16            | 207                         | 2.403                 | -0.16      | 103                         |  |  |  |  |  |

| 9.6   | 9.615                 | 0.16                                                 | 103                         | 9.615                 | -0.16            | 51                          | 9.615                 | -0.16      | 25                          |  |  |  |  |  |

| 19.2  | 19.231                | 0.16                                                 | 51                          | 19.230                | -0.16            | 25                          | 19.230                | -0.16      | 12                          |  |  |  |  |  |

| 57.6  | 58.824                | 2.12                                                 | 16                          | 55.555                | 3.55             | 8                           | —                     | _          | _                           |  |  |  |  |  |

| 115.2 | 111.111               | -3.55                                                | 8                           | —                     |                  | —                           | —                     |            | —                           |  |  |  |  |  |

#### 17.4.2 EUSART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of Sleep, or any Idle mode and bit, SREN, which is a "don't care" in Slave mode.

If receive is enabled by setting the CREN bit prior to entering Sleep or any Idle mode, then a word may be received while in this low-power mode. Once the word is received, the RSR register will transfer the data to the RCREG register; if the RCIE enable bit is set, the interrupt generated will wake the chip from the low-power mode. If the global interrupt is enabled, the program will branch to the interrupt vector. To set up a Synchronous Slave Reception:

- Enable the synchronous master serial port by setting bits, SYNC and SPEN, and clearing bit, CSRC.

- 2. If interrupts are desired, set enable bit, RCIE.

- 3. If 9-bit reception is desired, set bit, RX9.

- 4. To enable reception, set enable bit, CREN.

- 5. Flag bit, RCIF, will be set when reception is complete. An interrupt will be generated if enable bit, RCIE, was set.

- Read the RCSTA register to get the 9th bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit, CREN.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| Name    | Bit 7                                         | Bit 6        | Bit 5       | Bit 4        | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|-----------------------------------------------|--------------|-------------|--------------|--------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH                                      | PEIE/GIEL    | TMR0IE      | INT0IE       | RBIE   | TMR0IF | INT0IF | RBIF   | 47                         |

| PIR1    | PSPIF <sup>(1)</sup>                          | ADIF         | RCIF        | TXIF         | SSP1IF | CCP1IF | TMR2IF | TMR1IF | 49                         |

| PIE1    | PSPIE <sup>(1)</sup>                          | ADIE         | RCIE        | TXIE         | SSP1IE | CCP1IE | TMR2IE | TMR1IE | 49                         |

| IPR1    | PSPIP <sup>(1)</sup>                          | ADIP         | RCIP        | TXIP         | SSP1IP | CCP1IP | TMR2IP | TMR1IP | 49                         |

| RCSTA   | SPEN                                          | RX9          | SREN        | CREN         | ADDEN  | FERR   | OERR   | RX9D   | 49                         |

| RCREG   | EUSART F                                      | Receive Regi | ster        |              |        |        |        |        | 49                         |

| TXSTA   | CSRC                                          | TX9          | TXEN        | SYNC         | SENDB  | BRGH   | TRMT   | TX9D   | 49                         |

| BAUDCON | ABDOVF                                        | RCIDL        | _           | SCKP         | BRG16  | —      | WUE    | ABDEN  | 49                         |

| SPBRGH  | EUSART Baud Rate Generator Register High Byte |              |             |              |        |        |        |        |                            |

| SPBRG   | EUSART E                                      | Baud Rate G  | enerator Re | gister Low I | Byte   |        |        |        | 49                         |

#### TABLE 17-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: — = unimplemented, read as '0'. Shaded cells are not used for synchronous slave reception.

Note 1: These bits are not implemented on 28-pin devices and should be read as '0'.

NOTES:

| Incremen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | t f, Skip if                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| INCFSZ f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |