Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 40MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 21                                                                           |

| Program Memory Size        | 16KB (8K x 16)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                    |

| Data Converters            | A/D 10x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 28-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf24j10t-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC18F45J10 FAMILY

|                                      | Pin Nu                  | mber  |             |                |                                                                                                               |  |  |

|--------------------------------------|-------------------------|-------|-------------|----------------|---------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name                             | SPDIP,<br>SOIC,<br>SSOP | QFN   | Pin<br>Type | Buffer<br>Type | Description                                                                                                   |  |  |

|                                      |                         |       |             |                | PORTB is a bidirectional I/O port. PORTB can be software programmed for internal weak pull-ups on all inputs. |  |  |

| RB0/INT0/FLT0/AN12                   | 21                      | 18    |             |                |                                                                                                               |  |  |

| RB0                                  |                         |       | I/O         | TTL            | Digital I/O.                                                                                                  |  |  |

| INT0                                 |                         |       | I           | ST             | External Interrupt 0.                                                                                         |  |  |

| FLT0                                 |                         |       | I           | ST             | PWM Fault input for CCP1.                                                                                     |  |  |

| AN12                                 |                         |       | I           | Analog         | Analog input 12.                                                                                              |  |  |

| RB1/INT1/AN10                        | 22                      | 19    |             |                |                                                                                                               |  |  |

| RB1                                  |                         |       | I/O         | TTL            | Digital I/O.                                                                                                  |  |  |

| INT1                                 |                         |       |             | ST             | External Interrupt 1.                                                                                         |  |  |

| AN10                                 |                         |       |             | Analog         | Analog input 10.                                                                                              |  |  |

| RB2/INT2/AN8                         | 23                      | 20    |             |                |                                                                                                               |  |  |

| RB2                                  |                         |       | I/O         | TTL            | Digital I/O.                                                                                                  |  |  |

| INT2                                 |                         |       |             | ST             | External Interrupt 2.                                                                                         |  |  |

| AN8                                  |                         |       |             | Analog         | Analog input 8.                                                                                               |  |  |

| RB3/AN9/CCP2                         | 24                      | 21    | 1/0         |                |                                                                                                               |  |  |

| RB3<br>AN9                           |                         |       | I/O<br>I    | TTL<br>Analog  | Digital I/O.<br>Analog Input 9.                                                                               |  |  |

| CCP2 <sup>(1)</sup>                  |                         |       | 1/O         | ST             | Capture 2 input/Compare 2 output/PWM2 output.                                                                 |  |  |

| RB4/KBI0/AN11                        | 25                      | 22    | 1/0         | 01             |                                                                                                               |  |  |

| RB4                                  | 25                      | 22    | I/O         | TTL            | Digital I/O.                                                                                                  |  |  |

| KBI0                                 |                         |       | 1/0         | TTL            | Interrupt-on-change pin.                                                                                      |  |  |

| AN11                                 |                         |       | i           | Analog         | Analog Input 11.                                                                                              |  |  |

| RB5/KBI1/T0CKI/                      | 26                      | 23    |             | 0              | 5                                                                                                             |  |  |

| C1OUT                                |                         |       | I/O         | TTL            | Digital I/O.                                                                                                  |  |  |

| RB5                                  |                         |       | I           | TTL            | Interrupt-on-change pin.                                                                                      |  |  |

| KBI1                                 |                         |       | I           | ST             | Timer0 external clock input.                                                                                  |  |  |

| TOCKI                                |                         |       | 0           | —              | Comparator 1 output.                                                                                          |  |  |

| C1OUT                                |                         |       |             |                |                                                                                                               |  |  |

| RB6/KBI2/PGC                         | 27                      | 24    |             |                |                                                                                                               |  |  |

| RB6                                  |                         |       | I/O         | TTL            | Digital I/O.                                                                                                  |  |  |

| KBI2                                 |                         |       |             | TTL            | Interrupt-on-change pin.                                                                                      |  |  |

| PGC                                  |                         | a-    | I/O         | ST             | In-Circuit Debugger and ICSP™ programming clock pin.                                                          |  |  |

| RB7/KBI3/PGD                         | 28                      | 25    |             |                | Divite 1/0                                                                                                    |  |  |

| RB7<br>KBI3                          |                         |       | 1/O<br>1    | TTL<br>TTL     | Digital I/O.<br>Interrupt-on-change pin.                                                                      |  |  |

| PGD                                  |                         |       | 1/O         | ST             | In-Circuit Debugger and ICSP programming data pin.                                                            |  |  |

|                                      |                         |       | "0          | 51             |                                                                                                               |  |  |

|                                      | montible                | innut |             |                | CMOS - CMOS compatible input or output                                                                        |  |  |

| Legend: TTL = TTL co<br>ST = Schmitt |                         |       | with CI     | MOS lev        | CMOS = CMOS compatible input or output<br>els I = Input                                                       |  |  |

| TABLE 1-2: | PIC18F24J10/25J10 PINOUT I/O DESCRIPTIONS (CONTINUED) |

|------------|-------------------------------------------------------|

| TADLE 1-2. | FIGTOFZ4JT0/20JT0 FINOUT I/O DESCRIFTIONS (CONTINUED) |

Note 1: Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

| Pin Name             | Pir  | n Numb    | er      | Pin    | Buffer | Description                            |

|----------------------|------|-----------|---------|--------|--------|----------------------------------------|

| Tinname              | PDIP | QFN       | TQFP    | Туре   | Туре   | Description                            |

|                      |      |           |         |        |        | PORTA is a bidirectional I/O port.     |

| RA0/AN0              | 2    | 19        | 19      |        |        |                                        |

| RA0                  |      |           |         | I/O    | TTL    | Digital I/O.                           |

| AN0                  |      |           |         | I      | Analog | Analog Input 0.                        |

| RA1/AN1              | 3    | 20        | 20      |        |        |                                        |

| RA1                  |      |           |         | I/O    | TTL    | Digital I/O.                           |

| AN1                  |      |           |         | Ι      | Analog | Analog Input 1.                        |

| RA2/AN2/VREF-/CVREF  | 4    | 21        | 21      |        |        |                                        |

| RA2                  |      |           |         | I/O    | TTL    | Digital I/O.                           |

| AN2                  |      |           |         | I      | Analog | Analog Input 2.                        |

| VREF-                |      |           |         | I      | Analog | A/D reference voltage (low) input.     |

| CVREF                |      |           |         | 0      | Analog | Comparator reference voltage output.   |

| RA3/AN3/VREF+        | 5    | 22        | 22      |        |        |                                        |

| RA3                  |      |           |         | I/O    | TTL    | Digital I/O.                           |

| AN3                  |      |           |         | I      | Analog | 5 1                                    |

| Vref+                |      |           |         | I      | Analog | A/D reference voltage (high) input.    |

| RA5/AN4/SS1/C2OUT    | 7    | 24        | 24      |        |        |                                        |

| RA5                  |      |           |         | I/O    | TTL    | Digital I/O.                           |

| AN4                  |      |           |         | I      | Analog | Analog Input 4.                        |

| SS1                  |      |           |         | I      | TTL    | SPI slave select input.                |

| C2OUT                |      |           |         | 0      | —      | Comparator 2 output.                   |

| Legend: TTL = TTL co |      |           |         |        |        | CMOS = CMOS compatible input or output |

| ST = Schmi           |      | r input v | with CM | OS lev |        | = Input                                |

| O = Output           | t    |           |         |        | Р      | P = Power                              |

# TABLE 1-3: PIC18F44J10/45J10 PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

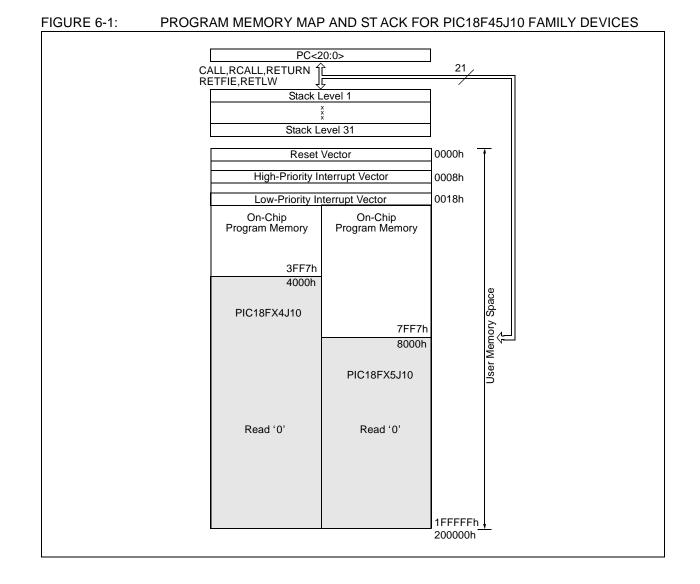

# 6.0 MEMORY ORGANIZATION

There are two types of memory in PIC18 Enhanced microcontroller devices:

- Program Memory

- Data RAM

As Harvard architecture devices, the data and program memories use separate busses; this allows for concurrent access of the two memory spaces.

Additional detailed information on the operation of the Flash program memory is provided in Section 7.0 "Flash Program Memory" .

# 6.1 Program Memory Organization

PIC18 microcontrollers implement a 21-bit program counter, which is capable of addressing a 2-Mbyte program memory space. Accessing a location between the upper boundary of the physically implemented memory and the 2-Mbyte address will return all '0's (a NOPinstruction).

The PIC18F24J10 and PIC18F44J10 each have 16 Kbytes of Flash memory and can store up to 8,192 single-word instructions. The PIC18F25J10 and PIC18F45J10 each have 32 Kbytes of Flash memory and can store up to 16,384 single-word instructions.

PIC18 devices have two interrupt vectors. The Reset vector address is at 0000h and the interrupt vector addresses are at 0008h and 0018h.

The program memory map for the PIC18F45J10 family devices is shown in Figure 6-1.

#### 6.1.4.4 Stack Full and Underflow Resets

Device Resets on stack overflow and stack underflow conditions are enabled by setting the STVREN bit in Configuration Register 4L. When STVREN is set, a full or underflow will set the appropriate STKFUL or STKUNF bit and then cause a device Reset. When STVREN is cleared, a full or underflow condition will set the appropriate STKFUL or STKUNF bit but not cause a device Reset. The STKFUL or STKUNF bits are cleared by the user software or a Power-on Reset.

#### 6.1.5 FAST REGISTER STACK

A Fast Register Stack is provided for the STATUS, WREG and BSR registers, to provide a "fast return" option for interrupts. The stack for each register is only one level deep and is neither readable nor writable. It is loaded with the current value of the corresponding register when the processor vectors for an interrupt. All interrupt sources will push values into the stack registers. The values in the registers are then loaded back into their associated registers if the RETFIE, FAST instruction is used to return from the interrupt.

If both low and high-priority interrupts are enabled, the stack registers cannot be used reliably to return from low-priority interrupts. If a high-priority interrupt occurs while servicing a low-priority interrupt, the stack register values stored by the low-priority interrupt will be overwritten. In these cases, users must save the key registers in software during a low-priority interrupt.

If interrupt priority is not used, all interrupts may use the Fast Register Stack for returns from interrupt. If no interrupts are used, the Fast Register Stack can be used to restore the STATUS, WREG and BSR registers at the end of a subroutine call. To use the Fast Register Stack for a subroutine call, a CALL label , FAST instruction must be executed to save the STATUS, WREG and BSR registers to the Fast Register Stack. A RETURN FAST instruction is then executed to restore these registers from the Fast Register Stack.

Example 6-1 shows a source code example that uses the Fast Register Stack during a subroutine call and return.

| EXAMPLE 6-1:    | FAST REGISTER STACK<br>CODE EXAMPLE                     |

|-----------------|---------------------------------------------------------|

| CALL SUB1, FAST | ;STATUS, WREG, BSR<br>;SAVED IN FAST REGISTER<br>;STACK |

| х               |                                                         |

| х               |                                                         |

|                 |                                                         |

#### х RETURN, FAST :RESTORE VALUES SAVED

;IN FAST REGISTER STACK

#### LOOK-UP TABLES IN PROGRAM 6.1.6 MEMORY

There may be programming situations that require the creation of data structures, or look-up tables, in program memory. For PIC18 devices, look-up tables can be implemented in two ways:

- Computed GOTO

- Table Reads

#### 6.1.6.1 Computed GOTO

A computed GOTOs accomplished by adding an offset to the program counter. An example is shown in Example 6-2.

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW nn instructions. The W register is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCLinstruction. The next instruction executed will be one of the RETLW nn instructions that returns the value 'nn' to the calling function.

The offset value (in WREG) specifies the number of bytes that the program counter should advance and should be multiples of 2 (LSb = 0).

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

| EXAMPLE 6-2: | COMPUTED GOTOUSING |

|--------------|--------------------|

|              | AN OFFSET VALUE    |

|       | MOVF  | OFFSET, W |

|-------|-------|-----------|

|       | CALL  | TABLE     |

| ORG   | nn00h |           |

| TABLE | ADDWF | PCL       |

|       | RETLW | nnh       |

|       | RETLW | nnh       |

|       | RETLW | nnh       |

|       |       |           |

|       |       |           |

|       |       |           |

|       |       |           |

#### 6.1.6.2 Table Reads and Table Writes

A better method of storing data in program memory allows two bytes of data to be stored in each instruction location.

Look-up table data may be stored two bytes per program word by using table reads and writes. The Table Pointer (TBLPTR) register specifies the byte address and the Table Latch (TABLAT) register contains the data that is read from or written to program memory. Data is transferred to or from program memory one byte at a time.

Table read and table write operations are discussed further in Section 7.1 "Table Reads and Table Writes".

SUB1

Х

# 9.2 PIR Registers

The PIR registers contain the individual flag bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are three Peripheral Interrupt Request (Flag) registers (PIR1, PIR2, PIR3).

- Note 1: Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE (INTCON<7>).

- User software should ensure the appropriate interrupt flag bits are cleared prior to enabling an interrupt and after servicing that interrupt.

# REGISTER 9-4: PIR1: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 1

| R/W-0                | R/W-0 | R-0  | R-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|----------------------|-------|------|------|--------|--------|--------|--------|

| PSPIF <sup>(1)</sup> | ADIF  | RCIF | TXIF | SSP1IF | CCP1IF | TMR2IF | TMR1IF |

| bit 7                |       |      |      |        |        |        | bit 0  |

|                      |       |      |      |        |        |        |        |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7 | PSPIF: Parallel Slave Port Read/Write Interrupt Flag bit <sup>(1)</sup>                                                                             |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = A read or a write operation has taken place (must be cleared in software)</li> <li>0 = No read or write has occurred</li> </ul>        |

| bit 6 | ADIF: A/D Converter Interrupt Flag bit                                                                                                              |

|       | <ul><li>1 = An A/D conversion completed (must be cleared in software)</li><li>0 = The A/D conversion is not complete</li></ul>                      |

| bit 5 | RCIF: EUSART Receive Interrupt Flag bit                                                                                                             |

|       | <ul><li>1 = The EUSART receive buffer, RCREG, is full (cleared when RCREG is read)</li><li>0 = The EUSART receive buffer is empty</li></ul>         |

| bit 4 | TXIF: EUSART Transmit Interrupt Flag bit                                                                                                            |

|       | <ul> <li>1 = The EUSART transmit buffer, TXREG, is empty (cleared when TXREG is written)</li> <li>0 = The EUSART transmit buffer is full</li> </ul> |

| bit 3 | SSP1IF: Master Synchronous Serial Port 1 Interrupt Flag bit                                                                                         |

|       | <ul><li>1 = The transmission/reception is complete (must be cleared in software)</li><li>0 = Waiting to transmit/receive</li></ul>                  |

| bit 2 | CCP1IF: ECCP1/CCP1 Interrupt Flag bit                                                                                                               |

|       | Capture mode:                                                                                                                                       |

|       | <ul><li>1 = A TMR1 register capture occurred (must be cleared in software)</li><li>0 = No TMR1 register capture occurred</li></ul>                  |

|       | Compare mode:                                                                                                                                       |

|       | <ul><li>1 = A TMR1 register compare match occurred (must be cleared in software)</li><li>0 = No TMR1 register compare match occurred</li></ul>      |

|       | <u>PWM mode:</u><br>Unused in this mode.                                                                                                            |

| bit 1 | TMR2IF: TMR2 to PR2 Match Interrupt Flag bit                                                                                                        |

|       | <ul><li>1 = TMR2 to PR2 match occurred (must be cleared in software)</li><li>0 = No TMR2 to PR2 match occurred</li></ul>                            |

| bit 0 | TMR1IF: TMR1 Overflow Interrupt Flag bit                                                                                                            |

|       | <ul><li>1 = TMR1 register overflowed (must be cleared in software)</li><li>0 = TMR1 register did not overflow</li></ul>                             |

|       |                                                                                                                                                     |

Note 1: This bit is not implemented on 28-pin devices and should be read as '0'.

# REGISTER 9-5: PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2

| R/W-0        | R/W-0                   | U-0                                     | U-0           | R/W-0             | U-0             | U-0              | R/W-0    |

|--------------|-------------------------|-----------------------------------------|---------------|-------------------|-----------------|------------------|----------|

| OSCFIF       | CMIF                    | _                                       | _             | BCLIF             | _               | —                | CCP2IF   |

| bit 7        | ·                       |                                         |               | ·                 |                 | ·                | bit 0    |

|              |                         |                                         |               |                   |                 |                  |          |

| Legend:      |                         |                                         |               |                   |                 |                  |          |

| R = Readab   | le bit                  | W = Writable b                          | oit           | U = Unimplem      | nented bit, rea | id as '0'        |          |

| -n = Value a | t POR                   | '1' = Bit is set                        |               | '0' = Bit is clea | ared            | x = Bit is unk   | nown     |

|              |                         |                                         |               |                   |                 |                  |          |

| bit 7        | OSCFIF: Os              | cillator Fail Interr                    | upt Flag bit  |                   |                 |                  |          |

|              |                         | oscillator failed, c                    | lock input ha | s changed to IN   | TOSC (must l    | be cleared in so | oftware) |

|              |                         | clock operating                         |               |                   |                 |                  |          |

| bit 6        | 1                       | parator Interrupt F                     | 0             |                   |                 |                  |          |

|              |                         | ator input has ch                       | <b>U</b> (    | be cleared in sc  | oftware)        |                  |          |

|              | •                       | ator input has no                       | 0             |                   |                 |                  |          |

| bit 5-4      | •                       | ited: Read as '0                        |               |                   |                 |                  |          |

| bit 3        |                         | Collision Interrup                      | •             | ,                 |                 |                  |          |

|              |                         | ollision occurred<br>collision occurred | •             | ared in software) |                 |                  |          |

| bit 2-1      | 0 .10 .000              | ited: Read as '0                        | -             |                   |                 |                  |          |

| bit 0        | •                       | P2 Interrupt Flag                       |               |                   |                 |                  |          |

|              | Capture mod             | 1 0                                     | 1 010         |                   |                 |                  |          |

|              |                         | register capture                        | occurred (m   | ust be cleared ir | software)       |                  |          |

|              | 0 = No TMR              | R1 register captur                      | e occurred    |                   | ,               |                  |          |

|              | Compare mo              |                                         |               |                   |                 |                  |          |

|              |                         | register compar                         |               | •                 | eared in softw  | vare)            |          |

|              | 0 = NO IMR<br>PWM mode: | R1 register compa                       | are match oc  | currea            |                 |                  |          |

|              | PVVIVI mode:            |                                         |               |                   |                 |                  |          |

# REGISTER 9-6: PIR3: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 3

| R/W-0  | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|--------|-----|-----|-----|-----|-----|-------|

| SSP2IF | BCL2IF | —   | —   | —   | —   | —   | —     |

| bit 7  | •      |     |     |     |     |     | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

|                   |                  |                       |                    |

| bit 7   | SSP2IF: Master Synchronous Serial Port 2 Interrupt Flag bit                                                                        |

|---------|------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul><li>1 = The transmission/reception is complete (must be cleared in software)</li><li>0 = Waiting to transmit/receive</li></ul> |

| bit 6   | BCL2IF: Bus Collision Interrupt Flag bit (MSSP2 module)                                                                            |

|         | 1 = A bus collision occurred (must be cleared in software)                                                                         |

|         | 0 = No bus collision occurred                                                                                                      |

| bit 5-0 | Unimplemented: Read as '0'                                                                                                         |

|         |                                                                                                                                    |

|             | SYNC = 0, BRGH = 0, BRG16 = 0 |            |                             |                       |            |                             |                       |                   |                             |                       |                  |                             |  |

|-------------|-------------------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|-------------------|-----------------------------|-----------------------|------------------|-----------------------------|--|

| BAUD        | Fosc                          | = 40.000   | 0 MHz                       | Fosc                  | = 20.000   | 0 MHz                       | Fosc                  | Fosc = 10.000 MHz |                             |                       | Fosc = 8.000 MHz |                             |  |

| RATE<br>(K) | (K) Actual %                  | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) |  |

| 0.3         | —                             | _          | _                           |                       | _          | _                           | _                     |                   |                             | _                     | _                | _                           |  |

| 1.2         | —                             | —          | —                           | 1.221                 | 1.73       | 255                         | 1.202                 | 0.16              | 129                         | 1.201                 | -0.16            | 103                         |  |

| 2.4         | 2.441                         | 1.73       | 255                         | 2.404                 | 0.16       | 129                         | 2.404                 | 0.16              | 64                          | 2.403                 | -0.16            | 51                          |  |

| 9.6         | 9.615                         | 0.16       | 64                          | 9.766                 | 1.73       | 31                          | 9.766                 | 1.73              | 15                          | 9.615                 | -0.16            | 12                          |  |

| 19.2        | 19.531                        | 1.73       | 31                          | 19.531                | 1.73       | 15                          | 19.531                | 1.73              | 7                           | —                     | _                | _                           |  |

| 57.6        | 56.818                        | -1.36      | 10                          | 62.500                | 8.51       | 4                           | 52.083                | -9.58             | 2                           | _                     | _                | _                           |  |

| 115.2       | 125.000                       | 8.51       | 4                           | 104.167               | -9.58      | 2                           | 78.125                | -32.18            | 1                           | —                     | —                | —                           |  |

| TABLE 17-3: | <b>BAUD RATES FOR ASYNCHRONOUS MODES</b> |  |

|-------------|------------------------------------------|--|

| IADLE II-J. | DAUD KATES FUR ASTINGTRUNUUS MUDES       |  |

|             | SYNC = 0, BRGH = 0, BRG16 = 0 |            |                             |                       |            |                             |                       |                  |                             |  |  |  |

|-------------|-------------------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------------|-----------------------------|--|--|--|

| BAUD        | Fos                           | c = 4.000  | MHz                         | Fos                   | c = 2.000  | MHz                         | Fos                   | Fosc = 1.000 MHz |                             |  |  |  |

| RATE<br>(K) | Actual<br>Rate<br>(K)         | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) |  |  |  |

| 0.3         | 0.300                         | 0.16       | 207                         | 0.300                 | -0.16      | 103                         | 0.300                 | -0.16            | 51                          |  |  |  |

| 1.2         | 1.202                         | 0.16       | 51                          | 1.201                 | -0.16      | 25                          | 1.201                 | -0.16            | 12                          |  |  |  |

| 2.4         | 2.404                         | 0.16       | 25                          | 2.403                 | -0.16      | 12                          | —                     | —                | _                           |  |  |  |

| 9.6         | 8.929                         | -6.99      | 6                           | —                     | _          | —                           | —                     | —                | _                           |  |  |  |

| 19.2        | 20.833                        | 8.51       | 2                           | _                     | _          | —                           | —                     | _                | _                           |  |  |  |

| 57.6        | 62.500                        | 8.51       | 0                           | —                     | _          | —                           | —                     | —                | _                           |  |  |  |

| 115.2       | 62.500                        | -45.75     | 0                           | —                     | —          | —                           | —                     | —                | _                           |  |  |  |

|              |                       | SYNC = 0, BRGH = 1, BRG16 = 0 |                             |                       |            |                             |                       |            |                             |                       |            |                             |  |  |

|--------------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|

| BAUD<br>RATE | Fosc = 40.000 MHz     |                               |                             | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |            |                             | Fosc = 8.000 MHz      |            |                             |  |  |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |

| 0.3          | _                     | _                             | _                           | _                     | _          | _                           | _                     |            | _                           |                       | _          | _                           |  |  |

| 1.2          | —                     | —                             | —                           | —                     | —          | —                           | —                     |            | —                           | —                     | —          | —                           |  |  |

| 2.4          | -                     | _                             | _                           | —                     | _          | —                           | 2.441                 | 1.73       | 255                         | 2.403                 | -0.16      | 207                         |  |  |

| 9.6          | 9.766                 | 1.73                          | 255                         | 9.615                 | 0.16       | 129                         | 9.615                 | 0.16       | 64                          | 9.615                 | -0.16      | 51                          |  |  |

| 19.2         | 19.231                | 0.16                          | 129                         | 19.231                | 0.16       | 64                          | 19.531                | 1.73       | 31                          | 19.230                | -0.16      | 25                          |  |  |

| 57.6         | 58.140                | 0.94                          | 42                          | 56.818                | -1.36      | 21                          | 56.818                | -1.36      | 10                          | 55.555                | 3.55       | 8                           |  |  |

| 115.2        | 113.636               | -1.36                         | 21                          | 113.636               | -1.36      | 10                          | 125.000               | 8.51       | 4                           | —                     | _          | _                           |  |  |

|             | SYNC = 0, BRGH = 1, BRG16 = 0 |            |                             |                       |            |                             |                       |            |                             |  |  |  |

|-------------|-------------------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|--|

| BAUD        | Foso                          | 2 = 4.000  | MHz                         | Fos                   | c = 2.000  | MHz                         | Fosc = 1.000 MHz      |            |                             |  |  |  |

| RATE<br>(K) | Actual<br>Rate<br>(K)         | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |

| 0.3         | _                             | _          | _                           |                       | _          | _                           | 0.300                 | -0.16      | 207                         |  |  |  |

| 1.2         | 1.202                         | 0.16       | 207                         | 1.201                 | -0.16      | 103                         | 1.201                 | -0.16      | 51                          |  |  |  |

| 2.4         | 2.404                         | 0.16       | 103                         | 2.403                 | -0.16      | 51                          | 2.403                 | -0.16      | 25                          |  |  |  |

| 9.6         | 9.615                         | 0.16       | 25                          | 9.615                 | -0.16      | 12                          | —                     | —          | —                           |  |  |  |

| 19.2        | 19.231                        | 0.16       | 12                          | —                     | _          | _                           | —                     | _          | —                           |  |  |  |

| 57.6        | 62.500                        | 8.51       | 3                           | —                     | —          | —                           | —                     | —          | —                           |  |  |  |

| 115.2       | 125.000                       | 8.51       | 1                           | —                     | _          | _                           | —                     | _          | _                           |  |  |  |

¤ 2009 Microchip Technology Inc.

# PIC18F45J10 FAMILY

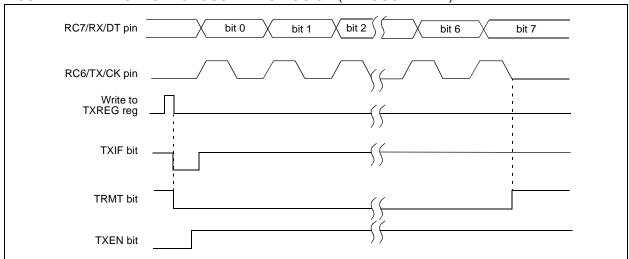

# FIGURE 17-12: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

## TABLE 17-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Name    | Bit 7                                            | Bit 6       | Bit 5       | Bit 4      | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|--------------------------------------------------|-------------|-------------|------------|--------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH                                         | PEIE/GIEL   | TMR0IE      | INT0IE     | RBIE   | TMR0IF | INT0IF | RBIF   | 47                         |

| PIR1    | PSPIF <sup>(1)</sup>                             | ADIF        | RCIF        | TXIF       | SSP1IF | CCP1IF | TMR2IF | TMR1IF | 49                         |

| PIE1    | PSPIE <sup>(1)</sup>                             | ADIE        | RCIE        | TXIE       | SSP1IE | CCP1IE | TMR2IE | TMR1IE | 49                         |

| IPR1    | PSPIP <sup>(1)</sup>                             | ADIP        | RCIP        | TXIP       | SSP1IP | CCP1IP | TMR2IP | TMR1IP | 49                         |

| RCSTA   | SPEN                                             | RX9         | SREN        | CREN       | ADDEN  | FERR   | OERR   | RX9D   | 49                         |

| TXREG   | EUSART T                                         | ransmit Reg | ister       |            |        |        |        |        | 49                         |

| TXSTA   | CSRC                                             | TX9         | TXEN        | SYNC       | SENDB  | BRGH   | TRMT   | TX9D   | 49                         |

| BAUDCON | ABDOVF                                           | RCIDL       |             | SCKP       | BRG16  | —      | WUE    | ABDEN  | 49                         |

| SPBRGH  | GH EUSART Baud Rate Generator Register High Byte |             |             |            |        |        |        |        |                            |

| SPBRG   | EUSART E                                         | Baud Rate G | enerator Re | gister Low | Byte   |        |        |        | 49                         |

Legend: — = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

Note 1: These bits are not implemented on 28-pin devices and should be read as '0'.