Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

EXF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 21                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 10x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf25j10-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| ABLE 1-1: DEVICE FEATURES               |                                                                                                                        |                                                                                                                        |                                                                                                                        |                                                                                                                        |  |  |  |  |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Features                                | PIC18F24J10                                                                                                            | PIC18F25J10                                                                                                            | PIC18F44J10                                                                                                            | PIC18F45J10                                                                                                            |  |  |  |  |

| Operating Frequency                     | DC – 40 MHz                                                                                                            |  |  |  |  |

| Program Memory (Bytes)                  | 16384                                                                                                                  | 32768                                                                                                                  | 16384                                                                                                                  | 32768                                                                                                                  |  |  |  |  |

| Program Memory<br>(Instructions)        | 8192                                                                                                                   | 16384                                                                                                                  | 8192                                                                                                                   | 16384                                                                                                                  |  |  |  |  |

| Data Memory (Bytes)                     | 1024                                                                                                                   | 1024                                                                                                                   | 1024                                                                                                                   | 1024                                                                                                                   |  |  |  |  |

| Interrupt Sources                       | 19                                                                                                                     | 19                                                                                                                     | 20                                                                                                                     | 20                                                                                                                     |  |  |  |  |

| I/O Ports                               | Ports A, B, C                                                                                                          | Ports A, B, C                                                                                                          | Ports A, B, C, D, E                                                                                                    | Ports A, B, C, D, E                                                                                                    |  |  |  |  |

| Timers                                  | 3                                                                                                                      | 3                                                                                                                      | 3                                                                                                                      | 3                                                                                                                      |  |  |  |  |

| Capture/Compare/PWM Modules             | 2                                                                                                                      | 2                                                                                                                      | 1                                                                                                                      | 1                                                                                                                      |  |  |  |  |

| Enhanced<br>Capture/Compare/PWM Modules | 0                                                                                                                      | 0                                                                                                                      | 1                                                                                                                      | 1                                                                                                                      |  |  |  |  |

| Serial Communications                   | MSSP,<br>Enhanced USART                                                                                                | MSSP,<br>Enhanced USART                                                                                                | MSSP,<br>Enhanced USART                                                                                                | MSSP,<br>Enhanced USART                                                                                                |  |  |  |  |

| Parallel Communications (PSP)           | No                                                                                                                     | No                                                                                                                     | Yes                                                                                                                    | Yes                                                                                                                    |  |  |  |  |

| 10-Bit Analog-to-Digital Module         | 10 Input Channels                                                                                                      | 10 Input Channels                                                                                                      | 13 Input Channels                                                                                                      | 13 Input Channels                                                                                                      |  |  |  |  |

| Resets (and Delays)                     | POR, BOR <sup>(1)</sup> ,<br>RESET Instruction,<br>Stack Full, Stack<br>Underflow (PWRT,<br><u>OS</u> T),<br>MCLR, WDT | POR, BOR <sup>(1)</sup> ,<br>RESET Instruction,<br>Stack Full, Stack<br>Underflow (PWRT,<br><u>OS</u> T),<br>MCLR, WDT | POR, BOR <sup>(1)</sup> ,<br>RESET Instruction,<br>Stack Full, Stack<br>Underflow (PWRT,<br><u>OS</u> T),<br>MCLR, WDT | POR, BOR <sup>(1)</sup> ,<br>RESET Instruction,<br>Stack Full, Stack<br>Underflow (PWRT,<br><u>OS</u> T),<br>MCLR, WDT |  |  |  |  |

| Programmable Brown-out Reset            | Yes                                                                                                                    | Yes                                                                                                                    | Yes                                                                                                                    | Yes                                                                                                                    |  |  |  |  |

| Instruction Set                         | 75 Instructions;<br>83 with Extended<br>Instruction Set enabled                                                        |  |  |  |  |

| Packages                                | 28-pin SPDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN                                                               | 28-pin SPDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN                                                               | 40-pin PDIP<br>44-pin QFN<br>44-pin TQFP                                                                               | 40-pin PDIP<br>44-pin QFN<br>44-pin TQFP                                                                               |  |  |  |  |

### TABLE 1-1: DEVICE FEATURES

**Note 1:** BOR is not available in PIC18LF2XJ10/4XJ10 devices.

| Pin Name                                                                                                            | Pin Number |     | Pin Buffer |        | Description |                                                                                                                                                                                                                           |  |

|---------------------------------------------------------------------------------------------------------------------|------------|-----|------------|--------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Fininame                                                                                                            | PDIP       | QFN | TQFP       | Туре   | Туре        | Description                                                                                                                                                                                                               |  |

| MCLR<br>MCLR                                                                                                        | 1          | 18  | 18         | ļ      | ST          | Master Clear (input) or programming voltage (input).<br>Master Clear (Reset) input. This pin is an active-low<br>Reset to the device.                                                                                     |  |

| OSC1/CLKI<br>OSC1<br>CLKI                                                                                           | 13         | 32  | 30         | <br>   | CMOS        | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input.<br>External clock source input. Always associated with<br>pin function OSC1. See related OSC2/CLKO pins.          |  |

| OSC2/CLKO<br>OSC2<br>CLKO                                                                                           | 14         | 33  | 31         | 0<br>0 | _           | Oscillator crystal or clock output.<br>Oscillator crystal output. Connects to crystal<br>or resonator in Crystal Oscillator mode.<br>In RC mode, OSC2 pin outputs CLKO which<br>has 1/4 the frequency of OSC1 and denotes |  |

| Legend: TTL = TTL compatible input       the instruction cycle rate.         CMOS = CMOS compatible input or output |            |     |            |        |             |                                                                                                                                                                                                                           |  |

### TABLE 1-3:PIC18F44J10/45J10 PINOUT I/O DESCRIPTIONS

ST = Schmitt Trigger input with CMOS levels I = Input O = Output P = Power

**Note 1:** Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

# 6.1.3 PROGRAM COUNTER

The Program Counter (PC) specifies the address of the instruction to fetch for execution. The PC is 21 bits wide and is contained in three separate 8-bit registers. The low byte, known as the PCL register, is both readable and writable. The high byte, or PCH register, contains the PC<15:8> bits; it is not directly readable or writable. Updates to the PCH register are performed through the PCLATH register. The upper byte is called PCU. This register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCH register. Updates to the PCU register are performed through the PCLATH register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCU register are performed through the PCLATU register.

The contents of PCLATH and PCLATU are transferred to the program counter by any operation that writes PCL. Similarly, the upper two bytes of the program counter are transferred to PCLATH and PCLATU by an operation that reads PCL. This is useful for computed offsets to the PC (see **Section 6.1.6.1 "Computed GOTO"**).

The PC addresses bytes in the program memory. To prevent the PC from becoming misaligned with word instructions, the Least Significant bit of PCL is fixed to a value of '0'. The PC increments by 2 to address sequential instructions in the program memory.

The CALL, RCALL, GOTO and program branch instructions write to the program counter directly. For these instructions, the contents of PCLATH and PCLATU are not transferred to the program counter.

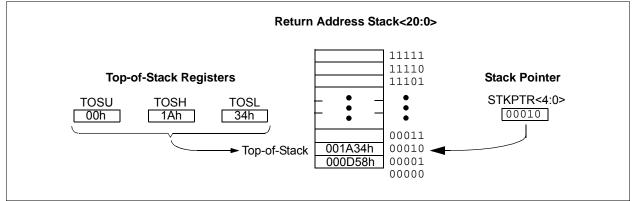

### 6.1.4 RETURN ADDRESS STACK

The return address stack allows any combination of up to 31 program calls and interrupts to occur. The PC is pushed onto the stack when a CALL or RCALL instruction is executed or an interrupt is Acknowledged. The PC value is pulled off the stack on a RETURN, RETLW or RETFIE instruction. PCLATU and PCLATH are not affected by any of the RETURN or CALL instructions.

The stack operates as a 31-word by 21-bit RAM and a 5-bit Stack Pointer, STKPTR. The stack space is not part of either program or data space. The Stack Pointer is readable and writable and the address on the top of the stack is readable and writable through the top-of-stack Special Function Registers. Data can also be pushed to, or popped from the stack, using these registers.

A CALL type instruction causes a push onto the stack; the Stack Pointer is first incremented and the location pointed to by the Stack Pointer is written with the contents of the PC (already pointing to the instruction following the CALL). A RETURN type instruction causes a pop from the stack; the contents of the location pointed to by the STKPTR are transferred to the PC and then the Stack Pointer is decremented.

The Stack Pointer is initialized to '00000' after all Resets. There is no RAM associated with the location corresponding to a Stack Pointer value of '00000'; this is only a Reset value. Status bits indicate if the stack is full or has overflowed or has underflowed.

### 6.1.4.1 Top-of-Stack Access

Only the top of the return address stack (TOS) is readable and writable. A set of three registers, TOSU:TOSH:TOSL, hold the contents of the stack location pointed to by the STKPTR register (Figure 6-3). This allows users to implement a software stack if necessary. After a CALL, RCALL or interrupt, the software can read the pushed value by reading the TOSU:TOSH:TOSL registers. These values can be placed on a user-defined software stack. At return time, the software can return these values to TOSU:TOSH:TOSL and do a return.

The user must disable the global interrupt enable bits while accessing the stack to prevent inadvertent stack corruption.

# FIGURE 6-3: RETURN ADDRESS STACK AND ASSOCIATED REGISTERS

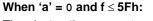

### FIGURE 6-9: COMPARING ADDRESSING OPTIONS FOR BIT-ORIENTED AND BYTE-ORIENTED INSTRUCTIONS (EXTENDED INSTRUCTION SET ENABLED)

Example Instruction: ADDWF, f, d, a (Opcode: 0010 01da ffff ffff)

### When 'a' = 0 and $f \ge 60h$ :

The instruction executes in Direct Forced mode. 'f' is interpreted as a location in the Access RAM between 060h and 0FFh. This is the same as locations 060h to 07Fh (Bank 0) and F80h to FFFh (Bank 15) of data memory.

Locations below 60h are not available in this addressing mode.

The instruction executes in Indexed Literal Offset mode. 'f' is interpreted as an offset to the address value in FSR2. The two are added together to obtain the address of the target register for the instruction. The address can be anywhere in the data memory space.

Note that in this mode, the correct syntax is now: ADDWF [k], d where 'k' is the same as 'f'.

#### When 'a' = 1 (all values of f):

The instruction executes in Direct mode (also known as Direct Long mode). 'f' is interpreted as a location in one of the 16 banks of the data memory space. The bank is designated by the Bank Select Register (BSR). The address can be in any implemented bank in the data memory space.

# 7.4 Erasing Flash Program Memory

The minimum erase block is 1024 bytes. Only through the use of an external programmer, or through ICSP control, can larger blocks of program memory be Bulk Erased. Word Erase in the Flash array is not supported.

When initiating an erase sequence from the microcontroller itself, a block of 1024 bytes of program memory is erased. The Most Significant 7 bits of the TBLPTR<21:10> point to the block being erased. TBLPTR<9:0> are ignored.

The EECON1 register commands the erase operation. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation.

For protection, the write initiate sequence for EECON2 must be used.

A long write is necessary for erasing the internal Flash. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

### 7.4.1 FLASH PROGRAM MEMORY ERASE SEQUENCE

The sequence of events for erasing a block of internal program memory location is:

- 1. Load Table Pointer register with address of the block being erased.

- 2. Set the WREN and FREE bits (EECON1<2,4>) to enable the erase operation.

- 3. Disable interrupts.

- 4. Write 55h to EECON2.

- 5. Write 0AAh to EECON2.

- 6. Set the WR bit. This will begin the erase cycle.

- The CPU will stall for duration of the erase for TIE (see parameter D133B).

- 8. Re-enable interrupts.

| EXAMPLE 7-2: | ERASING A FLASH PROGRAM MEMORY BLOCK |

|--------------|--------------------------------------|

|           | MOVLW | CODE_ADDR_UPPER | ; load TBLPTR with the base   |

|-----------|-------|-----------------|-------------------------------|

|           | MOVWF | TBLPTRU         | ; address of the memory block |

|           | MOVLW | CODE_ADDR_HIGH  |                               |

|           | MOVWF | TBLPTRH         |                               |

|           | MOVLW | CODE_ADDR_LOW   |                               |

|           | MOVWF | TBLPTRL         |                               |

| ERASE_ROW |       |                 |                               |

|           | BSF   | EECON1, WREN    | ; enable write to memory      |

|           | BSF   | EECON1, FREE    | ; enable Erase operation      |

|           | BCF   | INTCON, GIE     | ; disable interrupts          |

| Required  | MOVLW | 55h             |                               |

| Sequence  | MOVWF | EECON2          | ; write 55h                   |

|           | MOVLW | 0AAh            |                               |

|           | MOVWF | EECON2          | ; write OAAh                  |

|           | BSF   | EECON1, WR      | ; start erase (CPU stall)     |

|           | BSF   | INTCON, GIE     | ; re-enable interrupts        |

|           |       |                 |                               |

Example 8-3 shows the sequence to do a 16 x 16 unsigned multiplication. Equation 8-1 shows the algorithm that is used. The 32-bit result is stored in four registers (RES3:RES0).

### EQUATION 8-1: 16 x 16 UNSIGNED MULTIPLICATION ALGORITHM

| RES3:RES0 | = | ARG1H:ARG1L • ARG2H:ARG2L                |

|-----------|---|------------------------------------------|

|           | = | $(ARG1H \bullet ARG2H \bullet 2^{16}) +$ |

|           |   | $(ARG1H \bullet ARG2L \bullet 2^8) +$    |

|           |   | $(ARG1L \bullet ARG2H \bullet 2^8) +$    |

|           |   | (ARG1L • ARG2L)                          |

### EXAMPLE 8-3: 1

#### 16 x 16 UNSIGNED MULTIPLY ROUTINE

|   | MOVF   | ARG1L, W    |                   |

|---|--------|-------------|-------------------|

|   | MULWF  |             | ; ARG1L * ARG2L-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVFF  | PRODH, RES1 | ;                 |

|   |        | PRODL, RESO |                   |

| ; |        |             |                   |

|   | MOVF   | ARG1H, W    |                   |

|   |        |             | ; ARG1H * ARG2H-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVFF  | PRODH, RES3 | ;                 |

|   |        | PRODL, RES2 | ;                 |

| ; |        |             |                   |

|   | MOVF   | ARG1L, W    |                   |

|   |        |             | ; ARG1L * ARG2H-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVF   | PRODL, W    | ;                 |

|   | ADDWF  | RES1, F     | ; Add cross       |

|   | MOVF   | PRODH, W    | ; products        |

|   | ADDWFC | RES2, F     | ;                 |

|   | CLRF   | WREG        | ;                 |

|   | ADDWFC | RES3, F     | ;                 |

| ; |        |             |                   |

|   | MOVF   | ARG1H, W    | ;                 |

|   | MULWF  | ARG2L       | ; ARG1H * ARG2L-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVF   | PRODL, W    | ;                 |

|   | ADDWF  | RES1, F     | ; Add cross       |

|   | MOVF   | PRODH, W    | ; products        |

|   | ADDWFC | RES2, F     | ;                 |

|   | CLRF   | WREG        | ;                 |

|   | ADDWFC | RES3, F     | ;                 |

|   |        |             |                   |

Example 8-4 shows the sequence to do a 16 x 16 signed multiply. Equation 8-2 shows the algorithm used. The 32-bit result is stored in four registers (RES3:RES0). To account for the sign bits of the arguments, the MSb for each argument pair is tested and the appropriate subtractions are done.

### EQUATION 8-2: 16 x 16 SIGNED MULTIPLICATION ALGORITHM

| RES3:RES0 = ARG1H:ARG1L • ARG2H:ARG2L                            |

|------------------------------------------------------------------|

| $= (ARG1H \bullet ARG2H \bullet 2^{16}) +$                       |

| $(ARG1H \bullet ARG2L \bullet 2^8) +$                            |

| $(ARG1L \bullet ARG2H \bullet 2^8) +$                            |

| $(ARG1L \bullet ARG2L) +$                                        |

| $(-1 \bullet ARG2H < 7 > \bullet ARG1H: ARG1L \bullet 2^{16}) +$ |

| $(-1 \bullet ARG1H < 7 > \bullet ARG2H:ARG2L \bullet 2^{16})$    |

|                                                                  |

#### EXAMPLE 8-4: 16 x 16 SIGNED MULTIPLY ROUTINE

|     |        | INICEI            |                    |

|-----|--------|-------------------|--------------------|

|     | MOVF   | ARG1L, W          |                    |

|     | MULWF  | ARG2L             | ; ARG1L * ARG2L -> |

|     |        |                   | ; PRODH:PRODL      |

|     | MOVFF  | PRODH, RES1       |                    |

|     | MOVFF  | PRODL, RESO       |                    |

| ;   |        | ,                 |                    |

|     | MOVF   | ARG1H, W          |                    |

|     | MULWF  |                   | ; ARG1H * ARG2H -> |

|     | NOLWE  | AROZII            | ; PRODH:PRODL      |

|     | MOVEE  | PRODH, RES3       |                    |

|     | MOVFF  |                   |                    |

| ;   | MOVEE  | PRODL, RES2       | ,                  |

| '   | MOVE   |                   |                    |

|     | MOVF   | ARG1L, W<br>ARG2H |                    |

|     | MOLWF  | ARGZH             | ; ARG1L * ARG2H -> |

|     |        |                   | ; PRODH:PRODL      |

|     | MOVF   | PRODL, W          | ;                  |

|     | ADDWF  | RES1, F           | ; Add cross        |

|     |        |                   | ; products         |

|     |        | RES2, F           | ;                  |

|     | CLRF   |                   | i                  |

|     | ADDWFC | RES3, F           | i                  |

| ;   |        |                   |                    |

|     |        | ARG1H, W          | ;                  |

|     | MULWF  | ARG2L             | ; ARG1H * ARG2L -> |

|     |        |                   | ; PRODH:PRODL      |

|     | MOVF   | PRODL, W          | ;                  |

|     | ADDWF  | RES1, F           | ; Add cross        |

|     | MOVF.  | PRODH, W          | ; products         |

|     | ADDWFC | RES2, F           | ;                  |

|     | CLRF   |                   | ;                  |

|     | ADDWFC | RES3, F           | ;                  |

| ;   |        |                   |                    |

|     | BTFSS  | ARG2H, 7          | ; ARG2H:ARG2L neg? |

|     | BRA    | SIGN_ARG1         | ; no, check ARG1   |

|     | MOVF   | ARG1L, W          | ;                  |

|     | SUBWF  | RES2              | ;                  |

|     | MOVF   | ARG1H, W          | ;                  |

|     | SUBWFB | RES3              |                    |

| ;   |        |                   |                    |

| SIG | N_ARG1 |                   |                    |

|     | BTFSS  | ARG1H, 7          | ; ARG1H:ARG1L neg? |

|     | BRA    | CONT_CODE         | ; no, done         |

|     | MOVF   | ARG2L, W          | ;                  |

|     | SUBWF  | RES2              | ;                  |

|     | MOVF   | ARG2H, W          | ;                  |

|     | SUBWFB |                   |                    |

| ;   |        |                   |                    |

|     | T_CODE |                   |                    |

|     | :      |                   |                    |

|     |        |                   |                    |

# 9.0 INTERRUPTS

Members of the PIC18F45J10 family of devices have multiple interrupt sources and an interrupt priority feature that allows most interrupt sources to be assigned a high-priority level or a low-priority level. The high-priority interrupt vector is at 0008h and the low-priority interrupt vector is at 0018h. High-priority interrupt events will interrupt any low-priority interrupts that may be in progress.

There are thirteen registers which are used to control interrupt operation. These registers are:

- RCON

- INTCON

- INTCON2

- INTCON3

- PIR1, PIR2, PIR3

- PIE1, PIE2, PIE3

- IPR1, IPR2, IPR3

It is recommended that the Microchip header files supplied with MPLAB<sup>®</sup> IDE be used for the symbolic bit names in these registers. This allows the assembler/compiler to automatically take care of the placement of these bits within the specified register.

In general, interrupt sources have three bits to control their operation. They are:

- Flag bit to indicate that an interrupt event occurred

- Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set

- **Priority bit** to select high priority or low priority

The interrupt priority feature is enabled by setting the IPEN bit (RCON<7>). When interrupt priority is enabled, there are two bits which enable interrupts globally. Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set (high priority). Setting the GIEL bit (INTCON<6>) enables all interrupts that have the priority bit cleared (low priority). When the interrupt flag, enable bit and appropriate global interrupt enable bit are set, the interrupt will vector immediately to address 0008h or 0018h, depending on the priority bit setting. Individual interrupts can be disabled through their corresponding enable bits.

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup> mid-range devices. In Compatibility mode, the interrupt priority bits for each source have no effect. INTCON<6> is the PEIE bit which enables/disables all peripheral interrupt sources. INTCON<7> is the GIE bit which enables/disables all interrupt sources. All interrupts branch to address 0008h in Compatibility mode.

When an interrupt is responded to, the global interrupt enable bit is cleared to disable further interrupts. If the IPEN bit is cleared, this is the GIE bit. If interrupt priority levels are used, this will be either the GIEH or GIEL bit. High-priority interrupt sources can interrupt a low-priority interrupt. Low-priority interrupts are not processed while high-priority interrupts are in progress.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (0008h or 0018h). Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bits must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used) which re-enables interrupts.

For external interrupt events, such as the INTx pins or the PORTB input change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding enable bit or the GIE bit.

Note: Do not use the MOVFF instruction to modify any of the interrupt control registers while any interrupt is enabled. Doing so may cause erratic microcontroller behavior.

| R/W-1         | R/W-1         | U-0                | U-0               | R/W-1             | U-0              | U-0             | R/W-0  |

|---------------|---------------|--------------------|-------------------|-------------------|------------------|-----------------|--------|

| OSCFIP        | CMIP          | —                  | —                 | BCL1IP            | —                | —               | CCP2IP |

| bit 7         |               |                    |                   |                   |                  | •               | bit 0  |

|               |               |                    |                   |                   |                  |                 |        |

| Legend:       |               |                    |                   |                   |                  |                 |        |

| R = Readable  | e bit         | W = Writable I     | oit               | U = Unimplem      | nented bit, read | l as '0'        |        |

| -n = Value at | POR           | '1' = Bit is set   |                   | '0' = Bit is clea | ared             | x = Bit is unkr | iown   |

|               |               |                    |                   |                   |                  |                 |        |

| bit 7         | OSCFIP: Osc   | illator Fail Inter | rupt Priority bit | t                 |                  |                 |        |

|               | 1 = High prio | •                  |                   |                   |                  |                 |        |

|               | 0 = Low prior | rity               |                   |                   |                  |                 |        |

| bit 6         | CMIP: Compa   | arator Interrupt   | Priority bit      |                   |                  |                 |        |

|               | 1 = High prio | •                  |                   |                   |                  |                 |        |

|               | 0 = Low prior | ity                |                   |                   |                  |                 |        |

| bit 5-4       | Unimplemen    | ted: Read as '0    | )'                |                   |                  |                 |        |

| bit 3         | BCL1IP: Bus   | Collision Interr   | upt Priority bit  | (MSSP1 modul      | le)              |                 |        |

|               | 1 = High prio |                    |                   |                   |                  |                 |        |

|               | 0 = Low prior | rity               |                   |                   |                  |                 |        |

| bit 2-1       | Unimplemen    | ted: Read as '0    | )'                |                   |                  |                 |        |

| bit 0         | CCP2IP: CCF   | P2 Interrupt Price | ority bit         |                   |                  |                 |        |

|               | 1 = High prio | rity               |                   |                   |                  |                 |        |

|               | 0 = Low prior | ity                |                   |                   |                  |                 |        |

|               |               |                    |                   |                   |                  |                 |        |

### REGISTER 9-12: IPR3: PERIPHERAL INTERRUPT PRIORITY REGISTER 3

| R/W-1  | R/W-1  | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|--------|-----|-----|-----|-----|-----|-------|

| SSP2IP | BCL2IP | —   | —   | —   | —   | —   | —     |

| bit 7  |        |     |     |     |     |     | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7

SSP2IP: Master Synchronous Serial Port 2 Interrupt Priority bit

1 = High priority

0 = Low priority

bit 6

BCL2IP: Bus Collision Interrupt Priority bit (MSSP2 module)

1 = High priority

0 = Low priority

bit 5-0

Unimplemented: Read as '0'

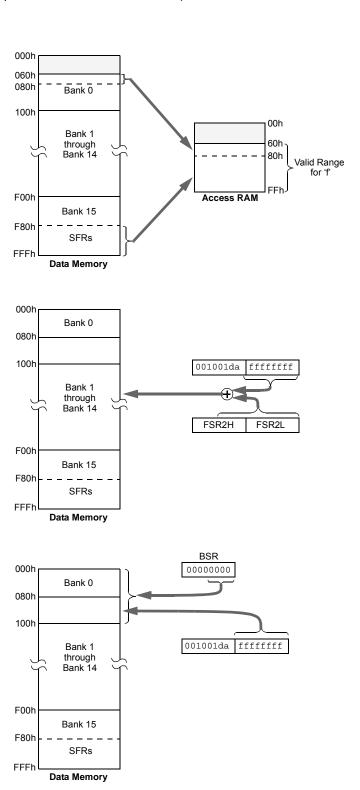

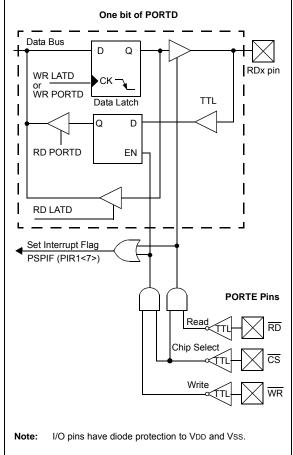

### 10.7 Parallel Slave Port

| Note: | The Parallel Slave Port is only available in |

|-------|----------------------------------------------|

|       | 40/44-pin devices.                           |

In addition to its function as a general I/O port, PORTD can also operate as an 8-bit wide Parallel Slave Port (PSP) or microprocessor port. PSP operation is controlled by the 4 upper bits of the TRISE register (Register 10-1). Setting control bit, PSPMODE (TRISE<4>), enables PSP operation as long as the Enhanced CCP module is not operating in Dual Output or Quad Output PWM mode. In Slave mode, the port is asynchronously readable and writable by the external world.

The PSP can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting the control bit, PSPMODE, enables the PORTE I/O pins to become control inputs for the microprocessor port. When set, port pin RE0 is the RD input, RE1 is the WR input and RE2 is the CS (Chip Select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set). The A/D port configuration bits, PFCG<3:0> (ADCON1<3:0>), must also be set to a value in the range of '1010' through '1111'.

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$  lines are first detected low and ends when either are detected high. The PSPIF and IBF flag bits are both set when the write ends.

A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low. The data in PORTD is read out and the OBF bit is clear. If the user writes new data to PORTD to set OBF, the data is immediately read out; however, the OBF bit is not set.

When either the  $\overline{CS}$  or  $\overline{RD}$  lines are detected high, the PORTD pins return to the input state and the PSPIF bit is set. User applications should wait for PSPIF to be set before servicing the PSP; when this happens, the IBF and OBF bits can be polled and the appropriate action taken. The timing for the control signals in Write and Read modes is shown in Figure 10-4 and Figure 10-5, respectively.

# FIGURE 10-3: PORTD AND PORTE BLOCK DIAGRAM (PARALLEL SLAVE PORT)

### EXAMPLE 12-1: IMPLEMENTING A REAL-TIME CLOCK USING A TIMER1 INTERRUPT SERVICE

| RTCinit |        |              |                                               |

|---------|--------|--------------|-----------------------------------------------|

|         | MOVLW  | 80h          | ; Preload TMR1 register pair                  |

|         | MOVWF  | TMR1H        | ; for 1 second overflow                       |

|         | CLRF   | TMR1L        |                                               |

|         | MOVLW  | b'00001111'  | ; Configure for external clock,               |

|         | MOVWF  | T1CON        | ; Asynchronous operation, external oscillator |

|         | CLRF   | secs         | ; Initialize timekeeping registers            |

|         | CLRF   | mins         | i                                             |

|         | MOVLW  | .12          |                                               |

|         | MOVWF  | hours        |                                               |

|         | BSF    | PIE1, TMR1IE | ; Enable Timer1 interrupt                     |

|         | RETURN |              |                                               |

| RTCisr  |        |              |                                               |

|         | BSF    | TMR1H, 7     | ; Preload for 1 sec overflow                  |

|         | BCF    | PIR1, TMR1IF | ; Clear interrupt flag                        |

|         | INCF   | secs, F      | ; Increment seconds                           |

|         | MOVLW  | .59          | ; 60 seconds elapsed?                         |

|         | CPFSGT | secs         |                                               |

|         | RETURN |              | ; No, done                                    |

|         | CLRF   | secs         | ; Clear seconds                               |

|         | INCF   | mins, F      | ; Increment minutes                           |

|         | MOVLW  | .59          | ; 60 minutes elapsed?                         |

|         | CPFSGT | mins         |                                               |

|         | RETURN |              | ; No, done                                    |

|         | CLRF   | mins         | ; clear minutes                               |

|         | INCF   | hours, F     | ; Increment hours                             |

|         | MOVLW  | .23          | ; 24 hours elapsed?                           |

|         | CPFSGT | hours        |                                               |

|         | RETURN |              | ; No, done                                    |

|         | CLRF   | hours        | ; Reset hours                                 |

|         | RETURN |              | ; Done                                        |

|         |        |              |                                               |

### TABLE 12-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Name   | Bit 7                | Bit 6         | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|----------------------|---------------|---------|---------|---------|--------|--------|--------|----------------------------|

| INTCON | GIE/GIEH             | PEIE/GIEL     | TMR0IE  | INT0IE  | RBIE    | TMR0IF | INT0IF | RBIF   | 47                         |

| PIR1   | PSPIF <sup>(1)</sup> | ADIF          | RCIF    | TXIF    | SSP1IF  | CCP1IF | TMR2IF | TMR1IF | 49                         |

| PIE1   | PSPIE <sup>(1)</sup> | ADIE          | RCIE    | TXIE    | SSP1IE  | CCP1IE | TMR2IE | TMR1IE | 49                         |

| IPR1   | PSPIP <sup>(1)</sup> | ADIP          | RCIP    | TXIP    | SSP1IP  | CCP1IP | TMR2IP | TMR1IP | 49                         |

| TMR1L  | Timer1 Reg           | gister Low By | /te     |         |         |        |        |        | 48                         |

| TMR1H  | Timer1 Reg           | gister High B | yte     |         |         |        |        |        | 48                         |

| T1CON  | RD16                 | T1RUN         | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 48                         |

**Legend:** Shaded cells are not used by the Timer1 module.

Note 1: These bits are not implemented on 28-pin devices and should be read as '0'.

# V+ PIC18F4XJ10 QC FET QA FET Driver Driver P1A Load P1B FET FET Driver Driver P1C QD QB V-P1D

### FIGURE 15-7: EXAMPLE OF FULL-BRIDGE APPLICATION

# 15.4.5.1 Direction Change in Full-Bridge Mode

In the Full-Bridge Output mode, the P1M1 bit in the CCP1CON register allows the user to control the forward/reverse direction. When the application firmware changes this direction control bit, the module will assume the new direction on the next PWM cycle.

Just before the end of the current PWM period, the modulated outputs (P1B and P1D) are placed in their inactive state, while the unmodulated outputs (P1A and P1C) are switched to drive in the opposite direction. This occurs in the time interval, 4 Tosc \* (Timer2 Prescale Value), before the next PWM period begins. The Timer2 prescaler will be either 1, 4 or 16, depending on the value of the T2CKPS<1:0> bits (T2CON<1:0>). During the interval from the switch of the unmodulated outputs to the beginning of the next period, the modulated outputs (P1B and P1D) remain inactive. This relationship is shown in Figure 15-8.

Note that in the Full-Bridge Output mode, the ECCP1 module does not provide any dead-band delay. In general, since only one output is modulated at all times, dead-band delay is not required. However, there is a situation where a dead-band delay might be required. This situation occurs when both of the following conditions are true:

- 1. The direction of the PWM output changes when the duty cycle of the output is at or near 100%.

- 2. The turn-off time of the power switch, including the power device and driver circuit, is greater than the turn-on time.

Figure 15-9 shows an example where the PWM direction changes from forward to reverse at a near 100% duty cycle. At time t1, the outputs P1A and P1D become inactive while output P1C becomes active. In this example, since the turn-off time of the power devices is longer than the turn-on time, a shoot-through current may flow through power devices, QC and QD (see Figure 15-7), for the duration of 't'. The same phenomenon will occur to power devices, QA and QB, for PWM direction change from reverse to forward.

If changing PWM direction at high duty cycle is required for an application, one of the following requirements must be met:

- 1. Reduce PWM for a PWM period before changing directions.

- 2. Use switch drivers that can drive the switches off faster than they can drive them on.

Other options to prevent shoot-through current may exist.

### 15.4.6 PROGRAMMABLE DEAD-BAND DELAY

| Note: | Programmable | dead-band | delay is | not  |

|-------|--------------|-----------|----------|------|

|       | implemented  | in 28-pin | devices  | with |

|       | standard CCP | modules.  |          |      |

In half-bridge applications, where all power switches are modulated at the PWM frequency at all times, the power switches normally require more time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on and the other turned off), both switches may be on for a short period of time until one switch completely turns off. During this brief interval, a very high current (*shootthrough current*) may flow through both power switches, shorting the bridge supply. To avoid this potentially destructive shoot-through current from flowing during switching, turning on either of the power switches is normally delayed to allow the other switch to completely turn off.

In the Half-Bridge Output mode, a digitally programmable dead-band delay is available to avoid shoot-through current from destroying the bridge power switches. The delay occurs at the signal transition from the nonactive state to the active state. See Figure 15-4 for an illustration. Bits PDC<6:0> of the ECCP1DEL register (Register 15-2) set the delay period in terms of microcontroller instruction cycles (TcY or 4 Tosc). These bits are not available in 28-pin devices as the standard CCP module does not support half-bridge operation.

### 15.4.7 ENHANCED PWM AUTO-SHUTDOWN

When the ECCP1 is programmed for any of the Enhanced PWM modes, the active output pins may be configured for auto-shutdown. Auto-shutdown immediately places the Enhanced PWM output pins into a defined shutdown state when a shutdown event occurs.

A shutdown event can be caused by either of the comparator modules, a low level on the Fault input pin (FLT0) or any combination of these three sources. The comparators may be used to monitor a voltage input proportional to a current being monitored in the bridge circuit. If the voltage exceeds a threshold, the comparator switches state and triggers a shutdown. Alternatively, a low digital signal on FLT0 can also trigger a shutdown. The auto-shutdown feature can be disabled by not selecting any auto-shutdown sources. The auto-shutdown sources to be used are selected using the ECCPAS<2:0> bits (bits<6:4> of the ECCP1AS register).

When a shutdown occurs, the output pins are asynchronously placed in their shutdown states, specified by the PSSAC<1:0> and PSSBD<1:0> bits (ECCPAS<3:0>). Each pin pair (P1A/P1C and P1B/P1D) may be set to drive high, drive low or be tri-stated (not driving). The ECCPASE bit (ECCP1AS<7>) is also set to hold the Enhanced PWM outputs in their shutdown states.

The ECCPASE bit is set by hardware when a shutdown event occurs. If automatic restarts are not enabled, the ECCPASE bit is cleared by firmware when the cause of the shutdown clears. If automatic restarts are enabled, the ECCPASE bit is automatically cleared when the cause of the auto-shutdown has cleared.

If the ECCPASE bit is set when a PWM period begins, the PWM outputs remain in their shutdown state for that entire PWM period. When the ECCPASE bit is cleared, the PWM outputs will return to normal operation at the beginning of the next PWM period.

**Note:** Writing to the ECCPASE bit is disabled while a shutdown condition is active.

| R/W-0            | R/W-0                                                                                              |                                                  |                                                                  |                                                       |                     |                     |                     |

|------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------|---------------------|---------------------|---------------------|

|                  | N/VV-0                                                                                             | R/W-0                                            | R/W-0                                                            | R/W-0                                                 | R/W-0               | R/W-0               | R/W-0               |

| PRSEN            | PDC6 <sup>(1)</sup>                                                                                | PDC5 <sup>(1)</sup>                              | PDC4 <sup>(1)</sup>                                              | PDC3 <sup>(1)</sup>                                   | PDC2 <sup>(1)</sup> | PDC1 <sup>(1)</sup> | PDC0 <sup>(1)</sup> |

| bit 7            |                                                                                                    |                                                  |                                                                  |                                                       |                     |                     | bit 0               |

|                  |                                                                                                    |                                                  |                                                                  |                                                       |                     |                     |                     |

| Legend:          |                                                                                                    |                                                  |                                                                  |                                                       |                     |                     |                     |

| R = Readable     | e bit                                                                                              | W = Writable I                                   | oit                                                              | U = Unimplem                                          | ented bit, read     | as '0'              |                     |

| n = Value at     | alue at POR '1' = Bit is set                                                                       |                                                  |                                                                  | '0' = Bit is clea                                     | ared                | x = Bit is unkn     | iown                |

| bit 7<br>bit 6-0 | 1 = Upon aut<br>the PWM<br>0 = Upon aut<br><b>PDC&lt;6:0&gt;:</b> P <sup>1</sup><br>Delay time, in | restarts autom<br>o-shutdown, E0<br>WM Delay Cou | e ECCPASE b<br>atically<br>CCPASE must<br>nt bits <sup>(1)</sup> | it clears automa<br>be cleared in s<br>cycles, betwee | oftware to resta    | art the PWM         |                     |

|                  |                                                                                                    |                                                  |                                                                  |                                                       |                     |                     |                     |

# REGISTER 15-2: ECCP1DEL: PWM DEAD-BAND DELAY REGISTER

Note 1: Reserved on 28-pin devices; maintain these bits clear.

### 15.4.9 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the ECCP module for PWM operation:

- 1. Configure the PWM pins, P1A and P1B (and P1C and P1D, if used), as inputs by setting the corresponding TRIS bits.

- 2. Set the PWM period by loading the PR2 register.

- 3. If auto-shutdown is required:

- Disable auto-shutdown (ECCPASE = 0)

- Configure source (FLT0, Comparator 1 or Comparator 2)

- Wait for non-shutdown condition

- Configure the ECCP module for the desired PWM mode and configuration by loading the CCP1CON register with the appropriate values:

- Select one of the available output configurations and direction with the P1M<1:0> bits.

- Select the polarities of the PWM output signals with the CCP1M<3:0> bits.

- 5. Set the PWM duty cycle by loading the CCPR1L register and CCP1CON<5:4> bits.

- 6. For Half-Bridge Output mode, set the deadband delay by loading ECCP1DEL<6:0> with the appropriate value.

- 7. If auto-shutdown operation is required, load the ECCP1AS register:

- Select the auto-shutdown sources using the ECCPAS<2:0> bits.

- Select the shutdown states of the PWM output pins using the PSSAC<1:0> and PSSBD<1:0> bits.

- Set the ECCPASE bit (ECCP1AS<7>).

- Configure the comparators using the CMCON register.

- Configure the comparator inputs as analog inputs.

- 8. If auto-restart operation is required, set the PRSEN bit (ECCP1DEL<7>).

- 9. Configure and start TMR2:

- Clear the TMR2 interrupt flag bit by clearing the TMR2IF bit (PIR1<1>).

- Set the TMR2 prescale value by loading the T2CKPS bits (T2CON<1:0>).

- Enable Timer2 by setting the TMR2ON bit (T2CON<2>).

- 10. Enable PWM outputs after a new PWM cycle has started:

- Wait until TMRx overflows (TMRxIF bit is set).

- Enable the CCP1/P1A, P1B, P1C and/or P1D pin outputs by clearing the respective TRIS bits.

- Clear the ECCPASE bit (ECCP1AS<7>).

# 15.4.10 OPERATION IN POWER-MANAGED MODES

In Sleep mode, all clock sources are disabled. Timer2 will not increment and the state of the module will not change. If the CCP1 pin is driving a value, it will continue to drive that value. When the device wakes up, it will continue from this state. If Two-Speed Start-ups are enabled, the initial start-up frequency from INTOSC and the postscaler may not be stable immediately.

In PRI\_IDLE mode, the primary clock will continue to clock the ECCP module without change. In all other power-managed modes, the selected power-managed mode clock will clock Timer2. Other power-managed mode clocks will most likely be different than the primary clock frequency.

### 15.4.10.1 Operation with Fail-Safe Clock Monitor

If the Fail-Safe Clock Monitor is enabled, a clock failure will force the device into the power-managed RC\_RUN mode and the OSCFIF bit (PIR2<7>) will be set. The ECCP will then be clocked from the internal oscillator clock source, which may have a different clock frequency than the primary clock.

See the previous section for additional details.

### 15.4.11 EFFECTS OF A RESET

Both Power-on Reset and subsequent Resets will force all ports to Input mode and the CCP registers to their Reset states.

This forces the Enhanced CCP module to reset to a state compatible with the standard CCP module.

# 17.2 EUSART Asynchronous Mode

The Asynchronous mode of operation is selected by clearing the SYNC bit (TXSTA<4>). In this mode, the EUSART uses standard Non-Return-to-Zero (NRZ) format (one Start bit, eight or nine data bits and one Stop bit). The most common data format is 8 bits. An on-chip, dedicated 8-bit/16-bit Baud Rate Generator can be used to derive standard baud rate frequencies from the oscillator.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent but use the same data format and baud rate. The Baud Rate Generator produces a clock, either x16 or x64 of the bit shift rate depending on the BRGH and BRG16 bits (TXSTA<2> and BAUDCON<3>). Parity is not supported by the hardware but can be implemented in software and stored as the 9th data bit.

When operating in Asynchronous mode, the EUSART module consists of the following important elements:

- Baud Rate Generator

- Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

- Auto-Wake-up on Sync Break Character

- 12-Bit Break Character Transmit

- Auto-Baud Rate Detection

### 17.2.1 EUSART ASYNCHRONOUS TRANSMITTER

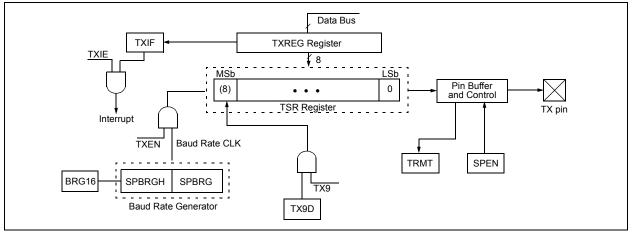

The EUSART transmitter block diagram is shown in Figure 17-3. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The Shift register obtains its data from the Read/Write Transmit Buffer register, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the Stop bit has been transmitted from the previous load. As soon as the Stop bit is transmitted, the TSR is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCY), the TXREG register is empty and the TXIF flag bit (PIR1<4>) is set. This interrupt can be enabled or disabled by setting or clearing the interrupt enable bit, TXIE (PIE1<4>). TXIF will be set regardless of the state of TXIE; it cannot be cleared in software. TXIF is also not cleared immediately upon loading TXREG, but becomes valid in the second instruction cycle following the load instruction. Polling TXIF immediately following a load of TXREG will return invalid results.

While TXIF indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. TRMT is a read-only bit which is set when the TSR register is empty. No interrupt logic is tied to this bit so the user has to poll this bit in order to determine if the TSR register is empty.

**Note 1:** The TSR register is not mapped in data memory so it is not available to the user.

2: Flag bit TXIF is set when enable bit TXEN is set.

To set up an Asynchronous Transmission:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing bit, SYNC, and setting bit, SPEN.

- 3. If interrupts are desired, set enable bit, TXIE.

- 4. If 9-bit transmission is desired, set transmit bit, TX9. Can be used as address/data bit.

- 5. Enable the transmission by setting bit, TXEN, which will also set bit, TXIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Load data to the TXREG register (starts transmission).

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

### FIGURE 17-3: EUSART TRANSMIT BLOCK DIAGRAM

# 20.0 COMPARATOR VOLTAGE REFERENCE MODULE

The comparator voltage reference is a 16-tap resistor ladder network that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it may also be used independently of them.

A block diagram of the module is shown in Figure 20-1. The resistor ladder is segmented to provide two ranges of CVREF values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/VSS or an external voltage reference.

### 20.1 Configuring the Comparator Voltage Reference

-----

The voltage reference module is controlled through the CVRCON register (Register 20-1). The comparator voltage reference provides two ranges of output voltage, each with 16 distinct levels. The range to be

used is selected by the CVRR bit (CVRCON<5>). The primary difference between the ranges is the size of the steps selected by the CVREF Selection bits (CVR<3:0>), with one range offering finer resolution. The equations used to calculate the output of the comparator voltage reference are as follows:

<u>If CVRR = 1:</u> CVREF = ((CVR<3:0>)/24) x CVRSRC <u>If CVRR = 0:</u> CVREF = (CVRSRC x 1/4) + (((CVR<3:0>)/32) x CVRSRC)

The comparator reference supply voltage can come from either VDD and VSS, or the external VREF+ and VREF- that are multiplexed with RA2 and RA3. The voltage source is selected by the CVRSS bit (CVRCON<4>).

The settling time of the comparator voltage reference must be considered when changing the CVREF output (see Table 24-3 in **Section 24.0 "Electrical Characteristics"**).

### **REGISTER 20-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER**

| R/W-0 | R/W-0                | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|----------------------|-------|-------|-------|-------|-------|-------|

| CVREN | CVROE <sup>(1)</sup> | CVRR  | CVRSS | CVR3  | CVR2  | CVR1  | CVR0  |

| bit 7 |                      |       |       |       |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 7   | CVREN: Comparator Voltage Reference Enable bit                                                                                                                                                                                     |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = CVREF circuit powered on                                                                                                                                                                                                       |

|         | 0 = CVREF circuit powered down                                                                                                                                                                                                     |

| bit 6   | CVROE: Comparator VREF Output Enable bit <sup>(1)</sup>                                                                                                                                                                            |

|         | <ul> <li>1 = CVREF voltage level is also output on the RA2/AN2/VREF-/CVREF pin</li> <li>0 = CVREF voltage is disconnected from the RA2/AN2/VREF-/CVREF pin</li> </ul>                                                              |

| bit 5   | CVRR: Comparator VREF Range Selection bit                                                                                                                                                                                          |

|         | <ul> <li>1 = 0 to 0.667 CVRsRc, with CVRsRc/24 step size (low range)</li> <li>0 = 0.25 CVRsRc to 0.75 CVRsRc, with CVRsRc/32 step size (high range)</li> </ul>                                                                     |

| bit 4   | CVRSS: Comparator VREF Source Selection bit                                                                                                                                                                                        |

|         | <ul> <li>1 = Comparator reference source, CVRSRC = (VREF+) – (VREF-)</li> <li>0 = Comparator reference source, CVRSRC = VDD – VSS</li> </ul>                                                                                       |

| bit 3-0 | <b>CVR&lt;3:0&gt;:</b> Comparator VREF Value Selection bits $(0 \le (CVR<3:0>) \le 15)$<br><u>When CVRR = 1:</u><br>CVREF = ((CVR<3:0>)/24) • (CVRSRC)<br><u>When CVRR = 0:</u><br>CVREF = (CVRSRC/4) + ((CVR<3:0>)/32) • (CVRSRC) |

|         |                                                                                                                                                                                                                                    |

Note 1: CVROE overrides the TRISA<2> bit setting.

# REGISTER 21-3: CONFIG2L: CONFIGURATION REGISTER 2 LOW (BYTE ADDRESS 300002h)

|                |                                                               |                                                                                                              |                                            |                                           | •                |                   | ,      |

|----------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------------------------------------------|------------------|-------------------|--------|

| R/WO-1         | R/WO-1                                                        | U-0                                                                                                          | U-0                                        | U-0                                       | R/WO-1           | R/WO-1            | R/WO-1 |

| IESO           | FCMEN                                                         |                                                                                                              |                                            |                                           | FOSC2            | FOSC1             | FOSC0  |

| bit 7          |                                                               |                                                                                                              |                                            |                                           |                  |                   | bit 0  |

|                |                                                               |                                                                                                              |                                            |                                           |                  |                   |        |

| Legend:        |                                                               |                                                                                                              |                                            |                                           |                  |                   |        |

| R = Readabl    | e bit                                                         | WO = Write C                                                                                                 | nce bit                                    | U = Unimplem                              | nented bit, read | <b>l as</b> '0'   |        |

| -n = Value w   | hen device is ur                                              | nprogrammed                                                                                                  |                                            | '1' = Bit is set                          |                  | '0' = Bit is clea | ared   |

| bit 7<br>bit 6 | 1 = Two-Spee<br>0 = Two-Spee<br>FCMEN: Fail-<br>1 = Fail-Safe | ed Start-up (<br>ed Start-up enal<br>ed Start-up disa<br>Safe Clock Mo<br>Clock Monitor (<br>Clock Monitor ( | bled<br>bled<br>nitor Enable bi<br>enabled | al Oscillator Sw<br>it                    | nichover) Cont   | ioi dit           |        |

| bit 5-3        | Unimplemen                                                    | ted: Read as '                                                                                               | )'                                         |                                           |                  |                   |        |

| bit 2          | FOSC2: Defa                                                   | ult/Reset Syste                                                                                              | m Clock Selec                              | ct bit                                    |                  |                   |        |

|                |                                                               |                                                                                                              |                                            | em clock is enal<br>OSCCON<1:0>           |                  | CCON<1:0> =       | 00     |

| bit 1-0        | FOSC<1:0>:                                                    | Oscillator Sele                                                                                              | ction bits                                 |                                           |                  |                   |        |

|                | 10 = EC osci                                                  | illator, CLKO fu<br>illator, PLL ena                                                                         | nction on OSC                              | r software contr<br>2<br>r software contr | ,                | tion on OSC2      |        |

00 = HS oscillator

# 24.1 DC Characteristics: Supply Voltage PIC18F24J10/25J10/44J10/45J10 (Industrial) PIC18LF24J10/25J10/44J10/45J10 (Industrial)

| PIC18F45J10 Family<br>(Industrial) |         |                                                                     | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |     |      |       |                                                                                                      |

|------------------------------------|---------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|------|-------|------------------------------------------------------------------------------------------------------|

| Param<br>No.                       | Symbol  | Characteristic                                                      | Min                                                                                                                                | Тур | Max  | Units | Conditions                                                                                           |

| D001                               | Vdd     | Supply Voltage                                                      | VDDCORE                                                                                                                            | _   | 3.6  | V     | PIC18LF4XJ10, PIC18LF2XJ10                                                                           |

| D001                               | Vdd     | Supply Voltage                                                      | 2.7 <sup>(1)</sup>                                                                                                                 | —   | 3.6  | V     | PIC18F4X/2XJ10                                                                                       |

| D001B                              | VDDCORE | External Supply for<br>Microcontroller Core                         | 2.0                                                                                                                                | —   | 2.7  | V     | Valid only in parts designated "LF".<br>See Section 21.3 "On-Chip<br>Voltage Regulator" for details. |

| D002                               | Vdr     | RAM Data Retention<br>Voltage <sup>(1)</sup>                        | 1.5                                                                                                                                | —   |      | V     |                                                                                                      |

| D003                               | Vpor    | VDD Start Voltage<br>to ensure internal<br>Power-on Reset signal    | _                                                                                                                                  | —   | 0.15 | V     | SeeSection 5.3 "Power-on<br>Reset (POR)" for details                                                 |

| D004                               | SVDD    | <b>VDD Rise Rate</b><br>to ensure internal<br>Power-on Reset signal | 0.05                                                                                                                               | —   |      | V/ms  | See Section 5.3 "Power-on<br>Reset (POR)" for details                                                |

| D005                               | VBOR    | Brown-out Reset (BOR)<br>Voltage                                    | 2.35                                                                                                                               | 2.5 | 2.7  | V     |                                                                                                      |

Note 1: This is the limit to which VDD can be lowered in Sleep mode, or during a device Reset, without losing RAM data.

NOTES: