Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 21                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 10x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf25j10-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

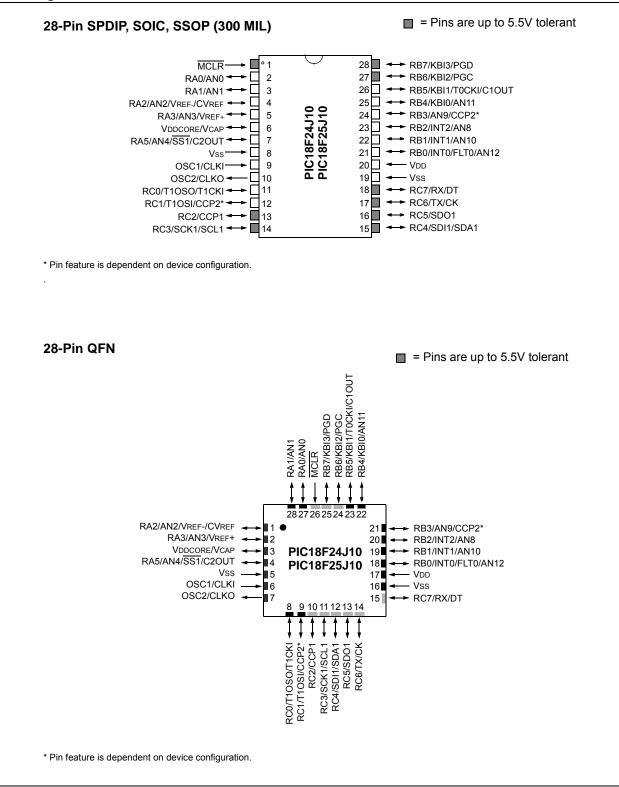

#### **Pin Diagrams**

|                                                       | Pin Number<br>SPDIP,<br>SOIC,<br>SSOP |       |                   |                    | Description                                                                                                                              |  |  |  |  |

|-------------------------------------------------------|---------------------------------------|-------|-------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin Name                                              |                                       |       | Pin<br>Type       | Buffer<br>Type     |                                                                                                                                          |  |  |  |  |

|                                                       |                                       |       |                   |                    | PORTC is a bidirectional I/O port.                                                                                                       |  |  |  |  |

| RC0/T1OSO/T1CKI<br>RC0<br>T1OSO<br>T1CKI              | 11                                    | 8     | I/O<br>O<br>I     | ST<br>—<br>ST      | Digital I/O.<br>Timer1 oscillator output.<br>Timer1 external clock input.                                                                |  |  |  |  |

| RC1/T1OSI/CCP2<br>RC1<br>T1OSI<br>CCP2 <sup>(2)</sup> | 12                                    | 9     | I/O<br>I<br>I/O   | ST<br>Analog<br>ST | Digital I/O.<br>Timer1 oscillator input.<br>Capture 2 input/Compare 2 output/PWM2 output.                                                |  |  |  |  |

| RC2/CCP1<br>RC2<br>CCP1                               | 13                                    | 10    | I/O<br>I/O        | ST<br>ST           | Digital I/O.<br>Capture 1 input/Compare 1 output/PWM1 output.                                                                            |  |  |  |  |

| RC3/SCK1/SCL1<br>RC3<br>SCK1<br>SCL1                  | 14                                    | 11    | I/O<br>I/O<br>I/O | ST<br>ST<br>ST     | Digital I/O.<br>Synchronous serial clock input/output for SPI mode.<br>Synchronous serial clock input/output for I <sup>2</sup> C™ mode. |  |  |  |  |

| RC4/SDI1/SDA1<br>RC4<br>SDI1<br>SDA1                  | 15                                    | 12    | I/O<br>I<br>I/O   | ST<br>ST<br>ST     | Digital I/O.<br>SPI data in.<br>I <sup>2</sup> C data I/O.                                                                               |  |  |  |  |

| RC5/SDO1<br>RC5<br>SDO1                               | 16                                    | 13    | I/O<br>O          | ST<br>—            | Digital I/O.<br>SPI data out.                                                                                                            |  |  |  |  |

| RC6/TX/CK<br>RC6<br>TX<br>CK                          | 17                                    | 14    | I/O<br>O<br>I/O   | ST<br>—<br>ST      | Digital I/O.<br>EUSART asynchronous transmit.<br>EUSART synchronous clock (see related RX/DT).                                           |  |  |  |  |

| RC7/RX/DT<br>RC7<br>RX<br>DT                          | 18                                    | 15    | I/O<br>I<br>I/O   | ST<br>ST<br>ST     | Digital I/O.<br>EUSART asynchronous receive.<br>EUSART synchronous data (see related TX/CK).                                             |  |  |  |  |

| Vss                                                   | 8, 19                                 | 5, 16 | Р                 |                    | Ground reference for logic and I/O pins.                                                                                                 |  |  |  |  |

| Vdd                                                   | 20                                    | 17    | Р                 |                    | Positive supply for logic and I/O pins.                                                                                                  |  |  |  |  |

| VDDCORE/VCAP<br>VDDCORE                               | 6                                     | 3     | P<br>P            | _                  | Positive supply for logic and I/O pins.<br>Ground reference for logic and I/O pins.                                                      |  |  |  |  |

| TABLE 1-2: | PIC18F24J10/25J10 PINOUT I/O DESCRIPTIONS (CONTINUED) |

|------------|-------------------------------------------------------|

|            |                                                       |

Note 1: Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

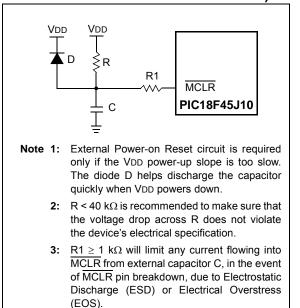

## 5.2 Master Clear (MCLR)

The  $\overline{\text{MCLR}}$  pin provides a method for triggering a hard external Reset of the device. A Reset is generated by holding the pin low. PIC18 extended microcontroller devices have a noise filter in the  $\overline{\text{MCLR}}$  Reset path which detects and ignores small pulses.

The  $\overline{\text{MCLR}}$  pin is not driven low by any internal Resets, including the WDT.

## 5.3 Power-on Reset (POR)

A Power-on Reset condition is generated on-chip whenever VDD rises above a certain threshold. This allows the device to start in the initialized state when VDD is adequate for operation.

To take advantage of the POR circuitry, tie the  $\overline{\text{MCLR}}$  pin through a resistor (1 k $\Omega$  to 10 k $\Omega$ ) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset delay. A minimum rise rate for VDD is specified (parameter D004). For a slow rise time, see Figure 5-2.

When the device starts normal operation (i.e., exits the Reset condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

Power-on Reset events are captured by the  $\overrightarrow{POR}$  bit (RCON<1>). The state of the bit is set to '0' whenever a Power-on Reset occurs; it does not change for any other Reset event.  $\overrightarrow{POR}$  is not reset to '1' by any hardware event. To capture multiple events, the user manually resets the bit to '1' in software following any Power-on Reset.

### 5.4 Brown-out Reset (BOR) (PIC18F2XJ10/4XJ10 Devices Only)

The PIC18F45J10 family of devices incorporates a simple BOR function when the internal regulator is enabled (ENVREG pin is tied to VDD). Any drop of VDD below VBOR (parameter D005) for greater than time TBOR (parameter 35) will reset the device. A Reset may or may not occur if VDD falls below VBOR for less than TBOR. The chip will remain in Brown-out Reset until VDD rises above VBOR.

Once a BOR has occurred, the Power-up Timer will keep the chip in Reset for TPWRT (parameter 33). If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above VBOR, the Power-up Timer will execute the additional time delay.

#### FIGURE 5-2:

#### EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

## 5.4.1 DETECTING BOR

The BOR bit always resets to '0' on any Brown-out Reset or Power-on Reset event. This makes it difficult to determine if a Brown-out Reset event has occurred just by reading the state of BOR alone. A more reliable method is to simultaneously check the state of both POR and BOR. This assumes that the POR bit is reset to '1' in software immediately after any Power-on Reset event. If BOR is '0' while POR is '1', it can be reliably assumed that a Brown-out Reset event has occurred.

In devices designated with an "LF" part number (such as PIC18LF25J10), Brown-out Reset functionality is disabled. In this case, the BOR bit cannot be used to determine a Brown-out Reset event. The BOR bit is still cleared by a Power-on Reset event.

| TABLE 5-2: | INITIALIZATI       | ED)         |                                                    |           |           |                                                                                |                                 |  |  |

|------------|--------------------|-------------|----------------------------------------------------|-----------|-----------|--------------------------------------------------------------------------------|---------------------------------|--|--|

| Register   | Applicable Devices |             | Applicable Devices Power-on Rese<br>Brown-out Rese |           |           | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets,<br>CM Resets | Wake-up via WDT<br>or Interrupt |  |  |

| TRISE      | PIC18F2XJ10 P      | IC18F4XJ10  | 0000 -111                                          | 1111 -111 | uuuu -uuu |                                                                                |                                 |  |  |

| TRISD      | PIC18F2XJ10 P      | IC18F4XJ10  | 1111 1111                                          | 1111 1111 | uuuu uuuu |                                                                                |                                 |  |  |

| TRISC      | PIC18F2XJ10 P      | PIC18F4XJ10 | 1111 1111                                          | 1111 1111 | սսսս սսսս |                                                                                |                                 |  |  |

| TRISB      | PIC18F2XJ10 P      | PIC18F4XJ10 | 1111 1111                                          | 1111 1111 | սսսս սսսս |                                                                                |                                 |  |  |

| TRISA      | PIC18F2XJ10 P      | PIC18F4XJ10 | 1- 1111                                            | 1- 1111   | u- uuuu   |                                                                                |                                 |  |  |

| SSP2BUF    | PIC18F2XJ10 P      | PIC18F4XJ10 | xxxx xxxx                                          | սսսս սսսս | uuuu uuuu |                                                                                |                                 |  |  |

| LATE       | PIC18F2XJ10 P      | PIC18F4XJ10 | xxx                                                | uuu       | uuu       |                                                                                |                                 |  |  |

| LATD       | PIC18F2XJ10 P      | PIC18F4XJ10 | XXXX XXXX                                          | uuuu uuuu | uuuu uuuu |                                                                                |                                 |  |  |

| LATC       | PIC18F2XJ10 P      | PIC18F4XJ10 | XXXX XXXX                                          | uuuu uuuu | uuuu uuuu |                                                                                |                                 |  |  |

| LATB       | PIC18F2XJ10 P      | PIC18F4XJ10 | xxxx xxxx                                          | սսսս սսսս | uuuu uuuu |                                                                                |                                 |  |  |

| LATA       | PIC18F2XJ10 P      | PIC18F4XJ10 | xx xxxx                                            | uu uuuu   | uu uuuu   |                                                                                |                                 |  |  |

| SSP2ADD    | PIC18F2XJ10 P      | PIC18F4XJ10 | 0000 0000                                          | 0000 0000 | uuuu uuuu |                                                                                |                                 |  |  |

| SSP2STAT   | PIC18F2XJ10 P      | PIC18F4XJ10 | 0000 0000                                          | 0000 0000 | սսսս սսսս |                                                                                |                                 |  |  |

| SSP2CON1   | PIC18F2XJ10 P      | PIC18F4XJ10 | 0000 0000                                          | 0000 0000 | uuuu uuuu |                                                                                |                                 |  |  |

| SSP2CON2   | PIC18F2XJ10 P      | PIC18F4XJ10 | 0000 0000                                          | 0000 0000 | սսսս սսսս |                                                                                |                                 |  |  |

| PORTE      | PIC18F2XJ10 P      | PIC18F4XJ10 | xxx                                                | uuu       | uuu       |                                                                                |                                 |  |  |

| PORTD      | PIC18F2XJ10 P      | PIC18F4XJ10 | xxxx xxxx                                          | սսսս սսսս | սսսս սսսս |                                                                                |                                 |  |  |

| PORTC      | PIC18F2XJ10 P      | PIC18F4XJ10 | xxxx xxxx                                          | սսսս սսսս | սսսս սսսս |                                                                                |                                 |  |  |

| PORTB      | PIC18F2XJ10 P      | PIC18F4XJ10 | xxxx xxxx                                          | սսսս սսսս | սսսս սսսս |                                                                                |                                 |  |  |

| PORTA      | PIC18F2XJ10 P      | PIC18F4XJ10 | 0- 0000                                            | 0- 0000   | u- uuuu   |                                                                                |                                 |  |  |

## TABLE 5-2: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

3: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

4: See Table 5-1 for Reset value for specific condition.

### 6.1.4.2 Return Stack Pointer (STKPTR)

The STKPTR register (Register 6-1) contains the Stack Pointer value, the STKFUL (Stack Overflow) status bit and the STKUNF (Stack Underflow) status bits. The value of the Stack Pointer can be 0 through 31. The Stack Pointer increments before values are pushed onto the stack and decrements after values are popped off the stack. On Reset, the Stack Pointer value will be zero. The user may read and write the Stack Pointer value. This feature can be used by a Real-Time Operating System (RTOS) for return stack maintenance.

After the PC is pushed onto the stack 31 times (without popping any values off the stack), the STKFUL bit is set. The STKFUL bit is cleared by software or by a POR.

The action that takes place when the stack becomes full depends on the state of the STVREN (Stack Overflow Reset Enable) Configuration bit. (Refer to **Section 21.1 "Configuration Bits**" for a description of the device Configuration bits.) If STVREN is set (default), the 31st push will push the (PC + 2) value onto the stack, set the STKFUL bit and reset the device. The STKFUL bit will remain set and the Stack Pointer will be set to zero.

If STVREN is cleared, the STKFUL bit will be set on the 31st push and the Stack Pointer will increment to 31. Any additional pushes will not overwrite the 31st push and the STKPTR will remain at 31.

When the stack has been popped enough times to unload the stack, the next pop will return a value of zero to the PC and sets the STKUNF bit, while the Stack Pointer remains at zero. The STKUNF bit will remain set until cleared by software or until a POR occurs.

| Note: | Returning a value of zero to the PC on an<br>underflow has the effect of vectoring the<br>program to the Reset vector, where the<br>stack conditions can be verified and<br>appropriate actions can be taken. This is |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | not the same as a Reset, as the contents of the SFRs are not affected.                                                                                                                                                |

#### 6.1.4.3 PUSH and POP Instructions

Since the Top-of-Stack is readable and writable, the ability to push values onto the stack and pull values off the stack without disturbing normal program execution is a desirable feature. The PIC18 instruction set includes two instructions, PUSH and POP, that permit the TOS to be manipulated under software control. TOSU, TOSH and TOSL can be modified to place data or a return address on the stack.

The PUSH instruction places the current PC value onto the stack. This increments the Stack Pointer and loads the current PC value onto the stack.

The POP instruction discards the current TOS by decrementing the Stack Pointer. The previous value pushed onto the stack then becomes the TOS value.

| R/C-0                                            | R/C-0                 | U-0              | R/W-0 | R/W-0             | R/W-0            | R/W-0              | R/W-0 |  |  |  |

|--------------------------------------------------|-----------------------|------------------|-------|-------------------|------------------|--------------------|-------|--|--|--|

| STKFUL <sup>(1)</sup>                            | STKUNF <sup>(1)</sup> | —                | SP4   | SP3               | SP2              | SP1                | SP0   |  |  |  |

| bit 7                                            |                       |                  |       |                   |                  |                    | bit 0 |  |  |  |

|                                                  |                       |                  |       |                   |                  |                    |       |  |  |  |

| Legend:                                          |                       | C = Clearable    | bit   |                   |                  |                    |       |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemen |                       |                  |       |                   | nented bit, read | l as '0'           |       |  |  |  |

| -n = Value at F                                  | POR                   | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unknown |       |  |  |  |

#### REGISTER 6-1: STKPTR: STACK POINTER REGISTER

| bit 7   | STKFUL: Stack Full Flag bit <sup>(1)</sup>      |

|---------|-------------------------------------------------|

|         | 1 = Stack became full or overflowed             |

|         | 0 = Stack has not become full or overflowed     |

| bit 6   | STKUNF: Stack Underflow Flag bit <sup>(1)</sup> |

|         | 1 = Stack underflow occurred                    |

|         | 0 = Stack underflow did not occur               |

| bit 5   | Unimplemented: Read as '0'                      |

| bit 4-0 | SP<4:0>: Stack Pointer Location bits            |

**Note 1:** Bit 7 and bit 6 are cleared by user software or by a POR.

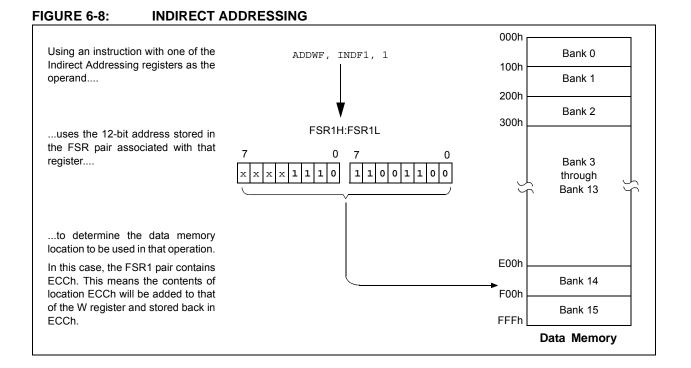

#### 6.4.3.1 FSR Registers and the INDF Operand

At the core of Indirect Addressing are three sets of registers: FSR0, FSR1 and FSR2. Each represents a pair of 8-bit registers, FSRnH and FSRnL. The four upper bits of the FSRnH register are not used, so each FSR pair holds a 12-bit value. This represents a value that can address the entire range of the data memory in a linear fashion. The FSR register pairs, then, serve as pointers to data memory locations.

Indirect Addressing is accomplished with a set of Indirect File Operands, INDF0 through INDF2. These can be thought of as "virtual" registers; they are mapped in the SFR space but are not physically implemented. Reading or writing to a particular INDF register actually accesses its corresponding FSR register pair. A read from INDF1, for example, reads the data at the address indicated by FSR1H:FSR1L. Instructions that use the INDF registers as operands actually use the contents of their corresponding FSR as a pointer to the instruction's target. The INDF operand is just a convenient way of using the pointer.

Because Indirect Addressing uses a full 12-bit address, data RAM banking is not necessary. Thus, the current contents of the BSR and the Access RAM bit have no effect on determining the target address.

#### 6.4.3.2 FSR Registers and POSTINC, POSTDEC, PREINC and PLUSW

In addition to the INDF operand, each FSR register pair also has four additional indirect operands. Like INDF, these are "virtual" registers that cannot be indirectly read or written to. Accessing these registers actually accesses the associated FSR register pair, but also performs a specific action on it stored value. They are:

- POSTDEC: accesses the FSR value, then automatically decrements it by 1 afterwards

- POSTINC: accesses the FSR value, then automatically increments it by 1 afterwards

- PREINC: increments the FSR value by 1, then uses it in the operation

- PLUSW: adds the signed value of the W register (range of -127 to 128) to that of the FSR and uses the new value in the operation.

In this context, accessing an INDF register uses the value in the FSR registers without changing them. Similarly, accessing a PLUSW register gives the FSR value offset by that in the W register; neither value is actually changed in the operation. Accessing the other virtual registers changes the value of the FSR registers.

Operations on the FSRs with POSTDEC, POSTINC and PREINC affect the entire register pair; that is, rollovers of the FSRnL register, from FFh to 00h, carry over to the FSRnH register. On the other hand, results of these operations do not change the value of any flags in the STATUS register (e.g., Z, N, OV, etc.).

## © 2009 Microchip Technology Inc.

### 9.3 PIE Registers

The PIE registers contain the individual enable bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are three Peripheral Interrupt Enable registers (PIE1, PIE2, PIE3). When IPEN = 0, the PEIE bit must be set to enable any of these peripheral interrupts.

#### REGISTER 9-7: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| R/W-0                | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|----------------------|-------|-------|-------|--------|--------|--------|--------|

| PSPIE <sup>(1)</sup> | ADIE  | RCIE  | TXIE  | SSP1IE | CCP1IE | TMR2IE | TMR1IE |

| bit 7                |       |       |       |        |        |        | bit 0  |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 7 | <b>PSPIE:</b> Parallel Slave Port Read/Write Interrupt Enable bit <sup>(1)</sup><br>1 = Enables the PSP read/write interrupt<br>0 = Disables the PSP read/write interrupt |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | ADIE: A/D Converter Interrupt Enable bit<br>1 = Enables the A/D interrupt                                                                                                 |

| bit 5 | 0 = Disables the A/D interrupt<br><b>RCIE:</b> EUSART Receive Interrupt Enable bit                                                                                        |

|       | <ul><li>1 = Enables the EUSART receive interrupt</li><li>0 = Disables the EUSART receive interrupt</li></ul>                                                              |

| bit 4 | <b>TXIE:</b> EUSART Transmit Interrupt Enable bit<br>1 = Enables the EUSART transmit interrupt<br>0 = Disables the EUSART transmit interrupt                              |

| bit 3 | <b>SSP1IE:</b> Master Synchronous Serial Port 1 Interrupt Enable bit<br>1 = Enables the MSSP interrupt<br>0 = Disables the MSSP interrupt                                 |

| bit 2 | <b>CCP1IE:</b> ECCP1/CCP1 Interrupt Enable bit<br>1 = Enables the ECCP1/CCP1 interrupt<br>0 = Disables the ECCP1/CCP1 interrupt                                           |

| bit 1 | <b>TMR2IE:</b> TMR2 to PR2 Match Interrupt Enable bit<br>1 = Enables the TMR2 to PR2 match interrupt<br>0 = Disables the TMR2 to PR2 match interrupt                      |

| bit 0 | <b>TMR1IE:</b> TMR1 Overflow Interrupt Enable bit<br>1 = Enables the TMR1 overflow interrupt<br>0 = Disables the TMR1 overflow interrupt                                  |

Note 1: This bit is not implemented on 28-pin devices and should be read as '0'.

#### 15.4.9 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the ECCP module for PWM operation:

- 1. Configure the PWM pins, P1A and P1B (and P1C and P1D, if used), as inputs by setting the corresponding TRIS bits.

- 2. Set the PWM period by loading the PR2 register.

- 3. If auto-shutdown is required:

- Disable auto-shutdown (ECCPASE = 0)

- Configure source (FLT0, Comparator 1 or Comparator 2)

- Wait for non-shutdown condition

- Configure the ECCP module for the desired PWM mode and configuration by loading the CCP1CON register with the appropriate values:

- Select one of the available output configurations and direction with the P1M<1:0> bits.

- Select the polarities of the PWM output signals with the CCP1M<3:0> bits.

- 5. Set the PWM duty cycle by loading the CCPR1L register and CCP1CON<5:4> bits.

- 6. For Half-Bridge Output mode, set the deadband delay by loading ECCP1DEL<6:0> with the appropriate value.

- 7. If auto-shutdown operation is required, load the ECCP1AS register:

- Select the auto-shutdown sources using the ECCPAS<2:0> bits.

- Select the shutdown states of the PWM output pins using the PSSAC<1:0> and PSSBD<1:0> bits.

- Set the ECCPASE bit (ECCP1AS<7>).

- Configure the comparators using the CMCON register.

- Configure the comparator inputs as analog inputs.

- 8. If auto-restart operation is required, set the PRSEN bit (ECCP1DEL<7>).

- 9. Configure and start TMR2:

- Clear the TMR2 interrupt flag bit by clearing the TMR2IF bit (PIR1<1>).

- Set the TMR2 prescale value by loading the T2CKPS bits (T2CON<1:0>).

- Enable Timer2 by setting the TMR2ON bit (T2CON<2>).

- 10. Enable PWM outputs after a new PWM cycle has started:

- Wait until TMRx overflows (TMRxIF bit is set).

- Enable the CCP1/P1A, P1B, P1C and/or P1D pin outputs by clearing the respective TRIS bits.

- Clear the ECCPASE bit (ECCP1AS<7>).

# 15.4.10 OPERATION IN POWER-MANAGED MODES

In Sleep mode, all clock sources are disabled. Timer2 will not increment and the state of the module will not change. If the CCP1 pin is driving a value, it will continue to drive that value. When the device wakes up, it will continue from this state. If Two-Speed Start-ups are enabled, the initial start-up frequency from INTOSC and the postscaler may not be stable immediately.

In PRI\_IDLE mode, the primary clock will continue to clock the ECCP module without change. In all other power-managed modes, the selected power-managed mode clock will clock Timer2. Other power-managed mode clocks will most likely be different than the primary clock frequency.

#### 15.4.10.1 Operation with Fail-Safe Clock Monitor

If the Fail-Safe Clock Monitor is enabled, a clock failure will force the device into the power-managed RC\_RUN mode and the OSCFIF bit (PIR2<7>) will be set. The ECCP will then be clocked from the internal oscillator clock source, which may have a different clock frequency than the primary clock.

See the previous section for additional details.

#### 15.4.11 EFFECTS OF A RESET

Both Power-on Reset and subsequent Resets will force all ports to Input mode and the CCP registers to their Reset states.

This forces the Enhanced CCP module to reset to a state compatible with the standard CCP module.

#### 16.4.7.2 Clock Arbitration

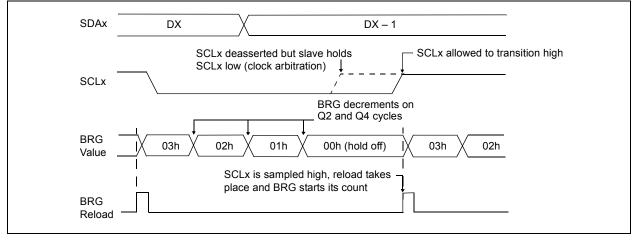

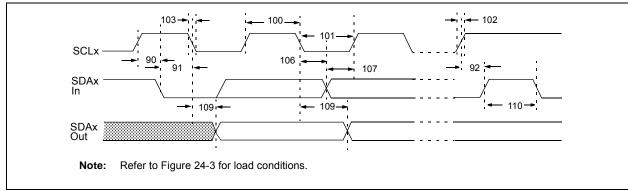

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, deasserts the SCLx pin (SCLx allowed to float high). When the SCLx pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCLx pin is actually sampled high. When the

SCLx pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<6:0> and begins counting. This ensures that the SCLx high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 16-18).

### 16.4.9 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

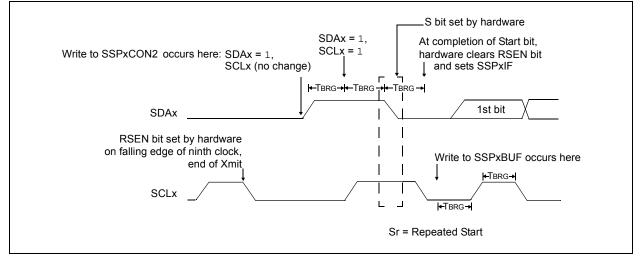

A Repeated Start condition occurs when the RSEN bit (SSPxCON2<1>) is programmed high and the I<sup>2</sup>C logic module is in the Idle state. When the RSEN bit is set, the SCLx pin is asserted low. When the SCLx pin is sampled low, the Baud Rate Generator is loaded with the contents of SSPxADD<6:0> and begins counting. The SDAx pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDAx is sampled high, the SCLx pin will be deasserted (brought high). When SCLx is sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<6:0> and begins counting. SDAx and SCLx must be sampled high for one TBRG. This action is then followed by assertion of the SDAx pin (SDAx = 0) for one TBRG while SCLx is high. Following this, the RSEN bit (SSPxCON2<1>) will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDAx pin held low. As soon as a Start condition is detected on the SDAx and SCLx pins, the S bit (SSPxSTAT<3>) will be set. The SSPxIF bit will not be set until the Baud Rate Generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDAx is sampled low when SCLx goes from low-to-high.

- SCLx goes low before SDAx is asserted low. This may indicate that another master is attempting to transmit a data '1'.

Immediately following the SSPxIF bit getting set, the user may write the SSPxBUF with the 7-bit address in 7-bit mode or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode) or eight bits of data (7-bit mode).

#### 16.4.9.1 WCOL Status Flag

If the user writes the SSPxBUF when a Repeated Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing of the lower 5 bits of SSPxCON2 is disabled until the Repeated Start condition is complete.

### FIGURE 16-20: REPEATED START CONDITION WAVEFORM

### 17.3 EUSART Synchronous Master Mode

The Synchronous Master mode is entered by setting the CSRC bit (TXSTA<7>). In this mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit SYNC (TXSTA<4>). In addition, enable bit SPEN (RCSTA<7>) is set in order to configure the TX and RX pins to CK (clock) and DT (data) lines, respectively.

The Master mode indicates that the processor transmits the master clock on the CK line. Clock polarity is selected with the SCKP bit (BAUDCON<4>). Setting SCKP sets the Idle state on CK as high, while clearing the bit sets the Idle state as Iow. This option is provided to support Microwire devices with this module.

#### 17.3.1 EUSART SYNCHRONOUS MASTER TRANSMISSION

The EUSART transmitter block diagram is shown in Figure 17-3. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The Shift register obtains its data from the Read/Write Transmit Buffer register, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available).

Once the TXREG register transfers the data to the TSR register (occurs in one Tcr), the TXREG is empty and the TXIF flag bit (PIR1<4>) is set. The interrupt can be enabled or disabled by setting or clearing the interrupt enable bit, TXIE (PIE1<4>). TXIF is set regardless of the state of enable bit TXIE; it cannot be cleared in software. It will reset only when new data is loaded into the TXREG register.

While flag bit TXIF indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. TRMT is a read-only bit which is set when the TSR is empty. No interrupt logic is tied to this bit so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory so it is not available to the user.

To set up a Synchronous Master Transmission:

- Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRG16 bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit, TXIE.

- 4. If 9-bit transmission is desired, set bit, TX9.

- 5. Enable the transmission by setting bit, TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Start transmission by loading data to the TXREG register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

|                             | Q1Q2C   | 23Q4 Q1 Q2 | Q3Q4 Q1Q2   | Q3Q4 Q1Q2   | Q3Q4 Q1 Q2   | 2 Q3 Q4     | Q3Q4 Q1C    | 2 Q3 Q4 Q1 Q2  | 2Q3Q4Q1Q    | 2Q3Q4Q1     | Q2Q3Q4Q1Q2 | Q3Q4Q1     | Q2Q3Q4      |

|-----------------------------|---------|------------|-------------|-------------|--------------|-------------|-------------|----------------|-------------|-------------|------------|------------|-------------|

| RC7/RX/DT                   |         | 1<br>      | bit 0       |             | bit :        |             | bit         | 7 <u>bit 0</u> |             |             |            | ×          | bit 7       |

| RC6/TX/CK p<br>(SCKP = 0)   |         | <br>       |             |             |              |             |             |                |             | ;           |            |            |             |

| RC6/TX/CK p<br>(SCKP = 1)   | bin     |            |             | ╶┊┎         | ٦ <u>ٺ</u> ר |             |             |                |             | - <u></u>   |            | - <u>+</u> | ,           |

| Write to<br>TXREG Reg       |         | Write W    | ord 1       | Write Wor   | d 2          |             |             | 1<br>1<br>1    | 1<br>1<br>1 | <br> <br>   | <u>}</u>   | <br> <br>  | i<br>i      |

| TXIF bit<br>(Interrupt Flag | g)      |            |             |             | <u>_</u> ن   |             |             |                |             |             |            |            |             |

| TRMT bit                    |         | ٦ <u>¦</u> | 1<br>1<br>1 | 1<br>1<br>1 | 1<br>1<br>1  |             | 1<br>1<br>1 | 1<br>1<br>1    | <br>        | 1<br>1<br>1 |            | <u>+</u> [ | 1<br>1<br>1 |

| TXEN bit                    | '1'     | <br> <br>  | 1<br>1<br>1 | <br> <br>   |              |             |             | ,<br>,<br>,    |             |             | {          |            | '1'         |

| Note: Syne                  | c Maste | er mode, S | PBRG = 0,   | continuous  | s transmis   | sion of two | 3-bit words |                |             |             |            |            |             |

#### FIGURE 17-11: SYNCHRONOUS TRANSMISSION

#### TABLE 21-1: CONFIGURATION BITS AND DEVICE IDs

| File Name |          | Bit 7 | Bit 6 | Bit 5  | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Default/<br>Unprogrammed<br>Value <sup>(1)</sup> |

|-----------|----------|-------|-------|--------|-------|--------|--------|--------|--------|--------------------------------------------------|

| 300000h   | CONFIG1L | DEBUG | XINST | STVREN |       |        | _      | _      | WDTEN  | 1111                                             |

| 300001h   | CONFIG1H | (2)   | _(2)  | _(2)   | (2)   | _(3)   | CP0    |        | _      | 1111 01                                          |

| 300002h   | CONFIG2L | IESO  | FCMEN | _      | _     | _      | FOSC2  | FOSC1  | FOSC0  | 11111                                            |

| 300003h   | CONFIG2H | (2)   | (2)   | (2)    | (2)   | WDTPS3 | WDTPS2 | WDTPS1 | WDTPS0 | 1111 1111                                        |

| 300004h   | CONFIG3L | _     | —     | _      | _     | _      | —      | _      | —      |                                                  |

| 300005h   | CONFIG3H | (2)   | _(2)  | _(2)   | (2)   | _      | —      | _      | CCP2MX | 11111                                            |

| 3FFFFEh   | DEVID1   | DEV2  | DEV1  | DEV0   | REV4  | REV3   | REV2   | REV1   | REV0   | xxxx xxxx <sup>(4)</sup>                         |

| 3FFFFFh   | DEVID2   | DEV10 | DEV9  | DEV8   | DEV7  | DEV6   | DEV5   | DEV4   | DEV3   | 0001 110x <sup>(4)</sup>                         |

$\label{eq:logend: Legend: Legend: Legend: Legend: u = unchanged, - = unimplemented. Shaded cells are unimplemented, read as '0'.$

**Note 1:** Values reflect the unprogrammed state as received from the factory and following Power-on Resets. In all other Reset states, the configuration bytes maintain their previously programmed states.

2: The value of these bits in program memory should always be '1'. This ensures that the location is executed as a NOP if it is accidentally executed.

**3:** This bit should always be maintained as '0'.

4: See Register 21-7 and Register 21-8 for DEVID values. These registers are read-only and cannot be programmed by the user.

| BNOV                                                                                                                                                     |                        | Branch if                                                                                                                                                                                                                                                                                    | Not Overflo                                                                 | w                                  | BNZ                                         | :                      | Branch if Not Zero                                                                                                                                                                                                                                                           |                                                       |                                                         |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------|---------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------|--|

| Synta                                                                                                                                                    | ax:                    | BNOV n                                                                                                                                                                                                                                                                                       |                                                                             |                                    | Synta                                       | ax:                    | BNZ n                                                                                                                                                                                                                                                                        | BNZ n                                                 |                                                         |  |

| Operands:                                                                                                                                                |                        | -128 ≤ n ≤ 1                                                                                                                                                                                                                                                                                 | 127                                                                         |                                    | Oper                                        | ands:                  | -128 ≤ n ≤ ′                                                                                                                                                                                                                                                                 | 127                                                   |                                                         |  |

| Oper                                                                                                                                                     | ation:                 | if Overflow<br>(PC) + 2 + 2                                                                                                                                                                                                                                                                  |                                                                             |                                    | Oper                                        | ation:                 |                                                                                                                                                                                                                                                                              | if Zero bit is '0',<br>(PC) + 2 + 2n $\rightarrow$ PC |                                                         |  |

| Statu                                                                                                                                                    | is Affected:           | None                                                                                                                                                                                                                                                                                         |                                                                             |                                    | Statu                                       | is Affected:           | None                                                                                                                                                                                                                                                                         |                                                       |                                                         |  |

| Enco                                                                                                                                                     | oding:                 | 1110                                                                                                                                                                                                                                                                                         | 0101 nnr                                                                    | nn nnnn                            | Enco                                        | oding:                 | 1110                                                                                                                                                                                                                                                                         | 0001 nn:                                              | nn nnnn                                                 |  |

| Description:                                                                                                                                             |                        | If the Overflow bit is '0', then the<br>program will branch.<br>The 2's complement number, '2n', is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>two-cycle instruction. |                                                                             |                                    | Desc                                        | ription:               | If the Zero bit is '0', then the progra<br>will branch.<br>The 2's complement number, '2n',<br>added to the PC. Since the PC will<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is the<br>two-cycle instruction. |                                                       | ber, '2n', is<br>le PC will have<br>next<br>ess will be |  |

| Word                                                                                                                                                     | ds:                    | 1                                                                                                                                                                                                                                                                                            |                                                                             |                                    | Word                                        | ls:                    | 1                                                                                                                                                                                                                                                                            |                                                       |                                                         |  |

| Cycle                                                                                                                                                    | es:                    | 1(2)                                                                                                                                                                                                                                                                                         |                                                                             |                                    | Cycle                                       | Cycles: 1(2)           |                                                                                                                                                                                                                                                                              |                                                       |                                                         |  |

|                                                                                                                                                          | ycle Activity:<br>Imp: |                                                                                                                                                                                                                                                                                              |                                                                             |                                    |                                             | ycle Activity:<br>Imp: |                                                                                                                                                                                                                                                                              |                                                       |                                                         |  |

|                                                                                                                                                          | Q1                     | Q2                                                                                                                                                                                                                                                                                           | Q3                                                                          | Q4                                 |                                             | Q1                     | Q2                                                                                                                                                                                                                                                                           | Q3                                                    | Q4                                                      |  |

|                                                                                                                                                          | Decode                 | Read literal<br>'n'                                                                                                                                                                                                                                                                          | Process<br>Data                                                             | Write to PC                        |                                             | Decode                 | Read literal<br>'n'                                                                                                                                                                                                                                                          | Process<br>Data                                       | Write to PC                                             |  |

|                                                                                                                                                          | No<br>operation        | No<br>operation                                                                                                                                                                                                                                                                              | No<br>operation                                                             | No<br>operation                    |                                             | No<br>operation        | No<br>operation                                                                                                                                                                                                                                                              | No<br>operation                                       | No<br>operation                                         |  |

| lf No                                                                                                                                                    | o Jump:                |                                                                                                                                                                                                                                                                                              |                                                                             |                                    | lf No                                       | o Jump:                |                                                                                                                                                                                                                                                                              |                                                       |                                                         |  |

|                                                                                                                                                          | Q1                     | Q2                                                                                                                                                                                                                                                                                           | Q3                                                                          | Q4                                 |                                             | Q1                     | Q2                                                                                                                                                                                                                                                                           | Q3                                                    | Q4                                                      |  |

|                                                                                                                                                          | Decode                 | Read literal<br>'n'                                                                                                                                                                                                                                                                          | Process<br>Data                                                             | No<br>operation                    |                                             | Decode                 | Read literal<br>'n'                                                                                                                                                                                                                                                          | Process<br>Data                                       | No<br>operation                                         |  |

| Exan                                                                                                                                                     |                        | HERE                                                                                                                                                                                                                                                                                         | BNOV Jump                                                                   |                                    | Exan                                        |                        | HERE                                                                                                                                                                                                                                                                         | BNZ Jump                                              |                                                         |  |

| Before Instruction<br>PC = address (HERE)<br>After Instruction<br>If Overflow = 0;<br>PC = address (Jump)<br>If Overflow = 1;<br>PC = address (HERE + 2) |                        |                                                                                                                                                                                                                                                                                              | Before Instruct<br>PC<br>After Instructio<br>If Zero<br>PC<br>If Zero<br>PC | = ad<br>on<br>= 0;<br>= ad<br>= 1; | dress (HERE)<br>dress (Jump)<br>dress (HERE |                        |                                                                                                                                                                                                                                                                              |                                                       |                                                         |  |

| SLEEP                  | Enter Sle                                                                                                                                                                                                                                             | ep mode         |        | SUBFWB                                                                                                                                             | Subtract                                                                                   | f from W w                               | ith Borrow                                                               |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------|--------------------------------------------------------------------------|

| Syntax:                | SLEEP                                                                                                                                                                                                                                                 |                 |        | Syntax:                                                                                                                                            | SUBFWB                                                                                     | f {,d {,a}}                              |                                                                          |

| Operands:              | None                                                                                                                                                                                                                                                  |                 |        | Operands:                                                                                                                                          | $0 \le f \le 255$                                                                          | 5                                        |                                                                          |

| Operation:             | $00h \rightarrow WE$                                                                                                                                                                                                                                  | DT,             |        |                                                                                                                                                    | $d \in [0, 1]$                                                                             |                                          |                                                                          |

|                        |                                                                                                                                                                                                                                                       | postscaler,     |        | <b>o</b> "                                                                                                                                         | a ∈ [0,1]                                                                                  | . <u></u>                                |                                                                          |

|                        | $1 \rightarrow \frac{\text{TO}}{\text{PD}},\\ 0 \rightarrow \frac{\text{PD}}{\text{PD}}$                                                                                                                                                              |                 |        | Operation:                                                                                                                                         |                                                                                            | $(\overline{C}) \rightarrow \text{dest}$ |                                                                          |

| Status Affected:       | TO, PD                                                                                                                                                                                                                                                |                 |        | Status Affected:                                                                                                                                   | N, OV, C,                                                                                  |                                          |                                                                          |

|                        |                                                                                                                                                                                                                                                       | 0000 000        | 0 0011 | Encoding:                                                                                                                                          | 0101                                                                                       | 01da ff                                  |                                                                          |

| Description:           | ncoding: 0000 0000 0011   escription: The Power-Down status bit (PD) is<br>cleared. The Time-out status bit (TO)<br>is set. Watchdog Timer and its<br>postscaler are cleared.<br>The processor is put into Sleep mode<br>with the oscillator stopped. |                 |        | Description:                                                                                                                                       | (borrow) fr<br>method). I<br>in W. If 'd'<br>register 'f'<br>If 'a' is '0',<br>selected. I | the Access Bailf 'a' is '1', the         | nplement<br>esult is stored<br>ilt is stored in<br>ank is<br>BSR is used |

| Words:                 | 1                                                                                                                                                                                                                                                     |                 |        |                                                                                                                                                    |                                                                                            | he GPR bank<br>and the extend            | · /                                                                      |

| Cycles:                | 1                                                                                                                                                                                                                                                     |                 |        |                                                                                                                                                    |                                                                                            | bled, this instru                        |                                                                          |

| Q Cycle Activity:      |                                                                                                                                                                                                                                                       |                 |        |                                                                                                                                                    | •                                                                                          | n Indexed Lite                           |                                                                          |

| Q1                     | Q2                                                                                                                                                                                                                                                    | Q3              | Q4     |                                                                                                                                                    |                                                                                            | g mode whene<br>n). See <b>Sectio</b>    |                                                                          |

| Decode                 | No                                                                                                                                                                                                                                                    | Process         | Go to  |                                                                                                                                                    | "Byte-Orio                                                                                 | ented and Bit-                           | Oriented                                                                 |

|                        | operation                                                                                                                                                                                                                                             | Data            | Sleep  |                                                                                                                                                    | Instructio<br>Mode" for                                                                    | ns in Indexed                            | Literal Offset                                                           |

| Example:               | SLEEP                                                                                                                                                                                                                                                 |                 |        | Words:                                                                                                                                             | 1 1                                                                                        | uetails.                                 |                                                                          |

| Before Instru          | ction                                                                                                                                                                                                                                                 |                 |        | Cycles:                                                                                                                                            | 1                                                                                          |                                          |                                                                          |

| <u>TO</u> =            | ?                                                                                                                                                                                                                                                     |                 |        | Q Cycle Activity:                                                                                                                                  |                                                                                            |                                          |                                                                          |

| PD =                   | ?                                                                                                                                                                                                                                                     |                 |        | Q Cycle Activity.<br>Q1                                                                                                                            | Q2                                                                                         | Q3                                       | Q4                                                                       |

| After Instruct<br>TO = | ion<br>1†                                                                                                                                                                                                                                             |                 |        | Decode                                                                                                                                             | Read                                                                                       | Process                                  | Write to                                                                 |

| $\frac{10}{PD} =$      | 0                                                                                                                                                                                                                                                     |                 |        | 200000                                                                                                                                             | register 'f'                                                                               | Data                                     | destination                                                              |

| † If WDT causes        | wake-up, this t                                                                                                                                                                                                                                       | bit is cleared. |        | Example 1:<br>Before Instruct<br>REG<br>W<br>C<br>After Instructi<br>REG<br>W<br>C<br>Z<br>N                                                       | = 3<br>= 2<br>= 1<br>on<br>= FF<br>= 2<br>= 0<br>= 0<br>= 1 ; re                           | REG, 1, 0                                | e                                                                        |

|                        |                                                                                                                                                                                                                                                       |                 |        | Example 2:<br>Before Instruc                                                                                                                       | SUBFWB                                                                                     | REG, 0, 0                                |                                                                          |

|                        |                                                                                                                                                                                                                                                       |                 |        | REG<br>W<br>C<br>After Instruction<br>REG<br>W<br>C<br>Z<br>N<br><u>Example 3:</u><br>Before Instruct<br>REG<br>W<br>C<br>After Instruction<br>REG | = 2<br>= 3<br>= 1<br>= 0<br>= 0; re<br>SUBFWB<br>ction<br>= 1<br>= 2<br>= 0<br>on<br>= 0   | sult is positive<br>REG,1,0              |                                                                          |