Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 21                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 10x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Through Hole                                                                |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 28-SPDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf25j10-i-sp |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1.0   | Device Overview                                                           | 7   |

|-------|---------------------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with PIC18FJ Microcontrollers              | 23  |

| 3.0   | Oscillator Configurations                                                 | 27  |

| 4.0   | Power-Managed Modes                                                       | 35  |

| 5.0   | Reset                                                                     | 41  |

| 6.0   | Memory Organization                                                       | 51  |

| 7.0   | Flash Program Memory                                                      | 71  |

| 8.0   | 8 x 8 Hardware Multiplier                                                 | 81  |

| 9.0   | Interrupts                                                                | 83  |

| 10.0  | I/O Ports                                                                 | 97  |

| 11.0  | Timer0 Module                                                             | 115 |

| 12.0  | Timer1 Module                                                             | 119 |

| 13.0  | Timer2 Module                                                             | 125 |

| 14.0  | Capture/Compare/PWM (CCP) Modules                                         |     |

| 15.0  | Enhanced Capture/Compare/PWM (ECCP) Module                                | 135 |

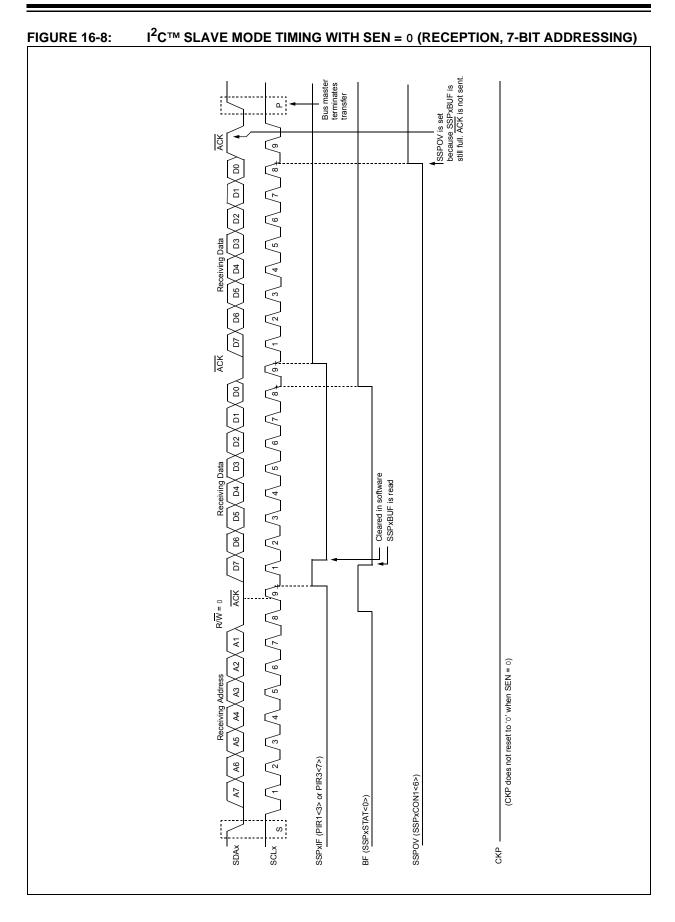

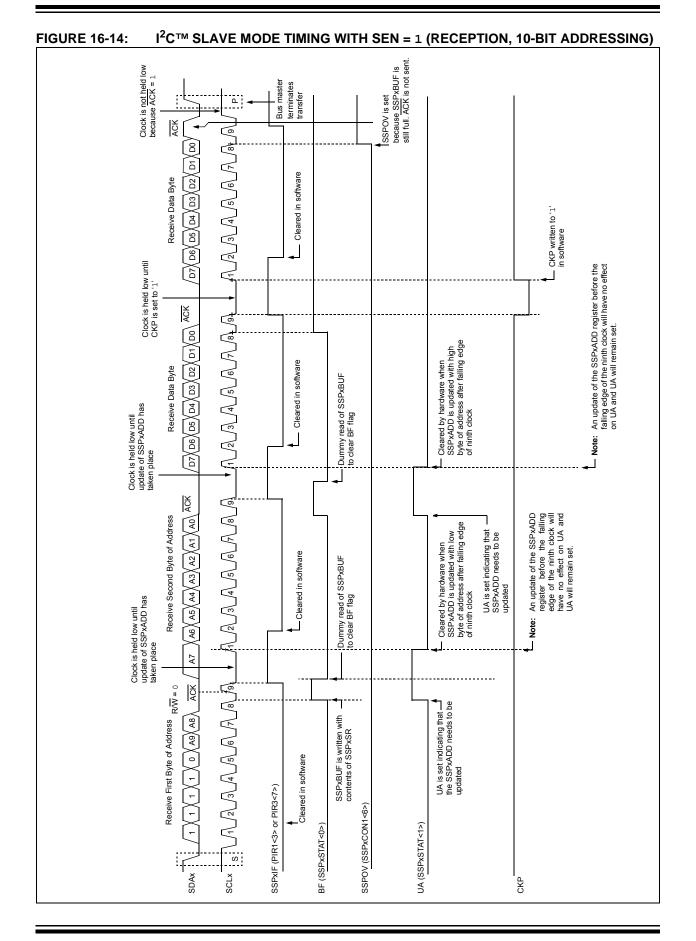

| 16.0  | Master Synchronous Serial Port (MSSP) Module                              | 149 |

| 17.0  | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) | 193 |

| 18.0  | 10-Bit Analog-to-Digital Converter (A/D) Module                           | 215 |

| 19.0  | Comparator Module                                                         |     |

| 20.0  |                                                                           |     |

| 21.0  | Special Features of the CPU                                               | 235 |

| 22.0  | Instruction Set Summary                                                   |     |

| 23.0  | Development Support                                                       | 299 |

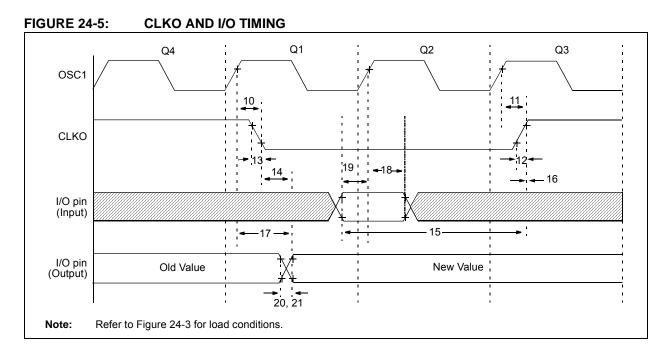

| 24.0  | Electrical Characteristics                                                | 303 |

|       | Packaging Information                                                     |     |

|       | ndix A: Revision History                                                  |     |

| Appe  | ndix B: Migration Between High-End Device Families                        | 350 |

| Index | <                                                                         | 353 |

|       | Nicrochip Web Site                                                        |     |

| Custo | omer Change Notification Service                                          | 363 |

|       | omer Support                                                              |     |

|       | ler Response                                                              |     |

| PIC1  | 8F45J10 family Product Identification System                              | 365 |

# 5.5 Configuration Mismatch (CM)

The Configuration Mismatch (CM) Reset is designed to detect and attempt to recover from random, memory corrupting events. These include Electrostatic Discharge (ESD) events, which can cause widespread, single-bit changes throughout the device and result in catastrophic failure.

In PIC18FXXJ Flash devices, the device Configuration registers (located in the configuration memory space) are continuously monitored during operation by comparing their values to complimentary shadow registers. If a mismatch is detected between the two sets of registers, a CM Reset automatically occurs. These events are captured by the CM bit (RCON<5>). The state of the bit is set to '0' whenever a CM event occurs; it does not change for any other Reset event.

A CM Reset behaves similarly to a Master Clear Reset, RESET instruction, WDT time-out or Stack Event Resets. As with all hard and power Reset events, the device Configuration Words are reloaded from the Flash Configuration Words in program memory as the device restarts.

### 5.6 Power-up Timer (PWRT)

PIC18F45J10 family devices incorporate an on-chip Power-up Timer (PWRT) to help regulate the Power-on Reset process. The PWRT is always enabled. The main function is to ensure that the device voltage is stable before code is executed.

The Power-up Timer (PWRT) of the PIC18F45J10 family devices is an 11-bit counter which uses the INTRC source as the clock input. This yields an approximate time interval of 2048 x 32  $\mu$ s = 65.6 ms. While the PWRT is counting, the device is held in Reset.

The power-up time delay depends on the INTRC clock and will vary from chip to chip due to temperature and process variation. See DC parameter 33 for details.

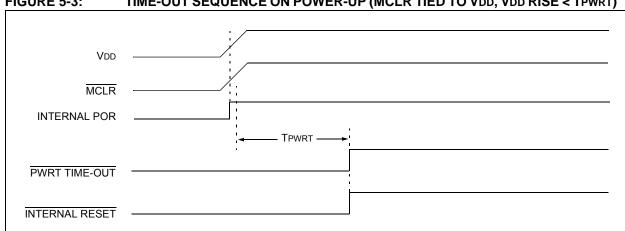

#### 5.6.1 TIME-OUT SEQUENCE

If enabled, the PWRT time-out is invoked after the POR pulse has cleared. The total time-out will vary based on the status of the PWRT. Figure 5-3, Figure 5-4, Figure 5-5 and Figure 5-6 all depict time-out sequences on power-up with the Power-up Timer enabled.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$ is kept low long enough, the PWRT will expire. Bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 5-5). This is useful for testing purposes, or to synchronize more than one PIC18F device operating in parallel.

#### FIGURE 5-3: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD, VDD RISE < TPWRT)

# 6.0 MEMORY ORGANIZATION

There are two types of memory in PIC18 Enhanced microcontroller devices:

- Program Memory

- Data RAM

As Harvard architecture devices, the data and program memories use separate busses; this allows for concurrent access of the two memory spaces.

Additional detailed information on the operation of the Flash program memory is provided in **Section 7.0 "Flash Program Memory"**.

### 6.1 Program Memory Organization

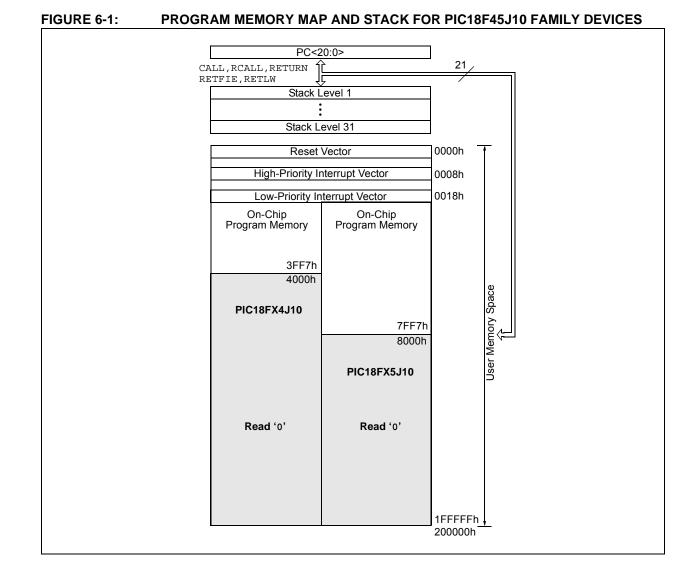

PIC18 microcontrollers implement a 21-bit program counter, which is capable of addressing a 2-Mbyte program memory space. Accessing a location between the upper boundary of the physically implemented memory and the 2-Mbyte address will return all '0's (a NOP instruction).

The PIC18F24J10 and PIC18F44J10 each have 16 Kbytes of Flash memory and can store up to 8,192 single-word instructions. The PIC18F25J10 and PIC18F45J10 each have 32 Kbytes of Flash memory and can store up to 16,384 single-word instructions.

PIC18 devices have two interrupt vectors. The Reset vector address is at 0000h and the interrupt vector addresses are at 0008h and 0018h.

The program memory map for the PIC18F45J10 family devices is shown in Figure 6-1.

#### 6.1.4.4 Stack Full and Underflow Resets

Device Resets on stack overflow and stack underflow conditions are enabled by setting the STVREN bit in Configuration Register 4L. When STVREN is set, a full or underflow will set the appropriate STKFUL or STKUNF bit and then cause a device Reset. When STVREN is cleared, a full or underflow condition will set the appropriate STKFUL or STKUNF bit but not cause a device Reset. The STKFUL or STKUNF bits are cleared by the user software or a Power-on Reset.

#### 6.1.5 FAST REGISTER STACK

A Fast Register Stack is provided for the STATUS, WREG and BSR registers, to provide a "fast return" option for interrupts. The stack for each register is only one level deep and is neither readable nor writable. It is loaded with the current value of the corresponding register when the processor vectors for an interrupt. All interrupt sources will push values into the stack registers. The values in the registers are then loaded back into their associated registers if the RETFIE, FAST instruction is used to return from the interrupt.

If both low and high-priority interrupts are enabled, the stack registers cannot be used reliably to return from low-priority interrupts. If a high-priority interrupt occurs while servicing a low-priority interrupt, the stack register values stored by the low-priority interrupt will be overwritten. In these cases, users must save the key registers in software during a low-priority interrupt.

If interrupt priority is not used, all interrupts may use the Fast Register Stack for returns from interrupt. If no interrupts are used, the Fast Register Stack can be used to restore the STATUS, WREG and BSR registers at the end of a subroutine call. To use the Fast Register Stack for a subroutine call, a CALL label, FAST instruction must be executed to save the STATUS, WREG and BSR registers to the Fast Register Stack. A RETURN, FAST instruction is then executed to restore these registers from the Fast Register Stack.

Example 6-1 shows a source code example that uses the Fast Register Stack during a subroutine call and return.

#### EXAMPLE 6-1: FAST REGISTER STACK CODE EXAMPLE

| CALL SUB1, FAST | ;STATUS, WREG, BSR<br>;SAVED IN FAST REGISTER<br>;STACK |

|-----------------|---------------------------------------------------------|

| SUB1 •          |                                                         |

| RETURN, FAST    | ;RESTORE VALUES SAVED<br>;IN FAST REGISTER STACK        |

#### 6.1.6 LOOK-UP TABLES IN PROGRAM MEMORY

There may be programming situations that require the creation of data structures, or look-up tables, in program memory. For PIC18 devices, look-up tables can be implemented in two ways:

- Computed GOTO

- Table Reads

#### 6.1.6.1 Computed GOTO

A computed GOTO is accomplished by adding an offset to the program counter. An example is shown in Example 6-2.

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW nn instructions. The W register is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW nn instructions that returns the value 'nn' to the calling function.

The offset value (in WREG) specifies the number of bytes that the program counter should advance and should be multiples of 2 (LSb = 0).

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

#### EXAMPLE 6-2: COMPUTED GOTO USING AN OFFSET VALUE

|       | MOVF  | OFFSET, W |

|-------|-------|-----------|

|       | CALL  | TABLE     |

| ORG   | nn00h |           |

| TABLE | ADDWF | PCL       |

|       | RETLW | nnh       |

|       | RETLW | nnh       |

|       | RETLW | nnh       |

|       | •     |           |

|       | •     |           |

|       | •     |           |

|       |       |           |

#### 6.1.6.2 Table Reads and Table Writes

A better method of storing data in program memory allows two bytes of data to be stored in each instruction location.

Look-up table data may be stored two bytes per program word by using table reads and writes. The Table Pointer (TBLPTR) register specifies the byte address and the Table Latch (TABLAT) register contains the data that is read from or written to program memory. Data is transferred to or from program memory one byte at a time.

Table read and table write operations are discussed further in Section 7.1 "Table Reads and Table Writes".

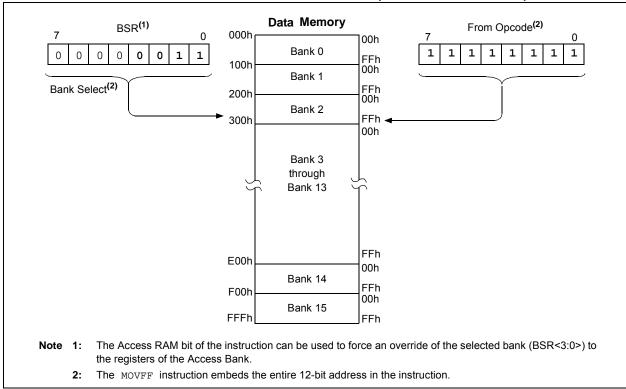

#### FIGURE 6-7: USE OF THE BANK SELECT REGISTER (DIRECT ADDRESSING)

#### 6.3.2 ACCESS BANK

While the use of the BSR with an embedded 8-bit address allows users to address the entire range of data memory, it also means that the user must always ensure that the correct bank is selected. Otherwise, data may be read from or written to the wrong location. This can be disastrous if a GPR is the intended target of an operation but an SFR is written to instead. Verifying and/or changing the BSR for each read or write to data memory can become very inefficient.

To streamline access for the most commonly used data memory locations, the data memory is configured with an Access Bank, which allows users to access a mapped block of memory without specifying a BSR. The Access Bank consists of the first 128 bytes of memory (00h-7Fh) in Bank 0 and the last 128 bytes of memory (80h-FFh) in Block 15. The lower half is known as the "Access RAM" and is composed of GPRs. This upper half is also where the device's SFRs are mapped. These two areas are mapped contiguously in the Access Bank and can be addressed in a linear fashion by an 8-bit address (Figure 6-6).

The Access Bank is used by core PIC18 instructions that include the Access RAM bit (the 'a' parameter in the instruction). When 'a' is equal to '1', the instruction uses the BSR and the 8-bit address included in the opcode for the data memory address. When 'a' is '0',

however, the instruction is forced to use the Access Bank address map; the current value of the BSR is ignored entirely.

Using this "forced" addressing allows the instruction to operate on a data address in a single cycle without updating the BSR first. For 8-bit addresses of 80h and above, this means that users can evaluate and operate on SFRs more efficiently. The Access RAM below 80h is a good place for data values that the user might need to access rapidly, such as immediate computational results or common program variables. Access RAM also allows for faster and more code efficient context saving and switching of variables.

The mapping of the Access Bank is slightly different when the extended instruction set is enabled (XINST Configuration bit = 1). This is discussed in more detail in Section 6.5.3 "Mapping the Access Bank in Indexed Literal Offset Mode".

#### 6.3.3 GENERAL PURPOSE REGISTER FILE

PIC18 devices may have banked memory in the GPR area. This is data RAM which is available for use by all instructions. GPRs start at the bottom of Bank 0 (address 000h) and grow upwards towards the bottom of the SFR area. GPRs are not initialized by a Power-on Reset and are unchanged on all other Resets.

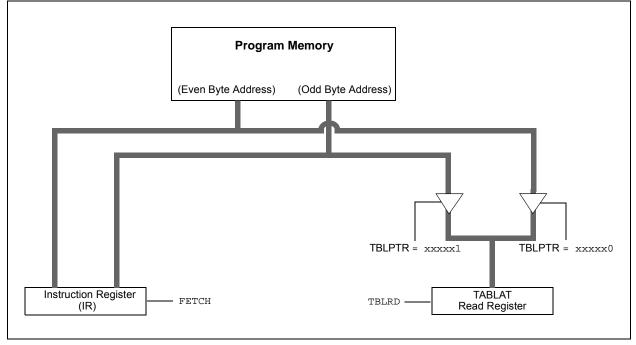

### 7.3 Reading the Flash Program Memory

The TBLRD instruction is used to retrieve data from program memory and places it into data RAM. Table reads from program memory are performed one byte at a time.

TBLPTR points to a byte address in program space. Executing TBLRD places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next table read operation.

The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 7-4 shows the interface between the internal program memory and the TABLAT.

### FIGURE 7-4: READS FROM FLASH PROGRAM MEMORY

#### EXAMPLE 7-1: READING A FLASH PROGRAM MEMORY WORD

|           | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>MOVLW | CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE_ADDR_LOW |   | Load TBLPTR with the base<br>address of the word |

|-----------|-------------------------------------------|--------------------------------------------------------------------------|---|--------------------------------------------------|

|           | MOVWF                                     | TBLPTRL                                                                  |   |                                                  |

| READ_WORD |                                           |                                                                          |   |                                                  |

|           | TBLRD*+                                   |                                                                          | ; | read into TABLAT and increment                   |

|           | MOVF                                      | TABLAT, W                                                                | ; | get data                                         |

|           | MOVWF                                     | WORD_EVEN                                                                |   |                                                  |

|           | TBLRD*+                                   |                                                                          | ; | read into TABLAT and increment                   |

|           | MOVF                                      | TABLAT, W                                                                | ; | get data                                         |

|           | MOVWF                                     | WORD_ODD                                                                 |   |                                                  |

#### EXAMPLE 12-1: IMPLEMENTING A REAL-TIME CLOCK USING A TIMER1 INTERRUPT SERVICE

| RTCinit |        |              |                                               |

|---------|--------|--------------|-----------------------------------------------|

|         | MOVLW  | 80h          | ; Preload TMR1 register pair                  |

|         | MOVWF  | TMR1H        | ; for 1 second overflow                       |

|         | CLRF   | TMR1L        |                                               |

|         | MOVLW  | b'00001111'  | ; Configure for external clock,               |

|         | MOVWF  | T1CON        | ; Asynchronous operation, external oscillator |

|         | CLRF   | secs         | ; Initialize timekeeping registers            |

|         | CLRF   | mins         | i                                             |

|         | MOVLW  | .12          |                                               |

|         | MOVWF  | hours        |                                               |

|         | BSF    | PIE1, TMR1IE | ; Enable Timer1 interrupt                     |

|         | RETURN |              |                                               |

| RTCisr  |        |              |                                               |

|         | BSF    | TMR1H, 7     | ; Preload for 1 sec overflow                  |

|         | BCF    | PIR1, TMR1IF | ; Clear interrupt flag                        |

|         | INCF   | secs, F      | ; Increment seconds                           |

|         | MOVLW  | .59          | ; 60 seconds elapsed?                         |

|         | CPFSGT | secs         |                                               |

|         | RETURN |              | ; No, done                                    |

|         | CLRF   | secs         | ; Clear seconds                               |

|         | INCF   | mins, F      | ; Increment minutes                           |

|         | MOVLW  | .59          | ; 60 minutes elapsed?                         |

|         | CPFSGT | mins         |                                               |

|         | RETURN |              | ; No, done                                    |

|         | CLRF   | mins         | ; clear minutes                               |

|         | INCF   | hours, F     | ; Increment hours                             |

|         | MOVLW  | .23          | ; 24 hours elapsed?                           |

|         | CPFSGT | hours        |                                               |

|         | RETURN |              | ; No, done                                    |

|         | CLRF   | hours        | ; Reset hours                                 |

|         | RETURN |              | ; Done                                        |

|         |        |              |                                               |

### TABLE 12-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Name   | Bit 7                     | Bit 6     | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|---------------------------|-----------|---------|---------|---------|--------|--------|--------|----------------------------|

| INTCON | GIE/GIEH                  | PEIE/GIEL | TMR0IE  | INT0IE  | RBIE    | TMR0IF | INT0IF | RBIF   | 47                         |

| PIR1   | PSPIF <sup>(1)</sup>      | ADIF      | RCIF    | TXIF    | SSP1IF  | CCP1IF | TMR2IF | TMR1IF | 49                         |

| PIE1   | PSPIE <sup>(1)</sup>      | ADIE      | RCIE    | TXIE    | SSP1IE  | CCP1IE | TMR2IE | TMR1IE | 49                         |

| IPR1   | PSPIP <sup>(1)</sup>      | ADIP      | RCIP    | TXIP    | SSP1IP  | CCP1IP | TMR2IP | TMR1IP | 49                         |

| TMR1L  | Timer1 Register Low Byte  |           |         |         |         |        |        |        | 48                         |

| TMR1H  | Timer1 Register High Byte |           |         |         |         |        |        |        | 48                         |

| T1CON  | RD16                      | T1RUN     | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 48                         |

**Legend:** Shaded cells are not used by the Timer1 module.

Note 1: These bits are not implemented on 28-pin devices and should be read as '0'.

### V+ PIC18F4XJ10 QC FET QA FET Driver Driver P1A Load P1B FET FET Driver Driver P1C QD QB V-P1D

### FIGURE 15-7: EXAMPLE OF FULL-BRIDGE APPLICATION

### 15.4.5.1 Direction Change in Full-Bridge Mode

In the Full-Bridge Output mode, the P1M1 bit in the CCP1CON register allows the user to control the forward/reverse direction. When the application firmware changes this direction control bit, the module will assume the new direction on the next PWM cycle.

Just before the end of the current PWM period, the modulated outputs (P1B and P1D) are placed in their inactive state, while the unmodulated outputs (P1A and P1C) are switched to drive in the opposite direction. This occurs in the time interval, 4 Tosc \* (Timer2 Prescale Value), before the next PWM period begins. The Timer2 prescaler will be either 1, 4 or 16, depending on the value of the T2CKPS<1:0> bits (T2CON<1:0>). During the interval from the switch of the unmodulated outputs to the beginning of the next period, the modulated outputs (P1B and P1D) remain inactive. This relationship is shown in Figure 15-8.

Note that in the Full-Bridge Output mode, the ECCP1 module does not provide any dead-band delay. In general, since only one output is modulated at all times, dead-band delay is not required. However, there is a situation where a dead-band delay might be required. This situation occurs when both of the following conditions are true:

- 1. The direction of the PWM output changes when the duty cycle of the output is at or near 100%.

- 2. The turn-off time of the power switch, including the power device and driver circuit, is greater than the turn-on time.

Figure 15-9 shows an example where the PWM direction changes from forward to reverse at a near 100% duty cycle. At time t1, the outputs P1A and P1D become inactive while output P1C becomes active. In this example, since the turn-off time of the power devices is longer than the turn-on time, a shoot-through current may flow through power devices, QC and QD (see Figure 15-7), for the duration of 't'. The same phenomenon will occur to power devices, QA and QB, for PWM direction change from reverse to forward.

If changing PWM direction at high duty cycle is required for an application, one of the following requirements must be met:

- 1. Reduce PWM for a PWM period before changing directions.

- 2. Use switch drivers that can drive the switches off faster than they can drive them on.

Other options to prevent shoot-through current may exist.

#### .

| R/W-0      | R/W-0                                                         | R/W-0                                                                                                                                                                        | R/W-0                                                                           | R/W-0                                                          | R/W-0                        | R/W-0                | R/W-0                |

|------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------|----------------------|----------------------|

| WCOL       | SSPOV <sup>(1</sup>                                           | ) SSPEN <sup>(2)</sup>                                                                                                                                                       | CKP                                                                             | SSPM3 <sup>(3)</sup>                                           | SSPM2 <sup>(3)</sup>         | SSPM1 <sup>(3)</sup> | SSPM0 <sup>(3)</sup> |

| bit 7      |                                                               |                                                                                                                                                                              |                                                                                 |                                                                |                              |                      | bit (                |

| Legend:    |                                                               |                                                                                                                                                                              |                                                                                 |                                                                |                              |                      |                      |

| R = Read   | able bit                                                      | W = Writable b                                                                                                                                                               | bit                                                                             | U = Unimplen                                                   | nented bit, read             | d as '0'             |                      |

| -n = Value | e at POR                                                      | '1' = Bit is set                                                                                                                                                             |                                                                                 | '0' = Bit is cle                                               | ared                         | x = Bit is unkr      | nown                 |

| bit 7      |                                                               | ,                                                                                                                                                                            |                                                                                 | e it is still transn                                           | nitting the previ            | ous word (mus        | t be cleared ir      |

| bit 6      | SSPOV: R                                                      | eceive Overflow Ir                                                                                                                                                           | dicator bit <sup>(1)</sup>                                                      |                                                                |                              |                      |                      |

|            | overflo<br>the SS<br>softwa<br>0 = No ove                     | erflow                                                                                                                                                                       | PxSR is lost. (<br>only transmi                                                 | Overflow can or<br>tting data, to a                            | ly occur in Slav             | ve mode. The ι       | iser must read       |

| bit 5      | 1 = Enable                                                    | aster Synchronou<br>s serial port and c<br>es serial port and c                                                                                                              | onfigures SC                                                                    | Kx, SDOx, SDIx                                                 |                              | erial port pins      |                      |

| bit 4      | CKP: Clock                                                    | k Polarity Select b                                                                                                                                                          | it                                                                              |                                                                |                              |                      |                      |

|            |                                                               | te for clock is a hi<br>te for clock is a lo                                                                                                                                 | Ģ                                                                               |                                                                |                              |                      |                      |

| bit 3-0    | 0101 = SP<br>0100 = SP<br>0011 = SP<br>0010 = SP<br>0001 = SP | >: Master Synchro<br>I Slave mode, cloo<br>I Slave mode, cloo<br>I Master mode, cloo<br>I Master mode, clo<br>I Master mode, clo<br>I Master mode, clo<br>I Master mode, clo | ck = SCKx pir<br>ck = SCKx pir<br>ock = TMR2 c<br>ock = FOSC/6<br>ock = FOSC/10 | n, <u>SSx</u> pin contro<br>n, SSx pin contro<br>putput/2<br>4 | ol disabled, $\overline{SS}$ | x can be used        | as I/O pin           |

| Note 1:    |                                                               | e, the overflow bit<br>SPxBUF register.                                                                                                                                      | is not set sind                                                                 | ce each new rec                                                | ception (and tra             | insmission) is ir    | nitiated by          |

- 2: When enabled, these pins must be properly configured as input or output.

- 3: Bit combinations not specifically listed here are either reserved or implemented in I<sup>2</sup>C<sup>™</sup> mode only.

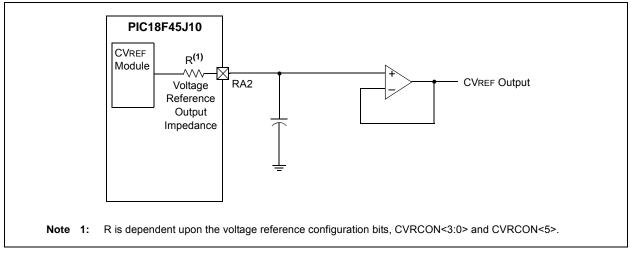

#### FIGURE 20-2: COMPARATOR VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

#### TABLE 20-1: REGISTERS ASSOCIATED WITH COMPARATOR VOLTAGE REFERENCE

| Name   | Bit 7 | Bit 6 | Bit 5  | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|-------|-------|--------|-------|--------|--------|--------|--------|----------------------------|

| CVRCON | CVREN | CVROE | CVRR   | CVRSS | CVR3   | CVR2   | CVR1   | CVR0   | 49                         |

| CMCON  | C2OUT | C10UT | C2INV  | C1INV | CIS    | CM2    | CM1    | CM0    | 49                         |

| TRISA  | _     | _     | TRISA5 | _     | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 50                         |

Legend: Shaded cells are not used with the comparator voltage reference.

### TABLE 22-1: OPCODE FIELD DESCRIPTIONS

| Field           | Description                                                                                                                                  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| a               | RAM access bit                                                                                                                               |

|                 | a = 0: RAM location in Access RAM (BSR register is ignored)                                                                                  |

|                 | a = 1: RAM bank is specified by BSR register                                                                                                 |

| bbb             | Bit address within an 8-bit file register (0 to 7).                                                                                          |

| BSR             | Bank Select Register. Used to select the current RAM bank.                                                                                   |

| C, DC, Z, OV, N | ALU Status bits: Carry, Digit Carry, Zero, Overflow, Negative.                                                                               |

| d               | Destination select bit                                                                                                                       |

|                 | d = 0: store result in WREG                                                                                                                  |

|                 | d = 1: store result in file register f                                                                                                       |

| dest            | Destination: either the WREG register or the specified register file location.                                                               |

| f               | 8-bit register file address (00h to FFh) or 2-bit FSR designator (0h to 3h).                                                                 |

| f <sub>s</sub>  | 12-bit register file address (000h to FFFh). This is the source address.                                                                     |

| f <sub>d</sub>  | 12-bit register file address (000h to FFFh). This is the destination address.                                                                |

| GIE             | Global Interrupt Enable bit.                                                                                                                 |

| k               | Literal field, constant data or label (may be either an 8-bit, 12-bit or a 20-bit value).                                                    |

| label           | Label name.                                                                                                                                  |

| mm              | The mode of the TBLPTR register for the table read and table write instructions.<br>Only used with table read and table write instructions:  |

| *               |                                                                                                                                              |

|                 | No change to register (such as TBLPTR with table reads and writes)                                                                           |

| *+              | Post-Increment register (such as TBLPTR with table reads and writes)                                                                         |

| *_              | Post-Decrement register (such as TBLPTR with table reads and writes)                                                                         |

| +*              | Pre-Increment register (such as TBLPTR with table reads and writes)                                                                          |

| n               | The relative address (2's complement number) for relative branch instructions or the direct address for Call/Branch and Return instructions. |

| PG              |                                                                                                                                              |

| PC              | Program Counter.                                                                                                                             |

| PCL             | Program Counter Low Byte.                                                                                                                    |

| PCH             | Program Counter High Byte.                                                                                                                   |

| PCLATH          | Program Counter High Byte Latch.                                                                                                             |

| PCLATU          | Program Counter Upper Byte Latch. Power-down bit.                                                                                            |

| PD              |                                                                                                                                              |

| PRODH           | Product of Multiply High Byte.                                                                                                               |

| PRODL           | Product of Multiply Low Byte.                                                                                                                |

| S               | Fast Call/Return mode select bit<br>s = 0: do not update into/from shadow registers                                                          |

|                 | s = 1: certain registers loaded into/from shadow registers (Fast mode)                                                                       |

| TBLPTR          | 21-bit Table Pointer (points to a program memory location).                                                                                  |

| TABLAT          | 8-bit Table Latch.                                                                                                                           |

| TO              | Time-out bit.                                                                                                                                |

| TOS             | Top-of-Stack.                                                                                                                                |

| u               | Unused or unchanged.                                                                                                                         |

| WDT             | Watchdog Timer.                                                                                                                              |

| WREG            | Working register (accumulator).                                                                                                              |

| x               | Don't care ('0' or '1'). The assembler will generate code with $x = 0$ . It is the recommended form of use for                               |

|                 | compatibility with all Microchip software tools.                                                                                             |

| Z <sub>S</sub>  | 7-bit offset value for indirect addressing of register files (source).                                                                       |

| zd              | 7-bit offset value for indirect addressing of register files (destination).                                                                  |

| { }             | Optional argument.                                                                                                                           |

| [text]          | Indicates an indexed address.                                                                                                                |

| (text)          | The contents of text.                                                                                                                        |

| [expr] <n></n>  | Specifies bit n of the register indicated by the pointer expr.                                                                               |

| →               | Assigned to.                                                                                                                                 |

| < >             | Register bit field.                                                                                                                          |

| e               | In the set of.                                                                                                                               |

| italics         | User-defined term (font is Courier New).                                                                                                     |

| RRM         | NCF                                            | Rotate Right f (No Carry)                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                      |         |   |                       |  |  |

|-------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------|---|-----------------------|--|--|

| Synt        | ax:                                            | RRNCF                                                                                                                                                 | f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <sup>;</sup> {,d {,a}}               |         |   |                       |  |  |

| Oper        | rands:                                         | d ∈ [0,                                                                                                                                               | $0 \le f \le 255$<br>$d \in [0, 1]$<br>$a \in [0, 1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                      |         |   |                       |  |  |

| Ope         | ration:                                        | (f <n>) –<br/>(f&lt;0&gt;) –</n>                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | est <n 1<br="" –="">est&lt;7&gt;</n> | L>,     |   |                       |  |  |

| Statu       | is Affected:                                   | N, Z                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                      |         |   |                       |  |  |

| Enco        | oding:                                         | 0100                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 00da                                 | fff     | f | ffff                  |  |  |

| Desc        | pription:                                      | one bit f<br>is placed b<br>If 'a' is '<br>selected<br>is '1', th<br>per the<br>If 'a' is '<br>set is er<br>in Index<br>mode w<br>Section<br>Bit-Orie | The contents of register 'f' are rotated<br>one bit to the right. If 'd' is '0', the result<br>is placed in W. If 'd' is '1', the result is<br>placed back in register 'f' (default).<br>If 'a' is '0', the Access Bank will be<br>selected, overriding the BSR value. If 'a'<br>is '1', then the bank will be selected as<br>per the BSR value (default).<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 22.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                                      |         |   |                       |  |  |

| 14/         | 1                                              | 4                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                      | egister |   |                       |  |  |

| Word        |                                                | 1                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                      |         |   |                       |  |  |

| Cycl        |                                                | 1                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                      |         |   |                       |  |  |

| QU          | ycle Activity:<br>Q1                           | Q2                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Q3                                   | 2       |   | Q4                    |  |  |

|             | Decode                                         | Read<br>register                                                                                                                                      | 'f'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Proce                                | ess     | - | Vrite to<br>stination |  |  |

| <u>Exar</u> | n <u>ple 1:</u><br>Before Instruc<br>REG       | RRNCF<br>tion<br>= 110                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | REG, 1,<br>0111                      | , 0     |   |                       |  |  |

|             | After Instruction<br>REG                       |                                                                                                                                                       | 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1011                                 |         |   |                       |  |  |

| Exar        | <u>nple 2:</u>                                 | RRNCF                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | REG, 0                               | , 0     |   |                       |  |  |

|             | Before Instruc<br>W<br>REG<br>After Instructio | = ?<br>= 110                                                                                                                                          | 1 (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0111                                 |         |   |                       |  |  |

|             | W<br>REG                                       |                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1011<br>0111                         |         |   |                       |  |  |

|                   | • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                     |      |            |  |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|------------|--|--|--|--|

| SETF              | Set f                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                     |      |            |  |  |  |  |

| Syntax:           | SETF f{,                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | a}                  |      |            |  |  |  |  |

| Operands:         | $0 \le f \le 255$                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                     |      |            |  |  |  |  |

|                   | <b>a</b> ∈[0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                     |      |            |  |  |  |  |

| Operation:        | $FFh \rightarrow f$                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                     |      |            |  |  |  |  |

| Status Affected:  | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     |      |            |  |  |  |  |

| Encoding:         | 0110                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0110 100a ffff ffff |      |            |  |  |  |  |

| Description:      | The contents of the specified register<br>are set to FFh.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 22.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                     |      |            |  |  |  |  |

| Words:            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                   |      |            |  |  |  |  |

| Cycles:           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                     |      |            |  |  |  |  |

| Q Cycle Activity: |                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                     |      |            |  |  |  |  |

| Q1                | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Q3                  | _    | Q4         |  |  |  |  |

| Decode            | Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Proce               |      | Write      |  |  |  |  |

|                   | register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Data                | a re | gister 'f' |  |  |  |  |

| Example:          | SETF                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | REG                 | , 1  |            |  |  |  |  |

| REG               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                     |      |            |  |  |  |  |

| After Instructio  | n –                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                     |      |            |  |  |  |  |

REG

= FFh

| Syntax:<br>Dperands:<br>Dperation:<br>Status Affected: | TBLWT (*<br>None<br>if TBLWT<br>(TABLAT)<br>TBLPTR -<br>if TBLWT<br>(TABLAT)<br>(TBLPTR)<br>if TBLWT<br>(TABLAT)<br>(TBLPTR)<br>if TBLWT<br>(TBLPTR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | *,<br>- No Chan<br>*+,<br>→ Holding<br>+ 1 → TE<br>*-,<br>→ Holding        | g Register<br>ge;<br>g Register<br>3LPTR; |                |  |

|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------|----------------|--|

| Dperation:                                             | if TBLWT<br>(TABLAT)<br>TBLPTR -<br>if TBLWT<br>(TABLAT)<br>(TBLPTR)<br>if TBLWT<br>(TABLAT)<br>(TBLPTR)<br>if TBLWT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | → Holding<br>- No Chan<br>*+,<br>→ Holding<br>+ 1 → TE<br>*-,<br>→ Holding | ge;<br>g Register<br>3LPTR;               |                |  |

|                                                        | (TABLAT)<br>TBLPTR -<br>if TBLWT<br>(TABLAT)<br>(TBLPTR)<br>if TBLWT<br>(TABLAT)<br>(TBLPTR)<br>if TBLWT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | → Holding<br>- No Chan<br>*+,<br>→ Holding<br>+ 1 → TE<br>*-,<br>→ Holding | ge;<br>g Register<br>3LPTR;               |                |  |

| Status Affected:                                       | if TBLWT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $-1 \rightarrow TF$                                                        |                                           | ,              |  |

| Status Affected:                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                            | SLPTR;                                    |                |  |

| Status Affected:                                       | (TABLAT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $+1 \rightarrow TE$                                                        | -                                         |                |  |