Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 010110                   |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 21                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 10x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf25j10-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.0 OSCILLATOR CONFIGURATIONS

# 3.1 Oscillator Types

The PIC18F45J10 family of devices can be operated in five different oscillator modes:

- 1. HS High-Speed Crystal/Resonator

- 2. HSPLL High-Speed Crystal/Resonator with Software PLL Control

- 3. EC External Clock with Fosc/4 Output

- 4. ECPLL External Clock with Software PLL Control

- 5. INTRC Internal 31 kHz Oscillator

Four of these are selected by the user by programming the FOSC<2:0> Configuration bits. The fifth mode (INTRC) may be invoked under software control; it can also be configured as the default mode on device Resets.

# 3.2 Crystal Oscillator/Ceramic Resonators (HS Modes)

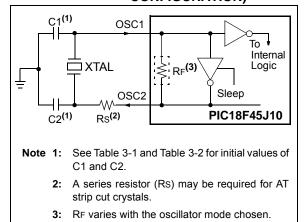

In HS or HSPLL Oscillator modes, a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation. Figure 3-1 shows the pin connections.

The oscillator design requires the use of a parallel cut crystal.

| Note: | Use of a series cut crystal may give a fre- |

|-------|---------------------------------------------|

|       | quency out of the crystal manufacturer's    |

|       | specifications.                             |

# FIGURE 3-1:

#### CRYSTAL/CERAMIC RESONATOR OPERATION (HS OR HSPLL CONFIGURATION)

#### TABLE 3-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS

| Typical Capacitor Values Used: |                     |                |                |  |  |  |

|--------------------------------|---------------------|----------------|----------------|--|--|--|

| Mode                           | Freq.               | OSC1           | OSC2           |  |  |  |

| HS                             | 8.0 MHz<br>16.0 MHz | 27 pF<br>22 pF | 27 pF<br>22 pF |  |  |  |

#### Capacitor values are for design guidance only.

These capacitors were tested with the resonators listed below for basic start-up and operation. **These values are not optimized**.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following Table 3-2 for additional information.

| Resonators Used: |

|------------------|

| 4.0 MHz          |

| 8.0 MHz          |

| 16.0 MHz         |

# 5.2 Master Clear (MCLR)

The MCLR pin provides a method for triggering a hard external Reset of the device. A Reset is generated by holding the pin low. PIC18 extended microcontroller devices have a noise filter in the MCLR Reset path which detects and ignores small pulses.

The  $\overline{\text{MCLR}}$  pin is not driven low by any internal Resets, including the WDT.

# 5.3 Power-on Reset (POR)

A Power-on Reset condition is generated on-chip whenever VDD rises above a certain threshold. This allows the device to start in the initialized state when VDD is adequate for operation.

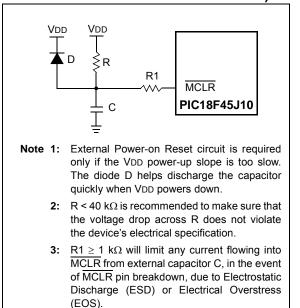

To take advantage of the POR circuitry, tie the  $\overline{\text{MCLR}}$  pin through a resistor (1 k $\Omega$  to 10 k $\Omega$ ) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset delay. A minimum rise rate for VDD is specified (parameter D004). For a slow rise time, see Figure 5-2.

When the device starts normal operation (i.e., exits the Reset condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

Power-on Reset events are captured by the  $\overrightarrow{POR}$  bit (RCON<1>). The state of the bit is set to '0' whenever a Power-on Reset occurs; it does not change for any other Reset event.  $\overrightarrow{POR}$  is not reset to '1' by any hardware event. To capture multiple events, the user manually resets the bit to '1' in software following any Power-on Reset.

# 5.4 Brown-out Reset (BOR) (PIC18F2XJ10/4XJ10 Devices Only)

The PIC18F45J10 family of devices incorporates a simple BOR function when the internal regulator is enabled (ENVREG pin is tied to VDD). Any drop of VDD below VBOR (parameter D005) for greater than time TBOR (parameter 35) will reset the device. A Reset may or may not occur if VDD falls below VBOR for less than TBOR. The chip will remain in Brown-out Reset until VDD rises above VBOR.

Once a BOR has occurred, the Power-up Timer will keep the chip in Reset for TPWRT (parameter 33). If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above VBOR, the Power-up Timer will execute the additional time delay.

#### FIGURE 5-2:

#### EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

# 5.4.1 DETECTING BOR

The BOR bit always resets to '0' on any Brown-out Reset or Power-on Reset event. This makes it difficult to determine if a Brown-out Reset event has occurred just by reading the state of BOR alone. A more reliable method is to simultaneously check the state of both POR and BOR. This assumes that the POR bit is reset to '1' in software immediately after any Power-on Reset event. If BOR is '0' while POR is '1', it can be reliably assumed that a Brown-out Reset event has occurred.

In devices designated with an "LF" part number (such as PIC18LF25J10), Brown-out Reset functionality is disabled. In this case, the BOR bit cannot be used to determine a Brown-out Reset event. The BOR bit is still cleared by a Power-on Reset event.

| Register | Applicable Devices |             | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets,<br>CM Resets | Wake-up via WDT<br>or Interrupt |

|----------|--------------------|-------------|------------------------------------|--------------------------------------------------------------------------------|---------------------------------|

| TOSU     | PIC18F2XJ10        | PIC18F4XJ10 | 0 0000                             | 0 0000                                                                         | 0 uuuu <b>(1)</b>               |

| TOSH     | PIC18F2XJ10        | PIC18F4XJ10 | 0000 0000                          | 0000 0000                                                                      | uuuu uuuu <b>(1)</b>            |

| TOSL     | PIC18F2XJ10        | PIC18F4XJ10 | 0000 0000                          | 0000 0000                                                                      | uuuu uuuu <b>(1)</b>            |

| STKPTR   | PIC18F2XJ10        | PIC18F4XJ10 | 00-0 0000                          | uu-0 0000                                                                      | uu-u uuuu <b>(1)</b>            |

| PCLATU   | PIC18F2XJ10        | PIC18F4XJ10 | 0 0000                             | 0 0000                                                                         | u uuuu                          |

| PCLATH   | PIC18F2XJ10        | PIC18F4XJ10 | 0000 0000                          | 0000 0000                                                                      | սսսս սսսս                       |

| PCL      | PIC18F2XJ10        | PIC18F4XJ10 | 0000 0000                          | 0000 0000                                                                      | PC + 2 <sup>(2)</sup>           |

| TBLPTRU  | PIC18F2XJ10        | PIC18F4XJ10 | 00 0000                            | 00 0000                                                                        | uu uuuu                         |

| TBLPTRH  | PIC18F2XJ10        | PIC18F4XJ10 | 0000 0000                          | 0000 0000                                                                      | սսսս սսսս                       |

| TBLPTRL  | PIC18F2XJ10        | PIC18F4XJ10 | 0000 0000                          | 0000 0000                                                                      | uuuu uuuu                       |

| TABLAT   | PIC18F2XJ10        | PIC18F4XJ10 | 0000 0000                          | 0000 0000                                                                      | uuuu uuuu                       |

| PRODH    | PIC18F2XJ10        | PIC18F4XJ10 | XXXX XXXX                          | uuuu uuuu                                                                      | uuuu uuuu                       |

| PRODL    | PIC18F2XJ10        | PIC18F4XJ10 | xxxx xxxx                          | uuuu uuuu                                                                      | uuuu uuuu                       |

| INTCON   | PIC18F2XJ10        | PIC18F4XJ10 | 0000 000x                          | 0000 000u                                                                      | uuuu uuuu <b>(3)</b>            |

| INTCON2  | PIC18F2XJ10        | PIC18F4XJ10 | 1111 -1-1                          | 1111 -1-1                                                                      | uuuu -u-u <b><sup>(3)</sup></b> |

| INTCON3  | PIC18F2XJ10        | PIC18F4XJ10 | 11-0 0-00                          | 11-0 0-00                                                                      | uu-u u-uu <sup>(3)</sup>        |

| INDF0    | PIC18F2XJ10        | PIC18F4XJ10 | N/A                                | N/A                                                                            | N/A                             |

| POSTINC0 | PIC18F2XJ10        | PIC18F4XJ10 | N/A N/A                            |                                                                                | N/A                             |

| POSTDEC0 | PIC18F2XJ10        | PIC18F4XJ10 | N/A                                | N/A                                                                            | N/A                             |

| PREINC0  | PIC18F2XJ10        | PIC18F4XJ10 | N/A                                | N/A                                                                            | N/A                             |

| PLUSW0   | PIC18F2XJ10        | PIC18F4XJ10 | N/A                                | N/A                                                                            | N/A                             |

| FSR0H    | PIC18F2XJ10        | PIC18F4XJ10 | xxxx                               | uuuu                                                                           | uuuu                            |

| FSR0L    | PIC18F2XJ10        | PIC18F4XJ10 | XXXX XXXX                          | uuuu uuuu                                                                      | uuuu uuuu                       |

| WREG     | PIC18F2XJ10        | PIC18F4XJ10 | XXXX XXXX                          | uuuu uuuu                                                                      | uuuu uuuu                       |

| INDF1    | PIC18F2XJ10        | PIC18F4XJ10 | N/A                                | N/A                                                                            | N/A                             |

| POSTINC1 | PIC18F2XJ10        | PIC18F4XJ10 | N/A                                | N/A                                                                            | N/A                             |

| POSTDEC1 | PIC18F2XJ10        | PIC18F4XJ10 | N/A                                | N/A                                                                            | N/A                             |

| PREINC1  | PIC18F2XJ10        | PIC18F4XJ10 | N/A                                | N/A                                                                            | N/A                             |

| PLUSW1   | PIC18F2XJ10        | PIC18F4XJ10 | N/A                                | N/A                                                                            | N/A                             |

| FSR1H    | PIC18F2XJ10        | PIC18F4XJ10 | xxxx                               | uuuu                                                                           | uuuu                            |

| FSR1L    | PIC18F2XJ10        | PIC18F4XJ10 | xxxx xxxx                          | uuuu uuuu                                                                      | uuuu uuuu                       |

| BSR      | PIC18F2XJ10        | PIC18F4XJ10 | 0000                               | 0000                                                                           | uuuu                            |

| TABLE 5-2: | INITIALIZATION CONDITIONS FOR ALL REGISTERS |

|------------|---------------------------------------------|

|            |                                             |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

3: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

4: See Table 5-1 for Reset value for specific condition.

# 7.5.2 WRITE VERIFY

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

# 7.5.3 UNEXPECTED TERMINATION OF WRITE OPERATION

If a write is terminated by an unplanned event, such as loss of power or an unexpected Reset, the memory location just programmed should be verified and reprogrammed if needed. If the write operation is interrupted by a MCLR Reset or a WDT Time-out Reset during normal operation, the user can check the WRERR bit and rewrite the location(s) as needed.

#### 7.5.4 PROTECTION AGAINST SPURIOUS WRITES

To protect against spurious writes to Flash program memory, the write initiate sequence must also be followed. See **Section 21.0** "**Special Features of the CPU**" for more detail.

# 7.6 Flash Program Operation During Code Protection

See Section 21.6 "Program Verification and Code Protection" for details on code protection of Flash program memory.

| Name    | Bit 7                                               | Bit 6       | Bit 5     | Bit 4         | Bit 3         | Bit 2        | Bit 1         | Bit 0      | Reset<br>Values on<br>page |

|---------|-----------------------------------------------------|-------------|-----------|---------------|---------------|--------------|---------------|------------|----------------------------|

| TBLPTRU | _                                                   |             | bit 21    | Program Me    | emory Table F | Pointer Uppe | r Byte (TBLP  | TR<20:16>) | 47                         |

| TBPLTRH | Program Me                                          | emory Table | Pointer H | ligh Byte (TE | BLPTR<15:8    | >)           |               |            | 47                         |

| TBLPTRL | Program Memory Table Pointer Low Byte (TBLPTR<7:0>) |             |           |               |               |              | 47            |            |                            |

| TABLAT  | Program Me                                          | emory Table | Latch     |               |               |              |               |            | 47                         |

| INTCON  | GIE/GIEH                                            | PEIE/GIEL   | TMR0IE    | INT0IE        | RBIE          | TMR0IF       | <b>INT0IF</b> | RBIF       | 47                         |

| EECON2  | EEPROM Control Register 2 (not a physical register) |             |           |               |               |              | 49            |            |                            |

| EECON1  | _                                                   | _           | _         | FREE          | WRERR         | WREN         | WR            | _          | 49                         |

| IPR2    | OSCFIP                                              | CMIP        | _         | _             | BCL1IP        | _            |               | CCP2IP     | 49                         |

| PIR2    | OSCFIF                                              | CMIF        |           | _             | BCL1IF        |              |               | CCP2IF     | 49                         |

| PIE2    | OSCFIE                                              | CMIE        | _         | _             | BCL1IE        |              |               | CCP2IE     | 49                         |

# TABLE 7-2: REGISTERS ASSOCIATED WITH PROGRAM FLASH MEMORY

Legend: — = unimplemented, read as '0'. Shaded cells are not used during Flash/EEPROM access.

# 9.2 PIR Registers

The PIR registers contain the individual flag bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are three Peripheral Interrupt Request (Flag) registers (PIR1, PIR2, PIR3).

- Note 1: Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE (INTCON<7>).

- 2: User software should ensure the appropriate interrupt flag bits are cleared prior to enabling an interrupt and after servicing that interrupt.

#### REGISTER 9-4: PIR1: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 1

| R/W-0                | R/W-0 | R-0  | R-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|----------------------|-------|------|------|--------|--------|--------|--------|

| PSPIF <sup>(1)</sup> | ADIF  | RCIF | TXIF | SSP1IF | CCP1IF | TMR2IF | TMR1IF |

| bit 7                |       |      |      |        |        |        | bit 0  |

|                      |       |      |      |        |        |        |        |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

|                   |                  |                       |                    |

| bit 7 | PSPIF: Parallel Slave Port Read/Write Interrupt Flag bit <sup>(1)</sup>                                                                             |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = A read or a write operation has taken place (must be cleared in software)</li> <li>0 = No read or write has occurred</li> </ul>        |

| bit 6 | ADIF: A/D Converter Interrupt Flag bit                                                                                                              |

|       | <ul> <li>1 = An A/D conversion completed (must be cleared in software)</li> <li>0 = The A/D conversion is not complete</li> </ul>                   |

| bit 5 | RCIF: EUSART Receive Interrupt Flag bit                                                                                                             |

|       | <ul> <li>1 = The EUSART receive buffer, RCREG, is full (cleared when RCREG is read)</li> <li>0 = The EUSART receive buffer is empty</li> </ul>      |

| bit 4 | TXIF: EUSART Transmit Interrupt Flag bit                                                                                                            |

|       | <ul> <li>1 = The EUSART transmit buffer, TXREG, is empty (cleared when TXREG is written)</li> <li>0 = The EUSART transmit buffer is full</li> </ul> |

| bit 3 | SSP1IF: Master Synchronous Serial Port 1 Interrupt Flag bit                                                                                         |

|       | <ul> <li>1 = The transmission/reception is complete (must be cleared in software)</li> <li>0 = Waiting to transmit/receive</li> </ul>               |

| bit 2 | CCP1IF: ECCP1/CCP1 Interrupt Flag bit                                                                                                               |

|       | <u>Capture mode:</u><br>1 = A TMR1 register capture occurred (must be cleared in software)<br>0 = No TMR1 register capture occurred                 |

|       | Compare mode:                                                                                                                                       |

|       | <ul> <li>1 = A TMR1 register compare match occurred (must be cleared in software)</li> <li>0 = No TMR1 register compare match occurred</li> </ul>   |

|       | <u>PWM mode:</u><br>Unused in this mode.                                                                                                            |

| bit 1 | TMR2IF: TMR2 to PR2 Match Interrupt Flag bit                                                                                                        |

|       | <ul> <li>1 = TMR2 to PR2 match occurred (must be cleared in software)</li> <li>0 = No TMR2 to PR2 match occurred</li> </ul>                         |

| bit 0 | TMR1IF: TMR1 Overflow Interrupt Flag bit                                                                                                            |

|       | <ul> <li>1 = TMR1 register overflowed (must be cleared in software)</li> <li>0 = TMR1 register did not overflow</li> </ul>                          |

|       |                                                                                                                                                     |

Note 1: This bit is not implemented on 28-pin devices and should be read as '0'.

# 9.4 IPR Registers

The IPR registers contain the individual priority bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are three Peripheral Interrupt Priority registers (IPR1, IPR2, IPR3). Using the priority bits requires that the Interrupt Priority Enable (IPEN) bit be set.

#### REGISTER 9-10: IPR1: PERIPHERAL INTERRUPT PRIORITY REGISTER 1

| R/W-1                  | R/W-1                          | R/W-1                             | R/W-1            | R/W-1              | R/W-1          | R/W-1           | R/W-1  |

|------------------------|--------------------------------|-----------------------------------|------------------|--------------------|----------------|-----------------|--------|

| PSPIP <sup>(1)</sup>   | ADIP                           | RCIP                              | TXIP             | SSP1IP             | CCP1IP         | TMR2IP          | TMR1IP |

| bit 7                  |                                |                                   |                  |                    |                |                 | bit 0  |

| Logondu                |                                |                                   |                  |                    |                |                 |        |

| Legend:<br>R = Readabl | e hit                          | W = Writable                      | bit              | U = Unimpler       | nented hit rea | d as '0'        |        |

| -n = Value at          |                                | '1' = Bit is set                  |                  | '0' = Bit is clea  |                | x = Bit is unkr | iown   |

|                        |                                |                                   |                  |                    |                |                 |        |

| bit 7                  | PSPIP: Parall                  | el Slave Port F                   | Read/Write Inte  | errupt Priority bi | t(1)           |                 |        |

|                        | 1 = High prio<br>0 = Low prior | ,                                 |                  |                    |                |                 |        |

| bit 6                  | ADIP: A/D Co                   | onverter Interru                  | pt Priority bit  |                    |                |                 |        |

|                        | 1 = High prio<br>0 = Low prior |                                   |                  |                    |                |                 |        |

| bit 5                  |                                | RT Receive Inte                   | errupt Priority  | bit                |                |                 |        |

|                        | 1 = High prio                  | •                                 |                  |                    |                |                 |        |

|                        | 0 = Low prior                  | •                                 |                  |                    |                |                 |        |

|                        |                                | T Transmit Interrupt Priority bit |                  |                    |                |                 |        |

|                        | 1 = High prio<br>0 = Low prior |                                   |                  |                    |                |                 |        |

| bit 3                  | SSP1IP: Mas                    | ter Synchronou                    | us Serial Port   | 1 Interrupt Priori | ity bit        |                 |        |

|                        | 1 = High prio                  | •                                 |                  |                    |                |                 |        |

|                        | 0 = Low prior                  | -                                 |                  |                    |                |                 |        |

| bit 2                  |                                | CP1/CCP1 Inte                     | rrupt Priority b | ot                 |                |                 |        |

|                        | 1 = High prio<br>0 = Low prior |                                   |                  |                    |                |                 |        |

| bit 1                  | •                              | R2 to PR2 Mate                    | ch Interrupt Pr  | iority bit         |                |                 |        |

|                        | 1 = High prio                  |                                   |                  | -                  |                |                 |        |

|                        | 0 = Low prior                  | •                                 |                  |                    |                |                 |        |

| bit 0                  |                                | R1 Overflow Int                   | errupt Priority  | bit                |                |                 |        |

|                        | 1 = High prio<br>0 = Low prior | •                                 |                  |                    |                |                 |        |

|                        |                                | ity                               |                  |                    |                |                 |        |

# 10.4 PORTC, TRISC and LATC Registers

PORTC is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATC) is also memory mapped. Read-modify-write operations on the LATC register read and write the latched output value for PORTC.

PORTC is multiplexed with several peripheral functions (Table 10-7). The pins have Schmitt Trigger input buffers. RC1 is normally configured by Configuration bit, CCP2MX, as the default peripheral pin of the CCP2 module (default/erased state, CCP2MX = 1).

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. The user should refer to the corresponding peripheral section for additional information.

#### Note: On a Power-on Reset, these pins are configured as digital inputs.

The contents of the TRISC register are affected by peripheral overrides. Reading TRISC always returns the current contents, even though a peripheral device may be overriding one or more of the pins.

#### EXAMPLE 10-4: INITIALIZING PORTC

| CLRF  | PORTC | ; Initialize PORTC by<br>; clearing output      |

|-------|-------|-------------------------------------------------|

| CLRF  | LATC  | ; data latches<br>; Alternate method            |

| CLRF  | LAIC  | ; to clear output                               |

|       |       | ; data latches                                  |

| MOVLW | 0CFh  | ; Value used to<br>; initialize data            |

|       |       | ; direction                                     |

| MOVWF | TRISC | ; Set RC<3:0> as inputs<br>; RC<5:4> as outputs |

|       |       | ; RC<7:6> as inputs                             |

|       |       |                                                 |

## 10.6 PORTE, TRISE and LATE Registers

| Note: | PORTE    | is | only | available | in | 40/44-pin |

|-------|----------|----|------|-----------|----|-----------|

|       | devices. |    |      |           |    |           |

Depending on the particular PIC18F45J10 family device selected, PORTE is implemented in two different ways.

For 40/44-pin devices, PORTE is a 4-bit wide port. Three pins (RE0/RD/AN5, RE1/WR/AN6 and RE2/CS/ AN7) are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers. When selected as analog inputs, these pins will read as '0's.

The corresponding Data Direction register is TRISE. Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., put the contents of the output latch on the selected pin).

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

Note: On a Power-on Reset, RE<2:0> are configured as analog inputs.

The upper four bits of the TRISE register also control the operation of the Parallel Slave Port. Their operation is explained in Register 10-1.

The Data Latch register (LATE) is also memory mapped. Read-modify-write operations on the LATE register read and write the latched output value for PORTE.

| CLRF  | PORTE  | ; Initialize PORTE by<br>; clearing output |

|-------|--------|--------------------------------------------|

|       |        | ; data latches                             |

| CLRF  | LATE   | ; Alternate method                         |

|       |        | ; to clear output                          |

|       |        | ; data latches                             |

| MOVLW | 0Ah    | ; Configure A/D                            |

| MOVWF | ADCON1 | ; for digital inputs                       |

| MOVLW | 03h    | ; Value used to                            |

|       |        | ; initialize data                          |

|       |        | ; direction                                |

| MOVWF | TRISE  | ; Set RE<0> as inputs                      |

|       |        | ; RE<1> as outputs                         |

|       |        | ; RE<2> as inputs                          |

|       |        |                                            |

| Pin        | Function                               | TRIS<br>Setting | I/O | l/O<br>Type                                        | Description                                              |  |

|------------|----------------------------------------|-----------------|-----|----------------------------------------------------|----------------------------------------------------------|--|

| RE0/RD/AN5 | RE0                                    | 0               | 0   | DIG                                                | LATE<0> data output; not affected by analog input.       |  |

|            |                                        | 1               | Ι   | ST                                                 | PORTE<0> data input; disabled when analog input enabled. |  |

|            | RD                                     | 1               | Ι   | TTL                                                | PSP read enable input (PSP enabled).                     |  |

|            | AN5                                    | 1               | Ι   | ANA                                                | A/D Input Channel 5; default input configuration on POR. |  |

| RE1/WR/AN6 | RE1 0 O DIG LATE<1> data output; not a |                 | DIG | LATE<1> data output; not affected by analog input. |                                                          |  |

|            |                                        |                 | Ι   | ST                                                 | PORTE<1> data input; disabled when analog input enabled. |  |

|            | WR                                     | 1               | Ι   | TTL                                                | PSP write enable input (PSP enabled).                    |  |

|            | AN6                                    |                 | Ι   | ANA                                                | A/D Input Channel 6; default input configuration on POR. |  |

| RE2/CS/AN7 | RE2                                    | 0               | 0   | DIG                                                | LATE<2> data output; not affected by analog input.       |  |

|            |                                        | 1               | Ι   | ST                                                 | PORTE<2> data input; disabled when analog input enabled. |  |

|            | CS 1                                   |                 | I   | TTL                                                | PSP write enable input (PSP enabled).                    |  |

|            | AN7                                    | 1               | Ι   | ANA                                                | A/D Input Channel 7; default input configuration on POR. |  |

# TABLE 10-11: PORTE I/O SUMMARY

Legend: DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output; x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

| TABLE 10-12: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTE |

|--------------|--------------------------------------------|

|--------------|--------------------------------------------|

| Name                 | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2                 | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|----------------------|-------|-------|-------|---------|-------|-----------------------|--------|--------|----------------------------|

| PORTE <sup>(1)</sup> |       | _     |       |         |       | RE2                   | RE1    | RE0    | 50                         |

| LATE <sup>(1)</sup>  | —     | —     | —     | -       |       | PORTE Da<br>(Read and |        |        | 50                         |

| TRISE <sup>(1)</sup> | IBF   | OBF   | IBOV  | PSPMODE | _     | TRISE2                | TRISE1 | TRISE0 | 50                         |

| ADCON1               | _     | _     | VCFG1 | VCFG0   | PCFG3 | PCFG2                 | PCFG1  | PCFG0  | 48                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PORTE.

Note 1: These registers are not available in 28-pin devices.

# 14.1 CCP Module Configuration

Each Capture/Compare/PWM module is associated with a control register (generically, CCPxCON) and a data register (CCPRx). The data register, in turn, is comprised of two 8-bit registers: CCPRxL (low byte) and CCPRxH (high byte). All registers are both readable and writable.

#### 14.1.1 CCP MODULES AND TIMER RESOURCES

The CCP modules utilize Timers 1 or 2, depending on the mode selected. Timer1 is available to modules in Capture or Compare modes, while Timer2 is available for modules in PWM mode.

# TABLE 14-1:ECCP/CCP MODE – TIMER<br/>RESOURCE

| ECCP/CCP Mode | Timer Resource |  |  |  |

|---------------|----------------|--|--|--|

| Capture       | Timer1         |  |  |  |

| Compare       | Timer1         |  |  |  |

| PWM           | Timer2         |  |  |  |

Both modules may be active at any given time and may share the same timer resource if they are configured to operate in the same mode (Capture/Compare or PWM) at the same time. The interactions between the two modules are summarized in Figure 14-1 and Figure 14-2. In Timer1 in Asynchronous Counter mode, the capture operation will not work.

#### 14.1.2 CCP2 PIN ASSIGNMENT

The pin assignment for CCP2 (Capture input, Compare and PWM output) can change, based on device configuration. The CCP2MX Configuration bit determines which pin CCP2 is multiplexed to. By default, it is assigned to RC1 (CCP2MX = 1). If the Configuration bit is cleared, CCP2 is multiplexed with RB3.

Changing the pin assignment of CCP2 does not automatically change any requirements for configuring the port pin. Users must always verify that the appropriate TRIS register is configured correctly for CCP2 operation regardless of where it is located.

| CCP1 Mode          | CCP2 Mode          | Interaction                                                                                                                                                                    |

|--------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Capture            | Capture            | Each module uses TMR1 as the time base.                                                                                                                                        |

| Capture            | Compare            | CCP2 can be configured for the Special Event Trigger to reset TMR1. Automatic A/D conversions on the trigger event can also be done. Operation of ECCP1/CCP1 will be affected. |

| Compare            | Capture            | ECCP1/CCP1 can be configured for the Special Event Trigger to reset TMR1. Operation of CCP2 will be affected.                                                                  |

| Compare            | Compare            | Either module can be configured for the Special Event Trigger to reset TMR1. Automatic A/D conversions on the CCP2 trigger event can be done.                                  |

| Capture            | PWM <sup>(1)</sup> | None                                                                                                                                                                           |

| Compare            | PWM <sup>(1)</sup> | None                                                                                                                                                                           |

| PWM <sup>(1)</sup> | Capture            | None                                                                                                                                                                           |

| PWM <sup>(1)</sup> | Compare            | None                                                                                                                                                                           |

| PWM <sup>(1)</sup> | PWM                | Both PWMs will have the same frequency and update rate (TMR2 interrupt).                                                                                                       |

#### TABLE 14-2: INTERACTIONS BETWEEN ECCP1/CCP1 AND CCP2 FOR TIMER RESOURCES

Note 1: Includes standard and Enhanced PWM operation.

The CCPRxH register and a 2-bit internal latch are used to double-buffer the PWM duty cycle. This double-buffering is essential for glitchless PWM operation.

When the CCPRxH and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCPx pin is cleared.

The maximum PWM resolution (bits) for a given PWM frequency is given by the equation:

#### **EQUATION 14-3:**

PWM Resolution (max) =

$$\frac{\log(\frac{Fosc}{FPWM})}{\log(2)}$$

bits

Note: If the PWM duty cycle value is longer than the PWM period, the CCP2 pin will not be cleared.

| <b>TABLE 14-4</b> : | EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 40 MHz |

|---------------------|---------------------------------------------------|

|                     |                                                   |

| PWM Frequency              | 2.44 kHz | 9.77 kHz | 39.06 kHz | 156.25 kHz | 312.50 kHz | 416.67 kHz |

|----------------------------|----------|----------|-----------|------------|------------|------------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1          | 1          | 1          |

| PR2 Value                  | FFh      | FFh      | FFh       | 3Fh        | 1Fh        | 17h        |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8          | 7          | 6.58       |

#### 14.4.3 PWM AUTO-SHUTDOWN (CCP1 ONLY)

The PWM auto-shutdown features of the Enhanced CCP module are also available to CCP1 in 28-pin devices. The operation of this feature is discussed in detail in **Section 15.4.7 "Enhanced PWM Auto-Shutdown"**.

Auto-shutdown features are not available for CCP2.

# 14.4.4 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPRxL register and CCPxCON<5:4> bits.

- 3. Make the CCPx pin an output by clearing the appropriate TRIS bit.

- 4. Set the TMR2 prescale value, then enable Timer2 by writing to T2CON.

- 5. Configure the CCPx module for PWM operation.

In addition to the expanded range of modes available through the CCP1CON register and ECCP1AS register, the ECCP module has an additional register associated with Enhanced PWM operation and auto-shutdown features. It is:

• ECCP1DEL (PWM Dead-Band Delay)

# 15.1 ECCP Outputs and Configuration

The Enhanced CCP module may have up to four PWM outputs, depending on the selected operating mode. These outputs, designated P1A through P1D, are multiplexed with I/O pins on PORTC and PORTD. The outputs that are active depend on the ECCP operating mode selected. The pin assignments are summarized in Table 15-1.

To configure the I/O pins as PWM outputs, the proper PWM mode must be selected by setting the P1M<1:0> and CCP1M<3:0> bits. The appropriate TRISC and TRISD direction bits for the port pins must also be set as outputs.

#### 15.1.1 ECCP MODULES AND TIMER RESOURCES

Like the standard CCP modules, the ECCP module can utilize Timers 1 or 2, depending on the mode selected. Timer1 is available for modules in Capture or Compare modes, while Timer2 is available for modules in PWM mode. Interactions between the standard and Enhanced CCP modules are identical to those described for standard CCP modules. Additional details on timer resources are provided in **Section 14.1.1 "CCP Modules and Timer Resources"**.

# 15.2 Capture and Compare Modes

Except for the operation of the Special Event Trigger discussed below, the Capture and Compare modes of the ECCP module are identical in operation to that of CCP2. These are discussed in detail in Section 14.2 "Capture Mode" and Section 14.3 "Compare Mode". No changes are required when moving between 28-pin and 40/44-pin devices.

#### 15.2.1 SPECIAL EVENT TRIGGER

The Special Event Trigger output of ECCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

# 15.3 Standard PWM Mode

When configured in Single Output mode, the ECCP module functions identically to the standard CCP module in PWM mode, as described in **Section 14.4 "PWM Mode"**. This is also sometimes referred to as "Compatible CCP" mode, as in Table 15-1.

| ECCP Mode      | CCP1CON<br>Configuration | RC2               | RD5      | RD6      | RD7      |

|----------------|--------------------------|-------------------|----------|----------|----------|

|                |                          | All 40/44-pin Dev | vices:   |          |          |

| Compatible CCP | 00xx 11xx                | CCP1              | RD5/PSP5 | RD6/PSP6 | RD7/PSP7 |

| Dual PWM       | 10xx 11xx                | P1A               | P1B      | RD6/PSP6 | RD7/PSP7 |

| Quad PWM       | x1xx 11xx                | P1A               | P1B      | P1C      | P1D      |

#### TABLE 15-1: PIN ASSIGNMENTS FOR VARIOUS ECCP1 MODES

**Legend:** x = Don't care. Shaded cells indicate pin assignments not used by ECCP1 in a given mode.

Note: When setting up single output PWM operations, users are free to use either of the processes described in Section 14.4.4 "Setup for PWM Operation" or Section 15.4.9 "Setup for PWM Operation". The latter is more generic and will work for either single or multi-output PWM.

| R/W-0            | R/W-0                                                                                                                                                   | R-0                                                                                                                                                                                                           | R-0              | R-0                              | R-0             | R0                   | R-0     |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------|-----------------|----------------------|---------|--|

| SMP              | CKE                                                                                                                                                     | D/A                                                                                                                                                                                                           | P <sup>(1)</sup> | S <sup>(1)</sup>                 | R/W             | UA                   | BF      |  |

| bit 7            |                                                                                                                                                         | •                                                                                                                                                                                                             |                  |                                  |                 |                      | bit     |  |

| Legend:          |                                                                                                                                                         |                                                                                                                                                                                                               |                  |                                  |                 |                      |         |  |

| R = Readable bit |                                                                                                                                                         | W = Writable                                                                                                                                                                                                  | bit              | U = Unimpler                     | mented bit, rea | id as '0'            |         |  |

| -n = Value       | at POR                                                                                                                                                  | '1' = Bit is set                                                                                                                                                                                              | :                | '0' = Bit is cle                 | ared            | x = Bit is unkno     | own     |  |

| bit 7            | SMP: Slew R                                                                                                                                             | ate Control bit                                                                                                                                                                                               |                  |                                  |                 |                      |         |  |

|                  |                                                                                                                                                         | e control disabl                                                                                                                                                                                              |                  | rd Speed mode<br>beed mode (400  |                 | 1 MHz)               |         |  |

| bit 6            | CKE: SMBus<br>In Master or S<br>1 = Enable SI                                                                                                           | Select bit                                                                                                                                                                                                    | nputs            | , ,                              |                 |                      |         |  |

| bit 5            | <b>D/A:</b> Data/Ad<br>In Master mo<br>Reserved.                                                                                                        | <u>de:</u>                                                                                                                                                                                                    |                  |                                  |                 |                      |         |  |

|                  |                                                                                                                                                         | that the last by                                                                                                                                                                                              |                  | transmitted wa<br>transmitted wa |                 |                      |         |  |

| bit 4            |                                                                                                                                                         | that a Stop bit<br>/as not detecte                                                                                                                                                                            |                  | ected last                       |                 |                      |         |  |

| bit 3            | <ul> <li>Start bit<sup>(1)</sup></li> <li>1 = Indicates that a Start bit has been detected last</li> <li>0 = Start bit was not detected last</li> </ul> |                                                                                                                                                                                                               |                  |                                  |                 |                      |         |  |

| bit 2            | In Slave mode<br>1 = Read<br>0 = Write<br>In Master mod<br>1 = Transmit                                                                                 | de: <sup>(3)</sup>                                                                                                                                                                                            |                  | e only)                          |                 |                      |         |  |

| bit 1            | 1 = Indicates                                                                                                                                           | <ul> <li>UA: Update Address bit (10-Bit Slave mode only)</li> <li>1 = Indicates that the user needs to update the address in the SSPxADD register</li> <li>0 = Address does not need to be updated</li> </ul> |                  |                                  |                 |                      |         |  |

| bit 0            | <b>BF:</b> Buffer Fu<br>In <u>Transmit m</u><br>1 = SSPxBUF<br>0 = SSPxBUF<br>In <u>Receive m</u><br>1 = SSPxBUF                                        | III Status bit<br>i <u>ode:</u><br>- is full<br>- is empty<br>ode:<br>- is full (does n                                                                                                                       | ot include the   | ACK and Stop t                   |                 |                      |         |  |

| Note 1:<br>2:    | 0 = SSPxBUF<br>This bit is cleared<br>This bit holds the<br>address match to                                                                            | I on Reset and $R/\overline{W}$ bit inform                                                                                                                                                                    | when SSPEN       | g the last addres                |                 | bit is only valid fr | rom the |  |

3: ORing this bit with SEN, RSEN, PEN, RCEN or ACKEN will indicate if the MSSP is in Active mode.

# **19.2** Comparator Operation

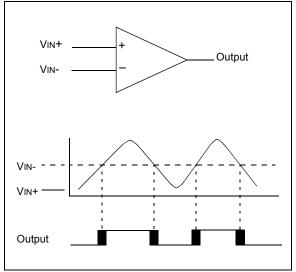

A single comparator is shown in Figure 19-2, along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input, VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input, VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 19-2 represent the uncertainty due to input offsets and response time.

# 19.3 Comparator Reference

Depending on the comparator operating mode, either an external or internal voltage reference may be used. The analog signal present at VIN- is compared to the signal at VIN+ and the digital output of the comparator is adjusted accordingly (Figure 19-2).

#### 19.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between Vss and VDD and can be applied to either pin of the comparator(s).

#### 19.3.2 INTERNAL REFERENCE SIGNAL

The comparator module also allows the selection of an internally generated voltage reference from the comparator voltage reference module. This module is described in more detail in **Section 20.0 "Comparator Voltage Reference Module"**.

The internal reference is only available in the mode where four inputs are multiplexed to two comparators (CM<2:0> = 110). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

# 19.4 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output has a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs. Otherwise, the maximum delay of the comparators should be used (see Section 24.0 "Electrical Characteristics").

# **19.5 Comparator Outputs**

The comparator outputs are read through the CMCON register. These bits are read-only. The comparator outputs may also be directly output to the RB5 and RA5 I/O pins. When enabled, multiplexors in the output path of the RB5 and RA5 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 19-3 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/ disable for the RB5 and RA5 pins while in this mode.

The polarity of the comparator outputs can be changed using the C2INV and C1INV bits (CMCON<5:4>).

- Note 1: When reading the PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- 2: Analog levels on any pin defined as a digital input may cause the input buffer to consume more current than is specified.

| ANDWF                        | AND W w                                                                                                                                                                             | ith f                                                                                                                                                                                                                                                                                                                                                                                                                           |                      | BC                                                                       |                                     | Branch if                                                                                                                                                                                                                                                                                                          | Carry                      |                 |  |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------|--|

| Syntax:                      | ANDWF f {,d {,a}}                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                 |                      | Synta                                                                    | Syntax:                             |                                                                                                                                                                                                                                                                                                                    | BC n                       |                 |  |

| Operands:                    | $0 \leq f \leq 255$                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                 | Operands:            |                                                                          | $-128 \le n \le 127$                |                                                                                                                                                                                                                                                                                                                    |                            |                 |  |

| d ∈ [0,1]<br>a ∈ [0,1]       |                                                                                                                                                                                     | Operation:                                                                                                                                                                                                                                                                                                                                                                                                                      |                      | if Carry bit is '1',<br>(PC) + 2 + 2n $\rightarrow$ PC                   |                                     |                                                                                                                                                                                                                                                                                                                    |                            |                 |  |

| Operation:                   | (W) .AND. (                                                                                                                                                                         | (f) $\rightarrow$ dest                                                                                                                                                                                                                                                                                                                                                                                                          |                      | Statu                                                                    | s Affected:                         | None                                                                                                                                                                                                                                                                                                               |                            |                 |  |

| Status Affected:             | N, Z                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                 |                      | Enco                                                                     | ding:                               | 1110                                                                                                                                                                                                                                                                                                               | 0010 nni                   | nn nnnn         |  |

| Encoding:                    | 0001 01da ffff ffff                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                 | ff ffff              | Description:<br>Words:<br>Cycles:<br>Q Cycle Activity:<br>If Jump:<br>Q1 |                                     | If the Carry bit is '1', then the program<br>will branch.<br>The 2's complement number, '2n', is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>two-cycle instruction.<br>1<br>1(2)<br>Q2 Q3 Q4 |                            |                 |  |

| Description:                 | register 'f. I<br>in W. If 'd' is<br>in register 'f<br>If 'a' is '0', t<br>If 'a' is '1', t<br>GPR bank<br>If 'a' is '0' a<br>set is enabl<br>in Indexed<br>mode when<br>Section 22 | ents of W are ANDed with<br>f'. If 'd' is '0', the result is stored<br>i' is '1', the result is stored back<br>er 'f' (default).<br>i', the Access Bank is selected.<br>i', the BSR is used to select the<br>hk (default).<br>i' and the extended instruction<br>abled, this instruction operates<br>ed Literal Offset Addressing<br>henever $f \le 95$ (5Fh). See<br>22.2.3 "Byte-Oriented and<br>hted Instructions in Indexed |                      |                                                                          |                                     |                                                                                                                                                                                                                                                                                                                    |                            |                 |  |

|                              |                                                                                                                                                                                     | set Mode" for                                                                                                                                                                                                                                                                                                                                                                                                                   | details.             |                                                                          | Decode                              | Read literal                                                                                                                                                                                                                                                                                                       | Process                    | Write to PC     |  |

| Words:                       | 1                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                 |                      |                                                                          |                                     | 'n'                                                                                                                                                                                                                                                                                                                | Data                       |                 |  |

| Cycles:                      | 1                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                 |                      |                                                                          | No<br>operation                     | No<br>operation                                                                                                                                                                                                                                                                                                    | No<br>operation            | No<br>operation |  |

| Q Cycle Activity:            |                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                 |                      | lf No                                                                    | Jump:                               | operation                                                                                                                                                                                                                                                                                                          | operation                  | operation       |  |

| Q1                           | Q2                                                                                                                                                                                  | Q3                                                                                                                                                                                                                                                                                                                                                                                                                              | Q4                   |                                                                          | Q1                                  | Q2                                                                                                                                                                                                                                                                                                                 | Q3                         | Q4              |  |

| Decode                       | Read<br>register 'f'                                                                                                                                                                | Process<br>Data                                                                                                                                                                                                                                                                                                                                                                                                                 | Write to destination |                                                                          | Decode                              | Read literal<br>'n'                                                                                                                                                                                                                                                                                                | Process<br>Data            | No<br>operation |  |