Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 40MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 21                                                                           |

| Program Memory Size        | 32KB (16K x 16)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                    |

| Data Converters            | A/D 10x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 28-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf25j10t-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 5-2: | INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |             |                                                                                |                                 |           |  |  |  |  |

|------------|---------------------------------------------------------|-------------|--------------------------------------------------------------------------------|---------------------------------|-----------|--|--|--|--|

| Register   | Applicable Devices Power-on Reset,<br>Brown-out Reset   |             | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets,<br>CM Resets | Wake-up via WDT<br>or Interrupt |           |  |  |  |  |

| TRISE      | PIC18F2XJ10 P                                           | IC18F4XJ10  | 0000 -111                                                                      | 1111 -111                       | uuuu -uuu |  |  |  |  |

| TRISD      | PIC18F2XJ10 P                                           | IC18F4XJ10  | 1111 1111                                                                      | 1111 1111                       | uuuu uuuu |  |  |  |  |

| TRISC      | PIC18F2XJ10 P                                           | PIC18F4XJ10 | 1111 1111                                                                      | 1111 1111                       | սսսս սսսս |  |  |  |  |

| TRISB      | PIC18F2XJ10 P                                           | PIC18F4XJ10 | 1111 1111                                                                      | 1111 1111                       | սսսս սսսս |  |  |  |  |

| TRISA      | PIC18F2XJ10 P                                           | PIC18F4XJ10 | 1- 1111                                                                        | 1- 1111                         | u- uuuu   |  |  |  |  |

| SSP2BUF    | PIC18F2XJ10 P                                           | PIC18F4XJ10 | xxxx xxxx                                                                      | սսսս սսսս                       | uuuu uuuu |  |  |  |  |

| LATE       | PIC18F2XJ10 P                                           | PIC18F4XJ10 | xxx                                                                            | uuu                             | uuu       |  |  |  |  |

| LATD       | PIC18F2XJ10 P                                           | PIC18F4XJ10 | XXXX XXXX                                                                      | uuuu uuuu                       | uuuu uuuu |  |  |  |  |

| LATC       | PIC18F2XJ10 P                                           | PIC18F4XJ10 | XXXX XXXX                                                                      | uuuu uuuu                       | uuuu uuuu |  |  |  |  |

| LATB       | PIC18F2XJ10 P                                           | PIC18F4XJ10 | xxxx xxxx                                                                      | սսսս սսսս                       | uuuu uuuu |  |  |  |  |

| LATA       | PIC18F2XJ10 P                                           | PIC18F4XJ10 | xx xxxx                                                                        | uu uuuu                         | uu uuuu   |  |  |  |  |

| SSP2ADD    | PIC18F2XJ10 P                                           | PIC18F4XJ10 | 0000 0000                                                                      | 0000 0000                       | uuuu uuuu |  |  |  |  |

| SSP2STAT   | PIC18F2XJ10 P                                           | PIC18F4XJ10 | 0000 0000                                                                      | 0000 0000                       | սսսս սսսս |  |  |  |  |

| SSP2CON1   | PIC18F2XJ10 P                                           | PIC18F4XJ10 | 0000 0000                                                                      | 0000 0000                       | uuuu uuuu |  |  |  |  |

| SSP2CON2   | PIC18F2XJ10 P                                           | PIC18F4XJ10 | 0000 0000                                                                      | 0000 0000                       | սսսս սսսս |  |  |  |  |

| PORTE      | PIC18F2XJ10 P                                           | PIC18F4XJ10 | xxx                                                                            | uuu                             | uuu       |  |  |  |  |

| PORTD      | PIC18F2XJ10 P                                           | PIC18F4XJ10 | xxxx xxxx                                                                      | սսսս սսսս                       | սսսս սսսս |  |  |  |  |

| PORTC      | PIC18F2XJ10 P                                           | PIC18F4XJ10 | xxxx xxxx                                                                      | սսսս սսսս                       | սսսս սսսս |  |  |  |  |

| PORTB      | PIC18F2XJ10 P                                           | PIC18F4XJ10 | xxxx xxxx                                                                      | սսսս սսսս                       | սսսս սսսս |  |  |  |  |

| PORTA      | PIC18F2XJ10 P                                           | PIC18F4XJ10 | 0- 0000                                                                        | 0- 0000                         | u- uuuu   |  |  |  |  |

## TABLE 5-2: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

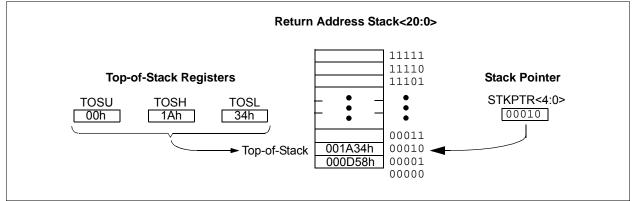

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

3: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

4: See Table 5-1 for Reset value for specific condition.

## 6.1.3 PROGRAM COUNTER

The Program Counter (PC) specifies the address of the instruction to fetch for execution. The PC is 21 bits wide and is contained in three separate 8-bit registers. The low byte, known as the PCL register, is both readable and writable. The high byte, or PCH register, contains the PC<15:8> bits; it is not directly readable or writable. Updates to the PCH register are performed through the PCLATH register. The upper byte is called PCU. This register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCH register. Updates to the PCU register are performed through the PCLATH register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCU register are performed through the PCLATU register.

The contents of PCLATH and PCLATU are transferred to the program counter by any operation that writes PCL. Similarly, the upper two bytes of the program counter are transferred to PCLATH and PCLATU by an operation that reads PCL. This is useful for computed offsets to the PC (see **Section 6.1.6.1 "Computed GOTO"**).

The PC addresses bytes in the program memory. To prevent the PC from becoming misaligned with word instructions, the Least Significant bit of PCL is fixed to a value of '0'. The PC increments by 2 to address sequential instructions in the program memory.

The CALL, RCALL, GOTO and program branch instructions write to the program counter directly. For these instructions, the contents of PCLATH and PCLATU are not transferred to the program counter.

### 6.1.4 RETURN ADDRESS STACK

The return address stack allows any combination of up to 31 program calls and interrupts to occur. The PC is pushed onto the stack when a CALL or RCALL instruction is executed or an interrupt is Acknowledged. The PC value is pulled off the stack on a RETURN, RETLW or RETFIE instruction. PCLATU and PCLATH are not affected by any of the RETURN or CALL instructions.

The stack operates as a 31-word by 21-bit RAM and a 5-bit Stack Pointer, STKPTR. The stack space is not part of either program or data space. The Stack Pointer is readable and writable and the address on the top of the stack is readable and writable through the top-of-stack Special Function Registers. Data can also be pushed to, or popped from the stack, using these registers.

A CALL type instruction causes a push onto the stack; the Stack Pointer is first incremented and the location pointed to by the Stack Pointer is written with the contents of the PC (already pointing to the instruction following the CALL). A RETURN type instruction causes a pop from the stack; the contents of the location pointed to by the STKPTR are transferred to the PC and then the Stack Pointer is decremented.

The Stack Pointer is initialized to '00000' after all Resets. There is no RAM associated with the location corresponding to a Stack Pointer value of '00000'; this is only a Reset value. Status bits indicate if the stack is full or has overflowed or has underflowed.

### 6.1.4.1 Top-of-Stack Access

Only the top of the return address stack (TOS) is readable and writable. A set of three registers, TOSU:TOSH:TOSL, hold the contents of the stack location pointed to by the STKPTR register (Figure 6-3). This allows users to implement a software stack if necessary. After a CALL, RCALL or interrupt, the software can read the pushed value by reading the TOSU:TOSH:TOSL registers. These values can be placed on a user-defined software stack. At return time, the software can return these values to TOSU:TOSH:TOSL and do a return.

The user must disable the global interrupt enable bits while accessing the stack to prevent inadvertent stack corruption.

## FIGURE 6-3: RETURN ADDRESS STACK AND ASSOCIATED REGISTERS

The PLUSW register can be used to implement a form of Indexed Addressing in the data memory space. By manipulating the value in the W register, users can reach addresses that are fixed offsets from pointer addresses. In some applications, this can be used to implement some powerful program control structure, such as software stacks, inside of data memory.

### 6.4.3.3 Operations by FSRs on FSRs

Indirect Addressing operations that target other FSRs or virtual registers represent special cases. For example, using an FSR to point to one of the virtual registers will not result in successful operations. As a specific case, assume that FSR0H:FSR0L contains FE7h, the address of INDF1. Attempts to read the value of the INDF1 using INDF0 as an operand will return 00h. Attempts to write to INDF1 using INDF0 as the operand will result in a NOP.

On the other hand, using the virtual registers to write to an FSR pair may not occur as planned. In these cases, the value will be written to the FSR pair but without any incrementing or decrementing. Thus, writing to INDF2 or POSTDEC2 will write the same value to the FSR2H:FSR2L.

Since the FSRs are physical registers mapped in the SFR space, they can be manipulated through all direct operations. Users should proceed cautiously when working on these registers, particularly if their code uses indirect addressing.

Similarly, operations by Indirect Addressing are generally permitted on all other SFRs. Users should exercise the appropriate caution that they do not inadvertently change settings that might affect the operation of the device.

# 6.5 Data Memory and the Extended Instruction Set

Enabling the PIC18 extended instruction set (XINST Configuration bit = 1) significantly changes certain aspects of data memory and its addressing. Specifically, the use of the Access Bank for many of the core PIC18 instructions is different; this is due to the introduction of a new addressing mode for the data memory space.

What does not change is just as important. The size of the data memory space is unchanged, as well as its linear addressing. The SFR map remains the same. Core PIC18 instructions can still operate in both Direct and Indirect Addressing mode; inherent and literal instructions do not change at all. Indirect addressing with FSR0 and FSR1 also remains unchanged.

### 6.5.1 INDEXED ADDRESSING WITH LITERAL OFFSET

Enabling the PIC18 extended instruction set changes the behavior of Indirect Addressing using the FSR2 register pair within Access RAM. Under the proper conditions, instructions that use the Access Bank – that is, most bit-oriented and byte-oriented instructions – can invoke a form of Indexed Addressing using an offset specified in the instruction. This special addressing mode is known as Indexed Addressing with Literal Offset, or Indexed Literal Offset mode.

When using the extended instruction set, this addressing mode requires the following:

- The use of the Access Bank is forced ('a' = 0) and

- The file address argument is less than or equal to 5Fh.

Under these conditions, the file address of the instruction is not interpreted as the lower byte of an address (used with the BSR in direct addressing), or as an 8-bit address in the Access Bank. Instead, the value is interpreted as an offset value to an Address Pointer, specified by FSR2. The offset and the contents of FSR2 are added to obtain the target address of the operation.

## 6.5.2 INSTRUCTIONS AFFECTED BY INDEXED LITERAL OFFSET MODE

Any of the core PIC18 instructions that can use Direct Addressing are potentially affected by the Indexed Literal Offset Addressing mode. This includes all byte-oriented and bit-oriented instructions, or almost one-half of the standard PIC18 instruction set. Instructions that only use Inherent or Literal Addressing modes are unaffected.

Additionally, byte-oriented and bit-oriented instructions are not affected if they do not use the Access Bank (Access RAM bit is '1'), or include a file address of 60h or above. Instructions meeting these criteria will continue to execute as before. A comparison of the different possible addressing modes when the extended instruction set is enabled in shown in Figure 6-9.

Those who desire to use byte-oriented or bit-oriented instructions in the Indexed Literal Offset mode should note the changes to assembler syntax for this mode. This is described in more detail in **Section 22.2.1** "Extended Instruction Syntax".

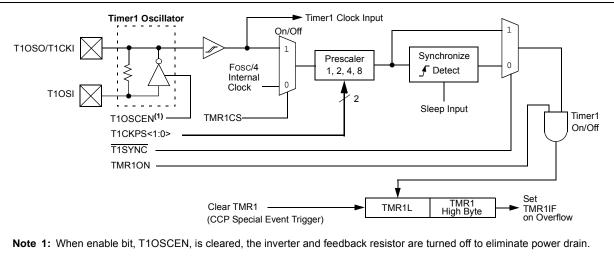

## 12.1 Timer1 Operation

Timer1 can operate in one of these modes:

- Timer

- Synchronous Counter

- Asynchronous Counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>). When TMR1CS is cleared (= 0), Timer1 increments on every internal instruction cycle (FOSC/4). When the bit is set, Timer1 increments on every rising edge of the Timer1 external clock input or the Timer1 oscillator, if enabled. When Timer1 is enabled, the RC1/T1OSI and RC0/T1OSO/T1CKI pins become inputs. This means the values of TRISC<1:0> are ignored and the pins are read as '0'.

### FIGURE 12-1: TIMER1 BLOCK DIAGRAM

## 15.4.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L register contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The PWM duty cycle is calculated by the following equation:

### EQUATION 15-2:

PWM Duty Cycle = (CCPR1L:CCP1CON<5:4>) • Tosc • (TMR2 Prescale Value)

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not copied into CCPR1H until a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double-buffer the PWM duty cycle. This double-buffering is essential for glitchless PWM operation. When the CCPR1H and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock or two bits of the TMR2 prescaler, the CCP1 pin is cleared. The maximum PWM resolution (bits) for a given PWM frequency is given by the following equation:

### **EQUATION 15-3:**

|                        | $\log\left(\frac{FOSC}{FPWM}\right)$ bits |

|------------------------|-------------------------------------------|

| PWM Resolution (max) = | log(2)                                    |

Note: If the PWM duty cycle value is longer than the PWM period, the CCP1 pin will not be cleared.

### 15.4.3 PWM OUTPUT CONFIGURATIONS

The P1M<1:0> bits in the CCP1CON register allow one of four configurations:

- Single Output

- · Half-Bridge Output

- Full-Bridge Output, Forward mode

- Full-Bridge Output, Reverse mode

The Single Output mode is the standard PWM mode discussed in **Section 15.4 "Enhanced PWM Mode"**. The Half-Bridge and Full-Bridge Output modes are covered in detail in the sections that follow.

The general relationship of the outputs in all configurations is summarized in Figure 15-2.

| PWM Frequency              | 2.44 kHz | 9.77 kHz | 39.06 kHz | 156.25 kHz | 312.50 kHz | 416.67 kHz |

|----------------------------|----------|----------|-----------|------------|------------|------------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1          | 1          | 1          |

| PR2 Value                  | FFh      | FFh      | FFh       | 3Fh        | 1Fh        | 17h        |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8          | 7          | 6.58       |

#### TABLE 15-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 40 MHz

| Name                 | Bit 7                | Bit 6                       | Bit 5                                         | Bit 4                                             | Bit 3     | Bit 2     | Bit 1                 | Bit 0  | Reset<br>Values<br>on Page |

|----------------------|----------------------|-----------------------------|-----------------------------------------------|---------------------------------------------------|-----------|-----------|-----------------------|--------|----------------------------|

| INTCON               | GIE/GIEH             | PEIE/GIEL                   | TMR0IE                                        | INT0IE                                            | RBIE      | TMR0IF    | <b>INT0IF</b>         | RBIF   | 47                         |

| PIR1                 | PSPIF <sup>(1)</sup> | ADIF                        | RCIF                                          | TXIF                                              | SSP1IF    | CCP1IF    | TMR2IF                | TMR1IF | 49                         |

| PIE1                 | PSPIE <sup>(1)</sup> | ADIE                        | RCIE                                          | TXIE                                              | SSP1IE    | CCP1IE    | TMR2IE                | TMR1IE | 49                         |

| IPR1                 | PSPIP <sup>(1)</sup> | ADIP                        | RCIP                                          | TXIP                                              | SSP1IP    | CCP1IP    | TMR2IP                | TMR1IP | 49                         |

| PIR2                 | OSCFIF               | CMIF                        | _                                             | _                                                 | BCL1IF    | _         | _                     | CCP2IF | 49                         |

| PIE2                 | OSCFIE               | CMIE                        | _                                             | _                                                 | BCL1IE    | _         |                       | CCP2IE | 49                         |

| IPR2                 | OSCFIP               | CMIP                        | _                                             | _                                                 | BCL1IP    | _         | _                     | CCP2IP | 49                         |

| PIR3                 | SSP2IF               | BCL2IF                      | _                                             | _                                                 | _         | _         | _                     | _      | 49                         |

| PIE3                 | SSP2IE               | BCL2IE                      | —                                             | _                                                 | —         | _         | —                     | _      | 49                         |

| IPR3                 | SSP2IP               | BCL2IP                      | _                                             | _                                                 | _         | _         | _                     | _      | 49                         |

| TRISC                | TRISC7               | TRISC6                      | TRISC5                                        | TRISC4                                            | TRISC3    | TRISC2    | TRISC1                | TRISC0 | 50                         |

| TRISD <sup>(1)</sup> | TRISD7               | TRISD6                      | TRISD5                                        | TRISD4                                            | TRISD3    | TRISD2    | TRISD1                | TRISD0 | 50                         |

| SSP1BUF              | MSSP1 Re             | eceive Buffer               | r/Transmit Re                                 | gister                                            |           |           |                       |        | 48                         |

| SSP1ADD              |                      |                             | ster (I <sup>2</sup> C™ Sla<br>load Register  |                                                   | mode).    |           |                       |        | 48                         |

| SSP1CON1             | WCOL                 | SSPOV                       | SSPEN                                         | CKP                                               | SSPM3     | SSPM2     | SSPM1                 | SSPM0  | 48                         |

| SSP1CON2             | GCEN                 | ACKSTAT                     | ACKDT                                         | ACKEN                                             | RCEN      | PEN       | RSEN                  | SEN    | 48                         |

|                      | GCEN                 | ACKSTAT                     | ADMSK5(2)                                     | ADMSK4 <sup>(2)</sup>                             | ADMSK3(2) | ADMSK2(2) | ADMSK1(2)             | SEN    | 48                         |

| SSP1STAT             | SMP                  | CKE                         | D/Ā                                           | Р                                                 | S         | R/W       | UA                    | BF     | 48                         |

| SSP2BUF              | MSSP2 Re             | eceive Buffer               | /Transmit Re                                  | gister                                            |           |           |                       |        | 50                         |

| SSP2ADD              | MSSP2 Ac<br>MSSP2 Ba | ldress Regis<br>aud Rate Re | ster (I <sup>2</sup> C Slave<br>load Register | e mode).<br><sup>.</sup> (I <sup>2</sup> C Master | mode).    |           |                       |        | 50                         |

| SSP2CON1             | WCOL                 | SSPOV                       | SSPEN                                         | CKP                                               | SSPM3     | SSPM2     | SSPM1                 | SSPM0  | 50                         |

| SSP2CON2             | GCEN                 | ACKSTAT                     | ACKDT                                         | ACKEN                                             | RCEN      | PEN       | RSEN                  | SEN    | 50                         |

|                      | GCEN                 | ACKSTAT                     | ADMSK5 <sup>(2)</sup>                         | ADMSK4 <sup>(2)</sup>                             | ADMSK3(2) | ADMSK2(2) | ADMSK1 <sup>(2)</sup> | SEN    | 48                         |

| SSP2STAT             | SMP                  | CKE                         | D/Ā                                           | Р                                                 | S         | R/W       | UA                    | BF     | 50                         |

## TABLE 16-4: REGISTERS ASSOCIATED WITH I<sup>2</sup>C<sup>™</sup> OPERATION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the MSSP module in  $I^2C^{TM}$  mode.

Note 1: These registers and/or bits are not implemented on 28-pin devices and should be read as '0'.

2: Alternate names and definitions for these bits when the MSSP module is operating in I<sup>2</sup>C Slave mode. See Section 16.4.3.2 "Address Masking" for details.

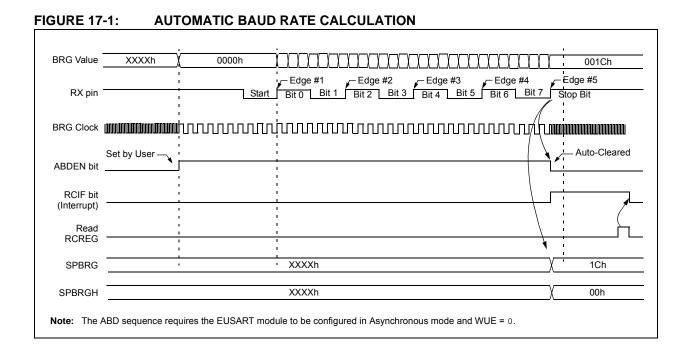

### EXAMPLE 17-1: CALCULATING BAUD RATE ERROR

|   | For a device with FOSC | of 1 | 6 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit BRG: |

|---|------------------------|------|-----------------------------------------------------------------|

|   | Desired Baud Rate      | =    | Fosc/(64 ([SPBRGH:SPBRG] + 1))                                  |

|   | Solving for SPBRGH:S   | SPBF | RG:                                                             |

|   | Х                      | =    | ((FOSC/Desired Baud Rate)/64) – 1                               |

|   |                        | =    | ((1600000/9600)/64) - 1                                         |

|   |                        | =    | [25.042] = 25                                                   |

|   | Calculated Baud Rate   | =    | 1600000/(64 (25 + 1))                                           |

|   |                        | =    | 9615                                                            |

|   | Error                  | =    | (Calculated Baud Rate - Desired Baud Rate)/Desired Baud Rate    |

|   |                        | =    | (9615 - 9600)/9600 = 0.16%                                      |

| I |                        |      |                                                                 |

### TABLE 17-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Name    | Bit 7                                                | Bit 6 | Bit 5 | Bit 4                    | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset Values<br>on page |  |

|---------|------------------------------------------------------|-------|-------|--------------------------|-------|-------|-------|-------|-------------------------|--|

| TXSTA   | CSRC                                                 | TX9   | TXEN  | SYNC                     | SENDB | BRGH  | TRMT  | TX9D  | 49                      |  |

| RCSTA   | SPEN                                                 | RX9   | SREN  | CREN                     | ADDEN | FERR  | OERR  | RX9D  | 49                      |  |

| BAUDCON | ABDOVF                                               | RCIDL | _     | - SCKP BRG16 - WUE ABDEN |       |       |       |       | 49                      |  |

| SPBRGH  | SPBRGH EUSART Baud Rate Generator Register High Byte |       |       |                          |       |       |       |       |                         |  |

| SPBRG   | SPBRG EUSART Baud Rate Generator Register Low Byte   |       |       |                          |       |       |       |       |                         |  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the BRG.

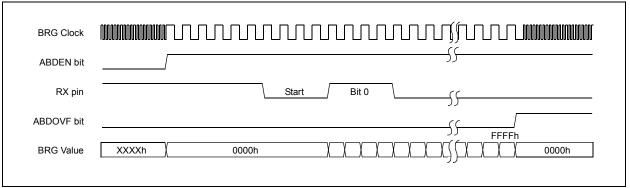

### FIGURE 17-2: BRG OVERFLOW SEQUENCE

### REGISTER 18-2: ADCON1: A/D CONTROL REGISTER 1

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | VCFG1 | VCFG0 | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

| bit 5 | VCFG1: Voltage Reference Configuration bit (VREF- source) |

|-------|-----------------------------------------------------------|

|       | 1 = VREF- (AN2)                                           |

|       | 0 = Vss                                                   |

| bit 4 | VCFG0: Voltage Reference Configuration bit (VREF+ source) |

|       | 1 = VREF+(AN3)                                            |

|       |                                                           |

bit 3-0 **PCFG<3:0>:** A/D Port Configuration Control bits:

| PCFG<3:0> | AN12 | AN11 | AN10 | AN9 | AN8 | AN7 <sup>(1)</sup> | AN6 <sup>(1)</sup> | AN5 <sup>(1)</sup> | AN4 | AN3 | AN2 | AN1 | ANO |

|-----------|------|------|------|-----|-----|--------------------|--------------------|--------------------|-----|-----|-----|-----|-----|

| 0000      | Α    | Α    | Α    | Α   | Α   | Α                  | Α                  | Α                  | Α   | Α   | Α   | Α   | Α   |

| 0001      | А    | А    | Α    | Α   | Α   | Α                  | Α                  | Α                  | А   | Α   | Α   | Α   | Α   |

| 0010      | А    | А    | Α    | Α   | Α   | Α                  | Α                  | Α                  | А   | Α   | Α   | Α   | Α   |

| 0011      | D    | А    | Α    | Α   | Α   | Α                  | Α                  | Α                  | А   | Α   | Α   | Α   | Α   |

| 0100      | D    | D    | Α    | Α   | Α   | Α                  | Α                  | Α                  | Α   | Α   | Α   | Α   | Α   |

| 0101      | D    | D    | D    | Α   | Α   | Α                  | Α                  | Α                  | А   | Α   | Α   | Α   | Α   |

| 0110      | D    | D    | D    | D   | Α   | Α                  | Α                  | Α                  | А   | Α   | Α   | Α   | Α   |

| 0111      | D    | D    | D    | D   | D   | Α                  | Α                  | Α                  | А   | Α   | Α   | Α   | Α   |

| 1000      | D    | D    | D    | D   | D   | D                  | Α                  | Α                  | А   | Α   | Α   | Α   | Α   |

| 1001      | D    | D    | D    | D   | D   | D                  | D                  | Α                  | А   | Α   | Α   | Α   | Α   |

| 1010      | D    | D    | D    | D   | D   | D                  | D                  | D                  | Α   | Α   | Α   | Α   | Α   |

| 1011      | D    | D    | D    | D   | D   | D                  | D                  | D                  | D   | Α   | Α   | Α   | Α   |

| 1100      | D    | D    | D    | D   | D   | D                  | D                  | D                  | D   | D   | Α   | Α   | Α   |

| 1101      | D    | D    | D    | D   | D   | D                  | D                  | D                  | D   | D   | D   | Α   | Α   |

| 1110      | D    | D    | D    | D   | D   | D                  | D                  | D                  | D   | D   | D   | D   | Α   |

| 1111      | D    | D    | D    | D   | D   | D                  | D                  | D                  | D   | D   | D   | D   | D   |

|           |      |      |      |     |     |                    |                    |                    |     |     |     |     |     |

A = Analog input

D = Digital I/O

Note 1: AN5 through AN7 are available only on 40/44-pin devices.

NOTES:

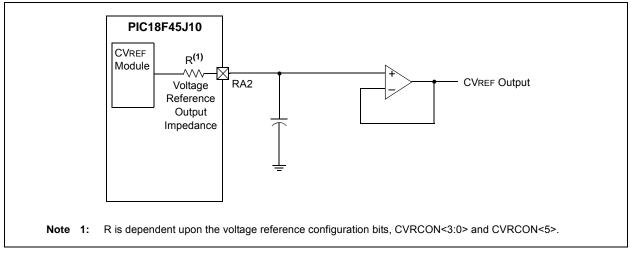

#### FIGURE 20-2: COMPARATOR VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

#### TABLE 20-1: REGISTERS ASSOCIATED WITH COMPARATOR VOLTAGE REFERENCE

| Name   | Bit 7 | Bit 6 | Bit 5  | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|-------|-------|--------|-------|--------|--------|--------|--------|----------------------------|

| CVRCON | CVREN | CVROE | CVRR   | CVRSS | CVR3   | CVR2   | CVR1   | CVR0   | 49                         |

| CMCON  | C2OUT | C10UT | C2INV  | C1INV | CIS    | CM2    | CM1    | CM0    | 49                         |

| TRISA  | _     | _     | TRISA5 | _     | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 50                         |

Legend: Shaded cells are not used with the comparator voltage reference.

## REGISTER 21-3: CONFIG2L: CONFIGURATION REGISTER 2 LOW (BYTE ADDRESS 300002h)

|                |                                                               |                                                                                                              |                                            |                                           | •                |                   | ,      |

|----------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------------------------------------------|------------------|-------------------|--------|

| R/WO-1         | R/WO-1                                                        | U-0                                                                                                          | U-0                                        | U-0                                       | R/WO-1           | R/WO-1            | R/WO-1 |

| IESO           | FCMEN                                                         |                                                                                                              |                                            |                                           | FOSC2            | FOSC1             | FOSC0  |

| bit 7          |                                                               |                                                                                                              |                                            |                                           |                  | bit 0             |        |

|                |                                                               |                                                                                                              |                                            |                                           |                  |                   |        |

| Legend:        |                                                               |                                                                                                              |                                            |                                           |                  |                   |        |

| R = Readabl    | e bit                                                         | WO = Write C                                                                                                 | nce bit                                    | U = Unimplem                              | nented bit, read | <b>l as</b> '0'   |        |

| -n = Value wi  | hen device is ur                                              | nprogrammed                                                                                                  |                                            | '1' = Bit is set                          |                  | '0' = Bit is clea | ared   |

| bit 7<br>bit 6 | 1 = Two-Spee<br>0 = Two-Spee<br>FCMEN: Fail-<br>1 = Fail-Safe | ed Start-up (<br>ed Start-up enal<br>ed Start-up disa<br>Safe Clock Mo<br>Clock Monitor (<br>Clock Monitor ( | bled<br>bled<br>nitor Enable bi<br>enabled | al Oscillator Sw<br>it                    | nichover) Cont   | ioi dit           |        |

| bit 5-3        | Unimplemen                                                    | ted: Read as '                                                                                               | )'                                         |                                           |                  |                   |        |

| bit 2          | FOSC2: Defa                                                   | ult/Reset Syste                                                                                              | m Clock Selec                              | ct bit                                    |                  |                   |        |

|                |                                                               |                                                                                                              |                                            | em clock is enal<br>OSCCON<1:0>           |                  | CCON<1:0> =       | 00     |

| bit 1-0        | FOSC<1:0>:                                                    | Oscillator Sele                                                                                              | ction bits                                 |                                           |                  |                   |        |

|                | 10 = EC osci                                                  | illator, CLKO fu<br>illator, PLL ena                                                                         | nction on OSC                              | r software contr<br>2<br>r software contr | ,                | tion on OSC2      |        |

00 = HS oscillator

### REGISTER 21-5: CONFIG3L: CONFIGURATION REGISTER 3 LOW (BYTE ADDRESS 300004h)

| U-0                                                                     | U-0   | U-0          | U-0     | U-0          | U-0             | U-0             | U-0   |  |  |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------|-------|--------------|---------|--------------|-----------------|-----------------|-------|--|--|--|--|--|--|--|--|--|

| _                                                                       | _     | —            | —       | —            |                 | —               | —     |  |  |  |  |  |  |  |  |  |

| bit 7                                                                   |       |              |         |              |                 |                 | bit 0 |  |  |  |  |  |  |  |  |  |

|                                                                         |       |              |         |              |                 |                 |       |  |  |  |  |  |  |  |  |  |

| Legend:                                                                 |       |              |         |              |                 | Legend:         |       |  |  |  |  |  |  |  |  |  |

| R = Readable bit WO = Write Once bit U = Unimplemented bit, read as '0' |       |              |         |              |                 |                 |       |  |  |  |  |  |  |  |  |  |

| R = Readable                                                            | e bit | WO = Write C | nce bit | U = Unimplem | ented bit, read | <b>l as</b> '0' |       |  |  |  |  |  |  |  |  |  |

bit 7-0 Unimplemented: Read as '0'

## REGISTER 21-6: CONFIG3H: CONFIGURATION REGISTER 3 HIGH (BYTE ADDRESS 300005h)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/WO-1 |

|-------|-----|-----|-----|-----|-----|-----|--------|

| (1)   | (1) | (1) | (1) | —   | —   |     | CCP2MX |

| bit 7 |     |     |     |     |     |     | bit 0  |

| Legend:                |                     |                     |                      |

|------------------------|---------------------|---------------------|----------------------|

| R = Readable bit       | WO = Write Once bit | U = Unimplemented b | bit, read as '0'     |

| -n = Value when device | is unprogrammed     | '1' = Bit is set    | '0' = Bit is cleared |

| bit 7-1 | Unimplemented: Read as ' | 1,' <b>(1)</b> |

|---------|--------------------------|----------------|

|         |                          |                |

bit 0 CCP2MX: CCP2 MUX bit

1 = CCP2 is multiplexed with RC1

0 = CCP2 is multiplexed with RB3

**Note 1:** The value of these bits in program memory should always be '1'. This ensures that the location is executed as a NOP if it is accidentally executed.

| BRA   | L L                                   | Uncondition                                                        | nal Branch                                         |                                         | BSF                       | Bit Set f                                  |                                 |                           |

|-------|---------------------------------------|--------------------------------------------------------------------|----------------------------------------------------|-----------------------------------------|---------------------------|--------------------------------------------|---------------------------------|---------------------------|

| Synta | ax:                                   | BRA n                                                              |                                                    |                                         | Syntax:                   | BSF f, b                                   | [,a}                            |                           |

| Oper  | ands:                                 | $-1024 \le n \le 10$                                               | )23                                                |                                         | Operands:                 | $0 \leq f \leq 255$                        |                                 |                           |

| Oper  | ation:                                | (PC) + 2 + 2n                                                      | $\rightarrow$ PC                                   |                                         |                           | $0 \le b \le 7$                            |                                 |                           |

| Statu | s Affected:                           | None                                                               |                                                    |                                         | Operation:                | a ∈ [0 , 1]<br>1 → f <b></b>               |                                 |                           |

| Enco  | ding:                                 | 1101 (                                                             | )nnn nnn                                           | n nnnn                                  | Status Affected:          | $1 \rightarrow 1 < 0 >$<br>None            |                                 |                           |

| Desc  | ription:                              | Add the 2's co<br>the PC. Since<br>incremented to<br>the new addre | the PC will ha<br>o fetch the nex<br>ss will be PC | ve<br>it instruction,<br>+ 2 + 2n. This | Encoding:<br>Description: | 1000<br>Bit 'b' in reg<br>If 'a' is '0', t | gister 'f' is se<br>he Access B | ank is selected           |

| Word  | s:                                    | instruction is a                                                   | i two-cycle ins                                    | truction.                               |                           | GPR bank                                   | (default).                      | ed to select th           |

| Cycle | es:                                   | 2                                                                  |                                                    |                                         |                           |                                            |                                 | uction operate            |

| QC    | ycle Activity:                        |                                                                    |                                                    |                                         |                           |                                            | Literal Offset                  | 0                         |

|       | Q1                                    | Q2                                                                 | Q3                                                 | Q4                                      |                           |                                            | never f ≤ 95 (<br>2 3 "Byte-C   | 5Fh). See<br>Driented and |

|       | Decode                                | Read literal<br>'n'                                                | Process<br>Data                                    | Write to PC                             |                           | Bit-Oriente                                |                                 | ns in Indexed             |

|       | No<br>operation                       | No<br>operation                                                    | No<br>operation                                    | No<br>operation                         | Words:                    | 1                                          |                                 |                           |

|       |                                       | •                                                                  | •                                                  | ·                                       | Cycles:                   | 1                                          |                                 |                           |

| Exam  | anlo:                                 | HERE                                                               | BRA Jump                                           |                                         | Q Cycle Activity:         |                                            |                                 |                           |

|       |                                       |                                                                    | BRA JUIIIP                                         |                                         | Q1                        | Q2                                         | Q3                              | Q4                        |

|       | Before Instru<br>PC<br>After Instruct | = ad                                                               | dress (HERE                                        | )                                       | Decode                    | Read<br>register 'f'                       | Process<br>Data                 | Write<br>register 'f'     |

|       | PC                                    |                                                                    | dress (Jump                                        | )                                       | Example:                  | BSF I                                      | LAG_REG,                        | 7,1                       |

|       |                                       |                                                                    |                                                    |                                         | Before Instru             | ction                                      |                                 |                           |

| Before Instruction |   |     |

|--------------------|---|-----|

| FLAG_REG           | = | 0Ah |

| After Instruction  |   |     |

| FLAG REG           | = | 8Ah |

| BTG                                                   | Bit Toggle f                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | BOV                                                                                         | Branch if Overflow                                                                                                                                                                                                                                                      |                                |

|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Syntax:                                               | BTG f, b {,a}                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Syntax:                                                                                     | BOV n                                                                                                                                                                                                                                                                   |                                |

| Operands:                                             | $0 \le f \le 255$                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Operands:                                                                                   | -128 ≤ n ≤ 127                                                                                                                                                                                                                                                          |                                |

|                                                       | 0 ≤ b < 7<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Operation:                                                                                  | if Overflow bit is '1',<br>(PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                                                               |                                |

| Operation:                                            | $(\overline{f}) \to f$                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Status Affected:                                                                            | None                                                                                                                                                                                                                                                                    |                                |

| Status Affected:                                      | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Encoding:                                                                                   | 1110 0100 nnnn                                                                                                                                                                                                                                                          | nnnn                           |

| Encoding:<br>Description:                             | 0111bbbaffffffffBit 'b' in data memory location 'f' is<br>inverted.If 'a' is '0', the Access Bank is selected.If 'a' is '0', the BSR is used to select the<br>GPR bank (default).GPR bank (default).If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). SeeSection 22.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. | Description:<br>Words:<br>Cycles:<br>Q Cycle Activity:                                      | If the Overflow bit is '1', then the<br>program will branch.<br>The 2's complement number, 'added to the PC. Since the PC<br>incremented to fetch the next<br>instruction, the new address w<br>PC + 2 + 2n. This instruction is<br>two-cycle instruction.<br>1<br>1(2) | 2n', is<br>will have<br>ill be |

| Words:                                                | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | lf Jump:<br>Q1                                                                              | Q2 Q3                                                                                                                                                                                                                                                                   | Q4                             |

| Cycles:                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Decode                                                                                      |                                                                                                                                                                                                                                                                         | te to PC                       |

| Q Cycle Activity:                                     | 02 02 04                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | No                                                                                          | No No                                                                                                                                                                                                                                                                   | No                             |

| Q1<br>Decode                                          | Q2 Q3 Q4<br>Read Process Write                                                                                                                                                                                                                                                                                                                                                                                                                                                           | operation                                                                                   | operation operation op                                                                                                                                                                                                                                                  | eration                        |

| Decode                                                | register 'f' Data register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                                                           | lf No Jump:<br>Q1                                                                           | Q2 Q3                                                                                                                                                                                                                                                                   | Q4                             |

| Example:                                              | BTG PORTC, 4, 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Decode                                                                                      | Read literal Process                                                                                                                                                                                                                                                    | No                             |

| Before Instruct<br>PORTC<br>After Instructio<br>PORTC | = 0111 0101 [75h]<br>on:                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Example:<br>Before Instruc<br>PC<br>After Instructi<br>If Overflu<br>PC<br>If Overflu<br>PC | = address (HERE)<br>on<br>ow = 1;<br>= address (Jump)                                                                                                                                                                                                                   | )                              |

| SUBWFB                                                   | Su                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | btract    | W from f wit              | h Borrow    |  |  |

|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------|-------------|--|--|

| Syntax:                                                  | SU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | BWFB      | f {,d {,a}}               |             |  |  |

| Operands:                                                | 0 ≤                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | f ≤ 255   |                           |             |  |  |

|                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | [0,1]     |                           |             |  |  |

|                                                          | $\mathbf{a} \in [0, 1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |                           |             |  |  |

| Operation: $(f) - (W) - (\overline{C}) \rightarrow dest$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |                           |             |  |  |

| Status Affected:                                         | N, OV, C, DC, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |                           |             |  |  |

| Encoding:                                                | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 101       | 10da fff                  | f ffff      |  |  |

| Description:<br>Words:<br>Cycles:                        | Subtract W and the Carry flag (borrow)<br>from register 'f' (2's complement<br>method). If 'd' is '0', the result is stored<br>in W. If 'd' is '1', the result is stored back<br>in register 'f' (default).<br>If 'a' is '0', the Access Bank is selected<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 22.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |           |                           |             |  |  |

| Q Cycle Activity:                                        | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |                           |             |  |  |

| Q1                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Q2        | Q3                        | Q4          |  |  |

| Decode                                                   | F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Read      | Process                   | Write to    |  |  |

|                                                          | reg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ister 'f' | Data                      | destination |  |  |

| Example 1:                                               | SI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | UBWFB     | REG, 1, 0                 |             |  |  |

| Before Instruc<br>REG                                    | tion<br>=                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 19h       | (0001 100                 | 11)         |  |  |

| W                                                        | =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0Dh       | (0001 100<br>(0000 110    |             |  |  |

| C                                                        | =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1         |                           |             |  |  |

| After Instructio<br>REG                                  | n<br>=                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0Ch       | (0000 101                 | L1)         |  |  |