Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 40MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 32                                                                           |

| Program Memory Size        | 16KB (8K x 16)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                    |

| Data Converters            | A/D 13x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

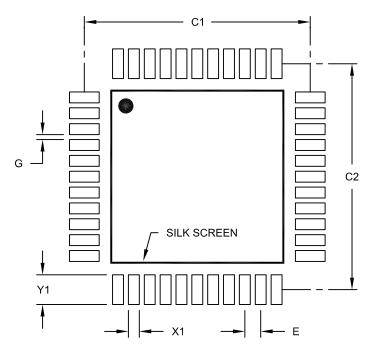

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 44-QFN (8x8)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf44j10t-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                                          | Pin Number |     |      | Pin Buffer        |                           | Description                                                                                                   |  |  |

|---------------------------------------------------|------------|-----|------|-------------------|---------------------------|---------------------------------------------------------------------------------------------------------------|--|--|

| Fiii Naille                                       | PDIP       | QFN | TQFP | Туре              | Туре                      | Description                                                                                                   |  |  |

|                                                   |            |     |      |                   |                           | PORTB is a bidirectional I/O port. PORTB can be software programmed for internal weak pull-ups on all inputs. |  |  |

| RB0/INT0/FLT0/AN12<br>RB0<br>INT0<br>FLT0<br>AN12 | 33         | 9   | 8    | I/O<br> <br> <br> | TTL<br>ST<br>ST<br>Analog | Digital I/O.<br>External Interrupt 0.<br>PWM Fault input for Enhanced CCP1.<br>Analog input 12.               |  |  |

| RB1/INT1/AN10<br>RB1<br>INT1<br>AN10              | 34         | 10  | 9    | I/O<br>I<br>I     | TTL<br>ST<br>Analog       | Digital I/O.<br>External Interrupt 1.<br>Analog input 10.                                                     |  |  |

| RB2/INT2/AN8<br>RB2<br>INT2<br>AN8                | 35         | 11  | 10   | I/O<br>I<br>I     | TTL<br>ST<br>Analog       | Digital I/O.<br>External Interrupt 2.<br>Analog input 8.                                                      |  |  |

| RB3/AN9/CCP2<br>RB3<br>AN9<br>CCP2 <sup>(1)</sup> | 36         | 12  | 11   | I/O<br>I<br>I/O   | TTL<br>Analog<br>ST       | Digital I/O.<br>Analog Input 9.<br>Capture 2 input/Compare 2 output/PWM2 output                               |  |  |

| RB4/KBI0/AN11<br>RB4<br>KBI0<br>AN11              | 37         | 14  | 14   | I/O<br>I<br>I     | TTL<br>TTL<br>Analog      | Digital I/O.<br>Interrupt-on-change pin.<br>Analog Input 11.                                                  |  |  |

| RB5/KBI1/C1OUT<br>RB5<br>KBI1<br>C1OUT            | 38         | 15  | 15   | I/O<br>I<br>O     | TTL<br>TTL<br>—           | Digital I/O.<br>Interrupt-on-change pin.<br>Comparator 1 output.                                              |  |  |

| RB6/KBI2/PGC<br>RB6<br>KBI2<br>PGC                | 39         | 16  | 16   | I/O<br>I<br>I/O   | TTL<br>TTL<br>ST          | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP™ programming<br>clock pin.           |  |  |

| RB7/KBI3/PGD<br>RB7<br>KBI3<br>PGD                | 40         | 17  | 17   | I/O<br>I<br>I/O   | TTL<br>TTL<br>ST          | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming<br>data pin.             |  |  |

# TABLE 1-3: PIC18F44J10/45J10 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

| Pin Name                                          | Pin Number |     |      | Pin                    | Buffer                | Description                                                                                                                                                                       |  |  |

|---------------------------------------------------|------------|-----|------|------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Fiil Name                                         | PDIP       | QFN | TQFP | Туре                   | Туре                  | Description                                                                                                                                                                       |  |  |

|                                                   | 10         | 20  | 20   |                        |                       | PORTD is a bidirectional I/O port or a Parallel Slave<br>Port (PSP) for interfacing to a microprocessor port.<br>These pins have TTL input buffers when PSP module<br>is enabled. |  |  |

| RD0/PSP0/SCK2/<br>SCL2                            | 19         | 38  | 38   |                        |                       |                                                                                                                                                                                   |  |  |

| RD0<br>PSP0<br>SCK2                               |            |     |      | 1/0<br>1/0<br>1/0      | ST<br>TTL<br>ST       | Digital I/O.<br>Parallel Slave Port data.<br>Synchronous serial clock input/output for<br>SPI mode.                                                                               |  |  |

| SCL2                                              |            |     |      | I/O                    | ST                    | Synchronous serial clock input/output for<br>I <sup>2</sup> C™ mode.                                                                                                              |  |  |

| RD1/PSP1/SDI2/SDA2<br>RD1<br>PSP1<br>SDI2<br>SDA2 | 20         | 39  | 39   | I/O<br>I/O<br>I<br>I/O | ST<br>TTL<br>ST<br>ST | Digital I/O.<br>Parallel Slave Port data.<br>SPI data in.<br>I <sup>2</sup> C data I/O.                                                                                           |  |  |

| RD2/PSP2/SDO2<br>RD2<br>PSP2<br>SDO2              | 21         | 40  | 40   | I/O<br>I/O<br>O        | ST<br>TTL             | Digital I/O.<br>Parallel Slave Port data.<br>SPI data out.                                                                                                                        |  |  |

| RD3/PSP3/ <del>SS2</del><br>RD3<br>PSP3<br>SS2    | 22         | 41  | 41   | I/O<br>I/O<br>I        | ST<br>TTL<br>TTL      | Digital I/O.<br>Parallel Slave Port data.<br>SPI slave select input.                                                                                                              |  |  |

| RD4/PSP4<br>RD4<br>PSP4                           | 27         | 2   | 2    | I/O<br>I/O             | ST<br>TTL             | Digital I/O.<br>Parallel Slave Port data.                                                                                                                                         |  |  |

| RD5/PSP5/P1B<br>RD5<br>PSP5<br>P1B                | 28         | 3   | 3    | I/O<br>I/O<br>O        | ST<br>TTL             | Digital I/O.<br>Parallel Slave Port data.<br>Enhanced CCP1 output.                                                                                                                |  |  |

| RD6/PSP6/P1C<br>RD6<br>PSP6<br>P1C                | 29         | 4   | 4    | I/O<br>I/O<br>O        | ST<br>TTL             | Digital I/O.<br>Parallel Slave Port data.<br>Enhanced CCP1 output.                                                                                                                |  |  |

| RD7/PSP7/P1D<br>RD7<br>PSP7                       | 30         | 5   | 5    | I/O<br>I/O             | ST<br>TTL             | Digital I/O.<br>Parallel Slave Port data.<br>Enhanced CCP1 output.                                                                                                                |  |  |

#### **TABLE 1-3:** PIC18F44J10/45J10 PINOUT I/O DESCRIPTIONS (CONTINUED)

O = Output

= Power

Note 1: Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

# 3.6.1 OSCILLATOR CONTROL REGISTER

The OSCCON register (Register 3-2) controls several aspects of the device clock's operation, both in full-power operation and in power-managed modes.

The System Clock Select bits, SCS<1:0>, select the clock source. The available clock sources are the primary clock (defined by the FOSC<2:0> Configuration bits), the secondary clock (Timer1 oscillator) and the internal oscillator. The clock source changes after one or more of the bits are written to, following a brief clock transition interval.

The OSTS (OSCCON<3>) and T1RUN (T1CON<6>) bits indicate which clock source is currently providing the device clock. The OSTS bit indicates that the Oscillator Start-up Timer (OST) has timed out and the primary clock is providing the device clock in primary clock modes. The T1RUN bit indicates when the Timer1 oscillator is providing the device clock in secondary clock modes. In power-managed modes, only one of these bits will be set at any time. If neither of these bits is set, the INTRC is providing the clock, or the internal oscillator has just started and is not yet stable.

The IDLEN bit determines if the device goes into Sleep mode or one of the Idle modes when the SLEEP instruction is executed.

The use of the flag and control bits in the OSCCON register is discussed in more detail in **Section 4.0** "**Power-Managed Modes**".

- Note 1: The Timer1 oscillator must be enabled to select the secondary clock source. The Timer1 oscillator is enabled by setting the T1OSCEN bit in the Timer1 Control register (T1CON<3>). If the Timer1 oscillator is not enabled, then any attempt to select a secondary clock source when executing a SLEEP instruction will be ignored.

- 2: It is recommended that the Timer1 oscillator be operating and stable before executing the SLEEP instruction or a very long delay may occur while the Timer1 oscillator starts.

# 3.6.1.1 System Clock Selection and the FOSC2 Configuration Bit

The SCS bits are cleared on all forms of Reset. In the device's default configuration, this means the primary oscillator defined by FOSC<1:0> (that is, one of the HC or EC modes) is used as the primary clock source on device Resets.

The default clock configuration on Reset can be changed with the FOSC2 Configuration bit. The effect of this bit is to set the clock source selected when SCS<1:0> = 00. When FOSC2 = 1 (default), the oscillator source defined by FOSC<1:0> is selected whenever SCS<1:0> = 00. When FOSC2 = 0, the INTRC oscillator is selected whenever SCS<1:0> = 00. Because the SCS bits are cleared on Reset, the FOSC2 setting also changes the default oscillator mode on Reset.

Regardless of the setting of FOSC2, INTRC will always be enabled on device power-up. It will serve as the clock source until the device has loaded its configuration values from memory. It is at this point that the FOSC Configuration bits are read and the oscillator selection of operational mode is made.

Note that either the primary clock or the internal oscillator will have two bit setting options, at any given time, depending on the setting of FOSC2.

# 3.6.2 OSCILLATOR TRANSITIONS

PIC18F45J10 family devices contain circuitry to prevent clock "glitches" when switching between clock sources. A short pause in the device clock occurs during the clock switch. The length of this pause is the sum of two cycles of the old clock source and three to four cycles of the new clock source. This formula assumes that the new clock source is stable.

Clock transitions are discussed in greater detail in **Section 4.1.2 "Entering Power-Managed Modes"**.

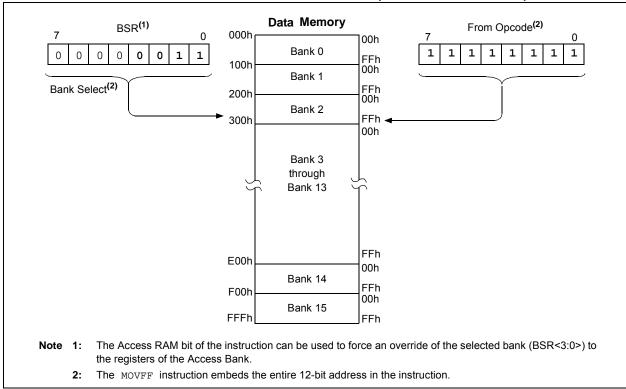

# FIGURE 6-7: USE OF THE BANK SELECT REGISTER (DIRECT ADDRESSING)

#### 6.3.2 ACCESS BANK

While the use of the BSR with an embedded 8-bit address allows users to address the entire range of data memory, it also means that the user must always ensure that the correct bank is selected. Otherwise, data may be read from or written to the wrong location. This can be disastrous if a GPR is the intended target of an operation but an SFR is written to instead. Verifying and/or changing the BSR for each read or write to data memory can become very inefficient.

To streamline access for the most commonly used data memory locations, the data memory is configured with an Access Bank, which allows users to access a mapped block of memory without specifying a BSR. The Access Bank consists of the first 128 bytes of memory (00h-7Fh) in Bank 0 and the last 128 bytes of memory (80h-FFh) in Block 15. The lower half is known as the "Access RAM" and is composed of GPRs. This upper half is also where the device's SFRs are mapped. These two areas are mapped contiguously in the Access Bank and can be addressed in a linear fashion by an 8-bit address (Figure 6-6).

The Access Bank is used by core PIC18 instructions that include the Access RAM bit (the 'a' parameter in the instruction). When 'a' is equal to '1', the instruction uses the BSR and the 8-bit address included in the opcode for the data memory address. When 'a' is '0',

however, the instruction is forced to use the Access Bank address map; the current value of the BSR is ignored entirely.

Using this "forced" addressing allows the instruction to operate on a data address in a single cycle without updating the BSR first. For 8-bit addresses of 80h and above, this means that users can evaluate and operate on SFRs more efficiently. The Access RAM below 80h is a good place for data values that the user might need to access rapidly, such as immediate computational results or common program variables. Access RAM also allows for faster and more code efficient context saving and switching of variables.

The mapping of the Access Bank is slightly different when the extended instruction set is enabled (XINST Configuration bit = 1). This is discussed in more detail in Section 6.5.3 "Mapping the Access Bank in Indexed Literal Offset Mode".

### 6.3.3 GENERAL PURPOSE REGISTER FILE

PIC18 devices may have banked memory in the GPR area. This is data RAM which is available for use by all instructions. GPRs start at the bottom of Bank 0 (address 000h) and grow upwards towards the bottom of the SFR area. GPRs are not initialized by a Power-on Reset and are unchanged on all other Resets.

# 6.4 Data Addressing Modes

| Note: | The execution of some instructions in the  |

|-------|--------------------------------------------|

|       | core PIC18 instruction set are changed     |

|       | when the PIC18 extended instruction set is |

|       | enabled. See Section 6.5 "Data Memory      |

|       | and the Extended Instruction Set" for      |

|       | more information.                          |

While the program memory can be addressed in only one way – through the program counter – information in the data memory space can be addressed in several ways. For most instructions, the addressing mode is fixed. Other instructions may use up to three modes, depending on which operands are used and whether or not the extended instruction set is enabled.

The addressing modes are:

- Inherent

- Literal

- Direct

- Indirect

An additional addressing mode, Indexed Literal Offset, is available when the extended instruction set is enabled (XINST Configuration bit = 1). Its operation is discussed in greater detail in **Section 6.5.1 "Indexed Addressing with Literal Offset**".

# 6.4.1 INHERENT AND LITERAL ADDRESSING

Many PIC18 control instructions do not need any argument at all; they either perform an operation that globally affects the device or they operate implicitly on one register. This addressing mode is known as Inherent Addressing. Examples include SLEEP, RESET and DAW.

Other instructions work in a similar way but require an additional explicit argument in the opcode. This is known as Literal Addressing mode because they require some literal value as an argument. Examples include ADDLW and MOVLW, which respectively, add or move a literal value to the W register. Other examples include CALL and GOTO, which include a 20-bit program memory address.

# 6.4.2 DIRECT ADDRESSING

Direct Addressing specifies all or part of the source and/or destination address of the operation within the opcode itself. The options are specified by the arguments accompanying the instruction.

In the core PIC18 instruction set, bit-oriented and byteoriented instructions use some version of Direct Addressing by default. All of these instructions include some 8-bit literal address as their Least Significant Byte. This address specifies either a register address in one of the banks of data RAM (Section 6.3.3 "General Purpose Register File") or a location in the Access Bank (Section 6.3.2 "Access Bank") as the data source for the instruction. The Access RAM bit 'a' determines how the address is interpreted. When 'a' is '1', the contents of the BSR (Section 6.3.1 "Bank Select Register (BSR)") are used with the address to determine the complete 12-bit address of the register. When 'a' is '0', the address is interpreted as being a register in the Access Bank. Addressing that uses the Access RAM is sometimes also known as Direct Forced Addressing mode.

A few instructions, such as MOVFF, include the entire 12-bit address (either source or destination) in their opcodes. In these cases, the BSR is ignored entirely.

The destination of the operation's results is determined by the destination bit 'd'. When 'd' is '1', the results are stored back in the source register, overwriting its original contents. When 'd' is '0', the results are stored in the W register. Instructions without the 'd' argument have a destination that is implicit in the instruction; their destination is either the target register being operated on or the W register.

# 6.4.3 INDIRECT ADDRESSING

Indirect Addressing allows the user to access a location in data memory without giving a fixed address in the instruction. This is done by using File Select Registers (FSRs) as pointers to the locations to be read or written to. Since the FSRs are themselves located in RAM as Special Function Registers, they can also be directly manipulated under program control. This makes FSRs very useful in implementing data structures, such as tables and arrays in data memory.

The registers for Indirect Addressing are also implemented with Indirect File Operands (INDFs) that permit automatic manipulation of the pointer value with auto-incrementing, auto-decrementing or offsetting with another value. This allows for efficient code, using loops, such as the example of clearing an entire RAM bank in Example 6-5.

#### EXAMPLE 6-5: HOW TO CLEAR RAM (BANK 1) USING INDIRECT ADDRESSING

|        | LFSR  | FSR0, 100h | ; |                |

|--------|-------|------------|---|----------------|

| NEXT   | CLRF  | POSTINC0   | ; | Clear INDF     |

|        |       |            | ; | register then  |

|        |       |            | ; | inc pointer    |

|        | BTFSS | FSROH, 1   | ; | All done with  |

|        |       |            | ; | Bank1?         |

|        | BRA   | NEXT       | ; | NO, clear next |

| CONTIN | UE    |            | ; | YES, continue  |

|        |       |            |   |                |

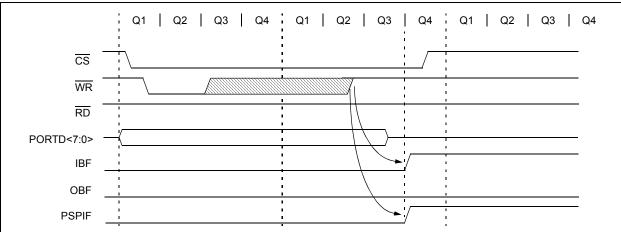

### FIGURE 10-4: PARALLEL SLAVE PORT WRITE WAVEFORMS

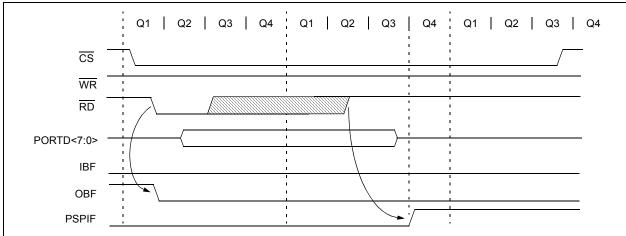

#### FIGURE 10-5: PARALLEL SLAVE PORT READ WAVEFORMS

#### TABLE 10-13: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Name                 | Bit 7                | Bit 6                                                    | Bit 5  | Bit 4   | Bit 3  | Bit 2                 | Bit 1                      | Bit 0  | Reset<br>Values<br>on page |

|----------------------|----------------------|----------------------------------------------------------|--------|---------|--------|-----------------------|----------------------------|--------|----------------------------|

| PORTD <sup>(1)</sup> | RD7                  | RD6                                                      | RD5    | RD4     | RD3    | RD2                   | RD1                        | RD0    | 50                         |

| LATD <sup>(1)</sup>  | PORTD Da             | PORTD Data Latch Register (Read and Write to Data Latch) |        |         |        |                       |                            |        | 50                         |

| TRISD <sup>(1)</sup> | PORTD Da             | PORTD Data Direction Control Register                    |        |         |        |                       |                            | 50     |                            |

| PORTE <sup>(1)</sup> | —                    | _                                                        | _      | —       | —      | RE2                   | RE1                        | RE0    | 50                         |

| LATE <sup>(1)</sup>  | —                    |                                                          | —      | -       | —      | PORTE Da<br>(Read and | ta Latch Re<br>Write to Da | 0      | 50                         |

| TRISE <sup>(1)</sup> | IBF                  | OBF                                                      | IBOV   | PSPMODE | _      | TRISE2                | TRISE1                     | TRISE0 | 50                         |

| INTCON               | GIE/GIEH             | PEIE/GIEL                                                | TMR0IE | INT0IE  | RBIE   | TMR0IF                | INT0IF                     | RBIF   | 47                         |

| PIR1                 | PSPIF <sup>(1)</sup> | ADIF                                                     | RCIF   | TXIF    | SSP1IF | CCP1IF                | TMR2IF                     | TMR1IF | 49                         |

| PIE1                 | PSPIE <sup>(1)</sup> | ADIE                                                     | RCIE   | TXIE    | SSP1IE | CCP1IE                | TMR2IE                     | TMR1IE | 49                         |

| IPR1                 | PSPIP <sup>(1)</sup> | ADIP                                                     | RCIP   | TXIP    | SSP1IP | CCP1IP                | TMR2IP                     | TMR1IP | 49                         |

| ADCON1               | _                    | _                                                        | VCFG1  | VCFG0   | PCFG3  | PCFG2                 | PCFG1                      | PCFG0  | 48                         |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the Parallel Slave Port.

Note 1: These registers and/or bits are not implemented on 28-pin devices and should be read as '0'.

# 12.5 Resetting Timer1 Using the ECCP/CCP Special Event Trigger

If ECCP1/CCP1 or CCP2 is configured to generate a Special Event Trigger in Compare mode (CCPxM<3:0> = 1011), this signal will reset Timer1. The trigger from CCP2 will also start an A/D conversion if the A/D module is enabled (see **Section 15.2.1** "**Special Event Trigger**" for more information).

The module must be configured as either a timer or a synchronous counter to take advantage of this feature. When used this way, the CCPRH:CCPRL register pair effectively becomes a period register for Timer1.

If Timer1 is running in Asynchronous Counter mode, this Reset operation may not work.

In the event that a write to Timer1 coincides with a Special Event Trigger, the write operation will take precedence.

| Note: | The Special Event Triggers from the  |

|-------|--------------------------------------|

|       | ECCP1/CCPx module will not set the   |

|       | TMR1IF interrupt flag bit (PIR1<0>). |

# 12.6 Using Timer1 as a Real-Time Clock

Adding an external LP oscillator to Timer1 (such as the one described in **Section 12.3 "Timer1 Oscillator"** above) gives users the option to include RTC functionality to their applications. This is accomplished with an inexpensive watch crystal to provide an accurate time base and several lines of application code to calculate the time. When operating in Sleep mode and using a battery or supercapacitor as a power source, it can completely eliminate the need for a separate RTC device and battery backup.

The application code routine, RTCisr, shown in Example 12-1, demonstrates a simple method to increment a counter at one-second intervals using an Interrupt Service Routine. Incrementing the TMR1 register pair to overflow triggers the interrupt and calls the routine which increments the seconds counter by one. Additional counters for minutes and hours are incremented as the previous counter overflows.

Since the register pair is 16 bits wide, counting up to overflow the register directly from a 32.768 kHz clock would take 2 seconds. To force the overflow at the required one-second intervals, it is necessary to preload it. The simplest method is to set the MSb of TMR1H with a BSF instruction. Note that the TMR1L register is never preloaded or altered; doing so may introduce cumulative error over many cycles.

For this method to be accurate, Timer1 must operate in Asynchronous mode and the Timer1 overflow interrupt must be enabled (PIE1<0> = 1) as shown in the routine, RTCinit. The Timer1 oscillator must also be enabled and running at all times.

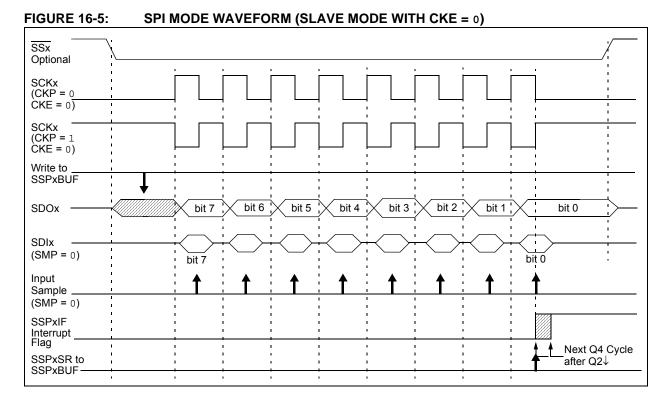

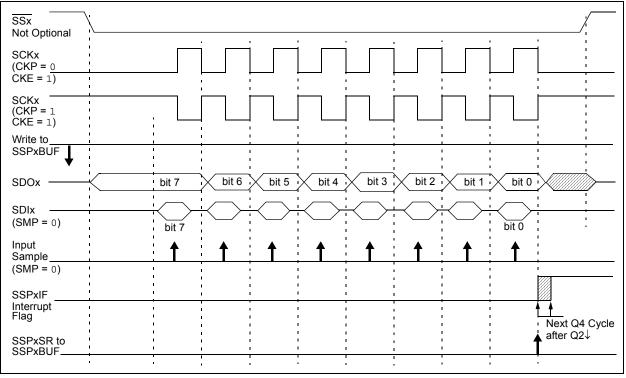

# FIGURE 16-6: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

# 16.4.6.1 I<sup>2</sup>C Master Mode Operation

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDAx, while SCLx outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the  $R/\overline{W}$  bit. In this case, the  $R/\overline{W}$  bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDAx, while SCLx outputs the serial clock. Serial data is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

The Baud Rate Generator used for the SPI mode operation is used to set the SCLx clock frequency for either 100 kHz, 400 kHz or 1 MHz I<sup>2</sup>C operation. See **Section 16.4.7 "Baud Rate"** for more detail.

A typical transmit sequence would go as follows:

- 1. The user generates a Start condition by setting the Start Enable bit, SEN (SSPxCON2<0>).

- SSPxIF is set. The MSSP module will wait the required start time before any other operation takes place.

- 3. The user loads the SSPxBUF with the slave address to transmit.

- 4. Address is shifted out the SDAx pin until all 8 bits are transmitted.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPxCON2 register (SSPxCON2<6>).

- The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 7. The user loads the SSPxBUF with eight bits of data.

- 8. Data is shifted out the SDAx pin until all 8 bits are transmitted.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPxCON2 register (SSPxCON2<6>).

- 10. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 11. The user generates a Stop condition by setting the Stop Enable bit, PEN (SSPxCON2<2>).

- 12. Interrupt is generated once the Stop condition is complete.

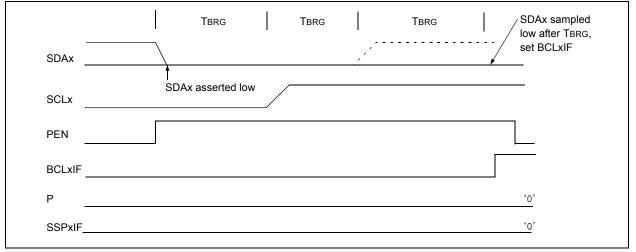

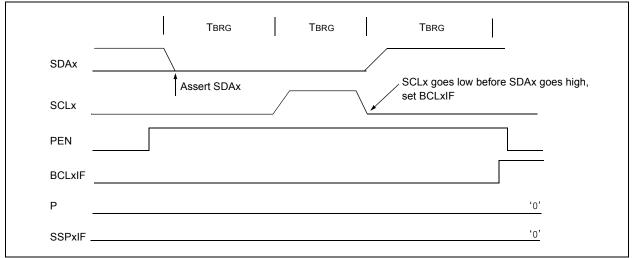

### 16.4.17.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDAx pin has been deasserted and allowed to float high, SDAx is sampled low after the BRG has timed out.

- b) After the SCLx pin is deasserted, SCLx is sampled low before SDAx goes high.

The Stop condition begins with SDAx asserted low. When SDAx is sampled low, the SCLx pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPxADD<6:0> and counts down to 0. After the BRG times out, SDAx is sampled. If SDAx is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 16-31). If the SCLx pin is sampled low before SDAx is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 16-32).

# FIGURE 16-31: BUS COLLISION DURING A STOP CONDITION (CASE 1)

FIGURE 16-32: BUS COLLISION DURING A STOP CONDITION (CASE 2)

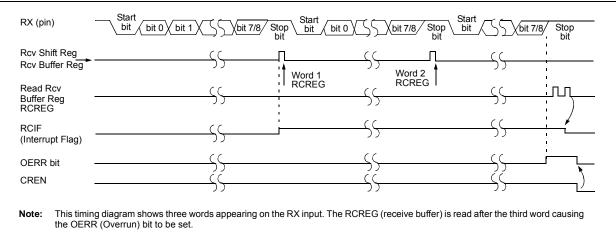

# FIGURE 17-7: ASYNCHRONOUS RECEPTION

| Name    | Bit 7                | Bit 6         | Bit 5        | Bit 4        | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|----------------------|---------------|--------------|--------------|--------|--------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH             | PEIE/GIEL     | TMR0IE       | INT0IE       | RBIE   | TMR0IF | INT0IF | RBIF   | 47                         |

| PIR1    | PSPIF <sup>(1)</sup> | ADIF          | RCIF         | TXIF         | SSP1IF | CCP1IF | TMR2IF | TMR1IF | 49                         |

| PIE1    | PSPIE <sup>(1)</sup> | ADIE          | RCIE         | TXIE         | SSP1IE | CCP1IE | TMR2IE | TMR1IE | 49                         |

| IPR1    | PSPIP <sup>(1)</sup> | ADIP          | RCIP         | TXIP         | SSP1IP | CCP1IP | TMR2IP | TMR1IP | 49                         |

| RCSTA   | SPEN                 | RX9           | SREN         | CREN         | ADDEN  | FERR   | OERR   | RX9D   | 49                         |

| RCREG   | EUSART F             | Receive Regis | ster         |              |        |        |        |        | 49                         |

| TXSTA   | CSRC                 | TX9           | TXEN         | SYNC         | SENDB  | BRGH   | TRMT   | TX9D   | 49                         |

| BAUDCON | ABDOVF               | RCIDL         | _            | SCKP         | BRG16  | _      | WUE    | ABDEN  | 49                         |

| SPBRGH  | EUSART E             | aud Rate Ge   | enerator Reg | gister High  | Byte   |        |        |        | 49                         |

| SPBRG   | EUSART E             | aud Rate Ge   | enerator Reg | gister Low E | Byte   |        |        |        | 49                         |

| · ·     | · · ·                |               |              |              |        |        |        |        | •                          |

Legend: — = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

**Note 1:** These bits are not implemented on 28-pin devices and should be read as '0'.

#### 17.2.4 AUTO-WAKE-UP ON SYNC BREAK CHARACTER

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper byte reception cannot be performed. The auto-wake-up feature allows the controller to wake-up due to activity on the RX/DT line while the EUSART is operating in Asynchronous mode.

The auto-wake-up feature is enabled by setting the WUE bit (BAUDCON<1>). Once set, the typical receive sequence on RX/DT is disabled and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a Wake-up Signal character for the LIN/J2602 support protocol.)

Following a wake-up event, the module generates an RCIF interrupt. The interrupt is generated synchronously to the Q clocks in normal operating modes (Figure 17-8) and asynchronously, if the device is in Sleep mode (Figure 17-9). The interrupt condition is cleared by reading the RCREG register.

The WUE bit is automatically cleared once a low-tohigh transition is observed on the RX line following the wake-up event. At this point, the EUSART module is in Idle mode and returns to normal operation. This signals to the user that the Sync Break event is over.

NOTES:

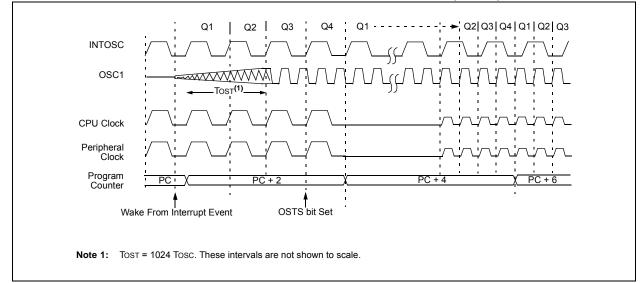

# 21.4 Two-Speed Start-up

The Two-Speed Start-up feature helps to minimize the latency period, from oscillator start-up to code execution, by allowing the microcontroller to use the INTRC oscillator as a clock source until the primary clock source is available. It is enabled by setting the IESO Configuration bit.

Two-Speed Start-up should be enabled only if the primary oscillator mode is HS (Crystal-Based) modes. Since the EC mode does not require an OST start-up delay, Two-Speed Start-up should be disabled.

When enabled, Resets and wake-ups from Sleep mode cause the device to configure itself to run from the internal oscillator block as the clock source, following the time-out of the Power-up Timer after a POR Reset is enabled. This allows almost immediate code execution while the primary oscillator starts and the OST is running. Once the OST times out, the device automatically switches to PRI\_RUN mode. In all other power-managed modes, Two-Speed Start-up is not used. The device will be clocked by the currently selected clock source until the primary clock source becomes available. The setting of the IESO bit is ignored.

# 21.4.1 SPECIAL CONSIDERATIONS FOR USING TWO-SPEED START-UP

While using the INTRC oscillator in Two-Speed Start-up, the device still obeys the normal command sequences for entering power-managed modes, including serial SLEEP instructions (refer to **Section 4.1.4 "Multiple Sleep Commands"**). In practice, this means that user code can change the SCS<1:0> bit settings or issue SLEEP instructions before the OST times out. This would allow an application to briefly wake-up, perform routine "housekeeping" tasks and return to Sleep before the device starts to operate from the primary oscillator.

User code can also check if the primary clock source is currently providing the device clocking by checking the status of the OSTS bit (OSCCON<3>). If the bit is set, the primary oscillator is providing the clock. Otherwise, the internal oscillator block is providing the clock during wake-up from Reset or Sleep mode.

### FIGURE 21-3: TIMING TRANSITION FOR TWO-SPEED START-UP (INTRC)

| GOT         | ю                                         | Uncondi                      | Unconditional Branch                 |                            |                                         |  |  |  |  |  |

|-------------|-------------------------------------------|------------------------------|--------------------------------------|----------------------------|-----------------------------------------|--|--|--|--|--|

| Synta       | ax:                                       | GOTO k                       |                                      |                            |                                         |  |  |  |  |  |

| Oper        | ands:                                     | $0 \le k \le 10^4$           | 48575                                |                            |                                         |  |  |  |  |  |

| Oper        | ation:                                    | $k \rightarrow PC<2$         | 0:1>                                 |                            |                                         |  |  |  |  |  |

| Statu       | s Affected:                               | None                         | None                                 |                            |                                         |  |  |  |  |  |

|             | oding:<br>vord (k<7:0>)<br>word(k<19:8>)  | 1110<br>1111                 | 1111<br>k <sub>19</sub> kkk          | /                          |                                         |  |  |  |  |  |

| Desc        | ription:                                  | is always a                  | within ent<br>emory rai<br>loaded in | ire<br>nge. The<br>to PC<2 | 20-bit<br>0:1>. дото                    |  |  |  |  |  |

|             |                                           | 2                            |                                      |                            |                                         |  |  |  |  |  |

| Cycle       | es:                                       | 2                            | 2                                    |                            |                                         |  |  |  |  |  |

| QC          | ycle Activity:                            |                              |                                      |                            |                                         |  |  |  |  |  |

|             | Q1                                        | Q2                           | Q3                                   |                            | Q4                                      |  |  |  |  |  |

|             | Decode                                    | Read literal<br>'k'<7:0>,    | No<br>operat                         | tion '                     | ead literal<br>k'<19:8>,<br>/rite to PC |  |  |  |  |  |

|             | No<br>operation                           | No<br>operation              | No<br>operat                         |                            | No<br>operation                         |  |  |  |  |  |

| <u>Exan</u> | n <u>ple:</u><br>After Instructic<br>PC = | GOTO THE<br>on<br>Address (1 |                                      |                            |                                         |  |  |  |  |  |

| INCF                                                                                                                      | Incremen                                                                                                                                                        | tf                                                                                                                |                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| Syntax:                                                                                                                   | INCF f{,c                                                                                                                                                       | l {,a}}                                                                                                           |                                                                                                   |

| Operands:                                                                                                                 | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$                                                                              |                                                                                                                   |                                                                                                   |

| Operation:                                                                                                                | (f) + 1 $\rightarrow$ de                                                                                                                                        | est                                                                                                               |                                                                                                   |

| Status Affected:                                                                                                          | C, DC, N, (                                                                                                                                                     | OV, Z                                                                                                             |                                                                                                   |

| Encoding:                                                                                                                 | 0010                                                                                                                                                            | 10da ff                                                                                                           | ff ffff                                                                                           |

|                                                                                                                           | placed bacl<br>If 'a' is '0', t<br>If 'a' is '1', t<br>GPR bank<br>If 'a' is '0' a                                                                              | nd the extende                                                                                                    | (default).<br>nk is selecte<br>d to select th<br>ed instructio                                    |

|                                                                                                                           | in Indexed<br>mode when<br>Section 22<br>Bit-Oriente                                                                                                            | ed, this instruct<br>Literal Offset A<br>lever f ≤ 95 (5)<br>.2.3 "Byte-Or<br>ed Instruction<br>set Mode" for     | Fh). See<br>iented and<br>is in Indexe                                                            |

| Words:                                                                                                                    | in Indexed<br>mode when<br>Section 22<br>Bit-Oriente                                                                                                            | Literal Offset A<br>lever f ≤ 95 (5<br>.2.3 "Byte-Or<br>ed Instruction                                            | Addressing<br>Fh). See<br>iented and<br>is in Indexe                                              |

| Words:<br>Cycles:                                                                                                         | in Indexed<br>mode when<br>Section 22<br>Bit-Oriente<br>Literal Offs                                                                                            | Literal Offset A<br>lever f ≤ 95 (5<br>.2.3 "Byte-Or<br>ed Instruction                                            | Addressing<br>Fh). See<br>iented and<br>is in Indexe                                              |

|                                                                                                                           | in Indexed<br>mode when<br>Section 22<br>Bit-Oriente<br>Literal Offs<br>1                                                                                       | Literal Offset A<br>lever f ≤ 95 (5<br>.2.3 "Byte-Or<br>ed Instruction                                            | Addressing<br>Fh). See<br>iented and<br>is in Indexe                                              |

| Cycles:                                                                                                                   | in Indexed<br>mode when<br>Section 22<br>Bit-Oriente<br>Literal Offs<br>1                                                                                       | Literal Offset A<br>lever f ≤ 95 (5<br>.2.3 "Byte-Or<br>ed Instruction                                            | Addressing<br>Fh). See<br>iented and<br>is in Indexe                                              |

| Cycles:<br>Q Cycle Activity:                                                                                              | in Indexed<br>mode wher<br>Section 22<br>Bit-Oriente<br>Literal Offs<br>1                                                                                       | Literal Offset A<br>never f ≤ 95 (5<br>.2.3 "Byte-Or<br>ed Instruction<br>set Mode" for                           | Addressing<br>Fh). See<br><b>iented and</b><br><b>is in Indexe</b><br>details.                    |

| Cycles:<br>Q Cycle Activity:<br>Q1                                                                                        | in Indexed<br>mode wher<br>Section 22<br>Bit-Oriente<br>Literal Offs<br>1<br>1<br>Q2<br>Read                                                                    | Literal Offset A<br>never $f \le 95$ (5<br>.2.3 "Byte-Or<br>ed Instruction<br>set Mode" for<br>Q3<br>Process      | Addressing<br>Fh). See<br>iented and<br>is in Indexe<br>details.<br>Q4<br>Write to<br>destination |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode                                                                              | in Indexed<br>mode when<br>Section 22<br>Bit-Oriente<br>Literal Offs<br>1<br>1<br>Q2<br>Read<br>register 'f'<br>INCF<br>tion                                    | Literal Offset A<br>never f ≤ 95 (5)<br>.2.3 "Byte-Or<br>ed Instruction<br>set Mode" for<br>Q3<br>Process<br>Data | Addressing<br>Fh). See<br>iented and<br>is in Indexe<br>details.<br>Q4<br>Write to<br>destination |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>Example:<br>Before Instruc<br>CNT                                         | in Indexed<br>mode when<br>Section 22<br>Bit-Oriente<br>Literal Offs<br>1<br>1<br>Q2<br>Read<br>register f<br>INCF<br>tion<br>= FFh                             | Literal Offset A<br>never f ≤ 95 (5)<br>.2.3 "Byte-Or<br>ed Instruction<br>set Mode" for<br>Q3<br>Process<br>Data | Addressing<br>Fh). See<br>iented and<br>is in Indexe<br>details.<br>Q4<br>Write to<br>destinatio  |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>Example:<br>Before Instruc<br>CNT<br>Z<br>C                               | in Indexed<br>mode when<br>Section 22<br>Bit-Oriente<br>Literal Offs<br>1<br>1<br>1<br>Q2<br>Read<br>register 'f'<br>INCF<br>tion<br>= FFh<br>= 0<br>= ?        | Literal Offset A<br>never f ≤ 95 (5)<br>.2.3 "Byte-Or<br>ed Instruction<br>set Mode" for<br>Q3<br>Process<br>Data | Addressing<br>Fh). See<br>iented and<br>is in Indexe<br>details.<br>Q4<br>Write to<br>destination |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>Example:<br>Before Instruc<br>CNT<br>Z<br>C<br>DC                         | in Indexed<br>mode when<br>Section 22<br>Bit-Oriente<br>Literal Offs<br>1<br>1<br>1<br>Q2<br>Read<br>register 'f'<br>INCF<br>tion<br>= FFh<br>= 0<br>= ?<br>= ? | Literal Offset A<br>never f ≤ 95 (5)<br>.2.3 "Byte-Or<br>ed Instruction<br>set Mode" for<br>Q3<br>Process<br>Data | Addressing<br>Fh). See<br>iented and<br>is in Indexe<br>details.<br>Q4<br>Write to<br>destinatio  |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>Example:<br>Before Instruct<br>CNT<br>C<br>DC<br>After Instruction<br>CNT | in Indexed<br>mode when<br>Section 22<br>Bit-Oriente<br>Literal Offs<br>1<br>1<br>1<br>Q2<br>Read<br>register 'f'<br>INCF<br>tion<br>= FFh<br>= 0<br>= ?<br>= ? | Literal Offset A<br>never f ≤ 95 (5)<br>.2.3 "Byte-Or<br>ed Instruction<br>set Mode" for<br>Q3<br>Process<br>Data | Addressing<br>Fh). See<br>iented and<br>is in Indexe<br>details.<br>Q4<br>Write to<br>destination |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>Example:<br>Before Instruct<br>CNT<br>Z<br>C<br>DC<br>After Instruction   | in Indexed<br>mode when<br>Section 22<br>Bit-Oriente<br>Literal Offs<br>1<br>1<br>1<br>Q2<br>Read<br>register 'f'<br>INCF<br>tion<br>= FFh<br>= 0<br>= ?<br>= ? | Literal Offset A<br>never f ≤ 95 (5)<br>.2.3 "Byte-Or<br>ed Instruction<br>set Mode" for<br>Q3<br>Process<br>Data | Addressing<br>Fh). See<br>iented and<br>is in Indexe<br>details.<br>Q4<br>Write to<br>destinatio  |

| IORLW            | OR Lite | eral w                            | /ith         | w   |    |          |  |  |  |

|------------------|---------|-----------------------------------|--------------|-----|----|----------|--|--|--|

| Syntax:          |         | IORLW k                           |              |     |    |          |  |  |  |

| Operands:        |         | $0 \le k \le 25$                  | 5            |     |    |          |  |  |  |

| Operation:       |         | (W) .OR. $k \rightarrow W$        |              |     |    |          |  |  |  |

| Status Affected  | :       | N, Z                              |              |     |    |          |  |  |  |

| Encoding:        |         | 0000                              | 1001         | kkk | k  | kkkk     |  |  |  |

| Description:     |         | The conter<br>eight-bit lit<br>W. |              |     |    |          |  |  |  |

| Words:           |         | 1                                 | 1            |     |    |          |  |  |  |

| Cycles:          |         | 1                                 |              |     |    |          |  |  |  |

| Q Cycle Activi   | ty:     |                                   |              |     |    |          |  |  |  |

| Q1               |         | Q2                                | Q3           | 3   | Q4 |          |  |  |  |

| Decod            | е       | Read<br>literal 'k'               | Proce<br>Dat |     | Wr | ite to W |  |  |  |

| Example:         |         | IORLW                             | 35h          |     |    |          |  |  |  |

| Before Ins       | structi | ion                               |              |     |    |          |  |  |  |

| W<br>After Instr | uctior  | = 9Ah<br>n                        |              |     |    |          |  |  |  |

| IORWF              | Inclusive OR W with f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                      |            |                       |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------|-----------------------|

| Syntax:            | IORWF f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IORWF f {,d {,a}}    |            |                       |

| Operands:          | $0 \le f \le 255$<br>$d \in [0, 1]$<br>$a \in [0, 1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                      |            |                       |

| Operation:         | (W) .OR. (f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $) \rightarrow dest$ |            |                       |

| Status Affected:   | N, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | N, Z                 |            |                       |

| Encoding:          | 0001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 00da                 | ffff       | ffff                  |

|                    | Inclusive OR W with register 'f'. If 'd' is<br>'0', the result is placed in W. If 'd' is '1',<br>the result is placed back in register 'f'<br>(default).<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 22.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                      |            |                       |

| Words:             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |            |                       |

| Cycles:            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |            |                       |

| Q Cycle Activity:  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |            |                       |

| Q1                 | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Q3                   | . <u> </u> | Q4                    |

| Decode             | Read<br>register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Proce<br>Dat         |            | Vrite to<br>stination |

| Example:           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ESULT,               | 0, 1       |                       |

| Before Instruction |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |            |                       |

RESULT =

=

=

W

W

After Instruction RESULT = 13h

91h

13h

93h

W

= BFh

| SUBLW                                                            | Subtrac                         | Subtract W from Literal         |           |   |  |

|------------------------------------------------------------------|---------------------------------|---------------------------------|-----------|---|--|

| Syntax:                                                          | SUBLW                           | SUBLW k                         |           |   |  |

| Operands:                                                        | $0 \le k \le 25$                | $0 \le k \le 255$               |           |   |  |

| Operation:                                                       | $k-(W) \rightarrow$             | $k - (W) \rightarrow W$         |           |   |  |

| Status Affected:                                                 | N, OV, C,                       | N, OV, C, DC, Z                 |           |   |  |

| Encoding:                                                        | 0000                            | 0000 1000 kkkk kkkk             |           |   |  |

| Description                                                      |                                 | acted from the The result is pl |           | • |  |

| Words:                                                           | 1                               |                                 |           |   |  |

| Cycles:                                                          | 1                               |                                 |           |   |  |

| Q Cycle Activity:                                                |                                 |                                 |           |   |  |

| Q1                                                               | Q2                              | Q3                              | Q4        |   |  |

| Decode                                                           | Read<br>literal 'k'             | Process<br>Data                 | Write to  | W |  |

| Example 1:                                                       | SUBLW                           | 02h                             |           |   |  |

| Before Instruc<br>W<br>C<br>After Instructio<br>W<br>C<br>Z<br>N | = 01h<br>= ?<br>on<br>= 01h     | esult is positive               | 9         |   |  |

| Example 2:                                                       | SUBLW                           | 02h                             |           |   |  |

| Before Instruc<br>W<br>C<br>After Instructio<br>W<br>C<br>Z<br>N | = 02h<br>= ?<br>on<br>= 00h     | esult is zero                   |           |   |  |

| Example 3:                                                       | SUBLW                           | 02h                             |           |   |  |

| Before Instruc<br>W<br>C<br>After Instructic<br>W<br>C<br>Z<br>N | = 03h<br>= ?<br>on<br>= FFh ; ( | 2's compleme<br>esult is negati | nt)<br>ve |   |  |

| SUBWF                                                                                                                                                                                                                                                                                                                                                                                                                                               | Subtract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | W from f                                                                                                                                                                                                                            |                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                                                                                                                                                                                                                                                                                                                                                                             | SUBWF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | f {,d {,a}}                                                                                                                                                                                                                         |                                                                                                                                                    |

| Operands:                                                                                                                                                                                                                                                                                                                                                                                                                                           | $0 \le f \le 255$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                     |                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $d \in [0, 1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                     |                                                                                                                                                    |

| Orrentierer                                                                                                                                                                                                                                                                                                                                                                                                                                         | $\mathbf{a} \in [0, 1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                     |                                                                                                                                                    |

| Operation:                                                                                                                                                                                                                                                                                                                                                                                                                                          | (f) – (W) –                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                     |                                                                                                                                                    |

| Status Affected:                                                                                                                                                                                                                                                                                                                                                                                                                                    | N, OV, C,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                     |                                                                                                                                                    |