Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 32                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 13x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

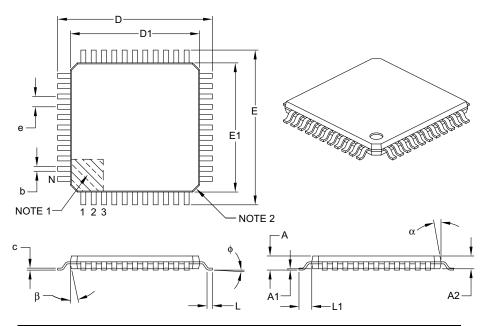

| Package / Case             | 44-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 44-QFN (8x8)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf45j10-i-ml |

#### 3.6.1 OSCILLATOR CONTROL REGISTER

The OSCCON register (Register 3-2) controls several aspects of the device clock's operation, both in full-power operation and in power-managed modes.

The System Clock Select bits, SCS<1:0>, select the clock source. The available clock sources are the primary clock (defined by the FOSC<2:0> Configuration bits), the secondary clock (Timer1 oscillator) and the internal oscillator. The clock source changes after one or more of the bits are written to, following a brief clock transition interval.

The OSTS (OSCCON<3>) and T1RUN (T1CON<6>) bits indicate which clock source is currently providing the device clock. The OSTS bit indicates that the Oscillator Start-up Timer (OST) has timed out and the primary clock is providing the device clock in primary clock modes. The T1RUN bit indicates when the Timer1 oscillator is providing the device clock in secondary clock modes. In power-managed modes, only one of these bits will be set at any time. If neither of these bits is set, the INTRC is providing the clock, or the internal oscillator has just started and is not yet stable.

The IDLEN bit determines if the device goes into Sleep mode or one of the Idle modes when the SLEEP instruction is executed.

The use of the flag and control bits in the OSCCON register is discussed in more detail in **Section 4.0** "Power-Managed Modes".

- Note 1: The Timer1 oscillator must be enabled to select the secondary clock source. The Timer1 oscillator is enabled by setting the T1OSCEN bit in the Timer1 Control register (T1CON<3>). If the Timer1 oscillator is not enabled, then any attempt to select a secondary clock source when executing a SLEEP instruction will be ignored.

- 2: It is recommended that the Timer1 oscillator be operating and stable before executing the SLEEP instruction or a very long delay may occur while the Timer1 oscillator starts.

# 3.6.1.1 System Clock Selection and the FOSC2 Configuration Bit

The SCS bits are cleared on all forms of Reset. In the device's default configuration, this means the primary oscillator defined by FOSC<1:0> (that is, one of the HC or EC modes) is used as the primary clock source on device Resets.

The default clock configuration on Reset can be changed with the FOSC2 Configuration bit. The effect of this bit is to set the clock source selected when SCS<1:0> = 00. When FOSC2 = 1 (default), the oscillator source defined by FOSC<1:0> is selected whenever SCS<1:0> = 00. When FOSC2 = 0, the INTRC oscillator is selected whenever SCS<1:0> = 00. Because the SCS bits are cleared on Reset, the FOSC2 setting also changes the default oscillator mode on Reset.

Regardless of the setting of FOSC2, INTRC will always be enabled on device power-up. It will serve as the clock source until the device has loaded its configuration values from memory. It is at this point that the FOSC Configuration bits are read and the oscillator selection of operational mode is made.

Note that either the primary clock or the internal oscillator will have two bit setting options, at any given time, depending on the setting of FOSC2.

#### 3.6.2 OSCILLATOR TRANSITIONS

PIC18F45J10 family devices contain circuitry to prevent clock "glitches" when switching between clock sources. A short pause in the device clock occurs during the clock switch. The length of this pause is the sum of two cycles of the old clock source and three to four cycles of the new clock source. This formula assumes that the new clock source is stable.

Clock transitions are discussed in greater detail in Section 4.1.2 "Entering Power-Managed Modes".

#### 6.3.4 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. SFRs start at the top of data memory (FFFh) and extend downward to occupy the top half of Bank 15 (F80h to FFFh). A list of these registers is given in Table 6-2 and Table 6-3.

The SFRs can be classified into two sets: those associated with the "core" device functionality (ALU, Resets and interrupts) and those related to the peripheral functions. The Reset and Interrupt registers are described in their respective chapters, while the ALU's STATUS register is described later in this section. Registers related to the operation of a peripheral feature are described in the chapter for that peripheral.

The SFRs are typically distributed among the peripherals whose functions they control. Unused SFR locations are unimplemented and read as '0's.

TABLE 6-2: SPECIAL FUNCTION REGISTER MAP FOR PIC18F45J10 FAMILY DEVICES

| Address | Name                    | Address | Name                    | Address | Name                    | Address | Name                    |

|---------|-------------------------|---------|-------------------------|---------|-------------------------|---------|-------------------------|

| FFFh    | TOSU                    | FDFh    | INDF2 <sup>(1)</sup>    | FBFh    | CCPR1H                  | F9Fh    | IPR1                    |

| FFEh    | TOSH                    | FDEh    | POSTINC2 <sup>(1)</sup> | FBEh    | CCPR1L                  | F9Eh    | PIR1                    |

| FFDh    | TOSL                    | FDDh    | POSTDEC2 <sup>(1)</sup> | FBDh    | CCP1CON                 | F9Dh    | PIE1                    |

| FFCh    | STKPTR                  | FDCh    | PREINC2 <sup>(1)</sup>  | FBCh    | CCPR2H                  | F9Ch    | (2)                     |

| FFBh    | PCLATU                  | FDBh    | PLUSW2 <sup>(1)</sup>   | FBBh    | CCPR2L                  | F9Bh    | (2)                     |

| FFAh    | PCLATH                  | FDAh    | FSR2H                   | FBAh    | CCP2CON                 | F9Ah    | (2)                     |

| FF9h    | PCL                     | FD9h    | FSR2L                   | FB9h    | (2)                     | F99h    | (2)                     |

| FF8h    | TBLPTRU                 | FD8h    | STATUS                  | FB8h    | BAUDCON                 | F98h    | (2)                     |

| FF7h    | TBLPTRH                 | FD7h    | TMR0H                   | FB7h    | ECCP1DEL <sup>(3)</sup> | F97h    | (2)                     |

| FF6h    | TBLPTRL                 | FD6h    | TMR0L                   | FB6h    | ECCP1AS <sup>(3)</sup>  | F96h    | TRISE <sup>(3)</sup>    |

| FF5h    | TABLAT                  | FD5h    | T0CON                   | FB5h    | CVRCON                  | F95h    | TRISD <sup>(3)</sup>    |

| FF4h    | PRODH                   | FD4h    | (2)                     | FB4h    | CMCON                   | F94h    | TRISC                   |

| FF3h    | PRODL                   | FD3h    | OSCCON                  | FB3h    | (2)                     | F93h    | TRISB                   |

| FF2h    | INTCON                  | FD2h    | (2)                     | FB2h    | (2)                     | F92h    | TRISA                   |

| FF1h    | INTCON2                 | FD1h    | WDTCON                  | FB1h    | (2)                     | F91h    | (2)                     |

| FF0h    | INTCON3                 | FD0h    | RCON                    | FB0h    | SPBRGH                  | F90h    | (2)                     |

| FEFh    | INDF0 <sup>(1)</sup>    | FCFh    | TMR1H                   | FAFh    | SPBRG                   | F8Fh    | (2)                     |

| FEEh    | POSTINC0 <sup>(1)</sup> | FCEh    | TMR1L                   | FAEh    | RCREG                   | F8Eh    | SSP2BUF                 |

| FEDh    | POSTDEC0 <sup>(1)</sup> | FCDh    | T1CON                   | FADh    | TXREG                   | F8Dh    | LATE <sup>(3)</sup>     |

| FECh    | PREINC0 <sup>(1)</sup>  | FCCh    | TMR2                    | FACh    | TXSTA                   | F8Ch    | LATD <sup>(3)</sup>     |

| FEBh    | PLUSW0 <sup>(1)</sup>   | FCBh    | PR2                     | FABh    | RCSTA                   | F8Bh    | LATC                    |

| FEAh    | FSR0H                   | FCAh    | T2CON                   | FAAh    | (2)                     | F8Ah    | LATB                    |

| FE9h    | FSR0L                   | FC9h    | SSP1BUF                 | FA9h    | (2)                     | F89h    | LATA                    |

| FE8h    | WREG                    | FC8h    | SSP1ADD                 | FA8h    | (2)                     | F88h    | SSP2ADD <sup>(3)</sup>  |

| FE7h    | INDF1 <sup>(1)</sup>    | FC7h    | SSP1STAT                | FA7h    | EECON2 <sup>(1)</sup>   | F87h    | SSP2STAT <sup>(3)</sup> |

| FE6h    | POSTINC1 <sup>(1)</sup> | FC6h    | SSP1CON1                | FA6h    | EECON1                  | F86h    | SSP2CON1 <sup>(3)</sup> |

| FE5h    | POSTDEC1 <sup>(1)</sup> | FC5h    | SSP1CON2                | FA5h    | IPR3                    | F85h    | SSP2CON2 <sup>(3)</sup> |

| FE4h    | PREINC1 <sup>(1)</sup>  | FC4h    | ADRESH                  | FA4h    | PIR3                    | F84h    | PORTE <sup>(3)</sup>    |

| FE3h    | PLUSW1 <sup>(1)</sup>   | FC3h    | ADRESL                  | FA3h    | PIE3                    | F83h    | PORTD <sup>(3)</sup>    |

| FE2h    | FSR1H                   | FC2h    | ADCON0                  | FA2h    | IPR2                    | F82h    | PORTC                   |

| FE1h    | FSR1L                   | FC1h    | ADCON1                  | FA1h    | PIR2                    | F81h    | PORTB                   |

| FE0h    | BSR                     | FC0h    | ADCON2                  | FA0h    | PIE2                    | F80h    | PORTA                   |

Note 1: This is not a physical register.

- 2: Unimplemented registers are read as '0'.

- 3: This register is not available in 28-pin devices.

TABLE 6-3: REGISTER FILE SUMMARY (PIC18F24J10/25J10/44J10/45J10) (CONTINUED)

|                      |                      |                |                           | 1171171               |                       |                       |                            | /(                 | 11111000)         |                  |

|----------------------|----------------------|----------------|---------------------------|-----------------------|-----------------------|-----------------------|----------------------------|--------------------|-------------------|------------------|

| File Name            | Bit 7                | Bit 6          | Bit 5                     | Bit 4                 | Bit 3                 | Bit 2                 | Bit 1                      | Bit 0              | Value on POR, BOR | Details on page: |

| SPBRGH               | EUSART Bau           | ıd Rate Gener  | ator Register I           | High Byte             |                       |                       |                            |                    | 0000 0000         | 49, 198          |

| SPBRG                | EUSART Bau           | ıd Rate Gener  | ator Register I           | Low Byte              |                       |                       |                            |                    | 0000 0000         | 49, 198          |

| RCREG                | EUSART Red           | eive Register  |                           |                       |                       |                       |                            |                    | 0000 0000         | 49, 205          |

| TXREG                | EUSART Trai          | nsmit Register | -                         |                       |                       |                       |                            |                    |                   | 49, 203          |

| TXSTA                | CSRC                 | TX9            | TXEN                      | SYNC                  | SENDB                 | BRGH                  | TRMT                       | TX9D               | 0000 0010         | 49, 196          |

| RCSTA                | SPEN                 | RX9            | SREN                      | CREN                  | ADDEN                 | FERR                  | OERR                       | RX9D               | 0000 000x         | 49, 195          |

| EECON2               | EEPROM Co            | ntrol Register | 2 (not a physic           | cal register)         |                       |                       |                            |                    | 0000 0000         | 49, 72           |

| EECON1               | _                    | _              | _                         | FREE                  | WRERR                 | WREN                  | WR                         | _                  | 0 x00-            | 49, 74           |

| IPR3                 | SSP2IP               | BCL2IP         | _                         | _                     | _                     | _                     | _                          | _                  | 11                | 49, 94           |

| PIR3                 | SSP2IF               | BCL2IF         | _                         | _                     | _                     | _                     | _                          | _                  | 00                | 49, 90           |

| PIE3                 | SSP2IE               | BCL2IE         | _                         | _                     | _                     | _                     | _                          | _                  | 00                | 49, 92           |

| IPR2                 | OSCFIP               | CMIP           | _                         | _                     | BCL1IP                | _                     | _                          | CCP2IP             | 11 11             | 49, 93           |

| PIR2                 | OSCFIF               | CMIF           | _                         | _                     | BCL1IF                | _                     | _                          | CCP2IF             | 00 00             | 49, 89           |

| PIE2                 | OSCFIE               | CMIE           | _                         | _                     | BCL1IE                | _                     | _                          | CCP2IE             | 00 00             | 49, 91           |

| IPR1                 | PSPIP <sup>(2)</sup> | ADIP           | RCIP                      | TXIP                  | SSP1IP                | CCP1IP                | TMR2IP                     | TMR1IP             | 1111 1111         | 49, 92           |

| PIR1                 | PSPIF <sup>(2)</sup> | ADIF           | RCIF                      | TXIF                  | SSP1IF                | CCP1IF                | TMR2IF                     | TMR1IF             | 0000 0000         | 49, 88           |

| PIE1                 | PSPIE <sup>(2)</sup> | ADIE           | RCIE                      | TXIE                  | SSP1IE                | CCP1IE                | TMR2IE                     | TMR1IE             | 0000 0000         | 49, 91           |

| TRISE <sup>(2)</sup> | IBF                  | OBF            | IBOV                      | PSPMODE               | _                     | TRISE2                | TRISE1                     | TRISE0             | 0000 -111         | 50, 112          |

| TRISD <sup>(2)</sup> | PORTD Data           | Direction Cor  | trol Register             |                       |                       |                       |                            |                    | 1111 1111         | 50, 107          |

| TRISC                | PORTC Data           | Direction Cor  | trol Register             |                       |                       |                       |                            |                    | 1111 1111         | 50, 104          |

| TRISB                | PORTB Data           | Direction Con  | trol Register             |                       |                       |                       |                            |                    | 1111 1111         | 50, 101          |

| TRISA                | _                    | _              | TRISA5                    | _                     | TRISA3                | TRISA2                | TRISA1                     | TRISA0             | 1- 1111           | 50, 98           |

| SSP2BUF              | MSSP2 Rece           | ive Buffer/Tra | nsmit Register            |                       |                       |                       |                            |                    | xxxx xxxx         | 50, 158          |

| LATE <sup>(2)</sup>  | _                    | _              | _                         | _                     | _                     |                       | Latch Registe              |                    | xxx               | 50, 110          |

| LATD <sup>(2)</sup>  | PORTD Data           | Latch Registe  | er (Read and V            | Vrite to Data L       | atch)                 |                       |                            |                    | xxxx xxxx         | 50, 107          |

| LATC                 | PORTC Data           | Latch Registe  | er (Read and V            | Vrite to Data L       | atch)                 |                       |                            |                    | xxxx xxxx         | 50, 104          |

| LATB                 | PORTB Data           | Latch Registe  | er (Read and V            | Vrite to Data L       | atch)                 |                       |                            |                    | xxxx xxxx         | 50, 101          |

| LATA                 | _                    | _              | PORTA Data                | Latch Registe         | r (Read and V         | Vrite to Data La      | atch)                      |                    | xx xxxx           | 50, 98           |

| SSP2ADD              | MSSP2 Addr           | ess Register i | n I <sup>2</sup> C™ Slave | mode. MSSP2           | Baud Rate R           | eload Register        | in I <sup>2</sup> C Master | mode.              | 0000 0000         | 50, 158          |

| SSP2STAT             | SMP                  | CKE            | D/Ā                       | Р                     | S                     | R/W                   | UA                         | BF                 | 0000 0000         | 50, 150,<br>160  |

| SSP2CON1             | WCOL                 | SSPOV          | SSPEN                     | CKP                   | SSPM3                 | SSPM2                 | SSPM1                      | SSPM0              | 0000 0000         | 50, 151,<br>161  |

| SSP2CON2             | GCEN                 | ACKSTAT        | ACKDT                     | ACKEN                 | RCEN                  | PEN                   | RSEN                       | SEN                | 0000 0000         | 50, 164          |

|                      | GCEN                 | ACKSTAT        | ADMSK5 <sup>(3)</sup>     | ADMSK4 <sup>(3)</sup> | ADMSK3 <sup>(3)</sup> | ADMSK2 <sup>(3)</sup> | ADMSK1 <sup>(3)</sup>      | SEN                | 0000 0000         | 48, 163          |

| PORTE <sup>(2)</sup> | _                    | _              | _                         | _                     | _                     | RE2 <sup>(2)</sup>    | RE1 <sup>(2)</sup>         | RE0 <sup>(2)</sup> | xxx               | 50, 110          |

| PORTD <sup>(2)</sup> | RD7                  | RD6            | RD5                       | RD4                   | RD3                   | RD2                   | RD1                        | RD0                | xxxx xxxx         | 50, 107          |

| PORTC                | RC7                  | RC6            | RC5                       | RC4                   | RC3                   | RC2                   | RC1                        | RC0                | xxxx xxxx         | 50, 104          |

| PORTB                | RB7                  | RB6            | RB5                       | RB4                   | RB3                   | RB2                   | RB1                        | RB0                | xxxx xxxx         | 50, 101          |

| PORTA                | _                    | _              | RA5                       |                       | RA3                   | RA2                   | RA1                        | RA0                | 0- 0000           | 50, 98           |

| l amandi             |                      |                | d =nim.nla                | monted -              | alua dananda          | on condition          |                            |                    |                   |                  |

Legend:

- x = unknown, u = unchanged, = unimplemented, q = value depends on condition

- Note 1: See Section 5.4 "Brown-out Reset (BOR) (PIC18F2XJ10/4XJ10 Devices Only)".

- 2: These registers and/or bits are not implemented on 28-pin devices and are read as '0'. Reset values are shown for 40/44-pin devices; individual unimplemented bits should be interpreted as '-'.

- 3: Alternate names and definitions for these bits when the MSSP module is operating in I<sup>2</sup>C™ Slave mode. See **Section 16.4.3.2 "Address Masking"** for details.

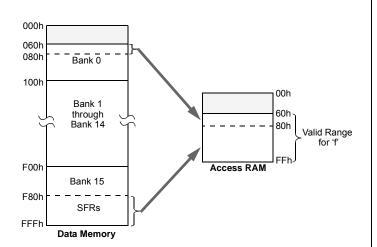

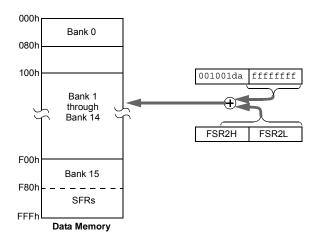

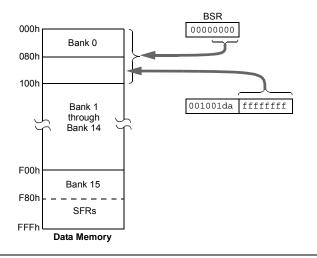

# FIGURE 6-9: COMPARING ADDRESSING OPTIONS FOR BIT-ORIENTED AND BYTE-ORIENTED INSTRUCTIONS (EXTENDED INSTRUCTION SET ENABLED)

Example Instruction: ADDWF, f, d, a (Opcode: 0010 01da fffff fffff)

#### When 'a' = 0 and $f \ge 60h$ :

The instruction executes in Direct Forced mode. 'f' is interpreted as a location in the Access RAM between 060h and 0FFh. This is the same as locations 060h to 07Fh (Bank 0) and F80h to FFFh (Bank 15) of data memory.

Locations below 60h are not available in this addressing mode.

#### When 'a' = 0 and $f \le 5Fh$ :

The instruction executes in Indexed Literal Offset mode. 'f' is interpreted as an offset to the address value in FSR2. The two are added together to obtain the address of the target register for the instruction. The address can be anywhere in the data memory space.

Note that in this mode, the correct syntax is now:

ADDWF [k], d

where 'k' is the same as 'f'.

#### When 'a' = 1 (all values of f):

The instruction executes in Direct mode (also known as Direct Long mode). 'f' is interpreted as a location in one of the 16 banks of the data memory space. The bank is designated by the Bank Select Register (BSR). The address can be in any implemented bank in the data memory space.

### 7.4 Erasing Flash Program Memory

The minimum erase block is 1024 bytes. Only through the use of an external programmer, or through ICSP control, can larger blocks of program memory be Bulk Erased. Word Erase in the Flash array is not supported.

When initiating an erase sequence from the micro-controller itself, a block of 1024 bytes of program memory is erased. The Most Significant 7 bits of the TBLPTR<21:10> point to the block being erased. TBLPTR<9:0> are ignored.

The EECON1 register commands the erase operation. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation.

For protection, the write initiate sequence for EECON2 must be used.

A long write is necessary for erasing the internal Flash. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

# 7.4.1 FLASH PROGRAM MEMORY ERASE SEQUENCE

The sequence of events for erasing a block of internal program memory location is:

- Load Table Pointer register with address of the block being erased.

- 2. Set the WREN and FREE bits (EECON1<2,4>) to enable the erase operation.

- 3. Disable interrupts.

- 4. Write 55h to EECON2.

- 5. Write 0AAh to EECON2.

- 6. Set the WR bit. This will begin the erase cycle.

- The CPU will stall for duration of the erase for TIE (see parameter D133B).

- 8. Re-enable interrupts.

#### EXAMPLE 7-2: ERASING A FLASH PROGRAM MEMORY BLOCK

|                      | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF | CODE_ADDR_UPPER TBLPTRU CODE_ADDR_HIGH TBLPTRH | ; load TBLPTR with the base<br>; address of the memory block                      |

|----------------------|----------------------------------|------------------------------------------------|-----------------------------------------------------------------------------------|

|                      | MOVLW<br>MOVWF                   | CODE_ADDR_LOW TBLPTRL                          |                                                                                   |

| ERASE_ROW            |                                  |                                                |                                                                                   |

|                      | BSF<br>BSF<br>BCF                | EECON1, WREN EECON1, FREE INTCON, GIE          | <pre>; enable write to memory ; enable Erase operation ; disable interrupts</pre> |

| Required<br>Sequence | MOVLW<br>MOVWF<br>MOVWF<br>BSF   | 55h<br>EECON2<br>0AAh<br>EECON2<br>EECON1, WR  | <pre>; write 55h ; write 0AAh ; start erase (CPU stall)</pre>                     |

|                      | BSF                              | INTCON, GIE                                    | ; re-enable interrupts                                                            |

#### 9.6 INTx Pin Interrupts

External interrupts on the RB0/INT0, RB1/INT1 and RB2/INT2 pins are edge-triggered. If the corresponding INTEDGx bit in the INTCON2 register is set (= 1), the interrupt is triggered by a rising edge; if the bit is clear, the trigger is on the falling edge. When a valid edge appears on the RBx/INTx pin, the corresponding flag bit, INTxIF, is set. This interrupt can be disabled by clearing the corresponding enable bit, INTxIE. Flag bit, INTxIF, must be cleared in software in the Interrupt Service Routine before re-enabling the interrupt.

All external interrupts (INT0, INT1 and INT2) can wake-up the processor from the power-managed modes if bit INTxIE was set prior to going into the power-managed modes. If the Global Interrupt Enable bit, GIE, is set, the processor will branch to the interrupt vector following wake-up.

Interrupt priority for INT1 and INT2 is determined by the value contained in the interrupt priority bits, INT1IP (INTCON3<6>) and INT2IP (INTCON3<7>). There is no priority bit associated with INT0. It is always a high-priority interrupt source.

### 9.7 TMR0 Interrupt

In 8-bit mode (which is the default), an overflow in the TMR0 register (FFh  $\rightarrow$  00h) will set flag bit, TMR0IF. In 16-bit mode, an overflow in the TMR0H:TMR0L register pair (FFFFh  $\rightarrow$  0000h) will set TMR0IF. The interrupt can be enabled/disabled by setting/clearing enable bit, TMR0IE (INTCON<5>). Interrupt priority for Timer0 is determined by the value contained in the interrupt priority bit, TMR0IP (INTCON2<2>). See **Section 11.0** "Timer0 Module" for further details on the Timer0 module

### 9.8 PORTB Interrupt-on-Change

An input change on PORTB<7:4> sets flag bit, RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit, RBIE (INTCON<3>). Interrupt priority for PORTB interrupt-on-change is determined by the value contained in the interrupt priority bit, RBIP (INTCON2<0>).

### 9.9 Context Saving During Interrupts

During interrupts, the return PC address is saved on the stack. Additionally, the WREG, STATUS and BSR registers are saved on the Fast Return Stack. If a fast return from interrupt is not used (see **Section 6.3** "**Data Memory Organization**"), the user may need to save the WREG, STATUS and BSR registers on entry to the Interrupt Service Routine. Depending on the user's application, other registers may also need to be saved. Example 9-1 saves and restores the WREG, STATUS and BSR registers during an Interrupt Service Routine.

#### EXAMPLE 9-1: SAVING STATUS, WREG AND BSR REGISTERS IN RAM

```

MOVWF

W TEMP

; W_TEMP is in virtual bank

MOVEE

STATUS, STATUS_TEMP

; STATUS_TEMP located anywhere

MOVFF

BSR, BSR TEMP

; BSR_TMEP located anywhere

; USER ISR CODE

MOVFF

BSR_TEMP, BSR

; Restore BSR

MOVF

; Restore WREG

W TEMP, W

STATUS_TEMP, STATUS

MOVEE

; Restore STATUS

```

TABLE 10-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Name   | Bit 7 | Bit 6 | Bit 5    | Bit 4       | Bit 3        | Bit 2       | Bit 1       | Bit 0  | Reset<br>Values<br>on page |

|--------|-------|-------|----------|-------------|--------------|-------------|-------------|--------|----------------------------|

| PORTA  | _     | _     | RA5      | _           | RA3          | RA2         | RA1         | RA0    | 50                         |

| LATA   | _     | _     | PORTA Da | ta Latch Re | gister (Read | d and Write | to Data Lat | ch)    | 50                         |

| TRISA  | _     | _     | TRISA5   | _           | TRISA3       | TRISA2      | TRISA1      | TRISA0 | 50                         |

| ADCON1 | _     | _     | VCFG1    | VCFG0       | PCFG3        | PCFG2       | PCFG1       | PCFG0  | 48                         |

| CMCON  | C2OUT | C10UT | C2INV    | C1INV       | CIS          | CM2         | CM1         | CM0    | 49                         |

| CVRCON | CVREN | CVROE | CVRR     | CVRSS       | CVR3         | CVR2        | CVR1        | CVR0   | 49                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PORTA.

#### 16.4.2 OPERATION

The MSSP module functions are enabled by setting the MSSP Enable bit, SSPEN (SSPxCON1<5>).

The SSPxCON1 register allows control of the  $\rm I^2C$  operation. Four mode selection bits (SSPxCON1<3:0>) allow one of the following  $\rm I^2C$  modes to be selected:

- I<sup>2</sup>C Master mode, clock = (Fosc/4) x (SSPxADD + 1)

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Firmware Controlled Master mode, slave is Idle

Selection of any I<sup>2</sup>C mode, with the SSPEN bit set, forces the SCLx and SDAx pins to be open-drain, provided these pins are programmed to inputs by setting the appropriate TRISC or TRISD bits. To ensure proper operation of the module, pull-up resistors must be provided externally to the SCLx and SDAx pins.

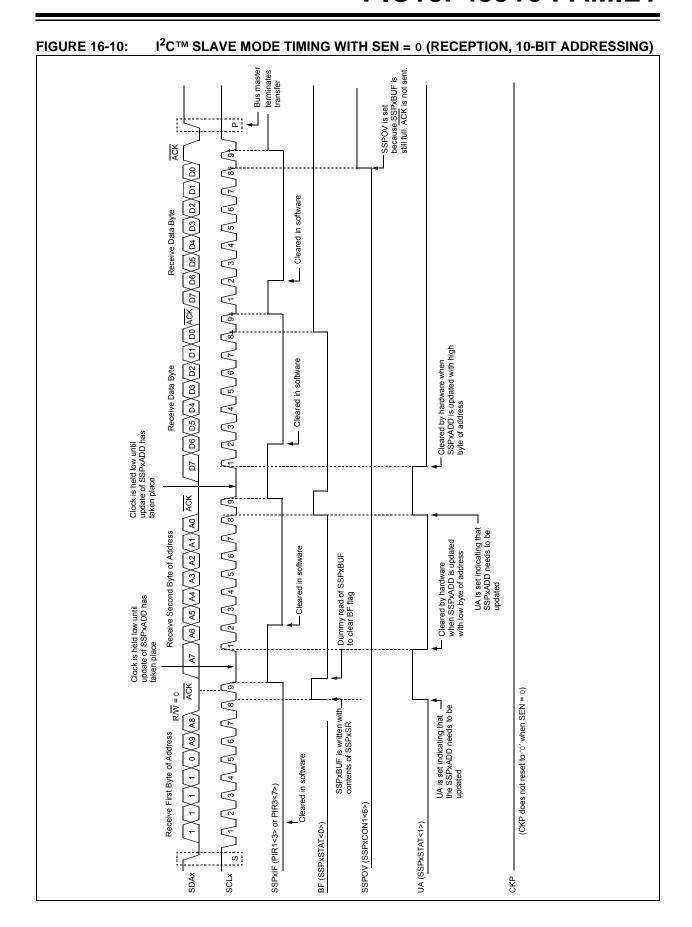

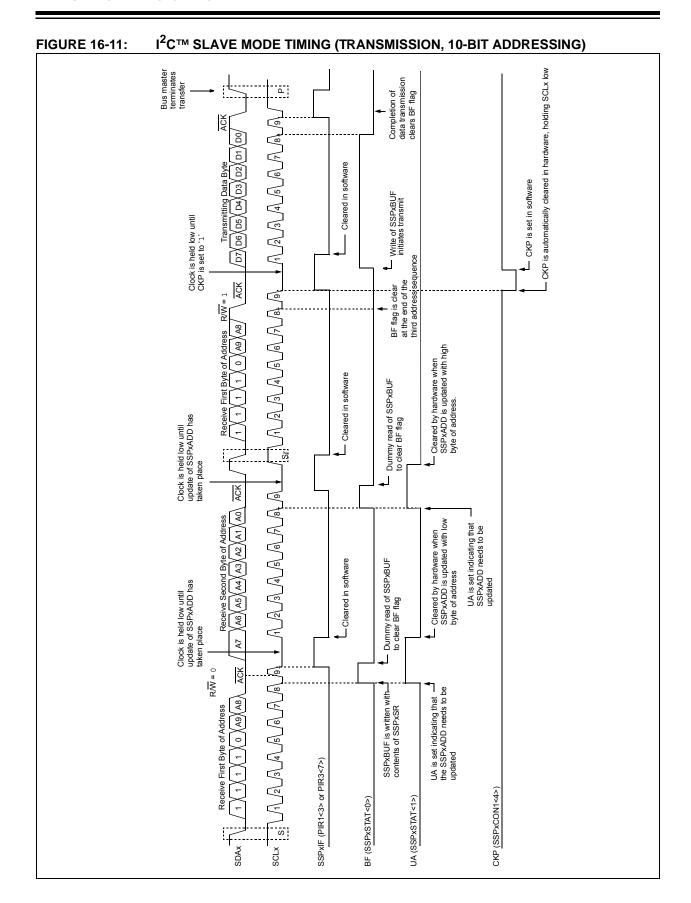

#### 16.4.3 SLAVE MODE

In Slave mode, the SCLx and SDAx pins must be configured as inputs (TRISC<4:3> set). The MSSP module will override the input state with the output data when required (slave-transmitter).

The I<sup>2</sup>C Slave mode hardware will always generate an interrupt on an exact address match. In addition, address masking will also allow the hardware to generate an interrupt for more than one address (up to 31 in 7-bit addressing and up to 63 in 10-bit addressing). Through the mode select bits, the user can also choose to interrupt on Start and Stop bits.

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge (ACK) pulse and load the SSPxBUF register with the received value currently in the SSPxSR register.

Any combination of the following conditions will cause the MSSP module not to give this  $\overline{ACK}$  pulse:

- The Buffer Full bit, BF (SSPxSTAT<0>), was set before the transfer was received.

- The MSSP Overflow bit, SSPOV (SSPxCON1<6>), was set before the transfer was received.

In this case, the SSPxSR register value is not loaded into the SSPxBUF, but the SSPxIF bit is set. The BF bit is cleared by reading the SSPxBUF register, while the SSPOV bit is cleared through software.

The SCLx clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirement of the MSSP module, are shown in timing parameter 100 and parameter 101.

#### 16.4.3.1 Addressing

Once the MSSP module has been enabled, it waits for a Start condition to occur. Following the Start condition, the 8 bits are shifted into the SSPxSR register. All incoming bits are sampled with the rising edge of the clock (SCLx) line. The value of register SSPxSR<7:1> is compared to the value of the SSPxADD register. The address is compared on the falling edge of the eighth clock (SCLx) pulse. If the addresses match and the BF and SSPOV bits are clear, the following events occur:

- The SSPxSR register value is loaded into the SSPxBUF register.

- 2. The Buffer Full bit, BF, is set.

- 3. An ACK pulse is generated.

- 4. The MSSP Interrupt Flag bit, SSPxIF, is set (and interrupt is generated, if enabled) on the falling edge of the ninth SCLx pulse.

In 10-Bit Addressing mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit  $R/\overline{W}$  (SSPxSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '11110 A9 A8 0', where 'A9' and 'A8' are the two MSbs of the address. The sequence of events for 10-Bit Addressing mode is as follows, with steps 7 through 9 for the slave-transmitter:

- Receive first (high) byte of address (bits, SSPxIF, BF and UA (SSPxSTAT<1>), are set).

- Update the SSPxADD register with second (low) byte of address (clears bit, UA, and releases the SCLx line).

- Read the SSPxBUF register (clears bit, BF) and clear flag bit, SSPxIF.

- 4. Receive second (low) byte of address (bits, SSPxIF, BF and UA, are set).

- Update the SSPxADD register with the first (high) byte of address. If match releases SCLx line, this will clear bit, UA.

- 6. Read the SSPxBUF register (clears bit, BF) and clear flag bit, SSPxIF.

- 7. Receive Repeated Start condition.

- 8. Receive first (high) byte of address (bits, SSPxIF and BF, are set).

- 9. Read the SSPxBUF register (clears bit, BF) and clear flag bit, SSPxIF.

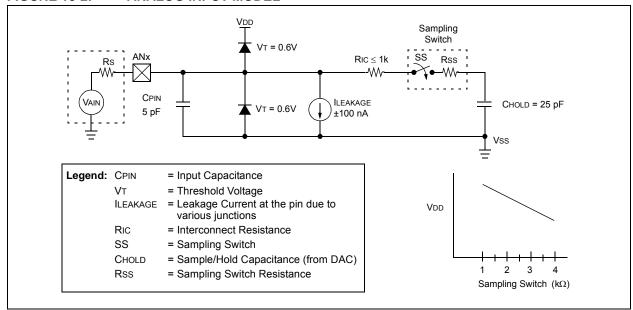

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as an input. To determine acquisition time, see **Section 18.1** "A/D Acquisition Requirements". After this acquisition time has elapsed, the A/D conversion can be started. An acquisition time can be programmed to occur between setting the GO/DONE bit and the actual start of the conversion.

The following steps should be followed to do an A/D conversion:

- 1. Configure the A/D module:

- Configure analog pins, voltage reference and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D acquisition time (ADCON2)

- Select A/D conversion clock (ADCON2)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- · Clear ADIF bit

- · Set ADIE bit

- · Set GIE bit

- 3. Wait the required acquisition time (if required).

- 4. Start conversion:

- Set GO/DONE bit (ADCON0<1>)

- 5. Wait for A/D conversion to complete, by either:

- Polling for the GO/DONE bit to be cleared OR

- · Waiting for the A/D interrupt

- Read A/D Result registers (ADRESH:ADRESL); clear bit, ADIF, if required.

- For next conversion, go to step 1 or step 2, as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2 TAD is required before next acquisition starts.

#### FIGURE 18-2: ANALOG INPUT MODEL

**BNC Branch if Not Carry**

Syntax: BNC n

Operands:  $\text{-}128 \leq n \leq 127$ Operation: if Carry bit is '0',  $(PC) + 2 + 2n \rightarrow PC$

Status Affected: None

Encoding: 1110 0011 nnnn nnnn

Description: If the Carry bit is '0', then the program

will branch.

The 2's complement number, '2n', is added to the PC. Since the PC will have incremented to fetch the next

instruction, the new address will be PC + 2 + 2n. This instruction is then a

two-cycle instruction.

Words: 1 Cycles: 1(2)

Q Cycle Activity:

If Jump:

| Q1        | Q2           | Q3        | Q4          |

|-----------|--------------|-----------|-------------|

| Decode    | Read literal | Process   | Write to PC |

|           | ʻn'          | Data      |             |

| No        | No           | No        | No          |

| operation | operation    | operation | operation   |

If No Jump:

| Q1     | Q2           | Q3      | Q4        |

|--------|--------------|---------|-----------|

| Decode | Read literal | Process | No        |

|        | ʻn'          | Data    | operation |

Example: HERE BNC Jump

Before Instruction

PC address (HERE)

After Instruction

If Carry PC

address (Jump)

If Carry

address (HERE + 2)

**BNN Branch if Not Negative**

Syntax: BNN n Operands:  $\text{-}128 \leq n \leq 127$

Operation: if Negative bit is '0',  $(PC) + 2 + 2n \rightarrow PC$

Status Affected: None

Encoding: 1110 0111 nnnn nnnn

Description: If the Negative bit is '0', then the

program will branch.

The 2's complement number, '2n', is added to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be

PC + 2 + 2n. This instruction is then a two-cycle instruction.

Words: 1

Cycles: 1(2)

Q Cycle Activity:

If Jump:

| Q1        | Q2           | Q3        | Q4          |

|-----------|--------------|-----------|-------------|

| Decode    | Read literal | Process   | Write to PC |

|           | ʻn'          | Data      |             |

| No        | No           | No        | No          |

| operation | operation    | operation | operation   |

If No Jump:

| Q1     | Q2           | Q3      | Q4        |

|--------|--------------|---------|-----------|

| Decode | Read literal | Process | No        |

|        | ʻn'          | Data    | operation |

Example: HERE BNN Jump

Before Instruction

PC address (HERE)

After Instruction

If Negative PC address (Jump)

If Negative PC

address (HERE + 2)

| BTFSC                                                                        | Bit Test Fil                                                                                                                                                                                                                 | e, Skip if Cle                       | ear                                                                                                                                                | BTFSS             | Bit Test Fil                                                                                                                                                                                                               | e, Skip if Se                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | t            |

|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Syntax:                                                                      | BTFSC f, b                                                                                                                                                                                                                   | {,a}                                 |                                                                                                                                                    | Syntax:           | BTFSS f, b                                                                                                                                                                                                                 | {,a}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |

| Operands:                                                                    | $\begin{array}{l} 0 \leq f \leq 255 \\ 0 \leq b \leq 7 \\ a \in [0,1] \end{array}$                                                                                                                                           |                                      |                                                                                                                                                    | Operands:         | $0 \le f \le 255$<br>$0 \le b < 7$<br>$a \in [0,1]$                                                                                                                                                                        | 0 ≤ b < 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |

| Operation:                                                                   | skip if (f <b>)</b>                                                                                                                                                                                                          | = 0                                  |                                                                                                                                                    | Operation:        | skip if (f <b>)</b>                                                                                                                                                                                                        | = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |

| Status Affected:                                                             | None                                                                                                                                                                                                                         |                                      |                                                                                                                                                    | Status Affected:  | None                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |

| Encoding:                                                                    | 1011                                                                                                                                                                                                                         | bbba ff                              | ff ffff                                                                                                                                            | Encoding:         | 1010                                                                                                                                                                                                                       | bbba ffi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ff ffff      |

| Description:                                                                 | instruction is<br>the next instru<br>and a NOP is<br>this a two-cy<br>If 'a' is '0', th<br>'a' is '1', the<br>GPR bank (o<br>If 'a' is '0' an<br>set is enable<br>Indexed Liter<br>mode where<br>See Section<br>Bit-Oriented | BSR is used to                       | 'b' is '0', then during the n is discarded lead, making is selected. If select the distriction on operates in lessing n).  Oriented and in Indexed | Description:      | instruction is the next instruction is the next instruction and a NOP is this a two-cyt if 'a' is '0', the 'a' is '1', the I GPR bank (d If 'a' is '0' and set is enable in Indexed Li mode whene See Section Bit-Oriented | In 1010 bbba fffff fffff ffff bit 'b' in register 'f' is '1', then the next instruction is skipped. If bit 'b' is '1', the the next instruction fetched during the current instruction execution is discard and a NOP is executed instead, making this a two-cycle instruction. If 'a' is '0', the Access Bank is selected 'a' is '1', the BSR is used to select the GPR bank (default). If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever f ≤ 95 (5Fh). See Section 22.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details. |              |

| Words:                                                                       | 1                                                                                                                                                                                                                            |                                      |                                                                                                                                                    | Words:            | 1                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |

| Cycles:                                                                      | •                                                                                                                                                                                                                            | cles if skip and<br>2-word instruc   |                                                                                                                                                    | Cycles:           | by a                                                                                                                                                                                                                       | cles if skip and<br>2-word instruc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |

| Q Cycle Activity:                                                            |                                                                                                                                                                                                                              |                                      |                                                                                                                                                    | Q Cycle Activity  |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |

| Q1                                                                           | Q2                                                                                                                                                                                                                           | Q3                                   | Q4                                                                                                                                                 | Q1                | Q2                                                                                                                                                                                                                         | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Q4           |

| Decode                                                                       | Read<br>register 'f'                                                                                                                                                                                                         | Process<br>Data                      | No operation                                                                                                                                       | Decode            | Read register 'f'                                                                                                                                                                                                          | Process<br>Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | No operation |

| If skip:                                                                     | register i                                                                                                                                                                                                                   | Data                                 | operation                                                                                                                                          | If skip:          | register i                                                                                                                                                                                                                 | Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | operation    |

| Q1                                                                           | Q2                                                                                                                                                                                                                           | Q3                                   | Q4                                                                                                                                                 | Gp.               | Q2                                                                                                                                                                                                                         | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Q4           |

| No                                                                           | No                                                                                                                                                                                                                           | No                                   | No                                                                                                                                                 | No                | No                                                                                                                                                                                                                         | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | No           |

| operation                                                                    | operation                                                                                                                                                                                                                    | operation                            | operation                                                                                                                                          | operation         | n operation                                                                                                                                                                                                                | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | operation    |

| If skip and followed                                                         | by 2-word inst                                                                                                                                                                                                               | truction:                            |                                                                                                                                                    | If skip and follo | wed by 2-word in                                                                                                                                                                                                           | struction:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |

| Q1                                                                           | Q2                                                                                                                                                                                                                           | Q3                                   | Q4                                                                                                                                                 | Q1                | Q2                                                                                                                                                                                                                         | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Q4           |

| No                                                                           | No                                                                                                                                                                                                                           | No                                   | No                                                                                                                                                 | No                | No                                                                                                                                                                                                                         | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | No           |

| operation                                                                    | operation<br>No                                                                                                                                                                                                              | operation<br>No                      | operation<br>No                                                                                                                                    | operation         | n operation<br>No                                                                                                                                                                                                          | operation<br>No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | operation    |

| No operation                                                                 | operation                                                                                                                                                                                                                    | operation                            | operation                                                                                                                                          | No operation      | _                                                                                                                                                                                                                          | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | No operation |

| Example:  Before Instruction PC  After Instruction If FLAG<1 PC If FLAG<1 PC | FALSE : TRUE : ion = add                                                                                                                                                                                                     | ress (HERE) ress (TRUE) ress (FALSE) | , 1, 0                                                                                                                                             | If FLA            | FALSE : TRUE :  ruction = ad ction G<1> = 0; PC = ad G<1> = 1;                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Ε)           |

# 22.2.5 SPECIAL CONSIDERATIONS WITH MICROCHIP MPLAB® IDE TOOLS

The latest versions of Microchip's software tools have been designed to fully support the extended instruction set of the PIC18F45J10 family of devices. This includes the MPLAB C18 C compiler, MPASM assembly language and MPLAB Integrated Development Environment (IDE).

When selecting a target device for software development, MPLAB IDE will automatically set default Configuration bits for that device. The default setting for the XINST Configuration bit is '0', disabling the extended instruction set and Indexed Literal Offset Addressing mode. For proper execution of applications developed to take advantage of the extended instruction set, XINST must be set during programming.

To develop software for the extended instruction set, the user must enable support for the instructions and the Indexed Addressing mode in their language tool(s). Depending on the environment being used, this may be done in several ways:

- A menu option, or dialog box within the environment, that allows the user to configure the language tool and its settings for the project

- · A command line option

- · A directive in the source code

These options vary between different compilers, assemblers and development environments. Users are encouraged to review the documentation accompanying their development systems for the appropriate information.

TABLE 24-1: MEMORY PROGRAMMING REQUIREMENTS

| DC CHARACTERISTICS |                    |                                        | Standard Operating Conditions (unless otherwise stated) Operating temperature -40 $^{\circ}$ C $\leq$ TA $\leq$ +85 $^{\circ}$ C for industrial |      |     |       |                                               |

|--------------------|--------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|-----------------------------------------------|

| Param<br>No.       | Sym Characteristic |                                        |                                                                                                                                                 | Тур† | Max | Units | Conditions                                    |

|                    |                    | Program Flash Memory                   |                                                                                                                                                 |      |     |       |                                               |

| D130               | ЕP                 | Cell Endurance                         | 100                                                                                                                                             | 1K   | _   | E/W   | -40°C to +85°C                                |

| D131               | VPR                | VDD for Read                           | VMIN                                                                                                                                            |      | 3.6 | V     | VMIN = Minimum operating voltage              |

| D132B              | VPEW               | Voltage for Self-Timed Erase or Write: |                                                                                                                                                 |      |     |       |                                               |

|                    |                    | VDD                                    | 2.7                                                                                                                                             | _    | 3.6 | V     | PIC18FXXJ10                                   |

|                    |                    | VDDCORE                                | 2.25                                                                                                                                            |      | 2.7 | V     | PIC18LFXXJ10                                  |

| D133A              | Tıw                | Self-Timed Write Cycle Time            | _                                                                                                                                               | 2.8  | _   | ms    |                                               |

| D133B              | TIE                | Self-Timed Page Erased Cycle Time      | _                                                                                                                                               | 33.0 | _   | ms    |                                               |

| D134               | TRETD              | Characteristic Retention               | 20                                                                                                                                              | _    | _   | Year  | Provided no other specifications are violated |

| D135               | IDDP               | Supply Current during Programming      | _                                                                                                                                               | 10   | _   | mA    |                                               |