Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 40MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 32                                                                           |

| Program Memory Size        | 32KB (16K x 16)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                |                                                                              |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                    |

| Data Converters            | A/D 13x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 44-QFN (8x8)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf45j10t-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

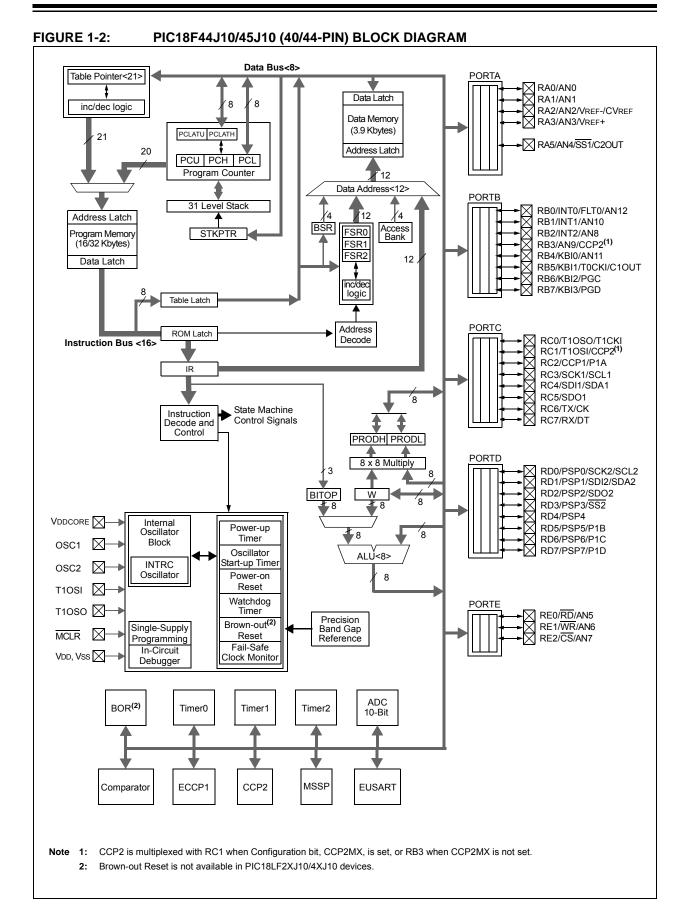

## 28/40/44-Pin High-Performance, RISC Microcontrollers

#### **Special Microcontroller Features:**

- Operating Voltage Range: 2.0V to 3.6V

- 5.5V Tolerant Input (digital pins only)

- · On-Chip 2.5V Regulator

- 4x Phase Lock Loop (PLL) available for Crystal and Internal Oscillators

- Self-Programmable under Software Control

- Low-Power, High-Speed CMOS Flash Technology

- C Compiler Optimized Architecture:

- Optional extended instruction set designed to optimize re-entrant code

- · Priority Levels for Interrupts

- 8 x 8 Single-Cycle Hardware Multiplier

- Extended Watchdog Timer (WDT):

- Programmable period from 4 ms to 131s

- Single-Supply In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via Two Pins

- In-Circuit Debug (ICD) with Three Breakpoints via Two Pins

- · Power-Managed modes with Clock Switching:

- Run: CPU on, peripherals on

- Idle: CPU off, peripherals on

- Sleep: CPU off, peripherals off

## **Flexible Oscillator Structure:**

- Two Crystal modes, up to 40 MHz

- Two External Clock modes, up to 40 MHz

- Internal 31 kHz Oscillator

- Secondary Oscillator using Timer1 @ 32 kHz

- Two-Speed Oscillator Start-up

- Fail-Safe Clock Monitor:

- Allows for safe shutdown if peripheral clock stops

## **Peripheral Highlights:**

- High-Current Sink/Source 25 mA/25 mA (PORTB and PORTC)

- · Three Programmable External Interrupts

- · Four Input Change Interrupts

- · One Capture/Compare/PWM (CCP) module

- One Enhanced Capture/Compare/PWM (ECCP) module:

- One, two or four PWM outputs

- Selectable polarity

- Programmable dead time

- Auto-shutdown and auto-restart

- Two Master Synchronous Serial Port (MSSP) modules supporting 3-Wire SPI (all 4 modes) and I<sup>2</sup>C<sup>™</sup> Master and Slave modes

- One Enhanced Addressable USART module:

- Supports RS-485, RS-232 and LIN/J2602

- Auto-wake-up on Start bit

- Auto-Baud Detect (ABD)

- 10-Bit, up to 13-Channel Analog-to-Digital Converter module (A/D):

- Auto-acquisition capability

- Conversion available during Sleep

- Self-calibration feature

- · Dual Analog Comparators with Input Multiplexing

|             | Program Memo     |                               |                                |     |                    | CCB                   | MSSP |     |                             | F     | ors       |                    |

|-------------|------------------|-------------------------------|--------------------------------|-----|--------------------|-----------------------|------|-----|-----------------------------|-------|-----------|--------------------|

| Device      | Flash<br>(bytes) | # Single-Word<br>Instructions | SRAM Data<br>Memory<br>(bytes) | I/O | 10-Bit<br>A/D (ch) | CCP/<br>ECCP<br>(PWM) |      | SPI | Master<br>I <sup>2</sup> C™ | EUSAR | Comparato | Timers<br>8/16-Bit |

| PIC18F24J10 | 16K              | 8192                          | 1024                           | 21  | 10                 | 2/0                   | 1    | Y   | Y                           | 1     | 2         | 1/2                |

| PIC18F25J10 | 32K              | 16384                         | 1024                           | 21  | 10                 | 2/0                   | 1    | Y   | Y                           | 1     | 2         | 1/2                |

| PIC18F44J10 | 16K              | 8192                          | 1024                           | 32  | 13                 | 1/1                   | 2    | Y   | Y                           | 1     | 2         | 1/2                |

| PIC18F45J10 | 32K              | 16384                         | 1024                           | 32  | 13                 | 1/1                   | 2    | Y   | Y                           | 1     | 2         | 1/2                |

| TABLE 1-1: DEVICE FE                    | AIURES                                                                                                                 |                                                                                                                        |                                                                                                                        |                                                                                                                        |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Features                                | PIC18F24J10                                                                                                            | PIC18F25J10                                                                                                            | PIC18F44J10                                                                                                            | PIC18F45J10                                                                                                            |

| Operating Frequency                     | DC – 40 MHz                                                                                                            |

| Program Memory (Bytes)                  | 16384                                                                                                                  | 32768                                                                                                                  | 16384                                                                                                                  | 32768                                                                                                                  |

| Program Memory<br>(Instructions)        | 8192                                                                                                                   | 16384                                                                                                                  | 8192                                                                                                                   | 16384                                                                                                                  |

| Data Memory (Bytes)                     | 1024                                                                                                                   | 1024                                                                                                                   | 1024                                                                                                                   | 1024                                                                                                                   |

| Interrupt Sources                       | 19                                                                                                                     | 19                                                                                                                     | 20                                                                                                                     | 20                                                                                                                     |

| I/O Ports                               | Ports A, B, C                                                                                                          | Ports A, B, C                                                                                                          | Ports A, B, C, D, E                                                                                                    | Ports A, B, C, D, E                                                                                                    |

| Timers                                  | 3                                                                                                                      | 3                                                                                                                      | 3                                                                                                                      | 3                                                                                                                      |

| Capture/Compare/PWM Modules             | 2                                                                                                                      | 2                                                                                                                      | 1                                                                                                                      | 1                                                                                                                      |

| Enhanced<br>Capture/Compare/PWM Modules | 0                                                                                                                      | 0                                                                                                                      | 1                                                                                                                      | 1                                                                                                                      |

| Serial Communications                   | MSSP,<br>Enhanced USART                                                                                                | MSSP,<br>Enhanced USART                                                                                                | MSSP,<br>Enhanced USART                                                                                                | MSSP,<br>Enhanced USART                                                                                                |

| Parallel Communications (PSP)           | No                                                                                                                     | No                                                                                                                     | Yes                                                                                                                    | Yes                                                                                                                    |

| 10-Bit Analog-to-Digital Module         | 10 Input Channels                                                                                                      | 10 Input Channels                                                                                                      | 13 Input Channels                                                                                                      | 13 Input Channels                                                                                                      |

| Resets (and Delays)                     | POR, BOR <sup>(1)</sup> ,<br>RESET Instruction,<br>Stack Full, Stack<br>Underflow (PWRT,<br><u>OS</u> T),<br>MCLR, WDT | POR, BOR <sup>(1)</sup> ,<br>RESET Instruction,<br>Stack Full, Stack<br>Underflow (PWRT,<br><u>OS</u> T),<br>MCLR, WDT | POR, BOR <sup>(1)</sup> ,<br>RESET Instruction,<br>Stack Full, Stack<br>Underflow (PWRT,<br><u>OS</u> T),<br>MCLR, WDT | POR, BOR <sup>(1)</sup> ,<br>RESET Instruction,<br>Stack Full, Stack<br>Underflow (PWRT,<br><u>OS</u> T),<br>MCLR, WDT |

| Programmable Brown-out Reset            | Yes                                                                                                                    | Yes                                                                                                                    | Yes                                                                                                                    | Yes                                                                                                                    |

| Instruction Set                         | 75 Instructions;<br>83 with Extended<br>Instruction Set enabled                                                        |

| Packages                                | 28-pin SPDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN                                                               | 28-pin SPDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN                                                               | 40-pin PDIP<br>44-pin QFN<br>44-pin TQFP                                                                               | 40-pin PDIP<br>44-pin QFN<br>44-pin TQFP                                                                               |

## TABLE 1-1: DEVICE FEATURES

**Note 1:** BOR is not available in PIC18LF2XJ10/4XJ10 devices.

NOTES:

## 3.5 Internal Oscillator Block

The PIC18F45J10 family of devices includes an internal oscillator source (INTRC) which provides a nominal 31 kHz output. The INTRC is enabled on device power-up and clocks the device during its configuration cycle until it enters operating mode. INTRC is also enabled if it is selected as the device clock source or if any of the following are enabled:

- Fail-Safe Clock Monitor

- Watchdog Timer

- · Two-Speed Start-up

These features are discussed in greater detail in **Section 21.0 "Special Features of the CPU"**.

The INTRC can also be optionally configured as the default clock source on device start-up by setting the FOSC2 Configuration bit. This is discussed in **Section 3.6.1 "Oscillator Control Register"**.

## 3.6 Clock Sources and Oscillator Switching

The PIC18F45J10 family includes a feature that allows the device clock source to be switched from the main oscillator to an alternate clock source. PIC18F45J10 family devices offer two alternate clock sources. When an alternate clock source is enabled, the various power-managed operating modes are available.

Essentially, there are three clock sources for these devices:

- · Primary oscillators

- Secondary oscillators

- Internal oscillator

## FIGURE 3-5: PIC18F45J10 FAMILY CLOCK DIAGRAM

PIC18F45J10 Family **Primary Oscillator** HS, EC OSC2 Sleep HSPLL, ECPLI 4 x PLL OSC1 ----Secondary Oscillator Peripherals MUX T10SC T10SO T1OSCEN Enable T10SI Oscillator Internal Oscillator INTRC CPU Source **IDLEN** Clock Control FOSC<2:0⊳ OSCCON<1:0> Clock Source Option for Other Modules WDT, PWRT, FSCM and Two-Speed Start-up

The **primary oscillators** include the External Crystal and Resonator modes and the External Clock modes. The particular mode is defined by the FOSC<2:0> Configuration bits. The details of these modes are covered earlier in this chapter.

The **secondary oscillators** are those external sources not connected to the OSC1 or OSC2 pins. These sources may continue to operate even after the controller is placed in a power-managed mode.

PIC18F45J10 family devices offer the Timer1 oscillator as a secondary oscillator. This oscillator, in all power-managed modes, is often the time base for functions such as a Real-Time Clock (RTC).

Most often, a 32.768 kHz watch crystal is connected between the RC0/T10S0/T13CKI and RC1/T10SI pins. Loading capacitors are also connected from each pin to ground.

The Timer1 oscillator is discussed in greater detail in **Section 12.3 "Timer1 Oscillator**".

In addition to being a primary clock source, the **internal oscillator** is available as a power-managed mode clock source. The INTRC source is also used as the clock source for several special features, such as the WDT and Fail-Safe Clock Monitor.

The clock sources for the PIC18F45J10 family devices are shown in Figure 3-5. See **Section 21.0** "**Special Features of the CPU**" for Configuration register details.

## 7.0 FLASH PROGRAM MEMORY

The Flash program memory is readable, writable and erasable during normal operation over the entire VDD range.

A read from program memory is executed on one byte at a time. A write to program memory is executed on blocks of 64 bytes at a time. Program memory is erased in blocks of 1024 bytes at a time. A Bulk Erase operation may not be issued from user code.

Writing or erasing program memory will cease instruction fetches until the operation is complete. The program memory cannot be accessed during the write or erase; therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

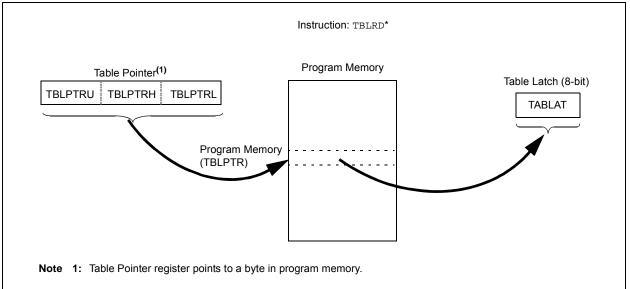

## 7.1 Table Reads and Table Writes

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16 bits wide, while the data RAM space is 8 bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

Table read operations retrieve data from program memory and place it into the data RAM space. Figure 7-1 shows the operation of a table read with program memory and data RAM.

Table write operations store data from the data memory space into holding registers in program memory. The procedure to write the contents of the holding registers into program memory is detailed in **Section 7.5** "**Writing to Flash Program Memory**". Figure 7-2 shows the operation of a table write with program memory and data RAM.

Table operations work with byte entities. A table block containing data, rather than program instructions, is not required to be word aligned. Therefore, a table block can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word-aligned.

FIGURE 7-1: TABLE READ OPERATION

## 15.0 ENHANCED CAPTURE/ COMPARE/PWM (ECCP) MODULE

| Note: | The ECCP module is implemented only in |

|-------|----------------------------------------|

|       | 40/44-pin devices.                     |

In PIC18F44J10/45J10 devices, ECCP1 is implemented as a standard CCP module with Enhanced PWM capabilities. These include the provisions for 2 or 4 output channels, user-selectable polarity, dead-band control and automatic shutdown

and restart. The Enhanced features are discussed in detail in **Section 15.4** "Enhanced PWM Mode". Capture, Compare and single output PWM functions of the ECCP module are the same as described for the standard CCP module.

The control register for the Enhanced CCP module is shown in Register 15-1. It differs from the CCP1CON register in PIC18F24J10/25J10 devices in that the two Most Significant bits are implemented to control PWM functionality.

## REGISTER 15-1: CCP1CON: ECCP1 CONTROL REGISTER (40/44-PIN DEVICES)

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|-------|-------|--------|--------|--------|--------|

| P1M1  | P1M0  | DC1B1 | DC1B0 | CCP1M3 | CCP1M2 | CCP1M1 | CCP1M0 |

| bit 7 |       |       |       |        |        |        | bit 0  |

| Legend:    |                                                                                                                                                          |                                                                                                 |                                                                                                                                                                                                                                                                                               |                                                     |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| R = Reada  | ible bit                                                                                                                                                 | W = Writable bit                                                                                | U = Unimplemented bit                                                                                                                                                                                                                                                                         | , read as '0'                                       |

| -n = Value | at POR                                                                                                                                                   | '1' = Bit is set                                                                                | '0' = Bit is cleared                                                                                                                                                                                                                                                                          | x = Bit is unknown                                  |

| bit 7-6    | <u>If CCP1N</u><br>xx = P1A                                                                                                                              | IS: Enhanced PWM Output C<br>M<3:2> = 00, 01, 10:<br>A assigned as Capture/Comp<br>M<3:2> = 11: | onfiguration bits<br>are input/output; P1B, P1C, P                                                                                                                                                                                                                                            | 1D assigned as port pins                            |

|            | 01 = Full<br>10 = Hal                                                                                                                                    | -bridge output forward: P1D i<br>f-bridge output: P1A, P1B mo                                   | 1B, P1C, P1D assigned as por<br>modulated; P1A active; P1B, I<br>dulated with dead-band contro<br>modulated; P1C active; P1A, I                                                                                                                                                               | P1C inactive<br>ol; P1C, P1D assigned as port pins  |

| bit 5-4    | <u>Capture</u><br>Unused.                                                                                                                                |                                                                                                 | nd bit 0                                                                                                                                                                                                                                                                                      |                                                     |

|            | Compare<br>Unused.<br><u>PWM mc</u><br>These bit<br>in CCPR                                                                                              | <u>ide:</u><br>is are the two LSbs of the 10-                                                   | bit PWM duty cycle. The eight                                                                                                                                                                                                                                                                 | t MSbs of the duty cycle are found                  |

| bit 3-0    | 0000 = 0<br>0001 = 0<br>0010 = 0<br>0100 = 0<br>0101 = 0<br>0110 = 0<br>1000 = 0<br>1001 = 0<br>1001 = 0<br>1001 = 0<br>1001 = 0<br>1100 = 1<br>1100 = 1 | Compare mode, initialize CCI<br>Compare mode, generate sol                                      | essets ECCP module)<br>t on match<br>edge<br>dge<br>ng edge<br>P1 pin low, set output on com<br>P1 pin high, clear output on co<br>ftware interrupt only, CCP1 pin<br>al event (ECCP resets TMR1<br>e-high; P1B, P1D active-high<br>e-low; P1B, P1D active-low<br>e-low; P1B, P1D active-high | ompare match (set CCP1IF)<br>n reverts to I/O state |

## V+ PIC18F4XJ10 QC FET QA FET Driver Driver P1A Load P1B FET FET Driver Driver P1C QD QB V-P1D

## FIGURE 15-7: EXAMPLE OF FULL-BRIDGE APPLICATION

## 15.4.5.1 Direction Change in Full-Bridge Mode

In the Full-Bridge Output mode, the P1M1 bit in the CCP1CON register allows the user to control the forward/reverse direction. When the application firmware changes this direction control bit, the module will assume the new direction on the next PWM cycle.

Just before the end of the current PWM period, the modulated outputs (P1B and P1D) are placed in their inactive state, while the unmodulated outputs (P1A and P1C) are switched to drive in the opposite direction. This occurs in the time interval, 4 Tosc \* (Timer2 Prescale Value), before the next PWM period begins. The Timer2 prescaler will be either 1, 4 or 16, depending on the value of the T2CKPS<1:0> bits (T2CON<1:0>). During the interval from the switch of the unmodulated outputs to the beginning of the next period, the modulated outputs (P1B and P1D) remain inactive. This relationship is shown in Figure 15-8.

Note that in the Full-Bridge Output mode, the ECCP1 module does not provide any dead-band delay. In general, since only one output is modulated at all times, dead-band delay is not required. However, there is a situation where a dead-band delay might be required. This situation occurs when both of the following conditions are true:

- 1. The direction of the PWM output changes when the duty cycle of the output is at or near 100%.

- 2. The turn-off time of the power switch, including the power device and driver circuit, is greater than the turn-on time.

Figure 15-9 shows an example where the PWM direction changes from forward to reverse at a near 100% duty cycle. At time t1, the outputs P1A and P1D become inactive while output P1C becomes active. In this example, since the turn-off time of the power devices is longer than the turn-on time, a shoot-through current may flow through power devices, QC and QD (see Figure 15-7), for the duration of 't'. The same phenomenon will occur to power devices, QA and QB, for PWM direction change from reverse to forward.

If changing PWM direction at high duty cycle is required for an application, one of the following requirements must be met:

- 1. Reduce PWM for a PWM period before changing directions.

- 2. Use switch drivers that can drive the switches off faster than they can drive them on.

Other options to prevent shoot-through current may exist.

#### 16.4.3.2 Address Masking

Masking an address bit causes that bit to become a "don't care". When one address bit is masked, two addresses will be Acknowledged and cause an interrupt. It is possible to mask more than one address bit at a time, which makes it possible to Acknowledge up to 31 addresses in 7-Bit Addressing mode and up to 63 addresses in 10-Bit Addressing mode (see Example 16-2).

The I<sup>2</sup>C Slave behaves the same way, whether address masking is used or not. However, when address masking is used, the I<sup>2</sup>C slave can Acknowledge multiple addresses and cause interrupts. When this occurs, it is necessary to determine which address caused the interrupt by checking SSPxBUF.

In 7-Bit Addressing mode, Address Mask bits, ADMSK<5:1> (SSPxCON2<5:1>), mask the corresponding address bits in the SSPxADD register. For any ADMSK bits that are set (ADMSK<n> = 1), the corresponding address bit is ignored (SSPxADD<n> = x). For the module to issue an address Acknowledge, it is sufficient to match only on addresses that do not have an active address mask.

In 10-Bit Addressing mode, ADMSK<5:2> bits mask the corresponding address bits in the SSPxADD register. In addition, ADMSK1 simultaneously masks the two LSbs of the address (SSPxADD<1:0>). For any ADMSK bits that are active (ADMSK<n> = 1), the corresponding address bit is ignored (SSPxADD<n> = x). Also note that although in 10-Bit Addressing mode, the upper address bits reuse part of the SSPxADD register bits, the address mask bits do not interact with those bits. They only affect the lower address bits.

**Note 1:** ADMSK1 masks the two Least Significant bits of the address.

The two Most Significant bits of the address are not affected by address masking.

## EXAMPLE 16-2: ADDRESS MASKING EXAMPLES

#### 7-Bit Addressing:

SSPxADD<7:1>= A0h (1010000) (SSPxADD<0> is assumed to be '0')

ADMSK<5:1> = 00111

Addresses Acknowledged: A0h, A2h, A4h, A6h, A8h, AAh, ACh, AEh

#### 10-Bit Addressing:

SSPxADD<7:0>= A0h (10100000) (the two MSbs of the address are ignored in this example, since they are not affected by masking)

ADMSK<5:1> = 00111

Addresses Acknowledged: A0h, A1h, A2h, A3h, A4h, A5h, A6h, A7h, A8h, A9h, AAh, ABh, ACh, ADh, AEh, AFh

## 16.4.6.1 I<sup>2</sup>C Master Mode Operation

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDAx, while SCLx outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the  $R/\overline{W}$  bit. In this case, the  $R/\overline{W}$  bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDAx, while SCLx outputs the serial clock. Serial data is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

The Baud Rate Generator used for the SPI mode operation is used to set the SCLx clock frequency for either 100 kHz, 400 kHz or 1 MHz I<sup>2</sup>C operation. See **Section 16.4.7 "Baud Rate"** for more detail.

A typical transmit sequence would go as follows:

- 1. The user generates a Start condition by setting the Start Enable bit, SEN (SSPxCON2<0>).

- SSPxIF is set. The MSSP module will wait the required start time before any other operation takes place.

- 3. The user loads the SSPxBUF with the slave address to transmit.

- 4. Address is shifted out the SDAx pin until all 8 bits are transmitted.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPxCON2 register (SSPxCON2<6>).

- 6. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 7. The user loads the SSPxBUF with eight bits of data.

- 8. Data is shifted out the SDAx pin until all 8 bits are transmitted.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPxCON2 register (SSPxCON2<6>).

- 10. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 11. The user generates a Stop condition by setting the Stop Enable bit, PEN (SSPxCON2<2>).

- 12. Interrupt is generated once the Stop condition is complete.

| Name                 | Bit 7                                  | Bit 6                       | Bit 5                                         | Bit 4                                             | Bit 3     | Bit 2     | Bit 1                 | Bit 0  | Reset<br>Values<br>on Page |

|----------------------|----------------------------------------|-----------------------------|-----------------------------------------------|---------------------------------------------------|-----------|-----------|-----------------------|--------|----------------------------|

| INTCON               | GIE/GIEH                               | PEIE/GIEL                   | TMR0IE                                        | INT0IE                                            | RBIE      | TMR0IF    | <b>INT0IF</b>         | RBIF   | 47                         |

| PIR1                 | PSPIF <sup>(1)</sup>                   | ADIF                        | RCIF                                          | TXIF                                              | SSP1IF    | CCP1IF    | TMR2IF                | TMR1IF | 49                         |

| PIE1                 | PSPIE <sup>(1)</sup>                   | ADIE                        | RCIE                                          | TXIE                                              | SSP1IE    | CCP1IE    | TMR2IE                | TMR1IE | 49                         |

| IPR1                 | PSPIP <sup>(1)</sup>                   | ADIP                        | RCIP                                          | TXIP                                              | SSP1IP    | CCP1IP    | TMR2IP                | TMR1IP | 49                         |

| PIR2                 | OSCFIF                                 | CMIF                        | _                                             | _                                                 | BCL1IF    | _         | _                     | CCP2IF | 49                         |

| PIE2                 | OSCFIE                                 | CMIE                        | _                                             | _                                                 | BCL1IE    |           |                       | CCP2IE | 49                         |

| IPR2                 | OSCFIP                                 | CMIP                        | _                                             | _                                                 | BCL1IP    | _         | _                     | CCP2IP | 49                         |

| PIR3                 | SSP2IF                                 | BCL2IF                      | _                                             | _                                                 | _         | _         | _                     | _      | 49                         |

| PIE3                 | SSP2IE                                 | BCL2IE                      | —                                             | _                                                 | —         | _         | —                     | _      | 49                         |

| IPR3                 | SSP2IP                                 | BCL2IP                      | _                                             | _                                                 | _         | _         | _                     | _      | 49                         |

| TRISC                | TRISC7                                 | TRISC6                      | TRISC5                                        | TRISC4                                            | TRISC3    | TRISC2    | TRISC1                | TRISC0 | 50                         |

| TRISD <sup>(1)</sup> | TRISD7                                 | TRISD6                      | TRISD5                                        | TRISD4                                            | TRISD3    | TRISD2    | TRISD1                | TRISD0 | 50                         |

| SSP1BUF              | MSSP1 Receive Buffer/Transmit Register |                             |                                               |                                                   |           |           |                       |        |                            |

| SSP1ADD              |                                        |                             | ster (I <sup>2</sup> C™ Sla<br>load Register  |                                                   | mode).    |           |                       |        | 48                         |

| SSP1CON1             | WCOL                                   | SSPOV                       | SSPEN                                         | CKP                                               | SSPM3     | SSPM2     | SSPM1                 | SSPM0  | 48                         |

| SSP1CON2             | GCEN                                   | ACKSTAT                     | ACKDT                                         | ACKEN                                             | RCEN      | PEN       | RSEN                  | SEN    | 48                         |

|                      | GCEN                                   | ACKSTAT                     | ADMSK5(2)                                     | ADMSK4 <sup>(2)</sup>                             | ADMSK3(2) | ADMSK2(2) | ADMSK1(2)             | SEN    | 48                         |

| SSP1STAT             | SMP                                    | CKE                         | D/Ā                                           | Р                                                 | S         | R/W       | UA                    | BF     | 48                         |

| SSP2BUF              | MSSP2 Re                               | eceive Buffer               | /Transmit Re                                  | gister                                            |           |           |                       |        | 50                         |

| SSP2ADD              | MSSP2 Ac<br>MSSP2 Ba                   | ldress Regis<br>aud Rate Re | ster (I <sup>2</sup> C Slave<br>load Register | e mode).<br><sup>.</sup> (I <sup>2</sup> C Master | mode).    |           |                       |        | 50                         |

| SSP2CON1             | WCOL                                   | SSPOV                       | SSPEN                                         | CKP                                               | SSPM3     | SSPM2     | SSPM1                 | SSPM0  | 50                         |

| SSP2CON2             | GCEN                                   | ACKSTAT                     | ACKDT                                         | ACKEN                                             | RCEN      | PEN       | RSEN                  | SEN    | 50                         |

|                      | GCEN                                   | ACKSTAT                     | ADMSK5 <sup>(2)</sup>                         | ADMSK4 <sup>(2)</sup>                             | ADMSK3(2) | ADMSK2(2) | ADMSK1 <sup>(2)</sup> | SEN    | 48                         |

| SSP2STAT             | SMP                                    | CKE                         | D/Ā                                           | Р                                                 | S         | R/W       | UA                    | BF     | 50                         |

## TABLE 16-4: REGISTERS ASSOCIATED WITH I<sup>2</sup>C<sup>™</sup> OPERATION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the MSSP module in  $I^2C^{TM}$  mode.

Note 1: These registers and/or bits are not implemented on 28-pin devices and should be read as '0'.

2: Alternate names and definitions for these bits when the MSSP module is operating in I<sup>2</sup>C Slave mode. See Section 16.4.3.2 "Address Masking" for details.

## 17.2 EUSART Asynchronous Mode

The Asynchronous mode of operation is selected by clearing the SYNC bit (TXSTA<4>). In this mode, the EUSART uses standard Non-Return-to-Zero (NRZ) format (one Start bit, eight or nine data bits and one Stop bit). The most common data format is 8 bits. An on-chip, dedicated 8-bit/16-bit Baud Rate Generator can be used to derive standard baud rate frequencies from the oscillator.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent but use the same data format and baud rate. The Baud Rate Generator produces a clock, either x16 or x64 of the bit shift rate depending on the BRGH and BRG16 bits (TXSTA<2> and BAUDCON<3>). Parity is not supported by the hardware but can be implemented in software and stored as the 9th data bit.

When operating in Asynchronous mode, the EUSART module consists of the following important elements:

- Baud Rate Generator

- Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

- Auto-Wake-up on Sync Break Character

- 12-Bit Break Character Transmit

- Auto-Baud Rate Detection

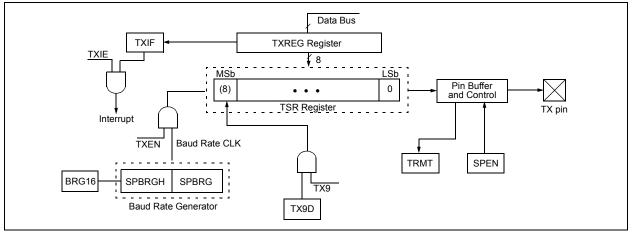

#### 17.2.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 17-3. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The Shift register obtains its data from the Read/Write Transmit Buffer register, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the Stop bit has been transmitted from the previous load. As soon as the Stop bit is transmitted, the TSR is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCY), the TXREG register is empty and the TXIF flag bit (PIR1<4>) is set. This interrupt can be enabled or disabled by setting or clearing the interrupt enable bit, TXIE (PIE1<4>). TXIF will be set regardless of the state of TXIE; it cannot be cleared in software. TXIF is also not cleared immediately upon loading TXREG, but becomes valid in the second instruction cycle following the load instruction. Polling TXIF immediately following a load of TXREG will return invalid results.

While TXIF indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. TRMT is a read-only bit which is set when the TSR register is empty. No interrupt logic is tied to this bit so the user has to poll this bit in order to determine if the TSR register is empty.

**Note 1:** The TSR register is not mapped in data memory so it is not available to the user.

2: Flag bit TXIF is set when enable bit TXEN is set.

To set up an Asynchronous Transmission:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing bit, SYNC, and setting bit, SPEN.

- 3. If interrupts are desired, set enable bit, TXIE.

- 4. If 9-bit transmission is desired, set transmit bit, TX9. Can be used as address/data bit.

- 5. Enable the transmission by setting bit, TXEN, which will also set bit, TXIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Load data to the TXREG register (starts transmission).

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

## FIGURE 17-3: EUSART TRANSMIT BLOCK DIAGRAM

## 17.3 EUSART Synchronous Master Mode

The Synchronous Master mode is entered by setting the CSRC bit (TXSTA<7>). In this mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit SYNC (TXSTA<4>). In addition, enable bit SPEN (RCSTA<7>) is set in order to configure the TX and RX pins to CK (clock) and DT (data) lines, respectively.

The Master mode indicates that the processor transmits the master clock on the CK line. Clock polarity is selected with the SCKP bit (BAUDCON<4>). Setting SCKP sets the Idle state on CK as high, while clearing the bit sets the Idle state as Iow. This option is provided to support Microwire devices with this module.

#### 17.3.1 EUSART SYNCHRONOUS MASTER TRANSMISSION

The EUSART transmitter block diagram is shown in Figure 17-3. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The Shift register obtains its data from the Read/Write Transmit Buffer register, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available).

Once the TXREG register transfers the data to the TSR register (occurs in one Tcr), the TXREG is empty and the TXIF flag bit (PIR1<4>) is set. The interrupt can be enabled or disabled by setting or clearing the interrupt enable bit, TXIE (PIE1<4>). TXIF is set regardless of the state of enable bit TXIE; it cannot be cleared in software. It will reset only when new data is loaded into the TXREG register.

While flag bit TXIF indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. TRMT is a read-only bit which is set when the TSR is empty. No interrupt logic is tied to this bit so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory so it is not available to the user.

To set up a Synchronous Master Transmission:

- Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRG16 bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit, TXIE.

- 4. If 9-bit transmission is desired, set bit, TX9.

- 5. Enable the transmission by setting bit, TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Start transmission by loading data to the TXREG register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

|                             | Q1Q2C   | 23Q4 Q1 Q2 | Q3Q4 Q1Q2        | Q3Q4 Q1Q2   | Q3Q4 Q1 Q2   | 2 Q3 Q4     | Q3Q4 Q1C    | 2 Q3 Q4 Q1 Q2  | 2Q3Q4Q1Q    | 2Q3Q4Q1     | Q2Q3Q4Q1Q2 | Q3Q4Q1     | Q2Q3Q4      |

|-----------------------------|---------|------------|------------------|-------------|--------------|-------------|-------------|----------------|-------------|-------------|------------|------------|-------------|

| RC7/RX/DT                   |         | 1<br>      | bit 0            |             | bit :        |             | bit         | 7 <u>bit 0</u> |             |             |            | ×          | bit 7       |

| RC6/TX/CK p<br>(SCKP = 0)   |         | <br>       |                  |             |              |             |             |                |             | ;           |            |            |             |

| RC6/TX/CK p<br>(SCKP = 1)   | bin     |            |                  | ╶┊┎         | ٦ <u>ٺ</u> ר |             |             |                |             | - <u></u>   |            | - <u>+</u> | ,           |

| Write to<br>TXREG Reg       |         | Write W    | ord 1            | Write Wor   | d 2          |             |             | 1<br>1<br>1    | 1<br>1<br>1 | <br> <br>   | <u>}</u>   | <br> <br>  | i<br>i      |

| TXIF bit<br>(Interrupt Flag | g)      |            |                  |             | <u>_</u> ن   |             |             |                |             |             |            |            |             |

| TRMT bit                    |         | ٦ <u>¦</u> | 1<br>1<br>1      | 1<br>1<br>1 | 1<br>1<br>1  |             | 1<br>1<br>1 | 1<br>1<br>1    | <br>        | 1<br>1<br>1 |            | <u>+</u> [ | 1<br>1<br>1 |

| TXEN bit                    | '1'     | <br>       | 1<br>1<br>1      | <br> <br>   |              |             |             | ,<br>,<br>,    |             |             | {          |            | <u>'1'</u>  |

| Note: Syne                  | c Maste | er mode, S | <b>PBRG =</b> 0, | continuous  | s transmis   | sion of two | 3-bit words |                |             |             |            |            |             |

## FIGURE 17-11: SYNCHRONOUS TRANSMISSION

## **19.2** Comparator Operation

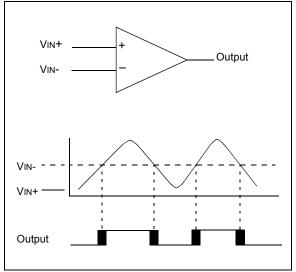

A single comparator is shown in Figure 19-2, along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input, VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input, VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 19-2 represent the uncertainty due to input offsets and response time.

## 19.3 Comparator Reference

Depending on the comparator operating mode, either an external or internal voltage reference may be used. The analog signal present at VIN- is compared to the signal at VIN+ and the digital output of the comparator is adjusted accordingly (Figure 19-2).

## 19.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between Vss and VDD and can be applied to either pin of the comparator(s).

## 19.3.2 INTERNAL REFERENCE SIGNAL

The comparator module also allows the selection of an internally generated voltage reference from the comparator voltage reference module. This module is described in more detail in **Section 20.0 "Comparator Voltage Reference Module"**.

The internal reference is only available in the mode where four inputs are multiplexed to two comparators (CM<2:0> = 110). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

## 19.4 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output has a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs. Otherwise, the maximum delay of the comparators should be used (see Section 24.0 "Electrical Characteristics").

## **19.5 Comparator Outputs**

The comparator outputs are read through the CMCON register. These bits are read-only. The comparator outputs may also be directly output to the RB5 and RA5 I/O pins. When enabled, multiplexors in the output path of the RB5 and RA5 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 19-3 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/ disable for the RB5 and RA5 pins while in this mode.

The polarity of the comparator outputs can be changed using the C2INV and C1INV bits (CMCON<5:4>).

- Note 1: When reading the PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- 2: Analog levels on any pin defined as a digital input may cause the input buffer to consume more current than is specified.

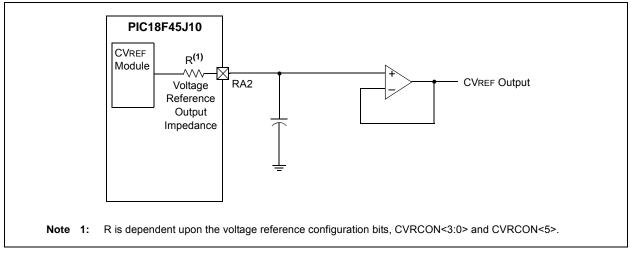

#### FIGURE 20-2: COMPARATOR VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

#### TABLE 20-1: REGISTERS ASSOCIATED WITH COMPARATOR VOLTAGE REFERENCE

| Name   | Bit 7 | Bit 6 | Bit 5  | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|-------|-------|--------|-------|--------|--------|--------|--------|----------------------------|

| CVRCON | CVREN | CVROE | CVRR   | CVRSS | CVR3   | CVR2   | CVR1   | CVR0   | 49                         |

| CMCON  | C2OUT | C10UT | C2INV  | C1INV | CIS    | CM2    | CM1    | CM0    | 49                         |

| TRISA  | _     | _     | TRISA5 | _     | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 50                         |

Legend: Shaded cells are not used with the comparator voltage reference.

## 22.2.2 EXTENDED INSTRUCTION SET

| ADDFSR Add Literal to FSR |                |             |                                                                             |     |   |          |  |  |  |  |

|---------------------------|----------------|-------------|-----------------------------------------------------------------------------|-----|---|----------|--|--|--|--|

| Synta                     | ax:            | ADDFSR      | ADDFSR f, k                                                                 |     |   |          |  |  |  |  |

| Oper                      | ands:          |             | $0 \le k \le 63$<br>f $\in$ [0, 1, 2]                                       |     |   |          |  |  |  |  |

| Oper                      | ation:         | FSR(f) + I  | $x \rightarrow FSR($                                                        | f)  |   |          |  |  |  |  |

| Statu                     | s Affected:    | None        | None                                                                        |     |   |          |  |  |  |  |

| Enco                      | ding:          | 1110        | 1000                                                                        | ffk | k | kkkk     |  |  |  |  |

| Desc                      | ription:       |             | The 6-bit literal 'k' is added to the contents of the FSR specified by 'f'. |     |   |          |  |  |  |  |

| Word                      | ls:            | 1           |                                                                             |     |   |          |  |  |  |  |

| Cycle                     | es:            | 1           |                                                                             |     |   |          |  |  |  |  |

| QC                        | ycle Activity: |             |                                                                             |     |   |          |  |  |  |  |

|                           | Q1             | Q2          | Q3                                                                          |     |   | Q4       |  |  |  |  |

|                           | Decode         | Read        | Proce                                                                       | SS  | V | Vrite to |  |  |  |  |

|                           |                | literal 'k' | Data                                                                        | a   |   | FSR      |  |  |  |  |

| Example: | ADDFSR | 2          | 23h    |  |

|----------|--------|------------|--------|--|

| Example. | ADDISK | <b>Z</b> , | 2 3 11 |  |

| Before Instru  | ction |       |

|----------------|-------|-------|

| FSR2           | =     | 03FFh |

| After Instruct | ion   |       |

| FSR2           | =     | 0422h |

| ADDULNK          | Add Literal to FSR2 and Return                                                                                                                                                                                                                                                                                                            |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | ADDULNK k                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| Operands:        | $0 \le k \le 63$                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Operation:       | $FSR2 + k \rightarrow FSR2$ ,                                                                                                                                                                                                                                                                                                             |  |  |  |

|                  | $(TOS) \rightarrow PC$                                                                                                                                                                                                                                                                                                                    |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| Encoding:        | 1110 1000 11kk kkkk                                                                                                                                                                                                                                                                                                                       |  |  |  |

| Description:     | The 6-bit literal 'k' is added to the contents of FSR2. A RETURN is then executed by loading the PC with the TOS.<br>The instruction takes two cycles to execute; a NOP is performed during the second cycle.<br>This may be thought of as a special case of the ADDFSR instruction, where f = 3 (binary '11'); it operates only on FSR2. |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                                                                                                                                         |  |  |  |

#### Q Cycle Activity:

| Q1        | Q2               | Q3        | Q4        |

|-----------|------------------|-----------|-----------|

| Decode    | ode Read Process |           | Write to  |

|           | literal 'k'      | Data      | FSR       |

| No        | No No            |           | No        |

| Operation | Operation        | Operation | Operation |

| Example: | ADDULNK | 23h |

|----------|---------|-----|

|          |         |     |

| Before Instruction |                   |  |  |  |  |  |  |

|--------------------|-------------------|--|--|--|--|--|--|

| =                  | 03FFh             |  |  |  |  |  |  |

| =                  | 0100h             |  |  |  |  |  |  |

| on                 |                   |  |  |  |  |  |  |

| =                  | 0422h             |  |  |  |  |  |  |

| =                  | (TOS)             |  |  |  |  |  |  |

|                    | =<br>=<br>on<br>= |  |  |  |  |  |  |

**Note:** All PIC18 instructions may take an optional label argument preceding the instruction mnemonic for use in symbolic addressing. If a label is used, the instruction syntax then becomes: {label} instruction argument(s).

| SUE   | SUBFSR Subtract Literal from FSR |                                   |              |      |             |  |  |  |

|-------|----------------------------------|-----------------------------------|--------------|------|-------------|--|--|--|

| Synta | ax:                              | SUBFSR                            | f, k         |      |             |  |  |  |

| Oper  | ands:                            | $0 \le k \le 63$                  | 5            |      |             |  |  |  |

|       |                                  | $f \in [ \ 0, \ 1,$               | 2]           |      |             |  |  |  |

| Oper  | ation:                           | FSR(f) – ł                        | $c \to FSRf$ |      |             |  |  |  |

| Statu | s Affected:                      | None                              |              |      |             |  |  |  |

| Enco  | ding:                            | 1110                              | 1001         | ffkk | kkkk        |  |  |  |

| Desc  | ription:                         | The 6-bit I<br>the conter<br>'f'. |              |      |             |  |  |  |

| Word  | ls:                              | 1                                 | 1            |      |             |  |  |  |

| Cycle | es:                              | 1                                 |              |      |             |  |  |  |

| QC    | ycle Activity:                   |                                   |              |      |             |  |  |  |

| Q1    |                                  | Q2                                | Q3           |      | Q4          |  |  |  |

|       | Decode                           | Decode Read Process               |              | ess  | Write to    |  |  |  |

|       |                                  | register 'f'                      | Data         | a c  | destination |  |  |  |

|       |                                  |                                   |              |      |             |  |  |  |

| Example: | SUBFSR | 2, | 23h |

|----------|--------|----|-----|

|----------|--------|----|-----|

| Before Instru | ction |       |

|---------------|-------|-------|

| FSR2          | =     | 03FFh |

| After Instruct | ion |       |

|----------------|-----|-------|

| FSR2           | =   | 03DCh |

| Syntax:           | SUBULNK                                                                                                                                                                                                                                                                                                                                                                          | ( k  |                 |                         |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------|-------------------------|

| Operands:         | 0 < k < 63                                                                                                                                                                                                                                                                                                                                                                       |      |                 |                         |

| Operation:        | FSR2 – k                                                                                                                                                                                                                                                                                                                                                                         |      | )               |                         |

| operation.        | $(TOS) \rightarrow F$                                                                                                                                                                                                                                                                                                                                                            |      | •               |                         |

| Status Affected:  | None                                                                                                                                                                                                                                                                                                                                                                             | 0    |                 |                         |

| Encoding:         | 1110                                                                                                                                                                                                                                                                                                                                                                             | 1001 | 11kk            | kkkk                    |

| Words:<br>Cycles: | <ul> <li>n: The 6-bit literal 'k' is subtracted from the contents of the FSR2. A RETURN is then executed by loading the PC with the TOS. The instruction takes two cycles to execute; a NOP is performed during the second cycle. This may be thought of as a special case of the SUBFSR instruction, where f = 3 (binary '11'); it operates only on FSR2.</li> <li>1</li> </ul> |      |                 |                         |

| Q Cycle Activity  | y:                                                                                                                                                                                                                                                                                                                                                                               |      |                 |                         |

| Q1                | Q                                                                                                                                                                                                                                                                                                                                                                                | 2    | Q3              | Q4                      |

| Decode            | e Rea<br>regist                                                                                                                                                                                                                                                                                                                                                                  | ~~   | Process<br>Data | Write to<br>destination |

| No                | No                                                                                                                                                                                                                                                                                                                                                                               | )    | No              | No                      |

|                   | n Opera                                                                                                                                                                                                                                                                                                                                                                          |      | Operation       | Operation               |

Example: SUBULNK 23h

| Before Instruction |    |       |  |  |  |  |  |  |

|--------------------|----|-------|--|--|--|--|--|--|

| FSR2               | =  | 03FFh |  |  |  |  |  |  |

| PC                 | =  | 0100h |  |  |  |  |  |  |

| After Instructi    | on |       |  |  |  |  |  |  |

| FSR2               | =  | 03DCh |  |  |  |  |  |  |

| PC                 | =  | (TOS) |  |  |  |  |  |  |

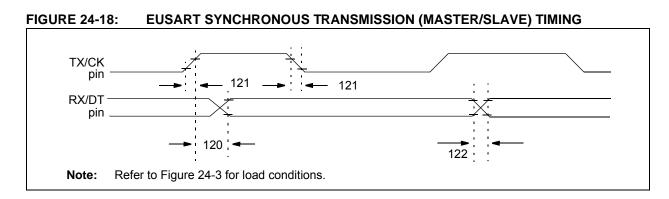

#### TABLE 24-22: EUSART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param<br>No. | Symbol   | Characteristic                                               | Min | Max | Units | Conditions |

|--------------|----------|--------------------------------------------------------------|-----|-----|-------|------------|

| 120          | TCKH2DTV | SYNC XMIT (MASTER and SLAVE)<br>Clock High to Data Out Valid | _   | 40  | ns    |            |

| 121          | TCKRF    | Clock Out Rise Time and Fall Time (Master mode)              |     | 20  | ns    |            |

| 122          | TDTRF    | Data Out Rise Time and Fall Time                             |     | 20  | ns    |            |

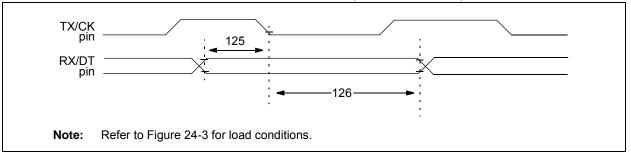

## FIGURE 24-19: EUSART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

## TABLE 24-23: EUSART SYNCHRONOUS RECEIVE REQUIREMENTS

| Param.<br>No. | Symbol   | Characteristic                                                                 | Min | Max | Units | Conditions |

|---------------|----------|--------------------------------------------------------------------------------|-----|-----|-------|------------|

| 125           | TDTV2CKL | SYNC RCV (MASTER and SLAVE)<br>Data Hold before $CK \downarrow (DT hold time)$ | 10  |     | ns    |            |

| 126           | TCKL2DTL | Data Hold after CK $\downarrow$ (DT hold time)                                 | 15  | _   | ns    |            |

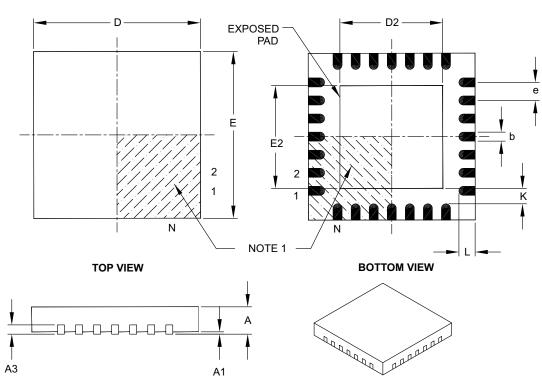

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units |          | MILLIMETERS |      |  |

|------------------------|-------|----------|-------------|------|--|

| Dimension Limits       |       | MIN      | NOM         | MAX  |  |

| Number of Pins         | Ν     | 28       |             |      |  |

| Pitch                  | е     | 0.65 BSC |             |      |  |

| Overall Height         | Α     | 0.80     | 0.90        | 1.00 |  |

| Standoff               | A1    | 0.00     | 0.02        | 0.05 |  |

| Contact Thickness      | A3    | 0.20 REF |             |      |  |

| Overall Width          | E     | 6.00 BSC |             |      |  |

| Exposed Pad Width      | E2    | 3.65     | 3.70        | 4.20 |  |

| Overall Length         | D     | 6.00 BSC |             |      |  |

| Exposed Pad Length     | D2    | 3.65     | 3.70        | 4.20 |  |

| Contact Width          | b     | 0.23     | 0.30        | 0.35 |  |

| Contact Length         | L     | 0.50     | 0.55        | 0.70 |  |

| Contact-to-Exposed Pad | К     | 0.20     | -           | -    |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105B

## WORLDWIDE SALES AND SERVICE

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://support.microchip.com Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo, IN Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

**Santa Clara** Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Hong Kong SAR** Tel: 852-2401-1200 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460

Fax: 86-25-8473-2470 China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4080

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513