Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 8MHz                                                                     |

| Connectivity               | SPI, UART/USART, USI                                                     |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                               |

| Number of I/O              | 54                                                                       |

| Program Memory Size        | 32KB (16K x 16)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 1K x 8                                                                   |

| RAM Size                   | 2K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-VFQFN Exposed Pad                                                     |

| Supplier Device Package    | 64-QFN (9x9)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega329v-8mu |

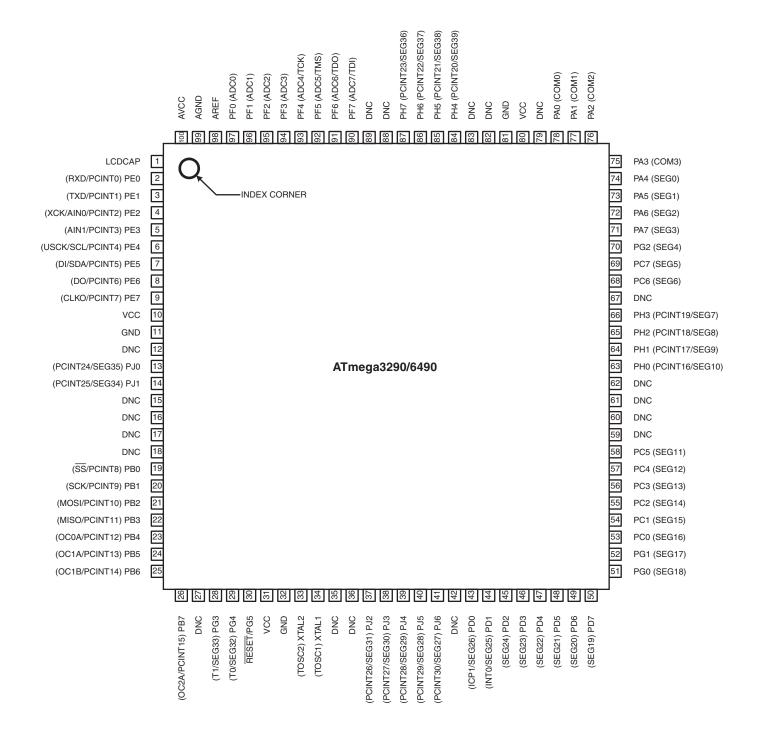

# 1. Pin Configurations

Figure 1-1. Pinout ATmega3290/6490

#### **TQFP**

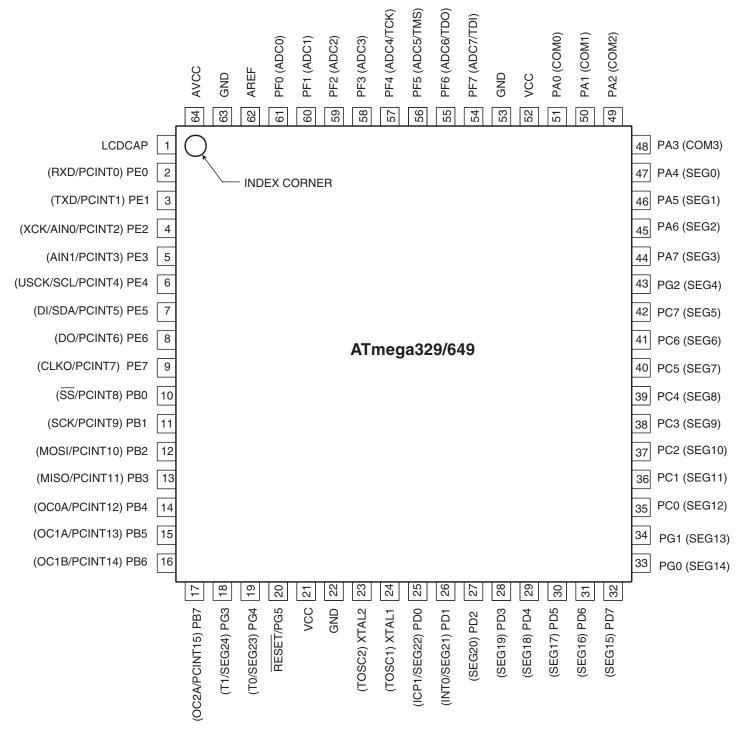

Figure 1-2. Pinout ATmega329/649

Note: The large center pad underneath the QFN/MLF packages is made of metal and internally connected to GND. It should be soldered or glued to the board to ensure good mechanical stability. If the center pad is left unconnected, the package might loosen from the board.

# 2. Overview

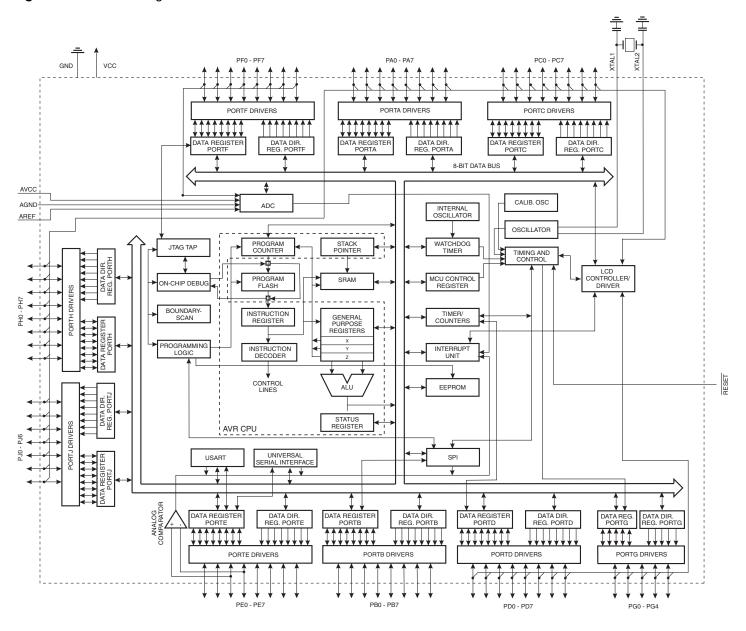

The ATmega329/3290/649/6490 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the ATmega329/3290/649/6490 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

# 2.1 Block Diagram

Figure 2-1. Block Diagram

# 2.2 Comparison between ATmega329, ATmega3290, ATmega649 and ATmega6490

The ATmega329, ATmega3290, ATmega649, and ATmega6490 differs only in memory sizes, pin count and pinout. Table 2-1 on page 6 summarizes the different configurations for the four devices.

Table 2-1.

Configuration Summary

| Device     | Flash    | EEPROM   | RAM     | LCD<br>Segments | General Purpose<br>I/O Pins |

|------------|----------|----------|---------|-----------------|-----------------------------|

| ATmega329  | 32Kbytes | 1Kbytes  | 2Kbytes | 4 x 25          | 54                          |

| ATmega3290 | 32Kbytes | 1K bytes | 2Kbytes | 4 x 40          | 69                          |

| ATmega649  | 64Kbytes | 2Kbytes  | 4Kbytes | 4 x 25          | 54                          |

| ATmega6490 | 64Kbytes | 2Kbytes  | 4Kbytes | 4 x 40          | 69                          |

# 2.3 Pin Descriptions

The following section describes the I/O-pin special functions.

2.3.1 V<sub>CC</sub>

Digital supply voltage.

2.3.2 GND

Ground.

#### 2.3.3 Port A (PA7..PA0)

Port A is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port A output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port A pins that are externally pulled low will source current if the pull-up resistors are activated. The Port A pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port A also serves the functions of various special features of the ATmega329/3290/649/6490 as listed on page 67.

#### 2.3.4 Port B (PB7..PB0)

Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port B has better driving capabilities than the other ports.

Port B also serves the functions of various special features of the ATmega329/3290/649/6490 as listed on page 68.

#### 2.3.5 Port C (PC7..PC0)

Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port C output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port C also serves the functions of special features of the ATmega329/3290/649/6490 as listed on page 71.

# 2.3.6 Port D (PD7..PD0)

Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port D also serves the functions of various special features of the ATmega329/3290/649/6490 as listed on page 73.

#### 2.3.7 Port E (PE7..PE0)

Port E is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port E output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port E pins that are externally pulled low will source current if the pull-up resistors are activated. The Port E pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port E also serves the functions of various special features of the ATmega329/3290/649/6490 as listed on page 75.

#### 2.3.8 Port F (PF7..PF0)

Port F serves as the analog inputs to the A/D Converter.

Port F also serves as an 8-bit bi-directional I/O port, if the A/D Converter is not used. Port pins can provide internal pull-up resistors (selected for each bit). The Port F output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port F pins that are externally pulled low will source current if the pull-up resistors are activated. The Port F pins are tri-stated when a reset condition becomes active, even if the clock is not running. If the JTAG interface is enabled, the pull-up resistors on pins PF7(TDI), PF5(TMS), and PF4(TCK) will be activated even if a reset occurs.

Port F also serves the functions of the JTAG interface.

#### 2.3.9 Port G (PG5..PG0)

Port G is a 6-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port G output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port G pins that are externally pulled low will source current if the pull-up resistors are activated. The Port G pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port G also serves the functions of various special features of the ATmega329/3290/649/6490 as listed on page 75.

#### 2.3.10 Port H (PH7..PH0)

Port H is a 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port H output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port H pins that are externally pulled low will source current if the pull-up resistors are activated. The Port H pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port H also serves the functions of various special features of the ATmega3290/6490 as listed on page 75.

#### 2.3.11 Port J (PJ6..PJ0)

Port J is a 7-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port J output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port J pins that are externally pulled low will source current if the pull-up resistors are activated. The Port J pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port J also serves the functions of various special features of the ATmega3290/6490 as listed on page 75.

#### 2.3.12 **RESET**

Reset input. A low level on this pin for longer than the minimum pulse length will generate a reset, even if the clock is not running. The minimum pulse length is given in "System and Reset Characteristics" on page 330. Shorter pulses are not guaranteed to generate a reset.

## 2.3.13 XTAL1

Input to the inverting Oscillator amplifier and input to the internal clock operating circuit.

# 2.3.14 XTAL2

Output from the inverting Oscillator amplifier.

#### 2.3.15 AVCC

AVCC is the supply voltage pin for Port F and the A/D Converter. It should be externally connected to  $V_{CC}$ , even if the ADC is not used. If the ADC is used, it should be connected to  $V_{CC}$  through a low-pass filter.

#### 2.3.16 AREF

This is the analog reference pin for the A/D Converter.

# 6. Register Summary

Note: Registers with bold type only available in ATmega3290/6490.

| Address | Name                      | Bit 7          | Bit 6          | Bit 5   | Bit 4            | Bit 3             | Bit 2         | Bit 1             | Bit 0           | Page       |

|---------|---------------------------|----------------|----------------|---------|------------------|-------------------|---------------|-------------------|-----------------|------------|

| (0xFF)  | LCDDR19                   | SEG339         | SEG338         | SEG337  | SEG336           | SEG335            | SEG334        | SEG333            | SEG332          | 244        |

| (0xFE)  | LCDDR18                   | SEG331         | SEG330         | SEG329  | SEG328           | SEG327            | SEG326        | SEG325            | SEG324          | 244        |

| (0xFD)  | LCDDR17                   | SEG323         | SEG322         | SEG321  | SEG320           | SEG319            | SEG318        | SEG317            | SEG316          | 244        |

| (0xFC)  | LCDDR16                   | SEG315         | SEG314         | SEG313  | SEG312           | SEG311            | SEG310        | SEG309            | SEG308          | 244        |

| (0xFB)  | LCDDR15                   | SEG307         | SEG306         | SEG305  | SEG304           | SEG303            | SEG302        | SEG301            | SEG300          | 244        |

| (0xFA)  | LCDDR14                   | SEG239         | SEG238         | SEG237  | SEG236           | SEG235            | SEG234        | SEG233            | SEG232          | 244        |

| (0xF9)  | LCDDR13                   | SEG231         | SEG230         | SEG229  | SEG228           | SEG227            | SEG226        | SEG225            | SEG224          | 244        |

| (0xF8)  | LCDDR12                   | SEG223         | SEG222         | SEG221  | SEG220           | SEG219            | SEG218        | SEG217            | SEG216          | 244        |

| (0xF7)  | LCDDR11                   | SEG215         | SEG214         | SEG213  | SEG212           | SEG211            | SEG210        | SEG209            | SEG208          | 244        |

| (0xF6)  | LCDDR10                   | SEG207         | SEG206         | SEG205  | SEG204           | SEG203            | SEG202        | SEG201            | SEG200          | 244        |

| (0xF5)  | LCDDR09                   | SEG139         | SEG138         | SEG137  | SEG136           | SEG135            | SEG134        | SEG133            | SEG132          | 244        |

| (0xF4)  | LCDDR08                   | SEG131         | SEG130         | SEG129  | SEG128           | SEG127            | SEG126        | SEG125            | SEG124          | 244        |

| (0xF3)  | LCDDR07                   | SEG123         | SEG122         | SEG121  | SEG120           | SEG119            | SEG118        | SEG117            | SEG116          | 244        |

| (0xF2)  | LCDDR06                   | SEG115         | SEG114         | SEG113  | SEG112           | SEG111            | SEG110        | SEG109            | SEG108          | 244        |

| (0xF1)  | LCDDR05                   | SEG107         | SEG106         | SEG105  | SEG104           | SEG103            | SEG102        | SEG101            | SEG100          | 244        |

| (0xF0)  | LCDDR04                   | SEG039         | SEG038         | SEG037  | SEG036           | SEG035            | SEG034        | SEG033            | SEG032          | 244        |

| (0xF)   | LCDDR03                   | SEG031         | SEG030         | SEG029  | SEG028           | SEG027            | SEG026        | SEG025            | SEG024          | 244        |

| (0xEE)  | LCDDR02                   | SEG023         | SEG022         | SEG021  | SEG020           | SEG019            | SEG018        | SEG017            | SEG016          | 244        |

| (0xEE)  | LCDDR01                   | SEG015         | SEG014         | SEG013  | SEG012           | SEG011            | SEG010        | SEG009            | SEG008          | 244        |

| (0xED)  | LCDDR00                   | SEG007         | SEG006         | SEG005  | SEG004           | SEG003            | SEG002        | SEG001            | SEG000          | 244        |

|         | Reserved                  | -              | -              | -       | -                | -                 | -             | -                 | -               | 211        |

| (0xEB)  | Reserved                  | -              | -              |         | -                |                   | -             | -                 | -               |            |

| (0xEA)  | Reserved                  | -              | -              | -       | -                | -                 | -             | -                 | -               |            |

| (0xE9)  | Reserved                  | _              | _              |         | -                | _                 | -             | _                 |                 |            |

| (0xE8)  | LCDCCR                    | LCDDC2         | LCDDC1         | LCDDC0  | -                | LCDCC3            | LCDCC2        | LCDCC1            | LCDCC0          | 243        |

| (0xE7)  | LCDFRR                    | LCDDC2         | LCDPS2         | LCDPS1  | LCDPS0           | LODGGS            | LCDCD2        | LCDCD1            | LCDCD0          | 243        |

| (0xE6)  |                           | -              |                |         |                  | - L CDDM2         |               |                   |                 |            |

| (0xE5)  | LCDCRB<br>LCDCRA          | LCDCS<br>LCDEN | LCD2B<br>LCDAB | LCDMUX1 | LCDMUX0<br>LCDIF | LCDPM3            | LCDPM2        | LCDPM1            | LCDPM0<br>LCDBL | 239<br>239 |

| (0xE4)  |                           | - LODEN        |                | -       |                  |                   | -             | -                 |                 | 239        |

| (0xE3)  | Reserved                  | -              | -              | -       | -                | -                 | -             | -                 | -               |            |

| (0xE2)  | Reserved<br>Reserved      | -              | -              | -       | -                | -                 | -             | -                 | -               |            |

| (0xE1)  | Reserved                  |                | -              | -       | -                |                   | -             | -                 |                 |            |

| (0xE0)  |                           | -              | -              | -       | -                | -                 | -             | -                 | -               |            |

| (0xDF)  | Reserved                  | -              | -              | -       | -                | -                 | -             | -                 | -               |            |

| (0xDE)  | Reserved                  | -              | PODT IS        | PODT IS | PODT 14          | PODT IS           | PODT IO       | PODT II           | PODT IO         | 90         |

| (0xDD)  | PORTJ                     | -              | PORTJ6         | PORTJ5  | PORTJ4           | PORTJ3            | PORTJ2        | PORTJ1            | PORTJ0          |            |

| (0xDC)  | PINJ                      | -              | DDJ6           | DDJ5    | DDJ4<br>PINJ4    | DDJ3              | DDJ2<br>PINJ2 | DDJ1              | DDJ0            | 90         |

| (0xDB)  |                           | -<br>DODTUT    | PINJ6          | PINJ5   |                  | PINJ3             |               | PINJ1             | PINJ0           |            |

| (0xDA)  | PORTH                     | PORTH7         | PORTH6         | PORTH5  | PORTH4           | PORTH3            | PORTH2        | PORTH1            | PORTH0          | 89         |

| (0xD9)  | DDRH                      | DDH7           | DDH6           | DDH5    | DDH4             | DDH3              | DDH2          | DDH1              | DDH0            | 90         |

| (0xD8)  | PINH                      | PINH7          | PINH6          | PINH5   | PINH4            | PINH3             | PINH2         | PINH1             | PINH0           | 90         |

| (0xD7)  | Reserved                  | -              | -              | -       | -                | -                 | -             | -                 | -               |            |

| (0xD6)  | Reserved                  | -              | -              | -       | -                | -                 | -             | -                 | -               |            |

| (0xD5)  | Reserved                  | -              | -              | -       | -                | -                 | -             | -                 | -               |            |

| (0xD4)  | Reserved                  | -              | -              | -       | -                | -                 | -             | -                 | -               |            |

| (0xD3)  | Reserved                  | -              | -              | -       | -                | -                 | -             | -                 | -               |            |

| (0xD2)  | Reserved                  | -              | -              | -       | -                | -                 | -             | -                 | -               |            |

| (0xD1)  | Reserved                  | -              | -              | -       | -                | -                 | -             | -                 | -               |            |

| (0xD0)  | Reserved                  | -              | -              | -       | -                | -                 | -             | -                 | -               |            |

| (0xCF)  | Reserved                  | -              | -              | -       | -                | -                 | -             | -                 | -               |            |

| (0xCE)  | Reserved                  | -              | -              | -       | -                | -                 | -             | -                 | -               |            |

| (0xCD)  | Reserved                  | -              | -              | -       | -                | -                 | -             | -                 | -               |            |

| (0xCC)  | Reserved                  | -              | -              | -       | -                | -                 | -             | -                 | -               |            |

| (0xCB)  | Reserved                  | -              | -              | -       | -                | -                 | -             | -                 | -               |            |

| (0xCA)  | Reserved                  | -              | -              | -       | -                | -                 | -             | -                 | -               |            |

| (0xC9)  | Reserved                  | -              | -              | -       | -                | -                 | -             | -                 | -               |            |

| (0xC8)  | Reserved                  | -              | -              | -       | -                | -                 | -             | -                 | -               |            |

| (0xC7)  | Reserved                  | -              | -              | -       | -                | -                 | -             | -                 | -               |            |

| (0xC6)  | UDR0 USART0 Data Register |                |                |         |                  | 190               |               |                   |                 |            |

| (0xC5)  | UBRR0H                    | _              |                |         |                  |                   | USART0 Baud R | ate Register High |                 | 194        |

| (0xC4)  | UBRR0L                    |                |                |         | USART0 Baud F    | Rate Register Low |               |                   |                 | 194        |

|         | 0.04)                     |                |                |         |                  |                   |               |                   |                 |            |

# ATmega329/3290/649/6490

| Address     | Name     | Bit 7  | Bit 6  | Bit 5  | Bit 4         | Bit 3            | Bit 2  | Bit 1             | Bit 0    | Page    |

|-------------|----------|--------|--------|--------|---------------|------------------|--------|-------------------|----------|---------|

| 0x25 (0x45) | Reserved | -      | -      | -      | -             | -                | -      | -                 | -        |         |

| 0x24 (0x44) | TCCR0A   | FOC0A  | WGM00  | COM0A1 | COM0A0        | WGM01            | CS02   | CS01              | CS00     | 103     |

| 0x23 (0x43) | GTCCR    | TSM    | -      | -      | -             | -                | -      | PSR2              | PSR10    | 108/157 |

| 0x22 (0x42) | EEARH    | -      | -      | -      | -             | -                | EEPRO  | DM Address Regist | ter High | 22      |

| 0x21 (0x41) | EEARL    |        |        |        | EEPROM Addre  | ess Register Low | '      |                   |          | 22      |

| 0x20 (0x40) | EEDR     |        |        |        | EEPROM D      | ata Register     |        |                   |          | 22      |

| 0x1F (0x3F) | EECR     | -      | -      | -      | -             | EERIE            | EEMWE  | EEWE              | EERE     | 22      |

| 0x1E (0x3E) | GPIOR0   |        |        |        | General Purpo | se I/O Register  |        |                   |          | 25      |

| 0x1D (0x3D) | EIMSK    | PCIE3  | PCIE2  | PCIE1  | PCIE0         | -                | -      | -                 | INT0     | 55      |

| 0x1C (0x3C) | EIFR     | PCIF3  | PCIF2  | PCIF1  | PCIF0         | -                | -      | -                 | INTF0    | 56      |

| 0x1B (0x3B) | Reserved | -      | -      | -      | -             | -                | -      | -                 | -        |         |

| 0x1A (0x3A) | Reserved | -      | -      | -      | -             | -                | -      | -                 | -        |         |

| 0x19 (0x39) | Reserved | -      | -      | -      | -             | -                | -      | -                 | -        |         |

| 0x18 (0x38) | Reserved | -      | -      | -      | -             | -                | -      | -                 | -        |         |

| 0x17 (0x37) | TIFR2    | -      | -      | -      | -             | -                | -      | OCF2A             | TOV2     | 157     |

| 0x16 (0x36) | TIFR1    | -      | -      | ICF1   | -             | -                | OCF1B  | OCF1A             | TOV1     | 138     |

| 0x15 (0x35) | TIFR0    | -      | -      | -      | -             | -                | -      | OCF0A             | TOV0     | 106     |

| 0x14 (0x34) | PORTG    | -      | -      | -      | PORTG4        | PORTG3           | PORTG2 | PORTG1            | PORTG0   | 89      |

| 0x13 (0x33) | DDRG     | -      | -      | -      | DDG4          | DDG3             | DDG2   | DDG1              | DDG0     | 89      |

| 0x12 (0x32) | PING     | -      | -      | PING5  | PING4         | PING3            | PING2  | PING1             | PING0    | 89      |

| 0x11 (0x31) | PORTF    | PORTF7 | PORTF6 | PORTF5 | PORTF4        | PORTF3           | PORTF2 | PORTF1            | PORTF0   | 89      |

| 0x10 (0x30) | DDRF     | DDF7   | DDF6   | DDF5   | DDF4          | DDF3             | DDF2   | DDF1              | DDF0     | 89      |

| 0x0F (0x2F) | PINF     | PINF7  | PINF6  | PINF5  | PINF4         | PINF3            | PINF2  | PINF1             | PINF0    | 89      |

| 0x0E (0x2E) | PORTE    | PORTE7 | PORTE6 | PORTE5 | PORTE4        | PORTE3           | PORTE2 | PORTE1            | PORTE0   | 88      |

| 0x0D (0x2D) | DDRE     | DDE7   | DDE6   | DDE5   | DDE4          | DDE3             | DDE2   | DDE1              | DDE0     | 88      |

| 0x0C (0x2C) | PINE     | PINE7  | PINE6  | PINE5  | PINE4         | PINE3            | PINE2  | PINE1             | PINE0    | 89      |

| 0x0B (0x2B) | PORTD    | PORTD7 | PORTD6 | PORTD5 | PORTD4        | PORTD3           | PORTD2 | PORTD1            | PORTD0   | 88      |

| 0x0A (0x2A) | DDRD     | DDD7   | DDD6   | DDD5   | DDD4          | DDD3             | DDD2   | DDD1              | DDD0     | 88      |

| 0x09 (0x29) | PIND     | PIND7  | PIND6  | PIND5  | PIND4         | PIND3            | PIND2  | PIND1             | PIND0    | 88      |

| 0x08 (0x28) | PORTC    | PORTC7 | PORTC6 | PORTC5 | PORTC4        | PORTC3           | PORTC2 | PORTC1            | PORTC0   | 88      |

| 0x07 (0x27) | DDRC     | DDC7   | DDC6   | DDC5   | DDC4          | DDC3             | DDC2   | DDC1              | DDC0     | 88      |

| 0x06 (0x26) | PINC     | PINC7  | PINC6  | PINC5  | PINC4         | PINC3            | PINC2  | PINC1             | PINC0    | 88      |

| 0x05 (0x25) | PORTB    | PORTB7 | PORTB6 | PORTB5 | PORTB4        | PORTB3           | PORTB2 | PORTB1            | PORTB0   | 87      |

| 0x04 (0x24) | DDRB     | DDB7   | DDB6   | DDB5   | DDB4          | DDB3             | DDB2   | DDB1              | DDB0     | 87      |

| 0x03 (0x23) | PINB     | PINB7  | PINB6  | PINB5  | PINB4         | PINB3            | PINB2  | PINB1             | PINB0    | 87      |

| 0x02 (0x22) | PORTA    | PORTA7 | PORTA6 | PORTA5 | PORTA4        | PORTA3           | PORTA2 | PORTA1            | PORTA0   | 87      |

| 0x01 (0x21) | DDRA     | DDA7   | DDA6   | DDA5   | DDA4          | DDA3             | DDA2   | DDA1              | DDA0     | 87      |

| 0x00 (0x20) | PINA     | PINA7  | PINA6  | PINA5  | PINA4         | PINA3            | PINA2  | PINA1             | PINA0    | 87      |

Note:

- 1. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

- 2. I/O Registers within the address range 0x00 0x1F are directly bit-accessible using the SBI and CBI instructions. In these registers, the value of single bits can be checked by using the SBIS and SBIC instructions.

- 3. Some of the Status Flags are cleared by writing a logical one to them. Note that, unlike most other AVRs, the CBI and SBI instructions will only operate on the specified bit, and can therefore be used on registers containing such Status Flags. The CBI and SBI instructions work with registers 0x00 to 0x1F only.

- 4. When using the I/O specific commands IN and OUT, the I/O addresses 0x00 0x3F must be used. When addressing I/O Registers as data space using LD and ST instructions, 0x20 must be added to these addresses. The ATmega329/3290/649/6490 is a complex microcontroller with more peripheral units than can be supported within the 64 location reserved in Opcode for the IN and OUT instructions. For the Extended I/O space from 0x60 0xFF in SRAM, only the ST/STS/STD and LD/LDS/LDD instructions can be used.

# 7. Instruction Set Summary

| Mnemonics        | Operands          | Description                              | Operation                                                                                    | Flags      | #Clocks |

|------------------|-------------------|------------------------------------------|----------------------------------------------------------------------------------------------|------------|---------|

| ARITHMETIC AND L | OGIC INSTRUCTIONS | 5                                        |                                                                                              |            |         |

| ADD              | Rd, Rr            | Add two Registers                        | Rd ← Rd + Rr                                                                                 | Z,C,N,V,H  | 1       |

| ADC              | Rd, Rr            | Add with Carry two Registers             | $Rd \leftarrow Rd + Rr + C$                                                                  | Z,C,N,V,H  | 1       |

| ADIW             | Rdl,K             | Add Immediate to Word                    | Rdh:Rdl ← Rdh:Rdl + K                                                                        | Z,C,N,V,S  | 2       |

| SUB              | Rd, Rr            | Subtract two Registers                   | Rd ← Rd - Rr                                                                                 | Z,C,N,V,H  | 1       |

| SUBI             | Rd, K             | Subtract Constant from Register          | Rd ← Rd - K                                                                                  | Z,C,N,V,H  | 1       |

| SBC              | Rd, Rr            | Subtract with Carry two Registers        | Rd ← Rd - Rr - C                                                                             | Z,C,N,V,H  | 1       |

| SBCI             | Rd, K             | Subtract with Carry Constant from Reg.   | Rd ← Rd - K - C                                                                              | Z,C,N,V,H  | 1       |

| SBIW             | Rdl,K             | Subtract Immediate from Word             | Rdh:Rdl ← Rdh:Rdl - K                                                                        | Z,C,N,V,S  | 2       |

| AND              | Rd, Rr            | Logical AND Registers                    | Rd ← Rd • Rr                                                                                 | Z,N,V      | 1       |

| ANDI             | Rd, K             | Logical AND Register and Constant        | Rd ← Rd • K                                                                                  | Z,N,V      | 1       |

| OR               | Rd, Rr            | Logical OR Registers                     | Rd ← Rd v Rr                                                                                 | Z,N,V      | 1       |

| ORI              | Rd, K             | Logical OR Register and Constant         | Rd ← Rd v K                                                                                  | Z,N,V      | 1       |

| EOR              | Rd, Rr            | Exclusive OR Registers                   | Rd ← Rd ⊕ Rr                                                                                 | Z,N,V      | 1       |

| COM              | Rd                | One's Complement                         | Rd ← 0xFF – Rd                                                                               | Z,C,N,V    | 1       |

| NEG              | Rd                | Two's Complement                         | Rd ← 0x00 – Rd                                                                               | Z,C,N,V,H  | 1       |

| SBR              | Rd,K              | Set Bit(s) in Register                   | Rd ← Rd v K                                                                                  | Z,N,V      | 1       |

| CBR              | Rd,K              | Clear Bit(s) in Register                 | $Rd \leftarrow Rd \bullet (0xFF - K)$                                                        | Z,N,V      | 1       |

| INC              | Rd                | Increment                                | Rd ← Rd + 1                                                                                  | Z,N,V      | 1       |

| DEC              | Rd                | Decrement                                | Rd ← Rd – 1                                                                                  | Z,N,V      | 1       |

| TST              | Rd                | Test for Zero or Minus                   | Rd ← Rd • Rd                                                                                 | Z,N,V      | 1       |

| CLR              | Rd                | Clear Register                           | Rd ← Rd ⊕ Rd                                                                                 | Z,N,V      | 1       |

| SER              | Rd                | Set Register                             | Rd ← 0xFF                                                                                    | None       | 1       |

| MUL              | Rd, Rr            | Multiply Unsigned                        | R1:R0 ← Rd x Rr                                                                              | Z,C        | 2       |

| MULS             | Rd, Rr            | Multiply Signed                          | R1:R0 ← Rd x Rr                                                                              | Z,C        | 2       |

| MULSU            | Rd, Rr            | Multiply Signed with Unsigned            | R1:R0 ← Rd x Rr                                                                              | Z,C        | 2       |

| FMUL             | Rd, Rr            | Fractional Multiply Unsigned             | R1:R0 ← (Rd x Rr) << 1                                                                       | Z,C        | 2       |

| FMULS            | Rd, Rr            | Fractional Multiply Signed               | R1:R0 ← (Rd x Rr) << 1                                                                       | Z,C        | 2       |

| FMULSU           | Rd, Rr            | Fractional Multiply Signed with Unsigned | R1:R0 ← (Rd x Rr) << 1                                                                       | Z.C        | 2       |

| BRANCH INSTRUC   | TIONS             |                                          |                                                                                              |            |         |

| RJMP             | k                 | Relative Jump                            | PC ← PC + k + 1                                                                              | None       | 2       |

| IJMP             |                   | Indirect Jump to (Z)                     | PC ← Z                                                                                       | None       | 2       |

| JMP              | k                 | Direct Jump                              | PC ← k                                                                                       | None       | 3       |

| RCALL            | k                 | Relative Subroutine Call                 | PC ← PC + k + 1                                                                              | None       | 3       |

| ICALL            |                   | Indirect Call to (Z)                     | PC ← Z                                                                                       | None       | 3       |

| CALL             | k                 | Direct Subroutine Call                   | PC ← k                                                                                       | None       | 4       |

| RET              |                   | Subroutine Return                        | PC ← STACK                                                                                   | None       | 4       |

| RETI             |                   | Interrupt Return                         | PC ← STACK                                                                                   | ı          | 4       |

| CPSE             | Rd,Rr             | Compare, Skip if Equal                   | if (Rd = Rr) PC ← PC + 2 or 3                                                                | None       | 1/2/3   |

| СР               | Rd,Rr             | Compare                                  | Rd – Rr                                                                                      | Z, N,V,C,H | 1       |

| CPC              | Rd,Rr             | Compare with Carry                       | Rd – Rr – C                                                                                  | Z, N,V,C,H | 1       |

| CPI              | Rd,K              | Compare Register with Immediate          | Rd – K                                                                                       | Z, N,V,C,H | 1       |

| SBRC             | Rr, b             | Skip if Bit in Register Cleared          | if (Rr(b)=0) PC ← PC + 2 or 3                                                                | None       | 1/2/3   |

| SBRS             | Rr, b             | Skip if Bit in Register is Set           | if $(Rr(b)=1)$ PC $\leftarrow$ PC + 2 or 3                                                   | None       | 1/2/3   |

| SBIC             | P, b              | Skip if Bit in I/O Register Cleared      | if $(P(b)=0)$ PC $\leftarrow$ PC + 2 or 3                                                    | None       | 1/2/3   |

| SBIS             | P, b              | Skip if Bit in I/O Register is Set       | if $(P(b)=1)$ PC $\leftarrow$ PC + 2 or 3                                                    | None       | 1/2/3   |

| BRBS             | s, k              | Branch if Status Flag Set                | if (SREG(s) = 1) then PC←PC+k + 1                                                            | None       | 1/2     |

| BRBC             | s, k              | Branch if Status Flag Cleared            | if (SREG(s) = 0) then PC←PC+k + 1                                                            | None       | 1/2     |

| BREQ             | k                 | Branch if Equal                          | if $(Z = 1)$ then $PC \leftarrow PC + k + 1$                                                 | None       | 1/2     |

| BRNE             | k                 | Branch if Not Equal                      | if $(Z = 0)$ then $PC \leftarrow PC + k + 1$                                                 | None       | 1/2     |

| BRCS             | k                 | Branch if Carry Set                      | if (C = 1) then PC $\leftarrow$ PC + k + 1                                                   | None       | 1/2     |

| BRCC             | k                 | Branch if Carry Cleared                  | if (C = 0) then $PC \leftarrow PC + k + 1$                                                   | None       | 1/2     |

| BRSH             | k                 | Branch if Same or Higher                 | if (C = 0) then PC $\leftarrow$ PC + k + 1                                                   | None       | 1/2     |

| BRLO             | k                 | Branch if Lower                          | if (C = 1) then PC $\leftarrow$ PC + k + 1                                                   | None       | 1/2     |

| BRMI             | k                 | Branch if Minus                          | if $(N = 1)$ then $PC \leftarrow PC + k + 1$                                                 | None       | 1/2     |

| BRPL             | k                 | Branch if Plus                           | if $(N = 0)$ then $PC \leftarrow PC + k + 1$                                                 | None       | 1/2     |

| BRGE             | k                 | Branch if Greater or Equal, Signed       | if $(N \oplus V = 0)$ then $PC \leftarrow PC + k + 1$                                        | None       | 1/2     |

| BRLT             | k                 | Branch if Less Than Zero, Signed         | if (N ⊕ V= 1) then PC ← PC + k + 1                                                           | None       | 1/2     |

| BRHS             | k                 | Branch if Half Carry Flag Set            | if (H = 1) then PC ← PC + k + 1                                                              | None       | 1/2     |

| BRHC             | k                 | Branch if Half Carry Flag Cleared        | if $(H = 1)$ then $PC \leftarrow PC + k + 1$<br>if $(H = 0)$ then $PC \leftarrow PC + k + 1$ | None       | 1/2     |

|                  |                   |                                          | , ,                                                                                          |            |         |

| BRTS             | k                 | Branch if T Flag Set                     | if (T = 1) then PC $\leftarrow$ PC + k + 1                                                   | None       | 1/2     |

| Mnomonios          | Operands          | Description                                                     | Operation                                                                                | Flags        | #Clocks    |

|--------------------|-------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------|------------|

| Mnemonics          | Operands          |                                                                 | Operation                                                                                |              |            |

| BRTC               | k                 | Branch if T Flag Cleared                                        | if (T = 0) then PC ← PC + k + 1                                                          | None         | 1/2        |

| BRVS               | k                 | Branch if Overflow Flag is Set                                  | if $(V = 1)$ then $PC \leftarrow PC + k + 1$                                             | None         | 1/2        |

| BRVC<br>BRIE       | k<br>k            | Branch if Overflow Flag is Cleared  Branch if Interrupt Enabled | if (V = 0) then PC $\leftarrow$ PC + k + 1<br>if (I = 1) then PC $\leftarrow$ PC + k + 1 | None<br>None | 1/2<br>1/2 |

| BRID               | k                 | Branch if Interrupt Disabled                                    | if ( I = 0) then PC ← PC + k + 1                                                         | None         | 1/2        |

| BIT AND BIT-TEST I |                   | Branch in Interrupt Bisabled                                    | TI (1 = 0) then I O = I O = K = I                                                        | None         | 1/2        |

| SBI                | P,b               | Set Bit in I/O Register                                         | I/O(P,b) ← 1                                                                             | None         | 2          |

| CBI                | P,b               | Clear Bit in I/O Register                                       | I/O(P,b) ← 0                                                                             | None         | 2          |

| LSL                | Rd                | Logical Shift Left                                              | $Rd(n+1) \leftarrow Rd(n), Rd(0) \leftarrow 0$                                           | Z,C,N,V      | 1          |

| LSR                | Rd                | Logical Shift Right                                             | $Rd(n) \leftarrow Rd(n+1), Rd(7) \leftarrow 0$                                           | Z,C,N,V      | 1          |

| ROL                | Rd                | Rotate Left Through Carry                                       | $Rd(0)\leftarrow C,Rd(n+1)\leftarrow Rd(n),C\leftarrow Rd(7)$                            | Z,C,N,V      | 1          |

| ROR                | Rd                | Rotate Right Through Carry                                      | $Rd(7)\leftarrow C,Rd(n)\leftarrow Rd(n+1),C\leftarrow Rd(0)$                            | Z,C,N,V      | 1          |

| ASR                | Rd                | Arithmetic Shift Right                                          | $Rd(n) \leftarrow Rd(n+1), n=06$                                                         | Z,C,N,V      | 1          |

| SWAP               | Rd                | Swap Nibbles                                                    | Rd(30)←Rd(74),Rd(74)←Rd(30)                                                              | None         | 1          |

| BSET               | S                 | Flag Set                                                        | SREG(s) ← 1                                                                              | SREG(s)      | 1          |

| BCLR               | S                 | Flag Clear                                                      | $SREG(s) \leftarrow 0$                                                                   | SREG(s)      | 1          |

| BST<br>BLD         | Rr, b<br>Rd, b    | Bit Store from Register to T  Bit load from T to Register       | $T \leftarrow Rr(b)$ $Rd(b) \leftarrow T$                                                | None         | 1          |

| SEC                | nu, b             | Set Carry                                                       | C ← 1                                                                                    | C            | 1 1        |

| CLC                |                   | Clear Carry                                                     | C ← 0                                                                                    | С            | 1          |

| SEN                |                   | Set Negative Flag                                               | N ← 1                                                                                    | N            | 1          |

| CLN                |                   | Clear Negative Flag                                             | N ← 0                                                                                    | N            | 1          |

| SEZ                |                   | Set Zero Flag                                                   | Z ← 1                                                                                    | Z            | 1          |

| CLZ                |                   | Clear Zero Flag                                                 | Z ← 0                                                                                    | Z            | 1          |

| SEI                |                   | Global Interrupt Enable                                         | I ← 1                                                                                    | 1            | 1          |

| CLI                |                   | Global Interrupt Disable                                        | 1←0                                                                                      | 1            | 1          |

| SES                |                   | Set Signed Test Flag                                            | S ← 1                                                                                    | S            | 1          |

| CLS                |                   | Clear Signed Test Flag                                          | S ← 0                                                                                    | S            | 1          |

| SEV                |                   | Set Twos Complement Overflow.                                   | V ← 1                                                                                    | V            | 1          |

| CLV<br>SET         |                   | Clear Twos Complement Overflow Set T in SREG                    | V ← 0<br>T ← 1                                                                           | T            | 1 1        |

| CLT                |                   | Clear T in SREG                                                 | T ← 0                                                                                    |              | 1          |

| SEH                |                   | Set Half Carry Flag in SREG                                     | H ← 1                                                                                    | Н            | 1          |

| CLH                |                   | Clear Half Carry Flag in SREG                                   | H ← 0                                                                                    | Н            | 1          |

| DATA TRANSFER II   | NSTRUCTIONS       |                                                                 |                                                                                          |              |            |

| MOV                | Rd, Rr            | Move Between Registers                                          | Rd ← Rr                                                                                  | None         | 1          |

| MOVW               | Rd, Rr            | Copy Register Word                                              | $Rd+1:Rd \leftarrow Rr+1:Rr$                                                             | None         | 1          |

| LDI                | Rd, K             | Load Immediate                                                  | Rd ← K                                                                                   | None         | 1          |

| LD                 | Rd, X             | Load Indirect                                                   | $Rd \leftarrow (X)$                                                                      | None         | 2          |

| LD                 | Rd, X+            | Load Indirect and Post-Inc.                                     | $Rd \leftarrow (X), X \leftarrow X + 1$                                                  | None         | 2          |

| LD                 | Rd, - X           | Load Indirect and Pre-Dec.                                      | $X \leftarrow X - 1$ , $Rd \leftarrow (X)$                                               | None         | 2          |

| LD<br>LD           | Rd, Y             | Load Indirect Load Indirect and Post-Inc.                       | $Rd \leftarrow (Y)$                                                                      | None         | 2          |

| LD                 | Rd, Y+<br>Rd, - Y | Load Indirect and Pre-Dec.                                      | $Rd \leftarrow (Y), Y \leftarrow Y + 1$ $Y \leftarrow Y - 1, Rd \leftarrow (Y)$          | None<br>None | 2          |

| LDD                | Rd,Y+q            | Load Indirect and Fre-Dec.  Load Indirect with Displacement     | $Rd \leftarrow (Y + q)$                                                                  | None         | 2          |

| LD                 | Rd, Z             | Load Indirect                                                   | $Rd \leftarrow (Z)$                                                                      | None         | 2          |

| LD                 | Rd, Z+            | Load Indirect and Post-Inc.                                     | $Rd \leftarrow (Z), Z \leftarrow Z+1$                                                    | None         | 2          |

| LD                 | Rd, -Z            | Load Indirect and Pre-Dec.                                      | $Z \leftarrow Z - 1$ , $Rd \leftarrow (Z)$                                               | None         | 2          |

| LDD                | Rd, Z+q           | Load Indirect with Displacement                                 | $Rd \leftarrow (Z + q)$                                                                  | None         | 2          |

| LDS                | Rd, k             | Load Direct from SRAM                                           | Rd ← (k)                                                                                 | None         | 2          |

| ST                 | X, Rr             | Store Indirect                                                  | (X) ← Rr                                                                                 | None         | 2          |

| ST                 | X+, Rr            | Store Indirect and Post-Inc.                                    | $(X) \leftarrow Rr, X \leftarrow X + 1$                                                  | None         | 2          |

| ST                 | - X, Rr           | Store Indirect and Pre-Dec.                                     | $X \leftarrow X - 1, (X) \leftarrow Rr$                                                  | None         | 2          |

| ST                 | Y, Rr             | Store Indirect                                                  | (Y) ← Rr                                                                                 | None         | 2          |

| ST                 | Y+, Rr            | Store Indirect and Post-Inc.                                    | $(Y) \leftarrow Rr, Y \leftarrow Y + 1$                                                  | None         | 2          |

| ST                 | - Y, Rr           | Store Indirect with Displacement                                | $Y \leftarrow Y - 1, (Y) \leftarrow Rr$                                                  | None         | 2          |

| STD<br>ST          | Y+q,Rr<br>Z, Rr   | Store Indirect with Displacement Store Indirect                 | $(Y + q) \leftarrow Rr$ $(Z) \leftarrow Rr$                                              | None<br>None | 2          |

| ST                 | Z+, Rr            | Store Indirect Store Indirect and Post-Inc.                     | $(Z) \leftarrow \square$<br>$(Z) \leftarrow Rr, Z \leftarrow Z + 1$                      | None         | 2          |

| ST                 | -Z, Rr            | Store Indirect and Prosenic.  Store Indirect and Pre-Dec.       | $Z \leftarrow Z - 1$ , $(Z) \leftarrow Rr$                                               | None         | 2          |

| STD                | Z+q,Rr            | Store Indirect with Displacement                                | $(Z+q) \leftarrow Rr$                                                                    | None         | 2          |

| STS                | k, Rr             | Store Direct to SRAM                                            | (k) ← Rr                                                                                 | None         | 2          |

| LPM                |                   | Load Program Memory                                             | R0 ← (Z)                                                                                 | None         | 3          |

| LPM                | Rd, Z             | Load Program Memory                                             | $Rd \leftarrow (Z)$                                                                      | None         | 3          |

| LPM                | Rd, Z+            | Load Program Memory and Post-Inc                                | $Rd \leftarrow (Z), Z \leftarrow Z+1$                                                    | None         | 3          |

| SPM                | İ                 | Store Program Memory                                            | (Z) ← R1:R0                                                                              | None         | -          |

# ■ ATmega329/3290/649/6490

| Mnemonics       | Operands   | Description             | Operation                                | Flags | #Clocks |

|-----------------|------------|-------------------------|------------------------------------------|-------|---------|

| IN              | Rd, P      | In Port                 | $Rd \leftarrow P$                        | None  | 1       |

| OUT             | P, Rr      | Out Port                | P ← Rr                                   | None  | 1       |

| PUSH            | Rr         | Push Register on Stack  | STACK ← Rr                               | None  | 2       |

| POP             | Rd         | Pop Register from Stack | Rd ← STACK                               | None  | 2       |

| MCU CONTROL INS | STRUCTIONS |                         |                                          |       |         |

| NOP             |            | No Operation            |                                          | None  | 1       |

| SLEEP           |            | Sleep                   | (see specific descr. for Sleep function) | None  | 1       |

| WDR             |            | Watchdog Reset          | (see specific descr. for WDR/timer)      | None  | 1       |

| BREAK           |            | Break                   | For On-chip Debug Only                   | None  | N/A     |

# 8. Ordering Information

# 8.1 ATmega329

| Speed (MHz) <sup>(3)</sup> | Power Supply | Ordering Code <sup>(2)</sup>                                                                         | Package Type <sup>(1)</sup> | Operational Range             |

|----------------------------|--------------|------------------------------------------------------------------------------------------------------|-----------------------------|-------------------------------|

| 8                          | 1.8 - 5.5V   | ATmega329V-8AU<br>ATmega329V-8AUR <sup>(4)</sup><br>ATmega329V-8MU<br>ATmega329V-8MUR <sup>(4)</sup> | 64A<br>64A<br>64M1<br>64M1  | Industrial<br>(-40°C to 85°C) |

| 16                         | 2.7 - 5.5V   | ATmega329-16AU<br>ATmega329-16AUR <sup>(4)</sup><br>ATmega329-16MU<br>ATmega329-16MUR <sup>(4)</sup> | 64A<br>64A<br>64M1<br>64M1  | Industrial<br>(-40°C to 85°C) |

Notes: 1. This device can also be supplied in wafer form. Please contact your local Atmel sales office for detailed ordering information and minimum quantities.

- 2. Pb-free packaging alternative, complies to the European Directive for Restriction of Hazardous Substances (RoHS directive). Also Halide free and fully Green.

- 3. For Speed vs.  $V_{CC}$  see Figure 28-1 on page 328 and Figure 28-2 on page 328.

- 4. Tape & Reel

|             | Package Type                                                                                 |  |  |  |  |  |

|-------------|----------------------------------------------------------------------------------------------|--|--|--|--|--|

| 64 <b>A</b> | 64-lead, 14 x 14 x 1.0 mm, Thin Profile Plastic Quad Flat Package (TQFP)                     |  |  |  |  |  |

| 64M1        | 64-pad, 9 x 9 x 1.0 mm, Quad Flat No-Lead/Micro Lead Frame Package (QFN/MLF)                 |  |  |  |  |  |

| 100A        | 100-lead, 14 x 14 x 1.0 mm, 0.5 mm Lead Pitch, Thin Profile Plastic Quad Flat Package (TQFP) |  |  |  |  |  |

# 8.2 ATmega3290

| Speed (MHz) <sup>(3)</sup> | Power Supply | Ordering Code <sup>(2)</sup>                       | Package Type <sup>(1)</sup> | Operational Range             |

|----------------------------|--------------|----------------------------------------------------|-----------------------------|-------------------------------|

| 8                          | 1.8 - 5.5V   | ATmega3290V-8AU<br>ATmega3290V-8AUR <sup>(4)</sup> | 100A<br>100A                | Industrial<br>(-40°C to 85°C) |

| 16                         | 2.7 - 5.5V   | ATmega3290-16AU<br>ATmega3290-16AUR <sup>(4)</sup> | 100A<br>100A                | Industrial<br>(-40°C to 85°C) |

Notes:

- 1. This device can also be supplied in wafer form. Please contact your local Atmel sales office for detailed ordering information and minimum quantities.

- 2. Pb-free packaging alternative, complies to the European Directive for Restriction of Hazardous Substances (RoHS directive). Also Halide free and fully Green.

- 3. For Speed vs.  $V_{\rm CC}$  see Figure 28-1 on page 328 and Figure 28-2 on page 328.

- 4. Tape & Reel

|      | Package Type                                                                                 |  |  |  |  |  |

|------|----------------------------------------------------------------------------------------------|--|--|--|--|--|

| 64A  | 64-lead, 14 x 14 x 1.0 mm, Thin Profile Plastic Quad Flat Package (TQFP)                     |  |  |  |  |  |

| 64M1 | 64-pad, 9 x 9 x 1.0 mm, Quad Flat No-Lead/Micro Lead Frame Package (QFN/MLF)                 |  |  |  |  |  |

| 100A | 100-lead, 14 x 14 x 1.0 mm, 0.5 mm Lead Pitch, Thin Profile Plastic Quad Flat Package (TQFP) |  |  |  |  |  |

# 8.3 ATmega649

| Speed (MHz) <sup>(3)</sup> | Power Supply | Ordering Code <sup>(2)</sup>                                                                         | Package Type <sup>(1)</sup> | Operational Range             |

|----------------------------|--------------|------------------------------------------------------------------------------------------------------|-----------------------------|-------------------------------|

| 8                          | 1.8 - 5.5V   | ATmega649V-8AU<br>ATmega649V-8AUR <sup>(4)</sup><br>ATmega649V-8MU<br>ATmega649V-8MUR <sup>(4)</sup> | 64A<br>64A<br>64M1<br>64M1  | Industrial<br>(-40°C to 85°C) |

| 16                         | 2.7 - 5.5V   | ATmega649-16AU<br>ATmega649-16AUR <sup>(4)</sup><br>ATmega649-16MU<br>ATmega649-16MUR <sup>(4)</sup> | 64A<br>64A<br>64M1<br>64M1  | Industrial<br>(-40°C to 85°C) |

Notes:

- 1. This device can also be supplied in wafer form. Please contact your local Atmel sales office for detailed ordering information and minimum quantities.

- 2. Pb-free packaging alternative, complies to the European Directive for Restriction of Hazardous Substances (RoHS directive). Also Halide free and fully Green.

- 3. For Speed vs.  $V_{CC}$  see Figure 28-1 on page 328 and Figure 28-2 on page 328.

- 4. Tape & Reel

| Package Type |                                                                                              |  |  |

|--------------|----------------------------------------------------------------------------------------------|--|--|

| 64A          | 64-lead, 14 x 14 x 1.0 mm, Thin Profile Plastic Quad Flat Package (TQFP)                     |  |  |

| 64M1         | 64-pad, 9 x 9 x 1.0 mm, Quad Flat No-Lead/Micro Lead Frame Package (QFN/MLF)                 |  |  |

| 100A         | 100-lead, 14 x 14 x 1.0 mm, 0.5 mm Lead Pitch, Thin Profile Plastic Quad Flat Package (TQFP) |  |  |

# 8.4 ATmega6490

| Speed (MHz) <sup>(3)</sup> | Power Supply | Ordering Code <sup>(2)</sup>                       | Package Type <sup>(1)</sup> | Operational Range             |

|----------------------------|--------------|----------------------------------------------------|-----------------------------|-------------------------------|

| 8                          | 1.8 - 5.5V   | ATmega6490V-8AU<br>ATmega6490V-8AUR <sup>(4)</sup> | 100A<br>100A                | Industrial<br>(-40°C to 85°C) |

| 16                         | 2.7 - 5.5V   | ATmega6490-16AU<br>ATmega6490-16AUR <sup>(4)</sup> | 100A<br>100A                | Industrial<br>(-40°C to 85°C) |

Notes:

- 1. This device can also be supplied in wafer form. Please contact your local Atmel sales office for detailed ordering information and minimum quantities.

- 2. Pb-free packaging alternative, complies to the European Directive for Restriction of Hazardous Substances (RoHS directive). Also Halide free and fully Green.

- 3. For Speed Grades see Figure 28-1 on page 328 and Figure 28-2 on page 328.

- 4. Tape & Reel

| Package Type |                                                                                              |  |  |

|--------------|----------------------------------------------------------------------------------------------|--|--|

| 64A          | 64-lead, 14 x 14 x 1.0 mm, Thin Profile Plastic Quad Flat Package (TQFP)                     |  |  |

| 64M1         | 64-pad, 9 x 9 x 1.0 mm, Quad Flat No-Lead/Micro Lead Frame Package (QFN/MLF)                 |  |  |

| 100A         | 100-lead, 14 x 14 x 1.0 mm, 0.5 mm Lead Pitch, Thin Profile Plastic Quad Flat Package (TQFP) |  |  |

## 10. Errata

#### 10.1 ATmega329

#### 10.1.1 ATmega329 rev. C

Interrupts may be lost when writing the timer registers in the asynchronous timer

#### 1. Interrupts may be lost when writing the timer registers in the asynchronous timer

The interrupt will be lost if a timer register that is synchronous timer clock is written when the asynchronous Timer/Counter register (TCNTx) is 0x00.

#### Problem Fix/Wortkaround

Always check that the asynchronous Timer/Counter register neither have the value 0xFF nor 0x00 before writing to the asynchronous Timer Control Register (TCCRx), asynchronous Timer Counter Register (TCNTx), or asynchronous Output Compare Register (OCRx).

#### 10.1.2 ATmega329 rev. B

Not sampled.

#### 10.1.3 ATmega329 rev. A

- LCD contrast voltage too high

- · Interrupts may be lost when writing the timer registers in the asynchronous timer

#### 1. LCD contrast voltage too high

When the LCD is active and using low power waveform, the LCD contrast voltage can be too high. This occurs when  $V_{CC}$  is higher than  $V_{LCD}$ , and when using low LCD drivetime.

#### Problem Fix/Workaround

There are several possible workarounds:

- Use normal waveform instead of low power waveform

- Use drivetime of 375 µs or longer

#### 2. Interrupts may be lost when writing the timer registers in the asynchronous timer

The interrupt will be lost if a timer register that is synchronous timer clock is written when the asynchronous Timer/Counter register (TCNTx) is 0x00.

#### **Problem Fix/Wortkaround**

Always check that the asynchronous Timer/Counter register neither have the value 0xFF nor 0x00 before writing to the asynchronous Timer Control Register (TCCRx), asynchronous Timer Counter Register (TCNTx), or asynchronous Output Compare Register (OCRx).

## 10.2 ATmega3290

#### 10.2.1 ATmega3290 rev. C

Interrupts may be lost when writing the timer registers in the asynchronous timer

#### 1. Interrupts may be lost when writing the timer registers in the asynchronous timer

The interrupt will be lost if a timer register that is synchronous timer clock is written when the asynchronous Timer/Counter register (TCNTx) is 0x00.

#### Problem Fix/Wortkaround

Always check that the asynchronous Timer/Counter register neither have the value 0xFF nor 0x00 before writing to the asynchronous Timer Control Register (TCCRx), asynchronous Timer Counter Register (TCNTx), or asynchronous Output Compare Register (OCRx).

#### 10.2.2 ATmega3290 rev. B

Not sampled.

#### 10.2.3 ATmega3290 rev. A

- LCD contrast voltage too high

- Interrupts may be lost when writing the timer registers in the asynchronous timer

#### 1. LCD contrast voltage too high

When the LCD is active and using low power waveform, the LCD contrast voltage can be too high. This occurs when  $V_{CC}$  is higher than  $V_{LCD}$ , and when using low LCD drivetime.

#### Problem Fix/Workaround

There are several possible workarounds:

- Use normal waveform instead of low power waveform

- Use drivetime of 375 µs or longer

#### 2. Interrupts may be lost when writing the timer registers in the asynchronous timer

The interrupt will be lost if a timer register that is synchronous timer clock is written when the asynchronous Timer/Counter register (TCNTx) is 0x00.

#### Problem Fix/Wortkaround

Always check that the asynchronous Timer/Counter register neither have the value 0xFF nor 0x00 before writing to the asynchronous Timer Control Register (TCCRx), asynchronous Timer Counter Register (TCNTx), or asynchronous Output Compare Register (OCRx).

## 10.3 ATmega649

#### 10.3.1 ATmega649 rev. A

- Interrupts may be lost when writing the timer registers in the asynchronous timer

- 1. Interrupts may be lost when writing the timer registers in the asynchronous timer

The interrupt will be lost if a timer register that is synchronous timer clock is written when the asynchronous Timer/Counter register (TCNTx) is 0x00.

#### Problem Fix/Wortkaround

Always check that the asynchronous Timer/Counter register neither have the value 0xFF nor 0x00 before writing to the asynchronous Timer Control Register (TCCRx), asynchronous Timer Counter Register (TCNTx), or asynchronous Output Compare Register (OCRx).

# 10.4 ATmega6490

#### 10.4.1 ATmega6490 rev. A

- · Interrupts may be lost when writing the timer registers in the asynchronous timer

- 1. Interrupts may be lost when writing the timer registers in the asynchronous timer. The interrupt will be lost if a timer register that is synchronous timer clock is written when the asynchronous Timer/Counter register (TCNTx) is 0x00.

#### Problem Fix/Wortkaround

Always check that the asynchronous Timer/Counter register neither have the value 0xFF nor 0x00 before writing to the asynchronous Timer Control Register (TCCRx), asynchronous Timer Counter Register (TCNTx), or asynchronous Output Compare Register (OCRx).

# 11. Datasheet Revision History

Please note that the referring page numbers in this section are referring to this document. The referring revision in this section are referring to the document revision.

#### 11.1 Rev. 2552K - 04/11

- 1. Removed "Preliminary" from the front page.

- 2. Removed "Disclaimer Section" from the datasheet.

- 3. Updated Table 28-5 on page 330 "BODLEVEL Fuse Coding(1)".

- 4. Updated Table 28-8 on page 334 "LCD Controller Characteristics".

- 5. Updated "Ordering Information" on page 372 to include "Tape & Reel" devices. The "Al" and "Ml" devices removed.

- 6. Updated "Errata" on page 379.

- 7. Updated the datasheet according to the Atmel new brand style guide, including the last page.

#### 11.2 Rev. 2552J - 08/07

- 1. Updated "Features" on page 1.

- 2. Added "Data Retention" on page 9.

- 3. Updated "Serial Programming Algorithm" on page 309.

- 4. Updated "Speed Grades" on page 328.

- 5. Updated "System and Reset Characteristics" on page 330.

- 6. Moved Register Descriptions to the end of each chapter.

#### 11.3 Rev. 2552I - 04/07

- 1. Updated date in backpage

- 2. Updated column in Table 28-5 on page 330.

#### 11.4 Rev. 2552H - 11/06

- 1. Updated Table 28-7 on page 333.

- 2. Updated note in Table 28-7 on page 333 and Table 28-2 on page 329.

#### 11.10 Rev. 2552B - 05/05

- 1. MLF-package alternative changed to "Quad Flat No-Lead/Micro Lead Frame Package QFN/MLF".

- 2. Added "Pin Change Interrupt Timing" on page 54.

- 3. Updated Table 23-6 on page 242, Table 23-7 on page 243 and Table 27-15 on page 310.

- 4. Added Figure 27-12 on page 312.

- 5. Updated Figure 22-9 on page 219 and Figure 27-5 on page 304.

- 6. Updated algorithm "Enter Programming Mode" on page 299.

- 7. Added "Supply Current of I/O modules" on page 340.

- 8. Updated "Ordering Information" on page 372.

#### 11.11 Rev. 2552A -11/04

1. Initial version.