# Toshiba Semiconductor and Storage - <u>TMP86FS49BFG(CZHZ) Datasheet</u>

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Details                    |                                                                                          |

|----------------------------|------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                   |

| Core Processor             | 870/C                                                                                    |

| Core Size                  | 8-Bit                                                                                    |

| Speed                      | 16MHz                                                                                    |

| Connectivity               | I <sup>2</sup> C, SIO, UART/USART                                                        |

| Peripherals                | LED, PWM, WDT                                                                            |

| Number of I/O              | 56                                                                                       |

| Program Memory Size        | 60KB (60K x 8)                                                                           |

| Program Memory Type        | FLASH                                                                                    |

| EEPROM Size                | <u>.</u>                                                                                 |

| RAM Size                   | 2K x 8                                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                              |

| Data Converters            | A/D 16x10b                                                                               |

| Oscillator Type            | Internal                                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                        |

| Mounting Type              | Surface Mount                                                                            |

| Package / Case             | 64-BQFP                                                                                  |

| Supplier Device Package    | 64-QFP (14x14)                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/toshiba-semiconductor-and-storage/tmp86fs49bfg-czhz |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                    | 7                         | 6                         | 5                           | 4                         | 3                    | 2              | 1                         | 0                         |                            |          |

|--------------------|---------------------------|---------------------------|-----------------------------|---------------------------|----------------------|----------------|---------------------------|---------------------------|----------------------------|----------|

| P1DR<br>(0001H)    | P17<br>TC6<br><u>PWM6</u> | P16<br>TC5<br><u>PWM5</u> | P15<br>TC2<br>INT3          | P14<br>TC4<br><u>PWM4</u> | P13<br>TC3<br>PWM3   | P12<br>PPG     | P11<br>DVO                | P10<br>TC1                | (Initial value: 0000 0000) |          |

| R/W                | PDO6<br>PPG6              | PDO5                      | 1113                        | PVVM4<br>PDO4<br>PPG4     | PDO3                 |                |                           |                           |                            |          |

| I                  |                           |                           |                             |                           |                      |                |                           |                           |                            |          |

| P1CR               | 7                         | 6                         | 5                           | 4                         | 3                    | 2              | 1                         | 0                         |                            |          |

| (0009H)            |                           |                           |                             |                           |                      |                |                           |                           | (Inițial value: 0000 0000) |          |

|                    | P1CR                      | I/O co                    | ontrol for po               | rt P1 (Spec               | ified for eac        | ch bit)        | 0:<br>1:                  | Input mode<br>Output mode | de P                       | R/W      |

|                    |                           |                           |                             |                           |                      |                | ~                         |                           |                            | <u> </u> |

|                    |                           |                           |                             |                           |                      |                |                           | $\langle \rangle$         |                            |          |

|                    |                           |                           |                             |                           |                      |                |                           |                           | $\diamond$                 |          |

|                    |                           |                           |                             |                           |                      |                |                           |                           |                            |          |

|                    |                           |                           |                             |                           |                      |                | $\searrow$                |                           | $\bigcirc$                 |          |

|                    |                           |                           |                             |                           | (                    |                | >                         | ((                        | 75                         |          |

|                    |                           |                           |                             |                           |                      | $\searrow$     | ſ                         | $\sim$                    |                            |          |

|                    |                           |                           |                             | ((                        | $\sim$               | >              | $\langle \langle \rangle$ | ))                        |                            |          |

|                    |                           |                           |                             |                           | $\bigcirc$           |                | ~                         |                           |                            |          |

|                    |                           |                           |                             |                           | ))                   | 5              | $\square$                 |                           |                            |          |

|                    |                           |                           | (7                          | 27                        |                      |                | $\mathbb{Z}$              |                           |                            |          |

|                    |                           | $\int \int$               | $\mathcal{D}_{\mathcal{A}}$ | $\bigcirc$                | $\sim$               | $\overline{0}$ |                           |                           |                            |          |

|                    |                           | $\langle \langle \rangle$ |                             | 7                         | $\langle \rangle$    |                | )                         |                           |                            |          |

|                    |                           |                           | $\searrow$                  | $\langle$                 | $\overline{\langle}$ | $\geq$         |                           |                           |                            |          |

|                    | $\sim$                    | 2 1                       |                             | $\sim$                    |                      | >              |                           |                           |                            |          |

|                    | $\square$                 |                           |                             | $\triangleleft$           |                      |                |                           |                           |                            |          |

|                    |                           | ))                        | $ \land ($                  | $\bigcirc$                | $\supset$            |                |                           |                           |                            |          |

| $\langle  \rangle$ | $\geq$                    |                           | $(\mathcal{S})$             | $\bigcirc$                |                      |                |                           |                           |                            |          |

|                    | >                         |                           | $\sim$                      | >                         |                      |                |                           |                           |                            |          |

|                    |                           |                           |                             |                           |                      |                |                           |                           |                            |          |

### 8.2 TimerCounter Control

The TimerCounter 1 is controlled by the TimerCounter 1 control register (TC1CR) and two 16-bit timer registers (TC1DRA and TC1DRB).

| Timer Regist     | er                                                                              |                                  |               |                          |                         |                          |                         |               |                | $\sim$                  |                  |                   |                   |              |

|------------------|---------------------------------------------------------------------------------|----------------------------------|---------------|--------------------------|-------------------------|--------------------------|-------------------------|---------------|----------------|-------------------------|------------------|-------------------|-------------------|--------------|

|                  | 15                                                                              | 14 1                             | 3 12          | 11                       | 10                      | 9 8                      | 7                       | ,             | 6              | 5 4                     | 3                | 2                 | 1                 | 0            |

| TC1DRA           |                                                                                 |                                  | TC1DRA        | H (0011H)                | )                       |                          |                         |               |                | T¢1D                    | RAL (001         | 0H)               |                   |              |

| (0011H, 0010H)   |                                                                                 | (Initia                          | l value: 1111 | 1 1111 11                | 11 1111)                |                          |                         |               |                | R                       | ead/Write        |                   |                   |              |

| TC1DRB           |                                                                                 |                                  | TC1DRBI       | H (0013H)                | )                       |                          |                         | <             |                |                         | RBL (001         | 2H)               |                   |              |

| (0013H, 0012H)   |                                                                                 | (Initia                          | l value: 1111 | 1 1111 11                | 11 1111)                |                          |                         | Read          | Write (W       | rite enable             | ed only in       | the PPG o         | output moo        | le)          |

| TimerCou         | inter 1 C                                                                       | Control Re                       | egister       |                          |                         |                          |                         | C             | $(\mathbb{C})$ | )                       | /                | $\frown$          |                   |              |

|                  |                                                                                 |                                  | •             |                          |                         |                          |                         | 4(            | $\searrow$     |                         | A                | $( \ )$           | >                 |              |

|                  | 7                                                                               | 6                                | 5             | 4                        | 3                       | 2                        | 1                       | $\rightarrow$ | 0              |                         | $\mathcal{L}$    | $\langle \rangle$ | Ŷ                 |              |

| TC1CR<br>(0026H) | TFF1                                                                            | ACAP1<br>MCAP1<br>METT1<br>MPPG1 | TC1           | S                        | тс                      | ICK                      |                         | TOIN          | 1              | Read/Wri<br>(Initial va | ite<br>lue: 0000 | 0000              |                   |              |

| 7554             | T                                                                               |                                  |               |                          |                         |                          |                         | /             | 1.0.1          | (Ć/                     |                  |                   |                   | <b>D</b> 444 |

| TFF1             | Timer F/F1                                                                      |                                  | 0: Clear      |                          |                         |                          | $\checkmark$            |               | 1: Set         |                         | <u>))</u>        |                   |                   | R/W          |

| ACAP1            | Auto captu                                                                      |                                  | U:Auto-       | capture di               |                         | $\sim \sim \sim$         | >                       |               | 1:Auto-c       | apture en               | able             |                   |                   |              |

| MCAP1            | ment mode                                                                       | h measure-<br>e control          | 0:Doub        | le edge ca               | apture                  | $\searrow$               |                         | $\square$     | 1:Single       | edge cap                | oture            |                   |                   | R/W          |

| METT1            | External tri<br>mode cont                                                       |                                  | 0:Trigge      | 0:Trigger start and stop |                         |                          |                         |               |                |                         |                  |                   |                   |              |

| MPPG1            | PPG outpu                                                                       | it control                       | 0:Conti       | nuous pul                | se generat              | ion                      |                         | $\nearrow$    | 1:One-s        | hot                     |                  |                   |                   |              |

|                  |                                                                                 |                                  |               | $\mathcal{C}$            |                         |                          | $\langle \cdot \rangle$ | Timer         | Extrig-<br>ger | Event                   | Win-<br>dow      | Pulse             | PPG               |              |

|                  |                                                                                 |                                  | 00: Sto       | p and cou                | nter clear              | ~                        | $\sim$                  | 9             | 0              | 0                       | 0                | 0                 | 0                 |              |

|                  |                                                                                 |                                  | 01. Cor       | mmand sta                | art                     | $\langle \rangle$        | $\overline{)}$          | 6             | -              | -                       | -                | -                 | 0                 |              |

|                  |                                                                                 | $\bigcap$                        | 10: Risi      | ing edge s               |                         | (A)                      | $\rightarrow$           |               |                |                         |                  |                   |                   |              |

| TC1S             | TC1 start control<br>Rising edge count (Event)<br>Positive logic count (Window) |                                  |               |                          | G)                      | <sup>3)</sup> –          | 0                       | 0             | 0              | 0                       | 0                | R/W               |                   |              |

|                  |                                                                                 |                                  |               |                          |                         |                          |                         |               |                |                         |                  |                   |                   |              |

|                  |                                                                                 |                                  | 11: Fall      | ing edge s               |                         | $\geq$                   |                         |               |                |                         |                  |                   |                   |              |

|                  | $\sim$                                                                          | $\land$                          | ∼<br>Fall     | lina edae i              | (Ex-trigg<br>count (Eve | er/Pulse/PP(             | G)                      | -             | 0              | 0                       | 0                | 0                 | 0                 |              |

|                  | $\sim$                                                                          | $\langle \rangle$                |               | • •                      | c count (W              | V.                       |                         |               |                |                         |                  |                   |                   |              |

|                  |                                                                                 | $\overline{}$                    |               |                          |                         | NORMAL                   | 1/2, ID                 | LE1/2 n       | node           |                         |                  |                   | SLOW,             |              |

| $\langle$        |                                                                                 | ))                               |               |                          | DV7CK                   | = 0                      |                         |               | DV70           | CK = 1                  |                  | Divider           | SLEEP<br>mode     |              |

| TC1CK            | TC1 source clock select                                                         |                                  | f 00          |                          | fc/2 <sup>11</sup>      |                          |                         |               | fs             | /2 <sup>3</sup>         |                  | DV9               | fs/2 <sup>3</sup> | R/W          |

| IN INA THE       |                                                                                 | V01                              |               |                          |                         | fc/2 <sup>7</sup>        |                         |               |                | DV5                     | -                | 10.00             |                   |              |

|                  |                                                                                 |                                  | 10            |                          | fc/2 <sup>3</sup>       |                          |                         |               | fc             | /2 <sup>3</sup>         |                  | DV1               | _                 |              |

|                  | $\searrow$                                                                      |                                  | 11            | 7                        |                         | E                        | Externa                 | l clock       | (TC1 pin       |                         |                  | 1                 |                   |              |

|                  |                                                                                 |                                  | 00: Tim       | er/externa               | al trigger tin          | ner/event cou            | unter n                 | node          | •              | . ,                     |                  |                   |                   |              |

| TC1M             | TC1 opera                                                                       | ting mode                        |               | ndow mod                 |                         |                          |                         |               |                |                         |                  |                   |                   | R/W          |

|                  | select                                                                          |                                  |               |                          | neasureme<br>mmable pu  | nt mode<br>Ise generate) | ) outpu                 | t mode        |                |                         |                  |                   |                   |              |

|                  |                                                                                 |                                  |               | (                        |                         | <b>U</b>                 |                         |               |                |                         |                  |                   |                   |              |

Note 1: fc: High-frequency clock [Hz], fs: Low-frequency clock [Hz]

Note 2: The timer register consists of two shift registers. A value set in the timer register becomes valid at the rising edge of the first source clock pulse that occurs after the upper byte (TC1DRAH and TC1DRBH) is written. Therefore, write the lower byte and the upper byte in this order (it is recommended to write the register with a 16-bit access instruction). Writing only the lower byte (TC1DRAL and TC1DRBL) does not enable the setting of the timer register.

Note 3: To set the mode, source clock, PPG output control and timer F/F control, write to TC1CR during TC1S=00. Set the timer F/ F1 control until the first timer start after setting the PPG mode.

#### 8.3 Function

TimerCounter 1 has six types of operating modes: timer, external trigger timer, event counter, window, pulse width measurement, programmable pulse generator output modes.

#### 8.3.1 Timer mode

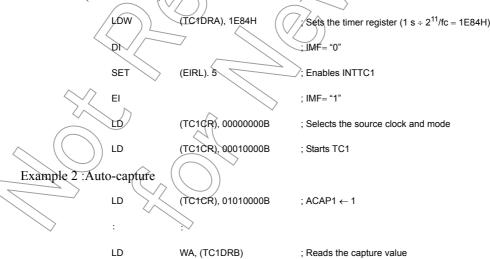

In the timer mode, the up-counter counts up using the internal clock. When a match between the up-counter and the timer register 1A (TC1DRA) value is detected, an INTTC1 interrupt is generated and the up-counter is cleared. After being cleared, the up-counter restarts counting. Setting TC1CR<ACAP1> to "1" captures the up-counter value into the timer register 1B (TC1DRB) with the auto-capture function. Use the auto-capture function in the operative condition of TC1. A captured value may not be fixed if it's read after the execution of the timer stop or auto-capture disable. Read the capture value in a capture enabled condition. Since the up-counter value is captured into TC1DRB by the source clock of up-counter after setting TC1CR<ACAP1> to "1". Therefore, to read the captured value, wait at least one cycle of the internal source clock before reading TC1DRB for the first time.

| TC1CK |                    |                             | EEP mode   |                      |                    |                                  |

|-------|--------------------|-----------------------------|------------|----------------------|--------------------|----------------------------------|

| TUTUK | DV7C               | CK = 0                      | DV7C       | СК = 1               | SLOW, SL           | EEP mode                         |

|       | Resolution<br>[μs] | Maximum Time Setting<br>[s] | Resolution | Maximum Time Setting | Resolution<br>[µs] | Maximum<br>Time Set-<br>ting [s] |

| 00    | 128                | 8.39                        | 244.14     | 16.0                 | 244.14             | 16.0                             |

| 01    | 8.0                | 0.524                       | 8.0        | 0.524                | -                  | -                                |

| 10    | 0.5                | 32.77 m                     | 0.5        | 32.77 m              | -                  | -                                |

| Table 8-1 | Internal Source Clock for | TimerCounter 1 | l (Example) fc = ' | 16 MHz, fs = 32,768 kHz) |

|-----------|---------------------------|----------------|--------------------|--------------------------|

|-----------|---------------------------|----------------|--------------------|--------------------------|

Example 1 :Setting the timer mode with source clock  $fc/2^{11}$  [Hz] and generating an interrupt 1 second later (fc = 16 MHz, TBTCR<DV7CK> = "0")

Note: Since the up-counter value is captured into TC1DRB by the source clock of up-counter after setting TC1CR<ACAP1> to "1". Therefore, to read the captured value, wait at least one cycle of the internal source clock before reading TC1DRB for the first time.

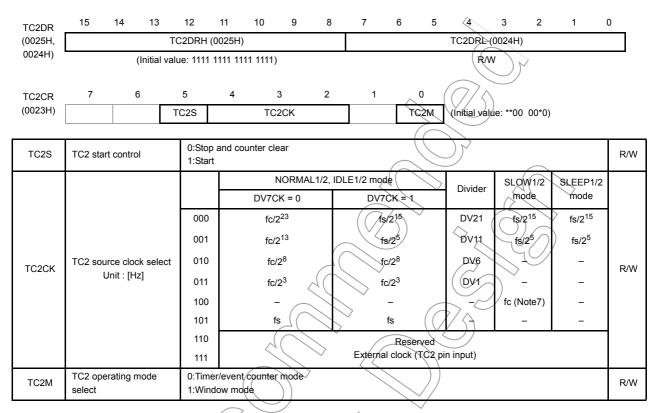

### 9.2 Control

The timer/counter 2 is controlled by a timer/counter 2 control register (TC2CR) and a 16-bit timer register 2 (TC2DR).

Note 1: fc: High-frequency clock [Hz], fs: Low/frequency clock [Hz], \*: Don't care

Note 2: When writing to the Timer Register 2 (TC2DR), always write to the lower side (TC2DRL) and then the upper side (TC2DRH) in that order. Writing to only the lower side (TC2DRL) or the upper side (TC2DRH) has no effect.

- Note 3: The timer register 2 (TC2DR) uses the value previously set in it for coincidence detection until data is written to the upper side (TC2DRH) after writing data to the lower side (TC2DRL).

- Note 4: Set the mode and source clock when the TC2 stops (TC2S = 0).

- Note 5: Values to be loaded to the timer register must satisfy the following condition.

TC2DR > 1 (TC2DR<sub>15</sub> to TC2DR<sub>11</sub> > 1 at warm up)

Note 6: If a read instruction is executed for TC2CR, read data of bit 7, 6 and 1 are unstable.

Note 7: The high-frequency clock (fc) canbe selected only when the time mode at SLOW2 mode is selected.

Note 8: On entering STOP mode, the TC2 start control (TC2S) is cleared to "0" automatically. So, the timer stops. Once the STOP mode has been released, to start using the timer counter, set TC2S again.

#### 9.3 Function

The timer/counter 2 has three operating modes: timer, event counter and window modes.

And if fc or fs is selected as the source clock in timer mode, when switching the timer mode from SLOW1 to NORMAL2, the timer/counter2 can generate warm-up time until the oscillator is stable.

#### 9.3.1 Timer mode

In this mode, the internal clock is used for counting up. The contents of TC2DR are compared with the contents of up counter. If a match is found, a timer/counter 2 interrupt (INTTC2) is generated, and the counter is cleared. Counting up is resumed after the counter is cleared.

When fc is selected for source clock at SLOW2 mode, lower 11-bits of TC2DR are ignored and generated a interrupt by matching upper 5-bits only. Though, in this situation, it is necessary to set TC2DRH only.

Table 9-1 Source Clock (Internal clock) for Timer/Counter2 (at fc = 16 MHz, DV7CK=0)

| TC2C |             | NORMAL1/2,                | (// s)     | SLOW1/2 mode SLEEP1/2     |                 |                                 |                 |                                 |

|------|-------------|---------------------------|------------|---------------------------|-----------------|---------------------------------|-----------------|---------------------------------|

| к    | DV7C        | CK = 0                    | DV7        |                           | /2 mode         | $\mathcal{D}$                   | /2 11000        |                                 |

|      | Resolution  | Maximum Time Set-<br>ting | Resolution | Maximum Time Set-<br>ting | Resolu-<br>tion | Maxi-<br>mum<br>Time<br>Setting | Resolu-<br>tion | Maxi-<br>mum<br>Time<br>Setting |

| 000  | 524.29 [ms] | 9.54 [h]                  | 1[5]       | 18.2 [h]                  | 1][s]           | 18.2 [h]                        | 1 [s]           | 18.2 [h]                        |

| 001  | 512.0 [ms]  | 33.55 [s]                 | 0.98.[ms]  | 1.07 [min]                | 0.98 [ms]       | 1.07<br>[min]                   | 0.98 [ms]       | 1.07<br>[min]                   |

| 010  | 16.0 [ms]   | 1.05 [s]                  | 16.0 [ms]  | 1:05 [s]                  | -               | -                               | -               | -                               |

| 011  | 0.5 [ms]    | 32.77 [ms]                | 0.5 [ms]   | 32.77 [ms]                | -               | -                               | -               | -                               |

| 100  | _           | - ((                      | -          |                           | 62.5 [ns]       | -                               | -               | -                               |

| 101  | 30.52 [ms]  | 2 [s]                     | 30.52 [ms] | 2.[s]                     | -               | -                               | -               | -                               |

Note: When fc is selected as the source clock in timer mode, it is used at warm-up for switching from SLOW1 mode to NORMA(2 mode.

Example :Sets the timer mode with source clock  $fc/2^3$  [Hz] and generates an interrupt every 25 ms (at fc = 16 MHz)

- ; Sets TC2DR (25 ms <sup>3</sup> 2<sup>8</sup>/fc = 061AH)

- ; IMF= "0"

- ; Enables INTTC2 interrupt

- ; IMF= "1"

- ; Source clock / mode select

- ; Starts Timer

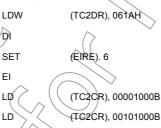

### 10.8-Bit TimerCounter (TC3, TC4)

### 10.1 Configuration

Note 7: The timer register settings are limited depending on the timer operating mode. For the detailed descriptions, see Table 10-3.

Note 8: The operating clock fc in the SLOW or SLEEP mode can be used only as the high-frequency warm-up mode.

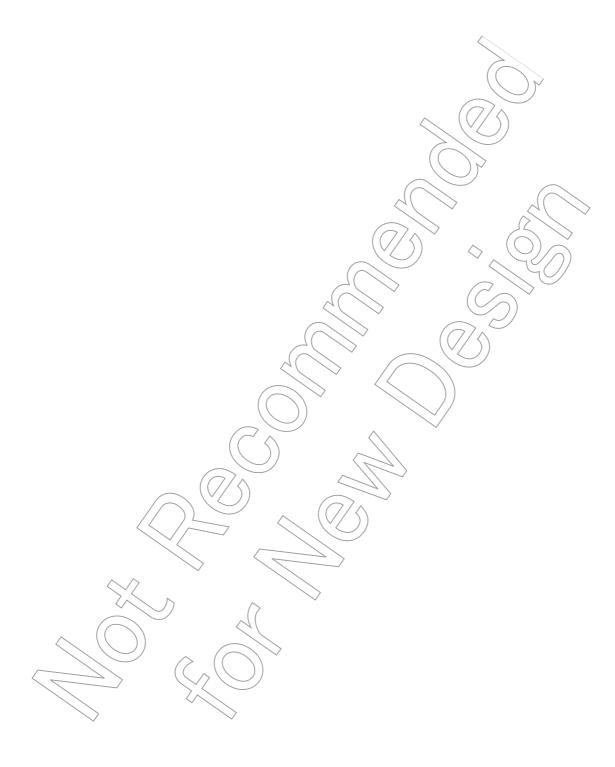

The TimerCounter 4 is controlled by the TimerCounter 4 control register (TC4CR) and two 8-bit timer registers (TTREG4 and PWREG4).

Note 1: fc: High-frequency clock [Hz] fs: Low-frequency clock [Hz]

- Note 2: Do not change the TC4M, TC4CK and TFF4 settings while the timer is running.

- Note 3: To stop the timer operation (TC4S=  $1 \rightarrow 0$ ), do not change the TC4M, TC4CK and TFF4 settings.

- To start the timer operation (TC4S= 0  $\rightarrow$  1), TC4M, TC4CK and TFF4 can be programmed.

- Note 4: When TC4M= 1\*\* (upper byte in the 16-bit mode), the source clock becomes the TC3 overflow signal regardless of the TC4CK setting.

- Note 5: To use the TimerCounter in the 16-bit mode, select the operating mode by programming TC4M, where TC3CR<TC3M> must be set to 011.

Example :Generating 1024 Hz pulse using TC4 (fc = 16.0 MHz)

#### 11.3.4 8-Bit Pulse Width Modulation (PWM) Output Mode (TC5, 6)

This mode is used to generate a pulse-width modulated (PWM) signals with up to 8 bits of resolution. The up-counter counts up using the internal clock.

When a match between the up-counter and the PWREGj value is detected, the logic level output from the timer F/Fj is switched to the opposite state. The counter continues counting. The logic level output from the timer F/Fj is switched to the opposite state again by the up-counter overflow, and the counter is cleared. The INTTCj interrupt request is generated at this time.

Since the initial value can be set to the timer F/Fj by TCjCR<TFFj>, positive and negative pulses can be generated. Upon reset, the timer F/Fj is cleared to 0.

(The logic level output from the PWMj pin is the opposite to the timer F/Fj togic level.)

Since PWREGj in the PWM mode is serially connected to the shift register, the value set to PWREGj can be changed while the timer is running. The value set to PWREGj during a run of the timer is shifted by the INTTCj interrupt request and loaded into PWREGj. While the timer is stopped, the value is shifted immediately after the programming of PWREGj. If executing the read instruction to PWREGj during PWM output, the value in the shift register is read, but not the value set in PWREGj. Therefore, after writing to PWREGj, the reading data of PWREGj is previous value until INTTCj is generated.

For the pin used for PWM output, the output latch of the 1/0 port must be set to 1.

- Note 1: In the PWM mode, program the timer register PWREGj immediately after the INTTCj interrupt request is generated (normally in the INTTCj interrupt service routine.) If the programming of PWREGj and the interrupt request occur at the same time, an unstable value is shifted, that may result in generation of the pulse different from the programmed value until the next INTTCj interrupt request is generated.

- Note 2: When the timer is stopped during PWM output, the PWMj pin holds the output status when the timer is stopped. To change the output status, program TCjCR<TFFj> after the timer is stopped. Do not change the TCjCR<TFFj> upon stopping of the timer.

Example: Fixing the PWMj pin to the high level when the TimerCounter is stopped CLR (TCjCR).3: Stops the timer.

- CLR (TCjCR).7: Sets the PWMj pin to the high level.

- Note 3: To enter the STOP mode during PWM output, stop the timer and then enter the STOP mode. If the STOP mode is entered without stopping the timer when fc, fc/2 or fs is selected as the source clock, a pulse is output from the PWMj pin during the warm-up period time after exiting the STOP mode.

- Note 4: j = 5, 6

| Source Clock                                   |                              | Reso        | lution          | Repeated Cycle |                 |  |

|------------------------------------------------|------------------------------|-------------|-----------------|----------------|-----------------|--|

| NORMAL1/2, IDLE1/2 mode   DV7CK = 0 DV7CK = 1  | SLOW1/2,<br>SLEEP1/2<br>mode | fc = 16 MHz | fs = 32.768 kHz | fc = 16 MHz    | fs = 32.768 kHz |  |

| fc/2 <sup>11</sup> [Hz] fs/2 <sup>3</sup> [Hz] | fs/2 <sup>3</sup> [Hz]       | 128 μs      | 244.14 μs       | 32.8 ms        | 62.5 ms         |  |

| fc/2 <sup>7</sup> fc/2 <sup>7</sup>            | 4(                           | 8 µs        | -               | 2.05 ms        | -               |  |

| fc/2 <sup>5</sup> fc/2 <sup>5</sup>            |                              | 2 μs        | -               | 512 μs         | -               |  |

| fc/2 <sup>3</sup> fc/2 <sup>3</sup>            | $^{>}$ (( -))                | 500 ns      | -               | 128 μs         | -               |  |

| fs fs                                          | fs                           | 30.5 μs     | 30.5 μs         | 7.81 ms        | 7.81 ms         |  |

| fc/2 fc/2                                      | ~                            | 125 ns      | -               | 32 µs          | -               |  |

| fc 🗸 fc                                        | ~ _                          | 62.5 ns     | -               | 16 μs          | -               |  |

Table 11-5 PWM Output Mode

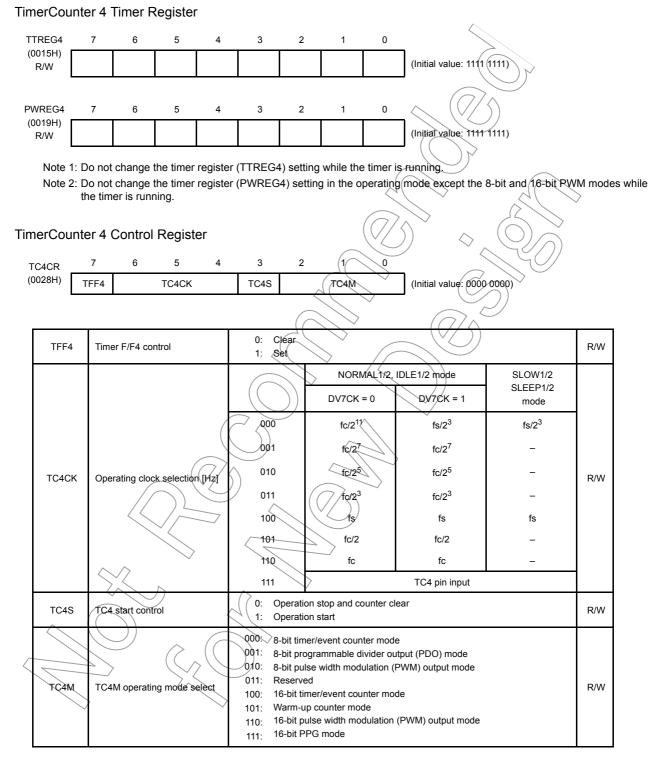

# 13. Asynchronous Serial interface (UART2)

### 13.1 Configuration

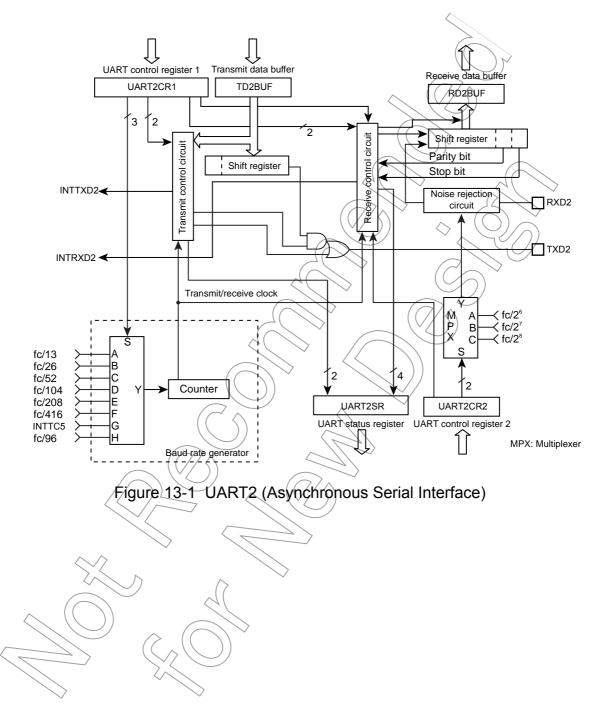

### 14.2 Control

The SIO is controlled using the serial interface control register (SIO1CR). The operating status of the serial interface can be inspected by reading the status register (SIO1CR).

- Note 1: When SIO1CR<SIOINH> is set to "1", SIO1CR<SIOS>, SIO1SR register, SIO1RDB register and SIO1TDB register are initialized.

- Note 2: Transfer mode, direction of transfer and serial clock must be select during the transfer is stopping (when SIO1SR<SIOF> "0").

Note 3: fc: High-frequency clock [Hz], fs: Low-frequency clock [Hz], \*: Don't care

(2) During the transmit/receive operation

When data is written to SIO1TDB, SIO1SR<TXF> is cleared to "0" and when a data is read from SIO1RDB, SIO1SR<RXF> is cleared to "0".

In internal clock operation, in case of the condition described below, the serial clock stops to "H" level by an automatic-wait function when all of the bit set in the data has been transmitted.

- Next transmit data is not written to SIO1TDB after reading a received data from SIO1RDB.

- Received data is not read from SIO1RDB after writing a next transmit data to SIO1TDB.

- Neither SIO1TDB nor SIO1RDB is accessed after transmission.

The automatic wait function is released by writing the next transmit data to SIO1TDB after reading the received data from SIO1RDB, or reading the received data from SIO1RDB after writing the next data to SIO1TDB.

Then, transmit/receive operation is restarted after maximum 1 eycle of serial clock.

In external clock operation, reading the received data from SIO1RDB and writing the next data to SIO1TDB must be finished before the shift operation of the next data begins.

If the transmit data is not written to SIO1TDB after SIO1SR<TXF> is set to "1", transmit error occurs immediately after shift operation is started. When the transmit error occurred, SIO1SR<TXERR> is set to "1".

If received data is not read out from SIO1RDB before next shift operation starts after setting SIO1SR<RXF> to "1", receive error occurs immediately after shift operation is finished. When the receive error has occurred, SIO1SR<RXERP is set to "1".

(3) Stopping the transmit/receive operation

There are two ways for stopping the transmit/receive operation.

• The way of clearing SIO1 CR<SIOS>.

When SIO1CR<SIOS> is cleared to "0", transmit/receive operation is stopped after all transfer of the data is finished. When transmit/receive operation is finished, SIO1SR<SIOF> is cleared to "0" and \$01 pin is kept in high level.

In external clock operation, SIO1CR SIOS must be cleared to "0" before SIO1SR SEF is set to "1" by beginning next transfer.

• The way of setting SIQ1CR < \$IOINH>.

Transmit/receive operation is stopped immediately after SIO1CR<SIOINH> is set to "1". In this case, SIO1CR<SIOS>, SIO1SR register, SIO1RDB register and SIO1TDB register are initialized.

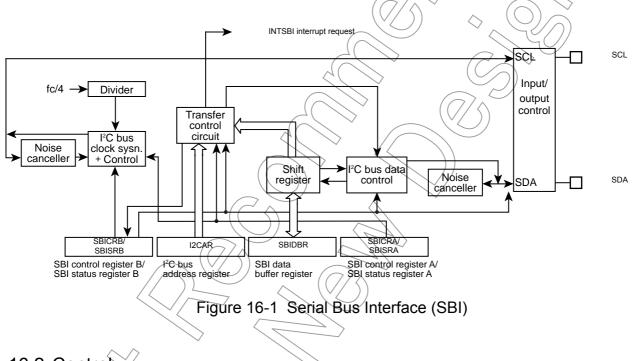

# 16. Serial Bus Interface(I<sup>2</sup>C Bus) Ver.-D (SBI)

The TMP86FS49BFG has a serial bus interface which employs an  $I^2C$  bus.

The serial interface is connected to an external devices through SDA and SCL.

The serial bus interface pins are also used as the port. When used as serial bus interface pins, set the output latches of these pins to "1". When not used as serial bus interface pins, the port is used as a normal I/O port.

- Note 1: The serial bus interface can be used only in NORMAL1/2 and IDLE1/2 mode. It can not be used in IDLE0, SLOW1/2 and SLEEP0/1/2 mode.

- Note 2: The serial bus interface can be used only in the Standard mode of I<sup>2</sup>C. The fast mode and the high-speed mode can not be used.

Note 3: Please refer to the I/O port section about the detail of setting port.

### 16.1 Configuration

16.2 Control

The following registers are used for control the serial bus interface and monitor the operation status.

- Serial bus interface control register A (SBICRA)

- Serial bus interface control register B (SBICRB)

- Serial bus interface data buffer register (SBIDBR)

- 1<sup>2</sup>C bus address register (12CAR)

- Serial bus interface status register A (SBISRA)

- Serial bus interface status register B (SBISRB)

#### 16.3 Software Reset

A serial bus interface circuit has a software reset function, when a serial bus interface circuit is locked by an external noise, etc.

To reset the serial bus interface circuit, write "10", "01" into the SWRST (Bit1, 0 in SBICRB).

And a status of software reset canbe read from SWRMON (Bit0 in SBISRA).

In the slave mode, the conditions of generating INTSBI interrupt request are follows:

- At the end of acknowledge signal when the received slave address matches to the value set by the I2CAR

- At the end of acknowledge signal when a "GENERAL CALL" is received

- At the end of transferring or receiving after matching of slave address or receiving of "GENERAL CALL"

When a serial bus interface interrupt request occurs, the PIN (Bit4 in SBISRB) is cleared to "0". During the time that the PIN is "0", the SCL pin is pulled-down to low level.

Either writing data to SBIDBR or reading data from the SBIDBR sets the PIN to "1"

The time from the PIN being set to "1" until the SCL pin is released takes the

Although the PIN (Bit4 in SBICRB) can be set to "1" by the softrware, the PIN can not be cleared to "0" by the softrware.

Note: When the arbitration lost occurs, if the slave address sent from the other master devices is not match, the INTSBI interrupt request is generated. But the PIN is not cleared.

#### 16.5.9 Setting of I<sup>2</sup>C bus mode

The SBIM (Bit3 and 2 in SBICRB) is used to set  $T^2C$  bus mode.

Set the SBIM to "10" in order to set  $I^2C$  bus mode. Before setting of  $I^2C$  bus mode, confirm serial bus interface pins in a high level, and then, write "10" to SBIM. And switch a port mode after confirming that a bus is free.

#### 16.5.10Arbitration lost detection monitor

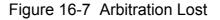

Since more than one master device can exist simultaneously on a bus, a bus arbitration procedure is implemented in order to guarantee the contents of transferred data.

Data on the SDA line is used for bus arbitration of the  $1^2$ C bus.

The following shows an example of a bus arbitration procedure when two master devices exist simultaneously on a bus. Master 1 and Master 2 output the same data until point "a". After that, when Master 1 outputs "1" and Master 2 outputs "0", since the SDA line of a bus is wired AND, the SDA line is pulled-down to the low level by Master 2. When the SCL time of a bus is pulled-up at point "b", the slave device reads data on the SDA line, that is data in Master 2. Data transmitted from Master 1 becomes invalid. The state in Master 1 is called "arbitration lost". A master device which loses arbitration releases the SDA pin and the SCL pin in order not to effect data transmitted from other masters with arbitration. When more than one master sends the same data at the first word, arbitration occurs continuously after the second word.

The serial bus interface circuit compares levels of a SDA line of a bus with its SDA pin at the rising edge of the SCL line. If the levels are unmatched, arbitration is lost and the AL (Bit3 in SBISRB) is set to "1".

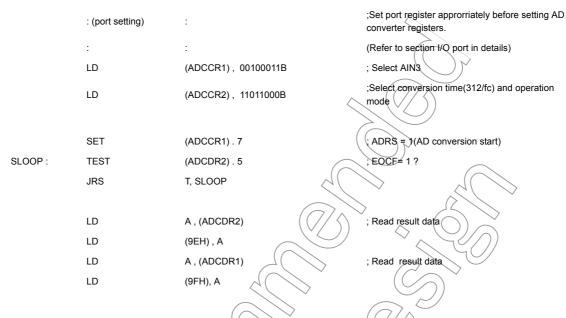

Example :After selecting the conversion time 19.5 µs at 16 MHz and the analog input channel AIN3 pin, perform AD conversion once. After checking EOCF, read the converted value, store the lower 2 bits in address 0009EH nd store the upper 8 bits in address 0009FH in RAM. The operation mode is software start mode.

### 17.4 STOP/SLOW Modes during AD Conversion

When standby mode (STOP or SLOW mode) is entered forcibly during AD conversion, the AD convert operation is suspended and the AD converter is initialized (ADCCR1 and ADCCR2 are initialized to initial value). Also, the conversion result is indeterminate. (Conversion results up to the previous operation are cleared, so be sure to read the conversion results before entering standby mode (STOP or SLOW mode).) When restored from standby mode (STOP or SLOW mode), AD conversion is not automatically restarted, so it is necessary to restart AD conversion. Note that since the analog reference voltage is automatically disconnected, there is no possibility of current flowing into the analog reference voltage.

### 20.3 Serial PROM Mode Setting

#### 20.3.1 Serial PROM Mode Control Pins

To execute on-board programming, activate the serial PROM mode. Table 20-2 shows pin setting to activate the serial PROM mode.

| Table 20-2 Serial PROM Mode Setting |         |                  |  |  |  |  |  |

|-------------------------------------|---------|------------------|--|--|--|--|--|

| Pin                                 | Setting | $\overline{(7)}$ |  |  |  |  |  |

| TEST pin                            | High    | $\sim$           |  |  |  |  |  |

| BOOT/RXD1 pin                       | High    |                  |  |  |  |  |  |

| RESET pin                           |         | $\mathcal{Y}$    |  |  |  |  |  |

Note: The BOOT pin is shared with the UART communication pin (RXD1 pin) in the serial PROM mode. This pin is used as UART communication pin after activating serial PROM mode

#### 20.3.2 Pin Function

In the serial PROM mode, TXD1 (P02) and RXD1 (P01) are used as a serial interface pin.

| Pin Name<br>(Serial PROM Mode) | Input/<br>Output | Function                                                             | Pin Name<br>(MCU Mode) |                                       |  |  |

|--------------------------------|------------------|----------------------------------------------------------------------|------------------------|---------------------------------------|--|--|

| TXD1                           | Output           | Serial data output                                                   |                        | P02                                   |  |  |

| BOOT/RXD1                      | Input/Input      | Serial PROM mode control/Serial data input                           | (Note 1)               | P01                                   |  |  |

| RESET                          | Input            | Serial PROM mode control                                             |                        | RESET                                 |  |  |

| TEST                           | Input            | Fixed to high                                                        |                        | TEST                                  |  |  |

| VDD, AVDD                      | Power<br>suppty  | 4.5 to 5.5 V                                                         |                        |                                       |  |  |

| VSS                            | Power<br>supply  | 0 V                                                                  |                        |                                       |  |  |

| VAREF                          | Power<br>supply  | Leave open or apply input reference voltage.                         |                        |                                       |  |  |

| I/O ports except<br>P02, P01   | 1/0              | These ports are in the high-impedance state in the serial PROM mode. |                        |                                       |  |  |

|                                | Input            | Self-oscillate with an oscillator. (Note 2)                          |                        |                                       |  |  |

| XOUT                           | Output           |                                                                      |                        | , , , , , , , , , , , , , , , , , , , |  |  |

Note 1: During on-board programming with other parts mounted on a user board, be careful no to affect these communication control pins.

Note 2: Operating range of high frequency in serial PROM mode is 2 MHz to 16 MHz.

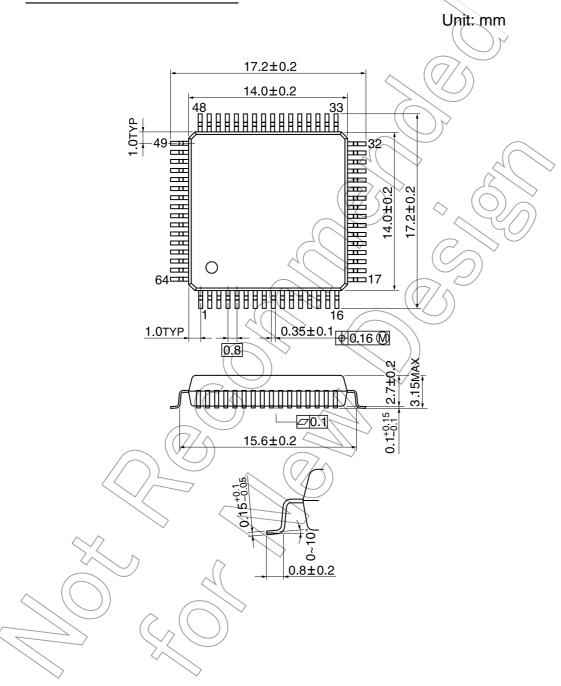

### 23. Package Dimensions

QFP64-P-1414-0.80A Rev 01