# E. Lattice Semiconductor Corporation - <u>LCMX01200E-3FT256I Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Obsolete                                                                      |

|--------------------------------|-------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 150                                                                           |

| Number of Logic Elements/Cells | 1200                                                                          |

| Total RAM Bits                 | 9421                                                                          |

| Number of I/O                  | 211                                                                           |

| Number of Gates                | -                                                                             |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                 |

| Mounting Type                  | Surface Mount                                                                 |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                            |

| Package / Case                 | 256-LBGA                                                                      |

| Supplier Device Package        | 256-FTBGA (17x17)                                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lcmxo1200e-3ft256i |

|                                |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# MachXO Family Data Sheet Architecture

June 2013

Data Sheet DS1002

### **Architecture Overview**

The MachXO family architecture contains an array of logic blocks surrounded by Programmable I/O (PIO). Some devices in this family have sysCLOCK PLLs and blocks of sysMEM<sup>™</sup> Embedded Block RAM (EBRs). Figures 2-1, 2-2, and 2-3 show the block diagrams of the various family members.

The logic blocks are arranged in a two-dimensional grid with rows and columns. The EBR blocks are arranged in a column to the left of the logic array. The PIO cells are located at the periphery of the device, arranged into Banks. The PIOs utilize a flexible I/O buffer referred to as a sysIO interface that supports operation with a variety of interface standards. The blocks are connected with many vertical and horizontal routing channel resources. The place and route software tool automatically allocates these routing resources.

There are two kinds of logic blocks, the Programmable Functional Unit (PFU) and the Programmable Functional unit without RAM (PFF). The PFU contains the building blocks for logic, arithmetic, RAM, ROM, and register functions. The PFF block contains building blocks for logic, arithmetic, ROM, and register functions. Both the PFU and PFF blocks are optimized for flexibility, allowing complex designs to be implemented quickly and effectively. Logic blocks are arranged in a two-dimensional array. Only one type of block is used per row.

In the MachXO family, the number of sysIO Banks varies by device. There are different types of I/O Buffers on different Banks. See the details in later sections of this document. The sysMEM EBRs are large, dedicated fast memory blocks; these blocks are found only in the larger devices. These blocks can be configured as RAM, ROM or FIFO. FIFO support includes dedicated FIFO pointer and flag "hard" control logic to minimize LUT use.

The MachXO registers in PFU and sysl/O can be configured to be SET or RESET. After power up and device is configured, the device enters into user mode with these registers SET/RESET according to the configuration setting, allowing device entering to a known state for predictable system function.

The MachXO architecture provides up to two sysCLOCK<sup>™</sup> Phase Locked Loop (PLL) blocks on larger devices. These blocks are located at either end of the memory blocks. The PLLs have multiply, divide, and phase shifting capabilities that are used to manage the frequency and phase relationships of the clocks.

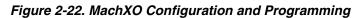

Every device in the family has a JTAG Port that supports programming and configuration of the device as well as access to the user logic. The MachXO devices are available for operation from 3.3V, 2.5V, 1.8V, and 1.2V power supplies, providing easy integration into the overall system.

<sup>© 2013</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

The ispLEVER design tool takes the output of the synthesis tool and places and routes the design. Generally, the place and route tool is completely automatic, although an interactive routing editor is available to optimize the design.

## **Clock/Control Distribution Network**

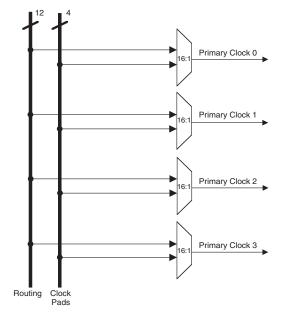

The MachXO family of devices provides global signals that are available to all PFUs. These signals consist of four primary clocks and four secondary clocks. Primary clock signals are generated from four 16:1 muxes as shown in Figure 2-7 and Figure 2-8. The available clock sources for the MachXO256 and MachXO640 devices are four dual function clock pins and 12 internal routing signals. The available clock sources for the MachXO2280 devices are four dual function clock pins, up to nine internal routing signals and up to six PLL outputs.

#### Figure 2-7. Primary Clocks for MachXO256 and MachXO640 Devices

### sysCLOCK Phase Locked Loops (PLLs)

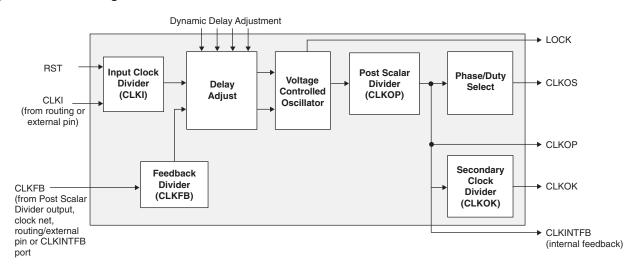

The MachXO1200 and MachXO2280 provide PLL support. The source of the PLL input divider can come from an external pin or from internal routing. There are four sources of feedback signals to the feedback divider: from CLKINTFB (internal feedback port), from the global clock nets, from the output of the post scalar divider, and from the routing (or from an external pin). There is a PLL\_LOCK signal to indicate that the PLL has locked on to the input clock signal. Figure 2-10 shows the sysCLOCK PLL diagram.

The setup and hold times of the device can be improved by programming a delay in the feedback or input path of the PLL which will advance or delay the output clock with reference to the input clock. This delay can be either programmed during configuration or can be adjusted dynamically. In dynamic mode, the PLL may lose lock after adjustment and not relock until the t<sub>LOCK</sub> parameter has been satisfied. Additionally, the phase and duty cycle block allows the user to adjust the phase and duty cycle of the CLKOS output.

The sysCLOCK PLLs provide the ability to synthesize clock frequencies. Each PLL has four dividers associated with it: input clock divider, feedback divider, post scalar divider, and secondary clock divider. The input clock divider is used to divide the input clock signal, while the feedback divider is used to multiply the input clock signal. The post scalar divider allows the VCO to operate at higher frequencies than the clock output, thereby increasing the frequency range. The secondary divider is used to derive lower frequency outputs.

#### Figure 2-10. PLL Diagram

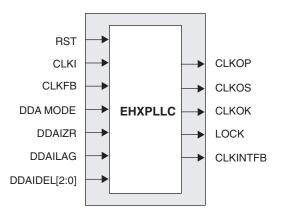

Figure 2-11 shows the available macros for the PLL. Table 2-5 provides signal description of the PLL Block.

#### Figure 2-11. PLL Primitive

#### Table 2-5. PLL Signal Descriptions

| Signal       | I/O | Description                                                                                                 |

|--------------|-----|-------------------------------------------------------------------------------------------------------------|

| CLKI         | I   | Clock input from external pin or routing                                                                    |

| CLKFB        | I   | PLL feedback input from PLL output, clock net, routing/external pin or internal feedback from CLKINTFB port |

| RST          | I   | "1" to reset the input clock divider                                                                        |

| CLKOS        | 0   | PLL output clock to clock tree (phase shifted/duty cycle changed)                                           |

| CLKOP        | 0   | PLL output clock to clock tree (No phase shift)                                                             |

| CLKOK        | 0   | PLL output to clock tree through secondary clock divider                                                    |

| LOCK         | 0   | "1" indicates PLL LOCK to CLKI                                                                              |

| CLKINTFB     | 0   | Internal feedback source, CLKOP divider output before CLOCKTREE                                             |

| DDAMODE      | I   | Dynamic Delay Enable. "1": Pin control (dynamic), "0": Fuse Control (static)                                |

| DDAIZR       | I   | Dynamic Delay Zero. "1": delay = 0, "0": delay = on                                                         |

| DDAILAG      | I   | Dynamic Delay Lag/Lead. "1": Lag, "0": Lead                                                                 |

| DDAIDEL[2:0] | I   | Dynamic Delay Input                                                                                         |

For more information on the PLL, please see details of additional technical documentation at the end of this data sheet.

### sysMEM Memory

The MachXO1200 and MachXO2280 devices contain sysMEM Embedded Block RAMs (EBRs). The EBR consists of a 9-Kbit RAM, with dedicated input and output registers.

#### sysMEM Memory Block

The sysMEM block can implement single port, dual port, pseudo dual port, or FIFO memories. Each block can be used in a variety of depths and widths as shown in Table 2-6.

#### Table 2-6. sysMEM Block Configurations

| Memory Mode      | Configurations                                                           |  |  |  |  |

|------------------|--------------------------------------------------------------------------|--|--|--|--|

| Single Port      | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18<br>256 x 36 |  |  |  |  |

| True Dual Port   | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18             |  |  |  |  |

| Pseudo Dual Port | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18<br>256 x 36 |  |  |  |  |

| FIFO             | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18<br>256 x 36 |  |  |  |  |

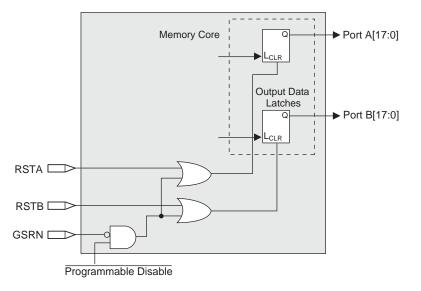

#### Figure 2-13. Memory Core Reset

For further information on the sysMEM EBR block, see the details of additional technical documentation at the end of this data sheet.

#### EBR Asynchronous Reset

EBR asynchronous reset or GSR (if used) can only be applied if all clock enables are low for a clock cycle before the reset is applied and released a clock cycle after the reset is released, as shown in Figure 2-14. The GSR input to the EBR is always asynchronous.

#### Figure 2-14. EBR Asynchronous Reset (Including GSR) Timing Diagram

| Reset           |  |

|-----------------|--|

| Clock           |  |

| Clock<br>Enable |  |

If all clock enables remain enabled, the EBR asynchronous reset or GSR may only be applied and released after the EBR read and write clock inputs are in a steady state condition for a minimum of 1/f<sub>MAX</sub> (EBR clock). The reset release must adhere to the EBR synchronous reset setup time before the next active read or write clock edge.

If an EBR is pre-loaded during configuration, the GSR input must be disabled or the release of the GSR during device Wake Up must occur before the release of the device I/Os becoming active.

These instructions apply to all EBR RAM, ROM and FIFO implementations. For the EBR FIFO mode, the GSR signal is always enabled and the WE and RE signals act like the clock enable signals in Figure 2-14. The reset timing rules apply to the RPReset input vs the RE input and the RST input vs. the WE and RE inputs. Both RST and RPReset are always asynchronous EBR inputs.

Note that there are no reset restrictions if the EBR synchronous reset is used and the EBR GSR input is disabled

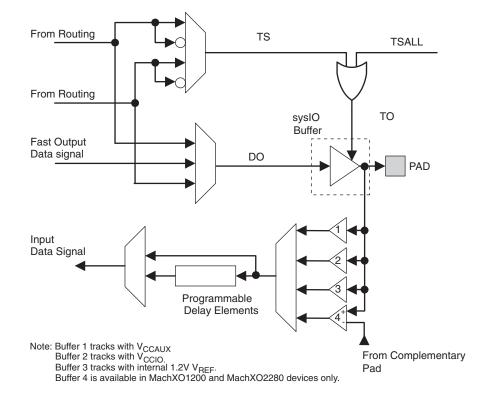

output data signals are multiplexed and provide a single signal to the I/O pin via the sysIO buffer. Figure 2-17 shows the MachXO PIO logic.

The tristate control signal is multiplexed from the output data signals and their complements. In addition a global signal (TSALL) from a dedicated pad can be used to tristate the sysIO buffer.

The PIO receives an input signal from the pin via the sysIO buffer and provides this signal to the core of the device. In addition there are programmable elements that can be utilized by the design tools to avoid positive hold times.

#### Figure 2-17. MachXO PIO Block Diagram

### sysIO Buffer

Each I/O is associated with a flexible buffer referred to as a sysIO buffer. These buffers are arranged around the periphery of the device in groups referred to as Banks. The sysIO buffers allow users to implement the wide variety of standards that are found in today's systems including LVCMOS, TTL, BLVDS, LVDS and LVPECL.

In the MachXO devices, single-ended output buffers and ratioed input buffers (LVTTL, LVCMOS and PCI) are powered using  $V_{CCIO}$ . In addition to the Bank  $V_{CCIO}$  supplies, the MachXO devices have a  $V_{CC}$  core logic power supply, and a  $V_{CCAUX}$  supply that powers up a variety of internal circuits including all the differential and referenced input buffers.

MachXO256 and MachXO640 devices contain single-ended input buffers and single-ended output buffers with complementary outputs on all the I/O Banks.

MachXO1200 and MachXO2280 devices contain two types of sysIO buffer pairs.

#### 1. Top and Bottom sysIO Buffer Pairs

The sysIO buffer pairs in the top and bottom Banks of the device consist of two single-ended output drivers and two sets of single-ended input buffers (for ratioed or absolute input levels). The I/O pairs on the top and bottom

#### Table 2-10. Supported Output Standards

| Output Standard          | Drive                | V <sub>CCIO</sub> (Typ.) |

|--------------------------|----------------------|--------------------------|

| Single-ended Interfaces  |                      |                          |

| LVTTL                    | 4mA, 8mA, 12mA, 16mA | 3.3                      |

| LVCMOS33                 | 4mA, 8mA, 12mA, 14mA | 3.3                      |

| LVCMOS25                 | 4mA, 8mA, 12mA, 14mA | 2.5                      |

| LVCMOS18                 | 4mA, 8mA, 12mA, 14mA | 1.8                      |

| LVCMOS15                 | 4mA, 8mA             | 1.5                      |

| LVCMOS12                 | 2mA, 6mA             | 1.2                      |

| LVCMOS33, Open Drain     | 4mA, 8mA, 12mA, 14mA | <b>—</b>                 |

| LVCMOS25, Open Drain     | 4mA, 8mA, 12mA, 14mA | —                        |

| LVCMOS18, Open Drain     | 4mA, 8mA, 12mA, 14mA | —                        |

| LVCMOS15, Open Drain     | 4mA, 8mA             | <b>—</b>                 |

| LVCMOS12, Open Drain     | 2mA, 6mA             | <b>—</b>                 |

| PCI33 <sup>3</sup>       | N/A                  | 3.3                      |

| Differential Interfaces  |                      |                          |

| LVDS <sup>1, 2</sup>     | N/A                  | 2.5                      |

| BLVDS, RSDS <sup>2</sup> | N/A                  | 2.5                      |

| LVPECL <sup>2</sup>      | N/A                  | 3.3                      |

1. MachXO1200 and MachXO2280 devices have dedicated LVDS buffers.

2. These interfaces can be emulated with external resistors in all devices.

3. Top Banks of MachXO1200 and MachXO2280 devices only.

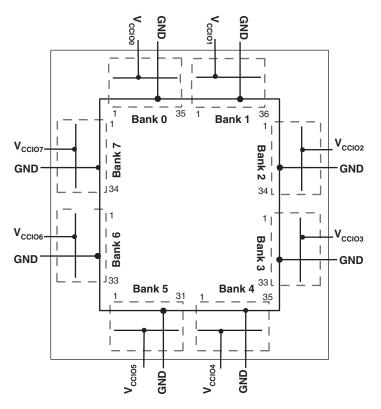

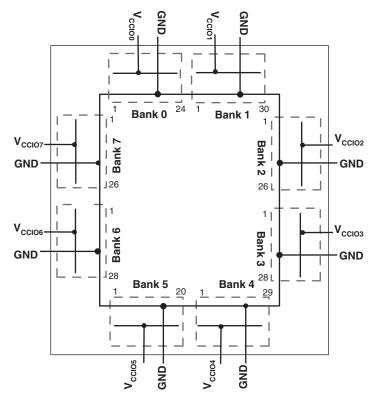

#### sysIO Buffer Banks

The number of Banks vary between the devices of this family. Eight Banks surround the two larger devices, the MachXO1200 and MachXO2280 (two Banks per side). The MachXO640 has four Banks (one Bank per side). The smallest member of this family, the MachXO256, has only two Banks.

Each sysIO buffer Bank is capable of supporting multiple I/O standards. Each Bank has its own I/O supply voltage ( $V_{CCIO}$ ) which allows it to be completely independent from the other Banks. Figure 2-18, Figure 2-18, Figure 2-20 and Figure 2-21 shows the sysIO Banks and their associated supplies for all devices.

#### Figure 2-18. MachXO2280 Banks

Figure 2-19. MachXO1200 Banks

# **Density Shifting**

The MachXO family has been designed to enable density migration in the same package. Furthermore, the architecture ensures a high success rate when performing design migration from lower density parts to higher density parts. In many cases, it is also possible to shift a lower utilization design targeted for a high-density device to a lower density device. However, the exact details of the final resource utilization will impact the likely success in each case.

# MachXO256 and MachXO640 Hot Socketing Specifications<sup>1, 2, 3</sup>

| Symbol          | Parameter                    | Parameter Condition             |   | Тур. | Max     | Units |

|-----------------|------------------------------|---------------------------------|---|------|---------|-------|

| I <sub>DK</sub> | Input or I/O leakage Current | $0 \le V_{IN} \le V_{IH}$ (MAX) | — | _    | +/-1000 | μΑ    |

1. Insensitive to sequence of V<sub>CC</sub>, V<sub>CCAUX</sub>, and V<sub>CCIO</sub>. However, assumes monotonic rise/fall rates for V<sub>CC</sub>, V<sub>CCAUX</sub>, and V<sub>CCIO</sub>.

2.  $0 \le V_{CC} \le V_{CC}$  (MAX),  $0 \le V_{CCIO} \le V_{CCIO}$  (MAX) and  $0 \le V_{CCAUX} \le V_{CCAUX}$  (MAX).

3. I<sub>DK</sub> is additive to I<sub>PU</sub>, I<sub>PD</sub> or I<sub>BH</sub>.

# MachXO1200 and MachXO2280 Hot Socketing Specifications<sup>1, 2, 3</sup>

| Symbol          | Parameter                    | Condition                           | Min. | Тур. | Max.    | Units |  |  |

|-----------------|------------------------------|-------------------------------------|------|------|---------|-------|--|--|

| Non-LVDS (      | General Purpose syslOs       |                                     | ·    |      |         |       |  |  |

| I <sub>DK</sub> | Input or I/O Leakage Current | $0 \le V_{IN} \le V_{IH}$ (MAX.)    | —    | —    | +/-1000 | μA    |  |  |

| LVDS Gene       | LVDS General Purpose syslOs  |                                     |      |      |         |       |  |  |

| 1 .             | Input or I/O Leakage Current | $V_{IN} \leq V_{CCIO}$              | —    |      | +/-1000 | μA    |  |  |

| IDK_LVDS        | Input of 1/O Leakage Current | V <sub>IN</sub> > V <sub>CCIO</sub> | _    | 35   |         | mA    |  |  |

1. Insensitive to sequence of V<sub>CC</sub>, V<sub>CCAUX</sub>, and V<sub>CCIO</sub>. However, assumes monotonic rise/fall rates for V<sub>CC</sub>, V<sub>CCAUX</sub>, and V<sub>CCIO</sub>.

2.  $0 \le V_{CC} \le V_{CC}$  (MAX),  $0 \le V_{CCIO} \le V_{CCIO}$  (MAX), and  $0 \le V_{CCAUX} \le V_{CCAUX}$  (MAX).

3. I<sub>DK</sub> is additive to I<sub>PU</sub>, I<sub>PW</sub> or I<sub>BH</sub>.

# **DC Electrical Characteristics**

#### **Over Recommended Operating Conditions**

| Symbol                                              | Parameter                                | Condition                                                                                     | Min.           | Тур. | Max.                  | Units |

|-----------------------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------|----------------|------|-----------------------|-------|

| I <sub>IL,</sub> I <sub>IH</sub> <sup>1, 4, 5</sup> | Input or I/O Leakage                     | $0 \le V_{IN} \le (V_{CCIO} - 0.2V)$                                                          | —              | _    | 10                    | μA    |

| 'IL, 'IH                                            | Input of I/O Leakage                     | $(V_{CCIO} - 0.2V) < V_{IN} \le 3.6V$                                                         | —              | _    | 40                    | μA    |

| I <sub>PU</sub>                                     | I/O Active Pull-up Current               | $0 \le V_{IN} \le 0.7 \ V_{CCIO}$                                                             | -30            | _    | -150                  | μΑ    |

| I <sub>PD</sub>                                     | I/O Active Pull-down Current             | $V_{IL} (MAX) \le V_{IN} \le V_{IH} (MAX)$                                                    | 30             |      | 150                   | μΑ    |

| I <sub>BHLS</sub>                                   | Bus Hold Low sustaining current          | $V_{IN} = V_{IL}$ (MAX)                                                                       | 30             | _    | —                     | μΑ    |

| I <sub>BHHS</sub>                                   | Bus Hold High sustaining current         | $V_{IN} = 0.7 V_{CCIO}$                                                                       | -30            |      | —                     | μΑ    |

| I <sub>BHLO</sub>                                   | Bus Hold Low Overdrive current           | $0 \le V_{IN} \le V_{IH}$ (MAX)                                                               | —              | _    | 150                   | μΑ    |

| I <sub>BHHO</sub>                                   | Bus Hold High Overdrive current          | $0 \le V_{IN} \le V_{IH}$ (MAX)                                                               | —              | _    | -150                  | μΑ    |

| V <sub>BHT</sub> <sup>3</sup>                       | Bus Hold trip Points                     | $0 \le V_{IN} \le V_{IH}$ (MAX)                                                               | $V_{IL}$ (MAX) |      | V <sub>IH</sub> (MIN) | V     |

| C1                                                  | I/O Capacitance <sup>2</sup>             |                                                                                               | _              | 8    |                       | pf    |

| C2                                                  | Dedicated Input Capacitance <sup>2</sup> | $V_{CCIO} = 3.3V, 2.5V, 1.8V, 1.5V, 1.2V, V_{CC} = Typ., V_{IO} = 0 \text{ to } V_{IH} (MAX)$ | _              | 8    | _                     | pf    |

1. Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tri-stated. It is not measured with the output driver active. Bus maintenance circuits are disabled.

2. T<sub>A</sub> 25°C, f = 1.0MHz

3. Please refer to  $V_{IL}$  and  $V_{IH}$  in the sysIO Single-Ended DC Electrical Characteristics table of this document.

4. Not applicable to SLEEPN pin.

When V<sub>IH</sub> is higher than V<sub>CCIO</sub>, a transient current typically of 30ns in duration or less with a peak current of 6mA can occur on the high-tolow transition. For MachXO1200 and MachXO2280 true LVDS output pins, V<sub>IH</sub> must be less than or equal to V<sub>CCIO</sub>.

# Initialization Supply Current<sup>1, 2, 3, 4</sup>

#### **Over Recommended Operating Conditions**

| Symbol             | Parameter                      | Device       | Typ.⁵ | Units |

|--------------------|--------------------------------|--------------|-------|-------|

|                    |                                | LCMXO256C    | 13    | mA    |

|                    |                                | LCMXO640C    | 17    | mA    |

|                    |                                | LCMXO1200C   | 21    | mA    |

|                    | Core Power Supply              | LCMXO2280C   | 23    | mA    |

| ICC                | Core Power Supply              | LCMXO256E    | 10    | mA    |

|                    |                                | LCMXO640E    | 14    | mA    |

|                    |                                | LCMXO1200E   | 18    | mA    |

|                    |                                | LCMXO2280E   | 20    | mA    |

|                    |                                | LCMXO256E/C  | 10    | mA    |

| I <sub>CCAUX</sub> | Auxiliary Power Supply         | LCMXO640E/C  | 13    | mA    |

|                    | $V_{CCAUX} = 3.3V$             | LCMXO1200E/C | 24    | mA    |

|                    |                                | LCMXO2280E/C | 25    | mA    |

| ICCIO              | Bank Power Supply <sup>6</sup> | All devices  | 2     | mA    |

1. For further information on supply current, please see details of additional technical documentation at the end of this data sheet.

2. Assumes all I/O pins are held at  $V_{CCIO}$  or GND.

3. Frequency = 0MHz.

4. Typical user pattern.

5.  $T_J = 25^{\circ}$ C, power supplies at nominal voltage.

6. Per Bank, V<sub>CCIO</sub> = 2.5V. Does not include pull-up/pull-down.

# Programming and Erase Flash Supply Current<sup>1, 2, 3, 4</sup>

| Symbol            | Parameter                      | Device       | Typ.⁵ | Units |

|-------------------|--------------------------------|--------------|-------|-------|

|                   |                                | LCMXO256C    | 9     | mA    |

|                   |                                | LCMXO640C    | 11    | mA    |

|                   |                                | LCMXO1200C   | 16    | mA    |

| 1                 | Core Power Supply              | LCMXO2280C   | 22    | mA    |

| ICC               | Cole Power Supply              | LCMXO256E    | 6     | mA    |

|                   |                                | LCMXO640E    | 8     | mA    |

|                   |                                | LCMXO1200E   | 12    | mA    |

|                   |                                | LCMXO2280E   | 14    | mA    |

|                   |                                | LCMXO256C/E  | 8     | mA    |

| 1                 | Auxiliary Power Supply         | LCMXO640C/E  | 10    | mA    |

| ICCAUX            | $V_{CCAUX} = 3.3V$             | LCMXO1200/E  | 15    | mA    |

|                   |                                | LCMXO2280C/E | 16    | mA    |

| I <sub>CCIO</sub> | Bank Power Supply <sup>6</sup> | All devices  | 2     | mA    |

1. For further information on supply current, please see details of additional technical documentation at the end of this data sheet.

2. Assumes all I/O pins are held at  $V_{CCIO}$  or GND.

3. Typical user pattern.

4. JTAG programming is at 25MHz.

5.  $T_J = 25^{\circ}C$ , power supplies at nominal voltage.

6. Per Bank. V<sub>CCIO</sub> = 2.5V. Does not include pull-up/pull-down.

### sysIO Recommended Operating Conditions

|                      | V <sub>CCIO</sub> (V) |      |       |  |  |

|----------------------|-----------------------|------|-------|--|--|

| Standard             | Min.                  | Тур. | Max.  |  |  |

| LVCMOS 3.3           | 3.135                 | 3.3  | 3.465 |  |  |

| LVCMOS 2.5           | 2.375                 | 2.5  | 2.625 |  |  |

| LVCMOS 1.8           | 1.71                  | 1.8  | 1.89  |  |  |

| LVCMOS 1.5           | 1.425                 | 1.5  | 1.575 |  |  |

| LVCMOS 1.2           | 1.14                  | 1.2  | 1.26  |  |  |

| LVTTL                | 3.135                 | 3.3  | 3.465 |  |  |

| PCl <sup>3</sup>     | 3.135                 | 3.3  | 3.465 |  |  |

| LVDS <sup>1, 2</sup> | 2.375                 | 2.5  | 2.625 |  |  |

| LVPECL <sup>1</sup>  | 3.135                 | 3.3  | 3.465 |  |  |

| BLVDS <sup>1</sup>   | 2.375                 | 2.5  | 2.625 |  |  |

| RSDS <sup>1</sup>    | 2.375                 | 2.5  | 2.625 |  |  |

1. Inputs on chip. Outputs are implemented with the addition of external resistors.

2. MachXO1200 and MachXO2280 devices have dedicated LVDS buffers

3. Input on the top bank of the MachXO1200 and MachXO2280 only.

### sysIO Single-Ended DC Electrical Characteristics

| Input/Output  |            | V <sub>IL</sub>       | V <sub>IH</sub>       | V <sub>IH</sub> |                             | V <sub>OH</sub> Min.    |              | I <sub>OH</sub> <sup>1</sup> |

|---------------|------------|-----------------------|-----------------------|-----------------|-----------------------------|-------------------------|--------------|------------------------------|

| Standard      | Min. (V)   | Max. (V)              | Min. (V)              | Max. (V)        | V <sub>OL</sub> Max.<br>(V) | (V)                     | (mĀ)         | (mÅ)                         |

| LVCMOS 3.3    | -0.3       | 0.8                   | 2.0                   | 3.6             | 0.4                         | V <sub>CCIO</sub> - 0.4 | 16, 12, 8, 4 | -14, -12, -8, -4             |

| 20010000.0    | -0.5       | -0.3 0.0              | 2.0                   | 3.0             | 0.2                         | V <sub>CCIO</sub> - 0.2 | 0.1          | -0.1                         |

|               |            |                       |                       |                 | 0.4                         | 2.4                     | 16           | -16                          |

| LVTTL         | -0.3       | 0.8                   | 2.0                   | 3.6             | 0.4                         | V <sub>CCIO</sub> - 0.4 | 12, 8, 4     | -12, -8, -4                  |

|               |            |                       |                       | 0.2             | 0.2                         | V <sub>CCIO</sub> - 0.2 | 0.1          | -0.1                         |

| LVCMOS 2.5    | -0.3       | 0.7                   | 1.7                   | 3.6             | 0.4                         | V <sub>CCIO</sub> - 0.4 | 16, 12, 8, 4 | -14, -12, -8, -4             |

| 2000002.5     | -0.5       | 0.7                   | 1.7                   | 0.0             | 0.2                         | V <sub>CCIO</sub> - 0.2 | 0.1          | -0.1                         |

| LVCMOS 1.8    | -0.3       | 0.35V <sub>CCIO</sub> | 0.65V <sub>CCIO</sub> | 3.6             | 0.4                         | V <sub>CCIO</sub> - 0.4 | 16, 12, 8, 4 | -14, -12, -8, -4             |

|               | -0.3 0.35V | 0.00 4 CCIO           | 0.03 ¢ CCIO           | 0.0             | 0.2                         | V <sub>CCIO</sub> - 0.2 | 0.1          | -0.1                         |

| LVCMOS 1.5    | -0.3       | 0.35V <sub>CCIO</sub> | 0.65V <sub>CCIO</sub> | 3.6             | 0.4                         | V <sub>CCIO</sub> - 0.4 | 8, 4         | -8, -4                       |

| 2001000 1.5   | -0.5       | 0.00 4 CCIO           | 0.00 4 CCIO           | 0.0             | 0.2                         | V <sub>CCIO</sub> - 0.2 | 0.1          | -0.1                         |

| LVCMOS 1.2    | -0.3       | 0.42                  | 0.78                  | 3.6             | 0.4                         | V <sub>CCIO</sub> - 0.4 | 6, 2         | -6, -2                       |

| ("C" Version) | -0.5       | 0.42                  | 0.70                  | 0.0             | 0.2                         | V <sub>CCIO</sub> - 0.2 | 0.1          | -0.1                         |

| LVCMOS 1.2    | -0.3       | 0.35V <sub>CC</sub>   | 0.65V <sub>CC</sub>   | 3.6             | 0.4                         | V <sub>CCIO</sub> - 0.4 | 6, 2         | -6, -2                       |

| ("E" Version) | -0.5       | 0.00 v CC             | 0.03 v CC             | 5.0             | 0.2                         | V <sub>CCIO</sub> - 0.2 | 0.1          | -0.1                         |

| PCI           | -0.3       | 0.3V <sub>CCIO</sub>  | 0.5V <sub>CCIO</sub>  | 3.6             | 0.1V <sub>CCIO</sub>        | 0.9V <sub>CCIO</sub>    | 1.5          | -0.5                         |

The average DC current drawn by I/Os between GND connections, or between the last GND in an I/O Bank and the end of an I/O Bank, as shown in the logic signal connections table shall not exceed n \* 8mA. Where n is the number of I/Os between Bank GND connections or between the last GND in a Bank and the end of a Bank.

# MachXO Internal Timing Parameters<sup>1</sup>

|                         |                                                              | -     | 5    | -4    |      | -3    |      |       |

|-------------------------|--------------------------------------------------------------|-------|------|-------|------|-------|------|-------|

| Parameter               | Description                                                  | Min.  | Max. | Min.  | Max. | Min.  | Max. | Units |

| PFU/PFF Log             | ic Mode Timing                                               | •     | 1    | 1     |      |       |      |       |

| t <sub>LUT4_PFU</sub>   | LUT4 delay (A to D inputs to F output)                       | —     | 0.28 |       | 0.34 | —     | 0.39 | ns    |

| t <sub>LUT6_PFU</sub>   | LUT6 delay (A to D inputs to OFX output)                     | —     | 0.44 | —     | 0.53 | —     | 0.62 | ns    |

| t <sub>LSR_PFU</sub>    | Set/Reset to output of PFU                                   | —     | 0.90 | —     | 1.08 | —     | 1.26 | ns    |

| t <sub>SUM_PFU</sub>    | Clock to Mux (M0,M1) input setup time                        | 0.10  |      | 0.13  |      | 0.15  |      | ns    |

| t <sub>HM_PFU</sub>     | Clock to Mux (M0,M1) input hold time                         | -0.05 | —    | -0.06 | —    | -0.07 | _    | ns    |

| t <sub>SUD_PFU</sub>    | Clock to D input setup time                                  | 0.13  | —    | 0.16  | —    | 0.18  | _    | ns    |

| t <sub>HD_PFU</sub>     | Clock to D input hold time                                   | -0.03 | —    | -0.03 |      | -0.04 |      | ns    |

| t <sub>CK2Q_PFU</sub>   | Clock to Q delay, D-type register configuration              | —     | 0.40 |       | 0.48 | —     | 0.56 | ns    |

| t <sub>LE2Q_PFU</sub>   | Clock to Q delay latch configuration                         | —     | 0.53 | —     | 0.64 | —     | 0.74 | ns    |

| t <sub>LD2Q_PFU</sub>   | D to Q throughput delay when latch is enabled                | —     | 0.55 |       | 0.66 | —     | 0.77 | ns    |

| PFU Dual Po             | rt Memory Mode Timing                                        | •     |      |       |      | •     |      |       |

| t <sub>CORAM_PFU</sub>  | Clock to Output                                              | —     | 0.40 |       | 0.48 | —     | 0.56 | ns    |

| t <sub>SUDATA_PFU</sub> | Data Setup Time                                              | -0.18 |      | -0.22 | _    | -0.25 | _    | ns    |

| t <sub>HDATA_PFU</sub>  | Data Hold Time                                               | 0.28  |      | 0.34  |      | 0.39  |      | ns    |

| t <sub>SUADDR_PFU</sub> | Address Setup Time                                           | -0.46 |      | -0.56 |      | -0.65 |      | ns    |

| t <sub>HADDR_PFU</sub>  | Address Hold Time                                            | 0.71  | —    | 0.85  | _    | 0.99  | _    | ns    |

| t <sub>SUWREN_PFU</sub> | Write/Read Enable Setup Time                                 | -0.22 | —    | -0.26 | _    | -0.30 | _    | ns    |

| t <sub>HWREN_PFU</sub>  | Write/Read Enable Hold Time                                  | 0.33  | —    | 0.40  | _    | 0.47  | _    | ns    |

| PIO Input/Ou            | tput Buffer Timing                                           |       |      |       |      |       |      |       |

| t <sub>IN_PIO</sub>     | Input Buffer Delay                                           | —     | 0.75 |       | 0.90 | —     | 1.06 | ns    |

| t <sub>OUT_PIO</sub>    | Output Buffer Delay                                          | —     | 1.29 |       | 1.54 | —     | 1.80 | ns    |

| EBR Timing              | 1200 and 2280 Devices Only)                                  |       |      |       |      |       |      |       |

| t <sub>CO_EBR</sub>     | Clock to output from Address or Data with no output register | _     | 2.24 | _     | 2.69 | _     | 3.14 | ns    |

| t <sub>COO_EBR</sub>    | Clock to output from EBR output Register                     | —     | 0.54 |       | 0.64 | —     | 0.75 | ns    |

| t <sub>SUDATA_EBR</sub> | Setup Data to EBR Memory                                     | -0.26 |      | -0.31 |      | -0.37 |      | ns    |

| t <sub>HDATA_EBR</sub>  | Hold Data to EBR Memory                                      | 0.41  | —    | 0.49  | _    | 0.57  | _    | ns    |

| t <sub>SUADDR_EBR</sub> | Setup Address to EBR Memory                                  | -0.26 | —    | -0.31 | _    | -0.37 | _    | ns    |

| t <sub>HADDR_EBR</sub>  | Hold Address to EBR Memory                                   | 0.41  | —    | 0.49  | _    | 0.57  |      | ns    |

| t <sub>SUWREN_EBR</sub> | Setup Write/Read Enable to EBR Memory                        | -0.17 | —    | -0.20 | _    | -0.23 | _    | ns    |

| t <sub>HWREN_EBR</sub>  | Hold Write/Read Enable to EBR Memory                         | 0.26  | —    | 0.31  | _    | 0.36  | _    | ns    |

| t <sub>SUCE_EBR</sub>   | Clock Enable Setup Time to EBR Output Register               | 0.19  | —    | 0.23  | _    | 0.27  | _    | ns    |

| t <sub>HCE_EBR</sub>    | Clock Enable Hold Time to EBR Output Register                | -0.13 |      | -0.16 | —    | -0.18 |      | ns    |

| t <sub>RSTO_EBR</sub>   | Reset To Output Delay Time from EBR Output Regis-<br>ter     | —     | 1.03 | _     | 1.23 | _     | 1.44 | ns    |

| PLL Paramet             | ers (1200 and 2280 Devices Only)                             |       |      |       |      |       |      |       |

| t <sub>RSTREC</sub>     | Reset Recovery to Rising Clock                               | 1.00  | —    | 1.00  |      | 1.00  | _    | ns    |

| t <sub>RSTSU</sub>      | Reset Signal Setup Time                                      | 1.00  | —    | 1.00  |      | 1.00  |      | ns    |

| 1 Internal para         | meters are characterized but not tested on every device      |       |      | •     |      |       |      |       |

1. Internal parameters are characterized but not tested on every device.

Rev. A 0.19

# **Power Supply and NC**

| Signal           | 100 TQFP <sup>1</sup>                                                                                                                                   | 144 TQFP <sup>1</sup>                                | 100 csBGA <sup>2</sup>                                                                                    |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| VCC              | LCMXO256/640: 35, 90<br>LCMXO1200/2280: 17, 35, 66, 91                                                                                                  | 21, 52, 93, 129                                      | P7, B6                                                                                                    |

| VCCIO0           | LCMXO256: 60, 74, 92<br>LCMXO640: 80, 92<br>LCMXO1200/2280: 94                                                                                          | LCMXO640: 117, 135<br>LCMXO1200/2280: 135            | LCMXO256: H14, A14, B5<br>LCMXO640: B12, B5                                                               |

| VCCIO1           | LCMXO256: 10, 24, 41<br>LCMXO640: 60, 74<br>LCMXO1200/2280: 80                                                                                          | LCMXO640: 82, 98<br>LCMXO1200/2280: 117              | LCMXO256: G1, P1, P10<br>LCMXO640: H14, A14                                                               |

| VCCIO2           | LCMXO256: None<br>LCMXO640: 29, 41<br>LCMXO1200/2280: 70                                                                                                | LCMXO640: 38, 63<br>LCMXO1200/2280: 98               | LCMXO256: None<br>LCMXO640: P4, P10                                                                       |

| VCCIO3           | LCMXO256: None<br>LCMXO640: 10, 24<br>LCMXO1200/2280: 56                                                                                                | LCMXO640: 10, 26<br>LCMXO1200/2280: 82               | LCMXO256: None<br>LCMXO640: G1, P1                                                                        |

| VCCIO4           | LCMXO256/640: None<br>LCMXO1200/2280: 44                                                                                                                | LCMXO640: None<br>LCMXO1200/2280: 63                 | -                                                                                                         |

| VCCIO5           | LCMXO256/640: None<br>LCMXO1200/2280: 27                                                                                                                | LCMXO640: None<br>LCMXO1200/2280: 38                 | —                                                                                                         |

| VCCIO6           | LCMXO256/640: None<br>LCMXO1200/2280: 20                                                                                                                | LCMXO640: None<br>LCMXO1200/2280: 26                 | —                                                                                                         |

| VCCIO7           | LCMXO256/640: None<br>LCMXO1200/2280: 6                                                                                                                 | LCMXO640: None<br>LCMXO1200/2280: 10                 | —                                                                                                         |

| VCCAUX           | LCMXO256/640: 88<br>LCMXO1200/2280: 36, 90                                                                                                              | 53, 128                                              | B7                                                                                                        |

| GND <sup>3</sup> | LCMXO256: 40, 84, 62, 75, 93, 12,<br>25, 42<br>LCMXO640: 40, 84, 81, 93, 62, 75,<br>30, 42, 12, 25<br>LCMXO1200/2280: 9, 41, 59, 83,<br>100, 76, 50, 26 | 16, 59, 88, 123, 118, 136, 83, 99,<br>37, 64, 11, 27 | LCMXO256: N9, B9, G14, B13,<br>A4, H1, N2, N10<br>LCMXO640: N9, B9, A10, A4,<br>G14, B13, N3, N10, H1, N2 |

| NC <sup>4</sup>  |                                                                                                                                                         |                                                      | —                                                                                                         |

1. Pin orientation follows the conventional order from pin 1 marking of the top side view and counter-clockwise.

Pin orientation follows the contention of the top side view with alphabetical order ascending vertically and numerical order ascending horizontally.

All grounds must be electrically connected at the board level. For fpBGA and ftBGA packages, the total number of GND balls is less than the actual number of GND logic connections from the die to the common package GND plane.

NC pins should not be connected to any active signals, VCC or GND.

# LCMXO256 and LCMXO640 Logic Signal Connections: 100 csBGA (Cont.)

|                |                  | LCMXO256 |                  |                   | LCMXO640       |                  |      |                  |                   |  |

|----------------|------------------|----------|------------------|-------------------|----------------|------------------|------|------------------|-------------------|--|

| Ball<br>Number | Ball<br>Function | Bank     | Dual<br>Function | Differen-<br>tial | Ball<br>Number | Ball<br>Function | Bank | Dual<br>Function | Differen-<br>tial |  |

| A4             | GNDIO0           | 0        |                  |                   | A4             | GNDIO0           | 0    |                  |                   |  |

| B4             | PT3A             | 0        |                  | Т                 | B4             | PT3B             | 0    |                  | С                 |  |

| A3             | PT2F             | 0        |                  | С                 | A3             | PT3A             | 0    |                  | Т                 |  |

| B3             | PT2E             | 0        |                  | Т                 | B3             | PT2F             | 0    |                  | С                 |  |

| A2             | PT2D             | 0        |                  | С                 | A2             | PT2E             | 0    |                  | Т                 |  |

| C3             | PT2C             | 0        |                  | Т                 | C3             | PT2B             | 0    |                  | С                 |  |

| A1             | PT2B             | 0        |                  | С                 | A1             | PT2C             | 0    |                  |                   |  |

| B2             | PT2A             | 0        |                  | Т                 | B2             | PT2A             | 0    |                  | Т                 |  |

| N9             | GND              | -        |                  |                   | N9             | GND              | -    |                  |                   |  |

| B9             | GND              | -        |                  |                   | B9             | GND              | -    |                  |                   |  |

| B5             | VCCIO0           | 0        |                  |                   | B5             | VCCIO0           | 0    |                  |                   |  |

| A14            | VCCIO0           | 0        |                  |                   | A14            | VCCIO1           | 1    |                  |                   |  |

| H14            | VCCIO0           | 0        |                  |                   | H14            | VCCIO1           | 1    |                  |                   |  |

| P10            | VCCIO1           | 1        |                  |                   | P10            | VCCIO2           | 2    |                  |                   |  |

| G1             | VCCIO1           | 1        |                  |                   | G1             | VCCIO3           | 3    |                  |                   |  |

| P1             | VCCIO1           | 1        |                  |                   | P1             | VCCIO3           | 3    |                  |                   |  |

\*NC for "E" devices.

\*\*Primary clock inputs are single-ended.

# LCMXO640, LCMXO1200 and LCMXO2280 Logic Signal Connections: 132 csBGA (Cont.)

|        |                  | LCM) | (O640            |              |        |                  | LC   | MXO1200          |              |        |                  | LC   | MXO2280          |              |

|--------|------------------|------|------------------|--------------|--------|------------------|------|------------------|--------------|--------|------------------|------|------------------|--------------|

| Ball # | Ball<br>Function | Bank | Dual<br>Function | Differential | Ball # | Ball<br>Function | Bank | Dual<br>Function | Differential | Ball # | Ball<br>Function | Bank | Dual<br>Function | Differential |

| B9     | PT7B             | 0    |                  | С            | B9     | PT9B             | 1    |                  | С            | B9     | PT12D            | 1    |                  | С            |

| A9     | PT7A             | 0    |                  | Т            | A9     | PT9A             | 1    |                  | Т            | A9     | PT12C            | 1    |                  | Т            |

| A8     | PT6B             | 0    | PCLK0_1***       | С            | A8     | PT7D             | 1    | PCLK1_1***       |              | A8     | PT10B            | 1    | PCLK1_1***       |              |

| B8     | PT6A             | 0    |                  | Т            | B8     | PT7B             | 1    |                  |              | B8     | PT9D             | 1    |                  |              |

| C8     | PT5B             | 0    | PCLK0_0***       | С            | C8     | PT6F             | 0    | PCLK1_0***       |              | C8     | PT9B             | 1    | PCLK1_0***       |              |

| B7     | PT5A             | 0    |                  | Т            | B7     | PT6D             | 0    |                  |              | B7     | PT8D             | 0    |                  |              |

| A7     | VCCAUX           | -    |                  |              | A7     | VCCAUX           | -    |                  |              | A7     | VCCAUX           | -    |                  |              |

| C7     | VCC              | -    |                  |              | C7     | VCC              | -    |                  |              | C7     | VCC              | -    |                  |              |

| A6     | PT4D             | 0    |                  | С            | A6     | PT5D             | 0    |                  | С            | A6     | PT7B             | 0    |                  | С            |

| B6     | PT4C             | 0    |                  | Т            | B6     | PT5C             | 0    |                  | Т            | B6     | PT7A             | 0    |                  | Т            |

| C6     | PT3F             | 0    |                  | С            | C6     | PT5B             | 0    |                  | С            | C6     | PT6D             | 0    |                  |              |

| B5     | PT3E             | 0    |                  | Т            | B5     | PT5A             | 0    |                  | Т            | B5     | PT6E             | 0    |                  | Т            |

| A5     | PT3D             | 0    |                  |              | A5     | PT4B             | 0    |                  |              | A5     | PT6F             | 0    |                  | С            |

| B4     | GNDIO0           | 0    |                  |              | B4     | GNDIO0           | 0    |                  |              | B4     | GNDIO0           | 0    |                  |              |

| A4     | PT3B             | 0    |                  |              | A4     | PT3D             | 0    |                  | С            | A4     | PT4B             | 0    |                  | С            |

| C4     | PT2F             | 0    |                  |              | C4     | PT3C             | 0    |                  | Т            | C4     | PT4A             | 0    |                  | Т            |

| A3     | PT2D             | 0    |                  | С            | A3     | PT3B             | 0    |                  | С            | A3     | PT3B             | 0    |                  | С            |

| A2     | PT2C             | 0    |                  | Т            | A2     | PT2B             | 0    |                  | С            | A2     | PT2B             | 0    |                  | С            |

| B3     | PT2B             | 0    |                  | С            | B3     | PT3A             | 0    |                  | Т            | B3     | PT3A             | 0    |                  | Т            |

| A1     | PT2A             | 0    |                  | Т            | A1     | PT2A             | 0    |                  | Т            | A1     | PT2A             | 0    |                  | Т            |

| F1     | GND              | -    |                  |              | F1     | GND              | -    |                  |              | F1     | GND              | -    |                  |              |

| P9     | GND              | -    |                  |              | P9     | GND              | -    |                  |              | P9     | GND              | -    |                  |              |

| J14    | GND              | -    |                  |              | J14    | GND              | -    |                  |              | J14    | GND              | -    |                  |              |

| C9     | GND              | -    |                  |              | C9     | GND              | -    |                  |              | C9     | GND              | -    |                  |              |

| C5     | VCCIO0           | 0    |                  |              | C5     | VCCIO0           | 0    |                  |              | C5     | VCCIO0           | 0    |                  |              |

| B11    | VCCIO0           | 0    |                  |              | B11    | VCCIO1           | 1    |                  |              | B11    | VCCIO1           | 1    |                  |              |

| E12    | VCCIO1           | 1    |                  |              | E12    | VCCIO2           | 2    |                  |              | E12    | VCCIO2           | 2    |                  |              |

| L12    | VCCIO1           | 1    |                  |              | L12    | VCCIO3           | 3    |                  |              | L12    | VCCIO3           | 3    |                  |              |

| M10    | VCCIO2           | 2    |                  |              | M10    | VCCIO4           | 4    |                  |              | M10    | VCCIO4           | 4    |                  |              |

| N2     | VCCIO2           | 2    |                  |              | N2     | VCCIO5           | 5    |                  |              | N2     | VCCIO5           | 5    |                  |              |

| D2     | VCCIO3           | 3    |                  |              | D2     | VCCIO7           | 7    |                  |              | D2     | VCCI07           | 7    |                  |              |

| K3     | VCCIO3           | 3    |                  |              | K3     | VCCIO6           | 6    |                  |              | K3     | VCCIO6           | 6    |                  |              |

\*Supports true LVDS outputs. \*\*NC for "E" devices. \*\*\*Primary clock inputs arer single-ended.

# LCMXO2280 Logic Signal Connections: 324 ftBGA (Cont.)

| LCMXO2280   |               |      |               |              |  |  |

|-------------|---------------|------|---------------|--------------|--|--|

| Ball Number | Ball Function | Bank | Dual Function | Differential |  |  |

| E13         | PT16D         | 1    |               | С            |  |  |

| C15         | PT16C         | 1    |               | Т            |  |  |

| F13         | PT16B         | 1    |               | С            |  |  |

| D14         | PT16A         | 1    |               | Т            |  |  |

| A18         | PT15D         | 1    |               | С            |  |  |

| B17         | PT15C         | 1    |               | Т            |  |  |

| A16         | PT15B         | 1    |               | С            |  |  |

| A17         | PT15A         | 1    |               | Т            |  |  |

| VCC         | VCC           | -    |               |              |  |  |

| D13         | PT14D         | 1    |               | С            |  |  |

| F12         | PT14C         | 1    |               | Т            |  |  |

| C14         | PT14B         | 1    |               | С            |  |  |

| E12         | PT14A         | 1    |               | Т            |  |  |

| C13         | PT13D         | 1    |               | С            |  |  |

| B16         | PT13C         | 1    |               | Т            |  |  |

| B15         | PT13B         | 1    |               | С            |  |  |

| A15         | PT13A         | 1    |               | Т            |  |  |

| VCCIO1      | VCCIO1        | 1    |               |              |  |  |

| GND         | GNDIO1        | 1    |               |              |  |  |

| B14         | PT12F         | 1    |               | С            |  |  |

| A14         | PT12E         | 1    |               | Т            |  |  |

| D12         | PT12D         | 1    |               | С            |  |  |

| F11         | PT12C         | 1    |               | Т            |  |  |

| B13         | PT12B         | 1    |               | С            |  |  |

| A13         | PT12A         | 1    |               | Т            |  |  |

| C12         | PT11D         | 1    |               | С            |  |  |

| GND         | GND           | -    |               |              |  |  |

| B12         | PT11C         | 1    |               | Т            |  |  |

| E11         | PT11B         | 1    |               | С            |  |  |

| D11         | PT11A         | 1    |               | Т            |  |  |

| C11         | PT10F         | 1    |               | С            |  |  |

| A12         | PT10E         | 1    |               | Т            |  |  |

| VCCIO1      | VCCIO1        | 1    |               |              |  |  |

| GND         | GNDIO1        | 1    |               |              |  |  |

| F10         | PT10D         | 1    |               | С            |  |  |

| D10         | PT10C         | 1    |               | Т            |  |  |

| B11         | PT10B         | 1    | PCLK1_1***    | С            |  |  |

| A11         | PT10A         | 1    |               | Т            |  |  |

| E10         | PT9D          | 1    |               | С            |  |  |

| C10         | PT9C          | 1    |               | Т            |  |  |

| D9          | PT9B          | 1    | PCLK1_0***    | С            |  |  |

| E9          | PT9A          | 1    |               | Т            |  |  |

| B10         | PT8F          | 0    |               | С            |  |  |

| Part Number      | LUTs | Supply Voltage | I/Os | Grade | Package | Pins | Temp. |

|------------------|------|----------------|------|-------|---------|------|-------|

| LCMXO256E-3T100I | 256  | 1.2V           | 78   | -3    | TQFP    | 100  | IND   |

| LCMXO256E-4T100I | 256  | 1.2V           | 78   | -4    | TQFP    | 100  | IND   |

| LCMXO256E-3M100I | 256  | 1.2V           | 78   | -3    | csBGA   | 100  | IND   |

| LCMXO256E-4M100I | 256  | 1.2V           | 78   | -4    | csBGA   | 100  | IND   |

| Part Number       | LUTs | Supply Voltage | l/Os | Grade | Package | Pins | Temp. |

|-------------------|------|----------------|------|-------|---------|------|-------|

| LCMXO640E-3T100I  | 640  | 1.2V           | 74   | -3    | TQFP    | 100  | IND   |

| LCMXO640E-4T100I  | 640  | 1.2V           | 74   | -4    | TQFP    | 100  | IND   |

| LCMXO640E-3M100I  | 640  | 1.2V           | 74   | -3    | csBGA   | 100  | IND   |

| LCMXO640E-4M100I  | 640  | 1.2V           | 74   | -4    | csBGA   | 100  | IND   |

| LCMXO640E-3T144I  | 640  | 1.2V           | 113  | -3    | TQFP    | 144  | IND   |

| LCMXO640E-4T144I  | 640  | 1.2V           | 113  | -4    | TQFP    | 144  | IND   |

| LCMXO640E-3M132I  | 640  | 1.2V           | 101  | -3    | csBGA   | 132  | IND   |

| LCMXO640E-4M132I  | 640  | 1.2V           | 101  | -4    | csBGA   | 132  | IND   |

| LCMXO640E-3B256I  | 640  | 1.2V           | 159  | -3    | caBGA   | 256  | IND   |

| LCMXO640E-4B256I  | 640  | 1.2V           | 159  | -4    | caBGA   | 256  | IND   |

| LCMXO640E-3FT256I | 640  | 1.2V           | 159  | -3    | ftBGA   | 256  | IND   |

| LCMXO640E-4FT256I | 640  | 1.2V           | 159  | -4    | ftBGA   | 256  | IND   |

| Part Number        | LUTs | Supply Voltage | l/Os | Grade | Package | Pins | Temp. |

|--------------------|------|----------------|------|-------|---------|------|-------|

| LCMXO1200E-3T100I  | 1200 | 1.2V           | 73   | -3    | TQFP    | 100  | IND   |

| LCMXO1200E-4T100I  | 1200 | 1.2V           | 73   | -4    | TQFP    | 100  | IND   |

| LCMXO1200E-3T144I  | 1200 | 1.2V           | 113  | -3    | TQFP    | 144  | IND   |

| LCMXO1200E-4T144I  | 1200 | 1.2V           | 113  | -4    | TQFP    | 144  | IND   |

| LCMXO1200E-3M132I  | 1200 | 1.2V           | 101  | -3    | csBGA   | 132  | IND   |

| LCMXO1200E-4M132I  | 1200 | 1.2V           | 101  | -4    | csBGA   | 132  | IND   |

| LCMXO1200E-3B256I  | 1200 | 1.2V           | 211  | -3    | caBGA   | 256  | IND   |

| LCMXO1200E-4B256I  | 1200 | 1.2V           | 211  | -4    | caBGA   | 256  | IND   |

| LCMXO1200E-3FT256I | 1200 | 1.2V           | 211  | -3    | ftBGA   | 256  | IND   |

| LCMXO1200E-4FT256I | 1200 | 1.2V           | 211  | -4    | ftBGA   | 256  | IND   |

| Part Number        | LUTs | Supply Voltage | I/Os | Grade | Package | Pins | Temp. |

|--------------------|------|----------------|------|-------|---------|------|-------|

| LCMXO2280E-3T100I  | 2280 | 1.2V           | 73   | -3    | TQFP    | 100  | IND   |

| LCMXO2280E-4T100I  | 2280 | 1.2V           | 73   | -4    | TQFP    | 100  | IND   |

| LCMXO2280E-3T144I  | 2280 | 1.2V           | 113  | -3    | TQFP    | 144  | IND   |

| LCMXO2280E-4T144I  | 2280 | 1.2V           | 113  | -4    | TQFP    | 144  | IND   |

| LCMXO2280E-3M132I  | 2280 | 1.2V           | 101  | -3    | csBGA   | 132  | IND   |

| LCMXO2280E-4M132I  | 2280 | 1.2V           | 101  | -4    | csBGA   | 132  | IND   |

| LCMXO2280E-3B256I  | 2280 | 1.2V           | 211  | -3    | caBGA   | 256  | IND   |

| LCMXO2280E-4B256I  | 2280 | 1.2V           | 211  | -4    | caBGA   | 256  | IND   |

| LCMXO2280E-3FT256I | 2280 | 1.2V           | 211  | -3    | ftBGA   | 256  | IND   |

| LCMXO2280E-4FT256I | 2280 | 1.2V           | 211  | -4    | ftBGA   | 256  | IND   |

| LCMXO2280E-3FT324I | 2280 | 1.2V           | 271  | -3    | ftBGA   | 324  | IND   |

| LCMXO2280E-4FT324I | 2280 | 1.2V           | 271  | -4    | ftBGA   | 324  | IND   |

# MachXO Family Data Sheet Supplemental Information

June 2013

Data Sheet DS1002

### **For Further Information**

A variety of technical notes for the MachXO family are available on the Lattice web site.

- TN1091, MachXO sysIO Usage Guide

- TN1089, MachXO sysCLOCK Design and Usage Guide

- TN1092, Memory Usage Guide for MachXO Devices

- TN1090, Power Estimation and Management for MachXO Devices

- TN1086, MachXO JTAG Programming and Configuration User's Guide

- TN1087, Minimizing System Interruption During Configuration Using TransFR Technology

- TN1097, MachXO Density Migration

- AN8066, Boundary Scan Testability with Lattice sysIO Capability

For further information on interface standards refer to the following web sites:

- JEDEC Standards (LVTTL, LVCMOS): www.jedec.org

- PCI: <u>www.pcisig.com</u>

<sup>© 2013</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Date          | Version | Section                             | Change Summary                                                                                                                                                                       |

|---------------|---------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| November 2006 | 02.3    | DC and Switching<br>Characteristics | Corrections to MachXO "C" Sleep Mode Timing table - value for t <sub>WSLEEPN</sub> (400ns) changed from max. to min. Value for t <sub>WAWAKE</sub> (100ns) changed from min. to max. |

|               |         |                                     | Added Flash Download Time table.                                                                                                                                                     |

| December 2006 | 02.4    | Architecture                        | EBR Asynchronous Reset section added.                                                                                                                                                |

|               |         | Pinout Information                  | Power Supply and NC table: Pin/Ball orientation footnotes added.                                                                                                                     |

| February 2007 | 02.5    | Architecture                        | Updated EBR Asynchronous Reset section.                                                                                                                                              |

| August 2007   | 02.6    | DC and Switching<br>Characteristics | Updated sysIO Single-Ended DC Electrical Characteristics table.                                                                                                                      |

|               |         | DC and Switching<br>Characteristics | Added JTAG Port Timing Waveforms diagram.                                                                                                                                            |

|               |         | Pinout Information                  | Added Thermal Management text section.                                                                                                                                               |

|               |         | Supplemental<br>Information         | Updated title list.                                                                                                                                                                  |

| June 2009     | 02.8    | Introduction                        | Added 0.8-mm 256-pin caBGA package to MachXO Family Selection Guide table.                                                                                                           |

|               |         | Pinout Information                  | Added Logic Signal Connections table for 0.8-mm 256-pin caBGA package.                                                                                                               |

|               |         | Ordering Information                | Updated Part Number Description diagram and Ordering Part Number tables with 0.8-mm 256-pin caBGA package information.                                                               |

| July 2010     | 02.9    | DC and Switching<br>Characteristics | Updated sysCLOCK PLL Timing table.                                                                                                                                                   |

| June 2013     | 03.0    | All                                 | Updated document with new corporate logo.                                                                                                                                            |

|               |         | Architecture                        | Architecture Overview – Added information on the state of the register on power up and after configuration.                                                                          |

|               |         | DC and Switching<br>Characteristics | MachXO1200 and MachXO2280 Hot Socketing Specifications table – Removed footnote 4.                                                                                                   |

|               |         |                                     | Added MachXO Programming/Erase Specifications table.                                                                                                                                 |