# E. Keniconductor Corporation - <u>LCMXO2280E-5FTN256C Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                         |

|--------------------------------|--------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 285                                                                            |

| Number of Logic Elements/Cells | 2280                                                                           |

| Total RAM Bits                 | 28262                                                                          |

| Number of I/O                  | 211                                                                            |

| Number of Gates                | -                                                                              |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                  |

| Mounting Type                  | Surface Mount                                                                  |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                                |

| Package / Case                 | 256-LBGA                                                                       |

| Supplier Device Package        | 256-FTBGA (17x17)                                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lcmxo2280e-5ftn256c |

|                                |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

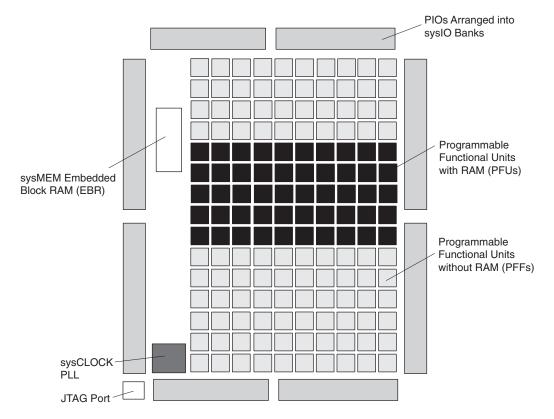

## Figure 2-1. Top View of the MachXO1200 Device<sup>1</sup>

1. Top view of the MachXO2280 device is similar but with higher LUT count, two PLLs, and three EBR blocks.

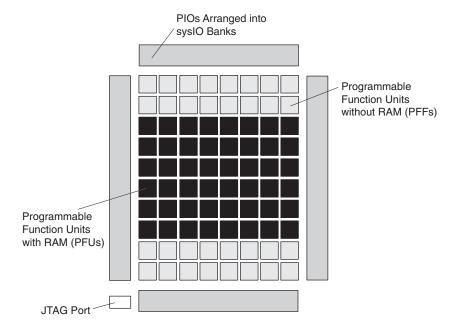

Figure 2-2. Top View of the MachXO640 Device

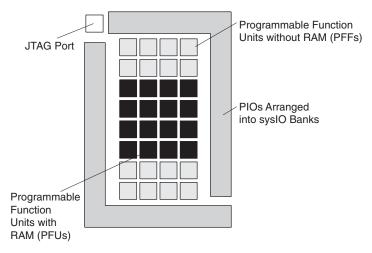

## Figure 2-3. Top View of the MachXO256 Device

## **PFU Blocks**

The core of the MachXO devices consists of PFU and PFF blocks. The PFUs can be programmed to perform Logic, Arithmetic, Distributed RAM, and Distributed ROM functions. PFF blocks can be programmed to perform Logic, Arithmetic, and Distributed ROM functions. Except where necessary, the remainder of this data sheet will use the term PFU to refer to both PFU and PFF blocks.

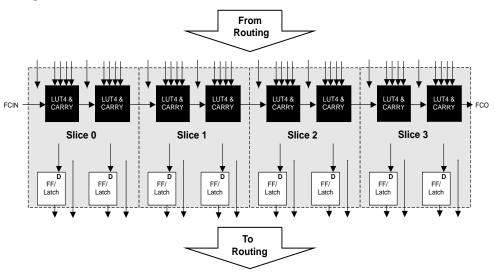

Each PFU block consists of four interconnected Slices, numbered 0-3 as shown in Figure 2-4. There are 53 inputs and 25 outputs associated with each PFU block.

## Figure 2-4. PFU Diagram

## Slice

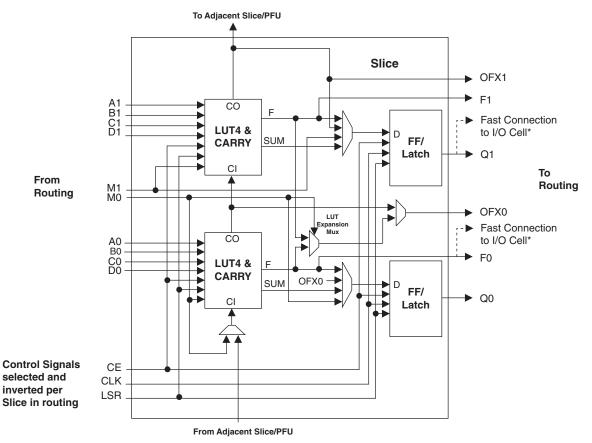

Each Slice contains two LUT4 lookup tables feeding two registers (programmed to be in FF or Latch mode), and some associated logic that allows the LUTs to be combined to perform functions such as LUT5, LUT6, LUT7, and LUT8. There is control logic to perform set/reset functions (programmable as synchronous/asynchronous), clock select, chip-select, and wider RAM/ROM functions. Figure 2-5 shows an overview of the internal logic of the Slice. The registers in the Slice can be configured for positive/negative and edge/level clocks.

There are 14 input signals: 13 signals from routing and one from the carry-chain (from the adjacent Slice/PFU). There are 7 outputs: 6 to the routing and one to the carry-chain (to the adjacent Slice/PFU). Table 2-1 lists the signals associated with each Slice.

#### Figure 2-5. Slice Diagram

Notes:

Some inter-Slice signals are not shown. \* Only PFUs at the edges have fast connections to the I/O cell.

Table 2-1. Slice Signal Descriptions

| Function | Туре             | Signal Names   | Description                                                          |

|----------|------------------|----------------|----------------------------------------------------------------------|

| Input    | Data signal      | A0, B0, C0, D0 | Inputs to LUT4                                                       |

| Input    | Data signal      | A1, B1, C1, D1 | Inputs to LUT4                                                       |

| Input    | Multi-purpose    | M0/M1          | Multipurpose Input                                                   |

| Input    | Control signal   | CE             | Clock Enable                                                         |

| Input    | Control signal   | LSR            | Local Set/Reset                                                      |

| Input    | Control signal   | CLK            | System Clock                                                         |

| Input    | Inter-PFU signal | FCIN           | Fast Carry In <sup>1</sup>                                           |

| Output   | Data signals     | F0, F1         | LUT4 output register bypass signals                                  |

| Output   | Data signals     | Q0, Q1         | Register Outputs                                                     |

| Output   | Data signals     | OFX0           | Output of a LUT5 MUX                                                 |

| Output   | Data signals     | OFX1           | Output of a LUT6, LUT7, LUT8 <sup>2</sup> MUX depending on the Slice |

| Output   | Inter-PFU signal | FCO            | Fast Carry Out <sup>1</sup>                                          |

1. See Figure 2-4 for connection details.

2. Requires two PFUs.

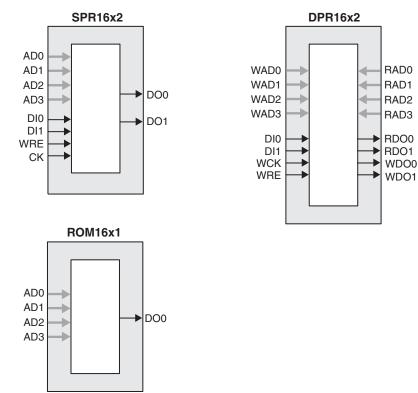

## Figure 2-6. Distributed Memory Primitives

**ROM Mode:** The ROM mode uses the same principal as the RAM modes, but without the Write port. Pre-loading is accomplished through the programming interface during configuration.

## **PFU Modes of Operation**

Slices can be combined within a PFU to form larger functions. Table 2-4 tabulates these modes and documents the functionality possible at the PFU level.

| Table | 2-4. | PFU | Modes | of | Operation |

|-------|------|-----|-------|----|-----------|

|-------|------|-----|-------|----|-----------|

| Logic                      | Ripple            | RAM                        | ROM         |

|----------------------------|-------------------|----------------------------|-------------|

| LUT 4x8 or<br>MUX 2x1 x 8  | 2-bit Add x 4     | SPR16x2 x 4<br>DPR16x2 x 2 | ROM16x1 x 8 |

| LUT 5x4 or<br>MUX 4x1 x 4  | 2-bit Sub x 4     | SPR16x4 x 2<br>DPR16x4 x 1 | ROM16x2 x 4 |

| LUT 6x 2 or<br>MUX 8x1 x 2 | 2-bit Counter x 4 | SPR16x8 x 1                | ROM16x4 x 2 |

| LUT 7x1 or<br>MUX 16x1 x 1 | 2-bit Comp x 4    |                            | ROM16x8 x 1 |

## Routing

There are many resources provided in the MachXO devices to route signals individually or as buses with related control signals. The routing resources consist of switching circuitry, buffers and metal interconnect (routing) segments.

The inter-PFU connections are made with three different types of routing resources: x1 (spans two PFUs), x2 (spans three PFUs) and x6 (spans seven PFUs). The x1, x2, and x6 connections provide fast and efficient connections in the horizontal and vertical directions.

The ispLEVER design tool takes the output of the synthesis tool and places and routes the design. Generally, the place and route tool is completely automatic, although an interactive routing editor is available to optimize the design.

## **Clock/Control Distribution Network**

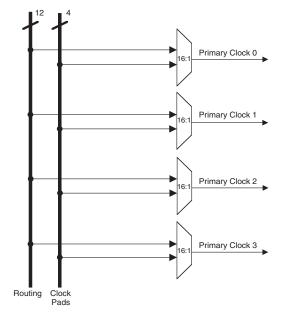

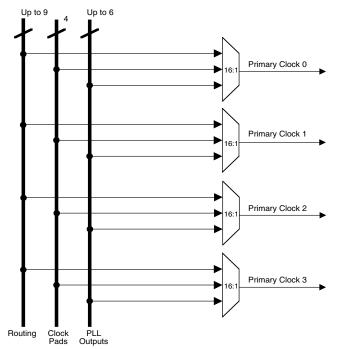

The MachXO family of devices provides global signals that are available to all PFUs. These signals consist of four primary clocks and four secondary clocks. Primary clock signals are generated from four 16:1 muxes as shown in Figure 2-7 and Figure 2-8. The available clock sources for the MachXO256 and MachXO640 devices are four dual function clock pins and 12 internal routing signals. The available clock sources for the MachXO2280 devices are four dual function clock pins, up to nine internal routing signals and up to six PLL outputs.

## Figure 2-7. Primary Clocks for MachXO256 and MachXO640 Devices

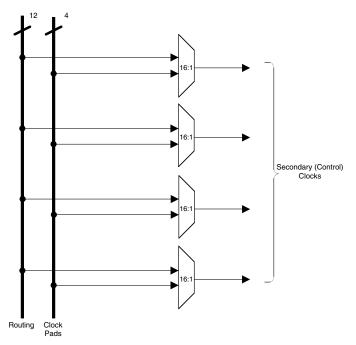

Four secondary clocks are generated from four 16:1 muxes as shown in Figure 2-9. Four of the secondary clock sources come from dual function clock pins and 12 come from internal routing.

Figure 2-9. Secondary Clocks for MachXO Devices

## Table 2-5. PLL Signal Descriptions

| Signal       | I/O | Description                                                                                                 |

|--------------|-----|-------------------------------------------------------------------------------------------------------------|

| CLKI         | I   | Clock input from external pin or routing                                                                    |

| CLKFB        | I   | PLL feedback input from PLL output, clock net, routing/external pin or internal feedback from CLKINTFB port |

| RST          | I   | "1" to reset the input clock divider                                                                        |

| CLKOS        | 0   | PLL output clock to clock tree (phase shifted/duty cycle changed)                                           |

| CLKOP        | 0   | PLL output clock to clock tree (No phase shift)                                                             |

| CLKOK        | 0   | PLL output to clock tree through secondary clock divider                                                    |

| LOCK         | 0   | "1" indicates PLL LOCK to CLKI                                                                              |

| CLKINTFB     | 0   | Internal feedback source, CLKOP divider output before CLOCKTREE                                             |

| DDAMODE      | I   | Dynamic Delay Enable. "1": Pin control (dynamic), "0": Fuse Control (static)                                |

| DDAIZR       | I   | Dynamic Delay Zero. "1": delay = 0, "0": delay = on                                                         |

| DDAILAG      | I   | Dynamic Delay Lag/Lead. "1": Lag, "0": Lead                                                                 |

| DDAIDEL[2:0] | I   | Dynamic Delay Input                                                                                         |

For more information on the PLL, please see details of additional technical documentation at the end of this data sheet.

## sysMEM Memory

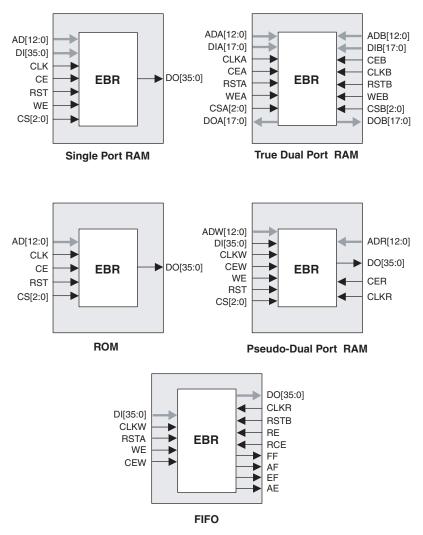

The MachXO1200 and MachXO2280 devices contain sysMEM Embedded Block RAMs (EBRs). The EBR consists of a 9-Kbit RAM, with dedicated input and output registers.

#### sysMEM Memory Block

The sysMEM block can implement single port, dual port, pseudo dual port, or FIFO memories. Each block can be used in a variety of depths and widths as shown in Table 2-6.

#### Table 2-6. sysMEM Block Configurations

| Memory Mode      | Configurations                                                           |

|------------------|--------------------------------------------------------------------------|

| Single Port      | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18<br>256 x 36 |

| True Dual Port   | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18             |

| Pseudo Dual Port | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18<br>256 x 36 |

| FIFO             | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18<br>256 x 36 |

#### **Bus Size Matching**

All of the multi-port memory modes support different widths on each of the ports. The RAM bits are mapped LSB word 0 to MSB word 0, LSB word 1 to MSB word 1 and so on. Although the word size and number of words for each port varies, this mapping scheme applies to each port.

#### **RAM Initialization and ROM Operation**

If desired, the contents of the RAM can be pre-loaded during device configuration. By preloading the RAM block during the chip configuration cycle and disabling the write controls, the sysMEM block can also be utilized as a ROM.

#### **Memory Cascading**

Larger and deeper blocks of RAMs can be created using EBR sysMEM Blocks. Typically, the Lattice design tools cascade memory transparently, based on specific design inputs.

#### Single, Dual, Pseudo-Dual Port and FIFO Modes

Figure 2-12 shows the five basic memory configurations and their input/output names. In all the sysMEM RAM modes, the input data and address for the ports are registered at the input of the memory array. The output data of the memory is optionally registered at the memory array output.

## Figure 2-12. sysMEM Memory Primitives

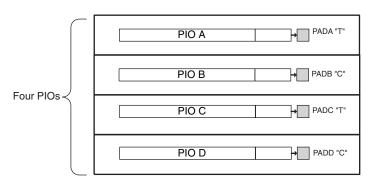

## **PIO Groups**

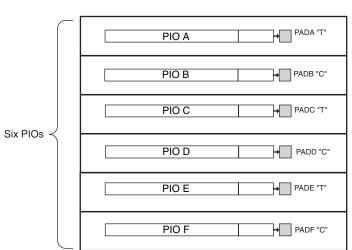

On the MachXO devices, PIO cells are assembled into two different types of PIO groups, those with four PIO cells and those with six PIO cells. PIO groups with four IOs are placed on the left and right sides of the device while PIO groups with six IOs are placed on the top and bottom. The individual PIO cells are connected to their respective sysIO buffers and PADs.

On all MachXO devices, two adjacent PIOs can be joined to provide a complementary Output driver pair. The I/O pin pairs are labeled as "T" and "C" to distinguish between the true and complement pins.

The MachXO1200 and MachXO2280 devices contain enhanced I/O capability. All PIO pairs on these larger devices can implement differential receivers. In addition, half of the PIO pairs on the left and right sides of these devices can be configured as LVDS transmit/receive pairs. PIOs on the top of these larger devices also provide PCI support.

## Figure 2-15. Group of Four Programmable I/O Cells

This structure is used on the left and right of MachXO devices

Figure 2-16. Group of Six Programmable I/O Cells

## This structure is used on the top and bottom of MachXO devices $\label{eq:machine}$

## PIO

The PIO blocks provide the interface between the sysIO buffers and the internal PFU array blocks. These blocks receive output data from the PFU array and a fast output data signal from adjacent PFUs. The output data and fast

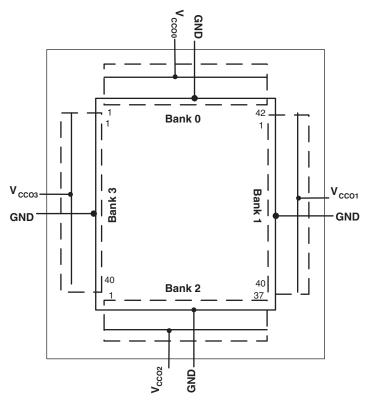

## Figure 2-20. MachXO640 Banks

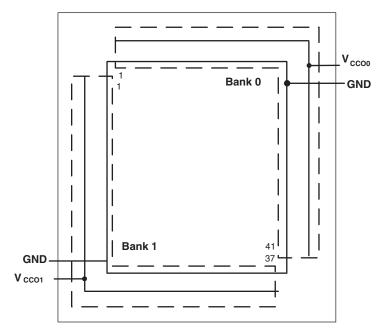

Figure 2-21. MachXO256 Banks

## **Hot Socketing**

The MachXO devices have been carefully designed to ensure predictable behavior during power-up and powerdown. Leakage into I/O pins is controlled to within specified limits. This allows for easy integration with the rest of

## **Density Shifting**

The MachXO family has been designed to enable density migration in the same package. Furthermore, the architecture ensures a high success rate when performing design migration from lower density parts to higher density parts. In many cases, it is also possible to shift a lower utilization design targeted for a high-density device to a lower density device. However, the exact details of the final resource utilization will impact the likely success in each case.

## sysIO Differential Electrical Characteristics LVDS

| Parameter<br>Symbol                | Parameter Description                          | Test Conditions                                                | Min.                | Тур. | Max.  | Units |

|------------------------------------|------------------------------------------------|----------------------------------------------------------------|---------------------|------|-------|-------|

| V <sub>INP,</sub> V <sub>INM</sub> | Input Voltage                                  |                                                                | 0                   |      | 2.4   | V     |

| V <sub>THD</sub>                   | Differential Input Threshold                   |                                                                | +/-100              | _    | —     | mV    |

|                                    |                                                | $100mV \le V_{THD}$                                            | V <sub>THD</sub> /2 | 1.2  | 1.8   | V     |

| V <sub>CM</sub>                    | Input Common Mode Voltage                      | $200mV \le V_{THD}$                                            | V <sub>THD</sub> /2 | 1.2  | 1.9   | V     |

|                                    |                                                | $350mV \le V_{THD}$                                            | V <sub>THD</sub> /2 | 1.2  | 2.0   | V     |

| I <sub>IN</sub>                    | Input current                                  | Power on                                                       | —                   |      | +/-10 | μΑ    |

| V <sub>OH</sub>                    | Output high voltage for $V_{OP}$ or $V_{OM}$   | R <sub>T</sub> = 100 Ohm                                       | —                   | 1.38 | 1.60  | V     |

| V <sub>OL</sub>                    | Output low voltage for $V_{OP}$ or $V_{OM}$    | R <sub>T</sub> = 100 Ohm                                       | 0.9V                | 1.03 | —     | V     |

| V <sub>OD</sub>                    | Output voltage differential                    | (V <sub>OP</sub> - V <sub>OM</sub> ), R <sub>T</sub> = 100 Ohm | 250                 | 350  | 450   | mV    |

| ΔV <sub>OD</sub>                   | Change in V <sub>OD</sub> between high and low |                                                                | _                   | _    | 50    | mV    |

| V <sub>OS</sub>                    | Output voltage offset                          | $(V_{OP} - V_{OM})/2, R_T = 100 \text{ Ohm}$                   | 1.125               | 1.25 | 1.375 | V     |

| $\Delta V_{OS}$                    | Change in V <sub>OS</sub> between H and L      |                                                                | —                   | _    | 50    | mV    |

| I <sub>OSD</sub>                   | Output short circuit current                   | V <sub>OD</sub> = 0V Driver outputs shorted                    | _                   |      | 6     | mA    |

## **Over Recommended Operating Conditions**

## **LVDS Emulation**

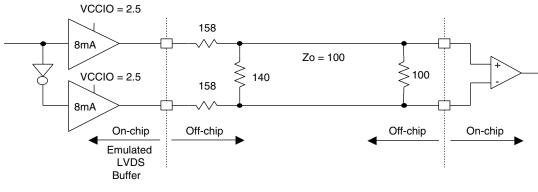

MachXO devices can support LVDS outputs via emulation (LVDS25E), in addition to the LVDS support that is available on-chip on certain devices. The output is emulated using complementary LVCMOS outputs in conjunction with resistors across the driver outputs on all devices. The scheme shown in Figure 3-1 is one possible solution for LVDS standard implementation. Resistor values in Figure 3-1 are industry standard values for 1% resistors.

## Figure 3-1. LVDS Using External Resistors (LVDS25E)

Note: All resistors are  $\pm 1\%$ .

The LVDS differential input buffers are available on certain devices in the MachXO family.

## MachXO External Switching Characteristics<sup>1</sup>

|                       |                                         |                         | -    | 5    | -    | 4    | -    | 3                                                                                                                                                                                                                                                                                                                          |       |

|-----------------------|-----------------------------------------|-------------------------|------|------|------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Parameter             | Description                             | Device                  | Min. | Max. | Min. | Max. | Min. | Max.                                                                                                                                                                                                                                                                                                                       | Units |

| General I/O           | Pin Parameters (Using Global Clock with |                         |      |      |      |      |      | •                                                                                                                                                                                                                                                                                                                          |       |

|                       |                                         | LCMXO256                | _    | 3.5  | —    | 4.2  | —    | 4.9                                                                                                                                                                                                                                                                                                                        | ns    |

| •                     | Post Cose t Through 1 LUT               | LCMXO640                | _    | 3.5  | —    | 4.2  | —    | 4.9                                                                                                                                                                                                                                                                                                                        | ns    |

| t <sub>PD</sub>       | Best Case t <sub>PD</sub> Through 1 LUT | LCMXO1200               | _    | 3.6  | —    | 4.4  | —    | 5.1                                                                                                                                                                                                                                                                                                                        | ns    |

|                       |                                         | LCMXO2280 — 3.6 — 4.4 — | 5.1  | ns   |      |      |      |                                                                                                                                                                                                                                                                                                                            |       |

|                       |                                         | LCMXO256                |      | 4.0  | —    | 4.8  | —    | 5.6                                                                                                                                                                                                                                                                                                                        | ns    |

| +                     | Best Case Clock to Output - From PFU    | LCMXO640                | _    | 4.0  | —    | 4.8  | —    | 5.7                                                                                                                                                                                                                                                                                                                        | ns    |

| t <sub>CO</sub>       | Best Case Clock to Output - FIOIII FFO  | LCMXO1200               | _    | 4.3  | —    | 5.2  | —    | 6.1                                                                                                                                                                                                                                                                                                                        | ns    |

|                       |                                         | LCMXO2280               |      | 4.3  | —    | 5.2  | —    | 6.1                                                                                                                                                                                                                                                                                                                        | ns    |

|                       |                                         | LCMXO256                | 1.3  | —    | 1.6  | —    | 1.8  | —                                                                                                                                                                                                                                                                                                                          | ns    |

| +                     | Clock to Data Setup - To PFU            | LCMXO640                | 1.1  | —    | 1.3  | —    | 1.5  | —                                                                                                                                                                                                                                                                                                                          | ns    |

| t <sub>SU</sub>       | Clock to Data Setup - To PPO            | LCMXO1200               | 1.1  | —    | 1.3  | —    | 1.6  | —                                                                                                                                                                                                                                                                                                                          | ns    |

|                       |                                         | LCMXO2280               | 1.1  | —    | 1.3  | —    | 1.5  | —                                                                                                                                                                                                                                                                                                                          | ns    |

|                       |                                         | LCMXO256                | -0.3 | —    | -0.3 | —    | -0.3 | —                                                                                                                                                                                                                                                                                                                          | ns    |

| +                     | Clock to Data Hold - To PFU             | LCMXO640                | -0.1 | —    | -0.1 |      | -0.1 | _                                                                                                                                                                                                                                                                                                                          | ns    |

| t <sub>H</sub>        |                                         | LCMXO1200               | 0.0  | —    | 0.0  | —    | 0.0  | —                                                                                                                                                                                                                                                                                                                          | ns    |

|                       |                                         | LCMXO2280               | -0.4 | —    | -0.4 |      | -0.4 | —                                                                                                                                                                                                                                                                                                                          | ns    |

|                       |                                         | LCMXO256                |      | 600  | —    | 550  | —    | 500                                                                                                                                                                                                                                                                                                                        | MHz   |

| f                     | Clock Frequency of I/O and PFU Register | LCMXO640                |      | 600  | —    | 550  | —    | 500                                                                                                                                                                                                                                                                                                                        | MHz   |

| f <sub>MAX_IO</sub>   | Clock Frequency of I/O and FFO Register | LCMXO1200               | _    | 600  | —    | 550  |      | 500                                                                                                                                                                                                                                                                                                                        | MHz   |

|                       |                                         | LCMXO2280               | _    | 600  | —    | 550  | —    | 500                                                                                                                                                                                                                                                                                                                        | MHz   |

|                       |                                         | LCMXO256                | _    | 200  | —    | 220  | —    | 240                                                                                                                                                                                                                                                                                                                        | ps    |

| +.                    | Global Clock Skew Across Device         | LCMXO640                |      | 200  | —    | 220  | —    | 240                                                                                                                                                                                                                                                                                                                        | ps    |

| t <sub>SKEW_PRI</sub> | GIODAI GIOCK SKEW ACIOSS DEVICE         | LCMXO1200               |      | 220  | —    | 240  | —    | 4.9   ns     5.1   ns     5.1   ns     5.6   ns     5.7   ns     6.1   ns     6.1   ns     6.1   ns      ns     500   MHz     500   MHz     500   MHz     240   ps |       |

|                       |                                         | LCMXO2280               | _    | 220  | —    | 240  | —    | 260                                                                                                                                                                                                                                                                                                                        | ps    |

## **Over Recommended Operating Conditions**

1. General timing numbers based on LVCMOS2.5V, 12 mA. Rev. A 0.19

## Power Supply and NC (Cont.)

| Signal           | 132 csBGA <sup>1</sup>                                 | 256 caBGA / 256 ftBGA <sup>1</sup>                                                                                                                                                                                                                                                                            | 324 ftBGA <sup>1</sup>                                                                                              |

|------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| VCC              | H3, P6, G12, C7                                        | G7, G10, K7, K10                                                                                                                                                                                                                                                                                              | F14, G11, G9, H7, L7, M9                                                                                            |

| VCCIO0           | LCMXO640: B11, C5<br>LCMXO1200/2280: C5                | LCMXO640: F8, F7, F9, F10<br>LCMXO1200/2280: F8, F7                                                                                                                                                                                                                                                           | G8, G7                                                                                                              |

| VCCIO1           | LCMXO640: L12, E12<br>LCMXO1200/2280: B11              | LCMXO640: H11, G11, K11, J11<br>LCMXO1200/2280: F9, F10                                                                                                                                                                                                                                                       | G12, G10                                                                                                            |

| VCCIO2           | LCMXO640: N2, M10<br>LCMXO1200/2280: E12               | LCMXO640: L9, L10, L8, L7<br>LCMXO1200/2280: H11, G11                                                                                                                                                                                                                                                         | J12, H12                                                                                                            |

| VCCIO3           | LCMXO640: D2, K3<br>LCMXO1200/2280: L12                | LCMXO640: K6, J6, H6, G6<br>LCMXO1200/2280: K11, J11                                                                                                                                                                                                                                                          | L12, K12                                                                                                            |

| VCCIO4           | LCMXO640: None<br>LCMXO1200/2280: M10                  | LCMXO640: None<br>LCMXO1200/2280: L9, L10                                                                                                                                                                                                                                                                     | M12, M11                                                                                                            |

| VCCIO5           | LCMXO640: None<br>LCMXO1200/2280: N2                   | LCMXO640: None<br>LCMXO1200/2280: L8, L7                                                                                                                                                                                                                                                                      | M8, R9                                                                                                              |

| VCCIO6           | LCMXO640: None<br>LCMXO1200/2280: K3                   | LCMXO640: None<br>LCMXO1200/2280: K6, J6                                                                                                                                                                                                                                                                      | M7, K7                                                                                                              |

| VCCIO7           | LCMXO640: None<br>LCMXO1200/2280: D2                   | LCMXO640: None<br>LCMXO1200/2280: H6, G6                                                                                                                                                                                                                                                                      | H6, J7                                                                                                              |

| VCCAUX           | P7, A7                                                 | T9, A8                                                                                                                                                                                                                                                                                                        | M10, F9                                                                                                             |

| GND <sup>2</sup> | F1, P9, J14, C9, A10, B4, L13,<br>D13, P2, N11, E1, L2 | A1, A16, F11, G8, G9, H7, H8, H9,<br>H10, J7, J8, J9, J10, K8, K9, L6,<br>T1, T16                                                                                                                                                                                                                             | E14, F16, H10, H11, H8, H9, J10,<br>J11, J4, J8, J9, K10, K11, K17, K8,<br>K9, L10, L11, L8, L9, N2, P14, P5,<br>R7 |

| NC <sup>3</sup>  |                                                        | LCMXO640: E4, E5, F5, F6, C3,<br>C2, G4, G5, H4, H5, K5, K4, M5,<br>M4, P2, P3, N5, N6, M7, M8, N10,<br>N11, R15, R16, P15, P16, M11,<br>L11, N12, N13, M13, M12, K12,<br>J12, F12, F13, E12, E13, D13,<br>D14, B15, A15, C14, B14, E11,<br>E10, E7, E6, D4, D3, B3, B2<br>LCMXO1200: None<br>LCMXO2280: None |                                                                                                                     |

Pin orientation A1 starts from the upper left corner of the top side view with alphabetical order ascending vertically and numerical order ascending horizontally.

All grounds must be electrically connected at the board level. For fpBGA and ftBGA packages, the total number of GND balls is less than the actual number of GND logic connections from the die to the common package GND plane.

NC pins should not be connected to any active signals, VCC or GND.

# LCMXO256 and LCMXO640 Logic Signal Connections: 100 TQFP

|            |                  | LCM  | IXO256           |              | LCMXO640         |      |                  |              |  |  |

|------------|------------------|------|------------------|--------------|------------------|------|------------------|--------------|--|--|

| Pin Number | Ball<br>Function | Bank | Dual<br>Function | Differential | Ball<br>Function | Bank | Dual<br>Function | Differential |  |  |

| 1          | PL2A             | 1    |                  | Т            | PL2A             | 3    |                  | Т            |  |  |

| 2          | PL2B             | 1    |                  | С            | PL2C             | 3    |                  | Т            |  |  |

| 3          | PL3A             | 1    |                  | Т            | PL2B             | 3    |                  | С            |  |  |

| 4          | PL3B             | 1    |                  | С            | PL2D             | 3    |                  | С            |  |  |

| 5          | PL3C             | 1    |                  | Т            | PL3A             | 3    |                  | Т            |  |  |

| 6          | PL3D             | 1    |                  | С            | PL3B             | 3    |                  | С            |  |  |

| 7          | PL4A             | 1    |                  | Т            | PL3C             | 3    |                  | Т            |  |  |

| 8          | PL4B             | 1    |                  | С            | PL3D             | 3    |                  | С            |  |  |

| 9          | PL5A             | 1    |                  | Т            | PL4A             | 3    |                  |              |  |  |

| 10         | VCCIO1           | 1    |                  |              | VCCIO3           | 3    |                  |              |  |  |

| 11         | PL5B             | 1    |                  | С            | PL4C             | 3    |                  | Т            |  |  |

| 12         | GNDIO1           | 1    |                  |              | GNDIO3           | 3    |                  |              |  |  |

| 13         | PL5C             | 1    |                  | Т            | PL4D             | 3    |                  | С            |  |  |

| 14         | PL5D             | 1    | GSRN             | С            | PL5B             | 3    | GSRN             |              |  |  |

| 15         | PL6A             | 1    |                  | Т            | PL7B             | 3    |                  |              |  |  |

| 16         | PL6B             | 1    | TSALL            | С            | PL8C             | 3    | TSALL            | Т            |  |  |

| 17         | PL7A             | 1    |                  | Т            | PL8D             | 3    |                  | С            |  |  |

| 18         | PL7B             | 1    |                  | С            | PL9A             | 3    |                  |              |  |  |

| 19         | PL7C             | 1    |                  | Т            | PL9C             | 3    |                  |              |  |  |

| 20         | PL7D             | 1    |                  | С            | PL10A            | 3    |                  |              |  |  |

| 21         | PL8A             | 1    |                  | Т            | PL10C            | 3    |                  |              |  |  |

| 22         | PL8B             | 1    |                  | С            | PL11A            | 3    |                  |              |  |  |

| 23         | PL9A             | 1    |                  | Т            | PL11C            | 3    |                  |              |  |  |

| 24         | VCCIO1           | 1    |                  |              | VCCIO3           | 3    |                  |              |  |  |

| 25         | GNDIO1           | 1    |                  |              | GNDIO3           | 3    |                  |              |  |  |

| 26         | TMS              | 1    | TMS              |              | TMS              | 2    | TMS              |              |  |  |

| 27         | PL9B             | 1    |                  | С            | PB2C             | 2    |                  |              |  |  |

| 28         | ТСК              | 1    | ТСК              |              | TCK              | 2    | ТСК              |              |  |  |

| 29         | PB2A             | 1    |                  | Т            | VCCIO2           | 2    |                  |              |  |  |

| 30         | PB2B             | 1    |                  | С            | GNDIO2           | 2    |                  |              |  |  |

| 31         | TDO              | 1    | TDO              |              | TDO              | 2    | TDO              |              |  |  |

| 32         | PB2C             | 1    |                  | Т            | PB4C             | 2    |                  |              |  |  |

| 33         | TDI              | 1    | TDI              |              | TDI              | 2    | TDI              |              |  |  |

| 34         | PB2D             | 1    |                  | С            | PB4E             | 2    |                  |              |  |  |

| 35         | VCC              | -    |                  |              | VCC              | -    |                  |              |  |  |

| 36         | PB3A             | 1    | PCLK1_1**        | Т            | PB5B             | 2    | PCLK2_1**        |              |  |  |

| 37         | PB3B             | 1    |                  | С            | PB5D             | 2    |                  |              |  |  |

| 38         | PB3C             | 1    | PCLK1_0**        | Т            | PB6B             | 2    | PCLK2_0**        |              |  |  |

| 39         | PB3D             | 1    |                  | С            | PB6C             | 2    |                  |              |  |  |

| 40         | GND              | -    |                  |              | GND              | -    |                  |              |  |  |

| 41         | VCCIO1           | 1    |                  |              | VCCIO2           | 2    |                  |              |  |  |

| 42         | GNDIO1           | 1    |                  |              | GNDIO2           | 2    | 1                |              |  |  |

# LCMXO640, LCMXO1200 and LCMXO2280 Logic Signal Connections: 132 csBGA

|          |                  | LCM  | KO640            |              |          |                  | LC   | MXO1200          |              | LCMXO2280 |                  |                   |                  |              |

|----------|------------------|------|------------------|--------------|----------|------------------|------|------------------|--------------|-----------|------------------|-------------------|------------------|--------------|

| Ball #   | Ball<br>Function | Bonk | Dual<br>Function | Differential | Ball #   | Ball<br>Function | Bonk | Dual<br>Function | Differential | Ball #    | Ball<br>Function | Bonk              | Dual<br>Function | Differential |

| Ball #   | PL2A             | 3    | Function         | T            | Ball #   | PL2A             | 7    | Function         | T            | Ball #    | PL2A             | <b>Dalik</b><br>7 | LUM0_PLLT_FB_A   | T            |

| C1       | PL2B             | 3    |                  | C            | C1       | PL3C             | 7    |                  | T            | C1        | PL3C             | 7                 | LUM0_PLLT_IN_A   | T            |

| B2       | PL2C             | 3    |                  | Т            | B2       | PL2B             | 7    |                  | C            | B2        | PL2B             | 7                 | LUM0_PLLC_FB_A   | C            |

| C2       | PL2D             | 3    |                  | C            | C2       | PL4A             | 7    |                  | T*           | C2        | PL4A             | 7                 |                  | T*           |

| C2       | PL3A             | 3    |                  | Т            | C2       | PL3D             | 7    |                  | C            | C2        | PL3D             | 7                 | LUM0_PLLC_IN_A   | C            |

| D1       | PL3B             | 3    |                  | C            | D1       | PL4B             | 7    |                  | C*           | D1        | PL4B             | 7                 |                  | C*           |

| D3       | PL3D             | 3    |                  | 0            | D3       | PL4C             | 7    |                  | 0            | D3        | PL4C             | 7                 |                  | Ŭ            |

| E1       | GNDIO3           | 3    |                  |              | E1       | GNDIO7           | 7    |                  |              | E1        | GNDIO7           | 7                 |                  |              |

| E2       | PL5A             | 3    |                  | т            | E2       | PL6A             | 7    |                  | T*           | E2        | PL7A             | 7                 |                  | T*           |

| E3       | PL5B             | 3    | GSRN             | C            | E3       | PL6B             | 7    | GSRN             | C*           | E3        | PL7B             | 7                 | GSRN             | C*           |

| F2       | PL5D             | 3    | CONN             | 0            | F2       | PL6D             | 7    | CONN             | 0            | F2        | PL7D             | 7                 | CONN             | Ŭ            |

| F3       | PL6B             | 3    |                  |              | F3       | PL7C             | 7    |                  | Т            | F3        | PL9C             | 7                 |                  | т            |

| G1       | PL6C             | 3    |                  | т            | G1       | PL7D             | 7    |                  | C            | G1        | PL9D             | 7                 |                  | C            |

| G2       | PL6D             | 3    |                  | C            | G2       | PL8C             | 7    |                  | T            | G2        | PL10C            | 7                 |                  | Т            |

| G2<br>G3 | PL0D<br>PL7A     | 3    |                  | Т            | G2<br>G3 | PL8D             | 7    |                  | C            | G2<br>G3  | PL10C            | 7                 |                  | C            |

| H2       | PL7A<br>PL7B     | 3    |                  | C            | H2       | PLOD<br>PL10A    | 6    |                  | T*           | H2        | PL10D<br>PL12A   | 6                 |                  | T*           |

| H1       | PL7B<br>PL7C     | 3    |                  | U U          | H1       | PL10A<br>PL10B   | 6    |                  | C*           | H1        | PL12A<br>PL12B   | 6                 |                  | C*           |

|          | VCC              | -    |                  |              | H3       | VCC              | -    |                  | C            | H3        | VCC              | -                 |                  | U            |

| H3<br>J1 | PL8A             | - 3  |                  |              | пз<br>J1 | PL11B            | 6    |                  |              | пз<br>J1  | PL14D            | 6                 |                  | С            |

| J2       | PL8C             | 3    | TSALL            |              | J2       | PLIIB<br>PL11C   | 6    | TSALL            | т            | J2        | PL14D<br>PL14C   | 6                 | TSALL            | Т            |

|          |                  |      | TSALL            | -            |          |                  |      | ISALL            | C            |           |                  |                   | TSALL            | I            |

| J3       | PL9A             | 3    |                  | Т            | J3       | PL11D            | 6    |                  |              | J3        | PL14B            | 6                 |                  | T+           |

| K2       | PL9B             | 3    |                  | С            | K2       | PL12A            | 6    |                  | T*           | K2        | PL15A            | 6                 |                  | T*           |

| K1       | PL9C             | 3    |                  |              | K1       | PL12B            | 6    |                  | C*           | K1        | PL15B            | 6                 |                  | C*           |

| L2       | GNDIO3           | 3    |                  |              | L2       | GNDIO6           | 6    |                  |              | L2        | GNDIO6           | 6                 |                  |              |

| L1       | PL10A            | 3    |                  | Т            | L1       | PL14A            | 6    | LLM0_PLLT_FB_A   | T*           | L1        | PL17A            | 6                 | LLM0_PLLT_FB_A   | T*           |

| L3       | PL10B            | 3    |                  | С            | L3       | PL14B            | 6    | LLM0_PLLC_FB_A   | C*           | L3        | PL17B            | 6                 | LLM0_PLLC_FB_A   | C*           |

| M1       | PL11A            | 3    |                  | Т            | M1       | PL15A            | 6    | LLM0_PLLT_IN_A   | T*           | M1        | PL18A            | 6                 | LLM0_PLLT_IN_A   | T*           |

| N1       | PL11B            | 3    |                  | С            | N1       | PL16A            | 6    |                  | Т            | N1        | PL19A            | 6                 |                  | Т            |

| M2       | PL11C            | 3    |                  | Т            | M2       | PL15B            | 6    | LLM0_PLLC_IN_A   | C*           | M2        | PL18B            | 6                 | LLM0_PLLC_IN_A   | C*           |

| P1       | PL11D            | 3    |                  | С            | P1       | PL16B            | 6    |                  | С            | P1        | PL19B            | 6                 |                  | С            |

| P2       | GNDIO2           | 2    |                  |              | P2       | GNDIO5           | 5    |                  |              | P2        | GNDIO5           | 5                 |                  |              |

| P3       | TMS              | 2    | TMS              |              | P3       | TMS              | 5    | TMS              |              | P3        | TMS              | 5                 | TMS              |              |

| M3       | PB2C             | 2    |                  | Т            | M3       | PB2C             | 5    |                  | Т            | M3        | PB2A             | 5                 |                  | Т            |

| N3       | PB2D             | 2    |                  | С            | N3       | PB2D             | 5    |                  | С            | N3        | PB2B             | 5                 |                  | С            |

| P4       | TCK              | 2    | TCK              |              | P4       | TCK              | 5    | ТСК              |              | P4        | TCK              | 5                 | ТСК              |              |

| M4       | PB3B             | 2    |                  |              | M4       | PB3B             | 5    |                  |              | M4        | PB3B             | 5                 |                  |              |

| N4       | PB3C             | 2    |                  | Т            | N4       | PB4A             | 5    |                  | Т            | N4        | PB4A             | 5                 |                  | Т            |

| P5       | PB3D             | 2    |                  | С            | P5       | PB4B             | 5    |                  | С            | P5        | PB4B             | 5                 |                  | С            |

| N5       | TDO              | 2    | TDO              |              | N5       | TDO              | 5    | TDO              |              | N5        | TDO              | 5                 | TDO              |              |

| M5       | TDI              | 2    | TDI              |              | M5       | TDI              | 5    | TDI              |              | M5        | TDI              | 5                 | TDI              |              |

| N6       | PB4E             | 2    |                  | Т            | N6       | PB5C             | 5    |                  |              | N6        | PB6C             | 5                 |                  |              |

| P6       | VCC              | -    |                  |              | P6       | VCC              | -    |                  |              | P6        | VCC              | -                 |                  |              |

| M6       | PB4F             | 2    |                  | С            | M6       | PB6A             | 5    |                  |              | M6        | PB8A             | 5                 |                  |              |

| P7       | VCCAUX           | -    |                  |              | P7       | VCCAUX           | -    |                  |              | P7        | VCCAUX           | -                 |                  |              |

| N7       | PB5A             | 2    |                  | Т            | N7       | PB6F             | 5    |                  |              | N7        | PB8F             | 5                 |                  |              |

| M7       | PB5B             | 2    | PCLK2_1***       | С            | M7       | PB7B             | 4    | PCLK4_1***       |              | M7        | PB10F            | 4                 | PCLK4_1***       |              |

| N8       | PB5D             | 2    |                  |              | N8       | PB7C             | 4    |                  | Т            | N8        | PB10C            | 4                 |                  | Т            |

| P8       | PB6A             | 2    |                  | Т            | P8       | PB7D             | 4    |                  | С            | P8        | PB10D            | 4                 |                  | С            |

| M8       | PB6B             | 2    | PCLK2_0***       | С            | M8       | PB7F             | 4    | PCLK4_0***       |              | M8        | PB10B            | 4                 | PCLK4_0***       |              |

| N9       | PB7A             | 2    |                  | Т            | N9       | PB9A             | 4    |                  | Т            | N9        | PB12A            | 4                 |                  | Т            |

## LCMXO2280 Logic Signal Connections: 324 ftBGA (Cont.)

| Dell Number |               | LCMXO2280 | Dual Free stires | D:#*****    |

|-------------|---------------|-----------|------------------|-------------|

| Ball Number | Ball Function | Bank      | Dual Function    | Differentia |

| V10         | PB9B          | 4         |                  | С           |

| N10         | PB9C          | 4         |                  | Т           |

| R10         | PB9D          | 4         |                  | С           |

| P10         | PB10F         | 4         | PCLK4_1***       | С           |

| T10         | PB10E         | 4         |                  | Т           |

| U10         | PB10D         | 4         |                  | С           |

| V11         | PB10C         | 4         |                  | Т           |

| U11         | PB10B         | 4         | PCLK4_0***       | С           |

| VCCIO4      | VCCIO4        | 4         |                  |             |

| GND         | GNDIO4        | 4         |                  |             |

| T11         | PB10A         | 4         |                  | Т           |

| U12         | PB11A         | 4         |                  | Т           |

| R11         | PB11B         | 4         |                  | С           |

| GND         | GND           | -         |                  |             |

| T12         | PB11C         | 4         |                  | Т           |

| P11         | PB11D         | 4         |                  | С           |

| V12         | PB12A         | 4         |                  | Т           |

| V13         | PB12B         | 4         |                  | С           |

| R12         | PB12C         | 4         |                  | Т           |

| N11         | PB12D         | 4         |                  | С           |

| U13         | PB12E         | 4         |                  | Т           |

| VCCIO4      | VCCIO4        | 4         |                  |             |

| GND         | GNDIO4        | 4         |                  |             |

| V14         | PB12F         | 4         |                  | С           |

| T13         | PB13A         | 4         |                  | Т           |

| P12         | PB13B         | 4         |                  | С           |

| R13         | PB13C         | 4         |                  | Т           |

| N12         | PB13D         | 4         |                  | С           |

| V15         | PB14A         | 4         |                  | Т           |

| U14         | PB14B         | 4         |                  | С           |

| V16         | PB14C         | 4         |                  | Т           |

| GND         | GND           | -         |                  |             |

| T14         | PB14D         | 4         |                  | С           |

| U15         | PB15A         | 4         |                  | Т           |

| V17         | PB15B         | 4         |                  | С           |

| P13**       | SLEEPN        | -         | SLEEPN           |             |

| T15         | PB15D         | 4         |                  |             |

| U16         | PB16A         | 4         |                  | Т           |

| V18         | PB16B         | 4         |                  | C           |

| N13         | PB16C         | 4         |                  | T           |

| R14         | PB16D         | 4         |                  | C           |

| VCCIO4      | VCCIO4        | 4         |                  | -           |

| GND         | GNDIO4        | 4         |                  |             |

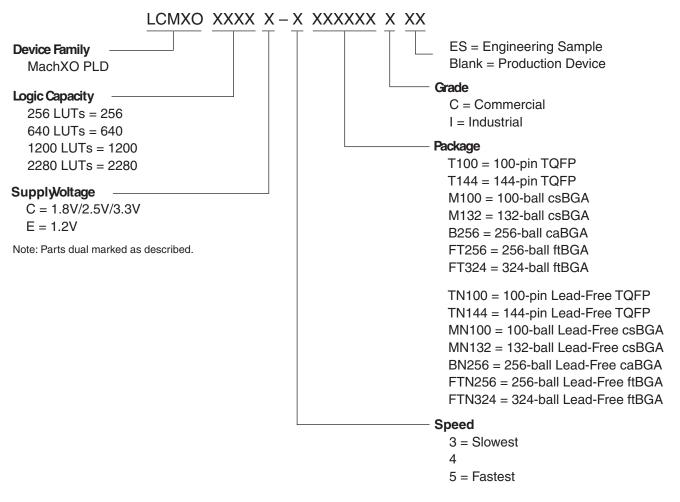

# MachXO Family Data Sheet Ordering Information

June 2013

Data Sheet DS1002

## **Part Number Description**

## **Ordering Information**

Note: MachXO devices are dual marked except the slowest commercial speed grade device.bFor example the commercial speed grade LCMXO640E-4F256C is also marked with industrial grade -3I grade.bThe slowest commercial speed grade does not have industrial markings.b The markings appears as follows:

<sup>© 2012</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## **Conventional Packaging**

| Industrial         |      |                |      |       |         |      |       |  |

|--------------------|------|----------------|------|-------|---------|------|-------|--|

| Part Number        | LUTs | Supply Voltage | I/Os | Grade | Package | Pins | Temp. |  |

| LCMXO256C-3T100I   | 256  | 1.8V/2.5V/3.3V | 78   | -3    | TQFP    | 100  | IND   |  |

| LCMXO256C-4T100I   | 256  | 1.8V/2.5V/3.3V | 78   | -4    | TQFP    | 100  | IND   |  |

| LCMXO256C-3M100I   | 256  | 1.8V/2.5V/3.3V | 78   | -3    | csBGA   | 100  | IND   |  |

| LCMXO256C-4M100I   | 256  | 1.8V/2.5V/3.3V | 78   | -4    | csBGA   | 100  | IND   |  |

| Part Number        | LUTs | Supply Voltage | I/Os | Grade | Package | Pins | Temp. |  |

| LCMXO640C-3T100I   | 640  | 1.8V/2.5V/3.3V | 74   | -3    | TQFP    | 100  | IND   |  |

| LCMXO640C-4T100I   | 640  | 1.8V/2.5V/3.3V | 74   | -4    | TQFP    | 100  | IND   |  |

| LCMXO640C-3M100I   | 640  | 1.8V/2.5V/3.3V | 74   | -3    | csBGA   | 100  | IND   |  |

| LCMXO640C-4M100I   | 640  | 1.8V/2.5V/3.3V | 74   | -4    | csBGA   | 100  | IND   |  |

| LCMXO640C-3T144I   | 640  | 1.8V/2.5V/3.3V | 113  | -3    | TQFP    | 144  | IND   |  |

| LCMXO640C-4T144I   | 640  | 1.8V/2.5V/3.3V | 113  | -4    | TQFP    | 144  | IND   |  |

| LCMXO640C-3M132I   | 640  | 1.8V/2.5V/3.3V | 101  | -3    | csBGA   | 132  | IND   |  |

| LCMXO640C-4M132I   | 640  | 1.8V/2.5V/3.3V | 101  | -4    | csBGA   | 132  | IND   |  |

| LCMXO640C-3B256I   | 640  | 1.8V/2.5V/3.3V | 159  | -3    | caBGA   | 256  | IND   |  |

| LCMXO640C-4B256I   | 640  | 1.8V/2.5V/3.3V | 159  | -4    | caBGA   | 256  | IND   |  |

| LCMX0640C-3FT256I  | 640  | 1.8V/2.5V/3.3V | 159  | -3    | ftBGA   | 256  | IND   |  |

| LCMX0640C-4FT256I  | 640  | 1.8V/2.5V/3.3V | 159  | -4    | ftBGA   | 256  | IND   |  |

|                    |      |                |      | -     |         |      |       |  |

| Part Number        | LUTs | Supply Voltage | I/Os | Grade | Package | Pins | Temp. |  |

| LCMXO1200C-3T100I  | 1200 | 1.8V/2.5V/3.3V | 73   | -3    | TQFP    | 100  | IND   |  |

| LCMXO1200C-4T100I  | 1200 | 1.8V/2.5V/3.3V | 73   | -4    | TQFP    | 100  | IND   |  |

| LCMXO1200C-3T144I  | 1200 | 1.8V/2.5V/3.3V | 113  | -3    | TQFP    | 144  | IND   |  |

| LCMXO1200C-4T144I  | 1200 | 1.8V/2.5V/3.3V | 113  | -4    | TQFP    | 144  | IND   |  |

| LCMXO1200C-3M132I  | 1200 | 1.8V/2.5V/3.3V | 101  | -3    | csBGA   | 132  | IND   |  |

| LCMXO1200C-4M132I  | 1200 | 1.8V/2.5V/3.3V | 101  | -4    | csBGA   | 132  | IND   |  |

| LCMXO1200C-3B256I  | 1200 | 1.8V/2.5V/3.3V | 211  | -3    | caBGA   | 256  | IND   |  |

| LCMXO1200C-4B256I  | 1200 | 1.8V/2.5V/3.3V | 211  | -4    | caBGA   | 256  | IND   |  |

| LCMXO1200C-3FT256I | 1200 | 1.8V/2.5V/3.3V | 211  | -3    | ftBGA   | 256  | IND   |  |

| LCMXO1200C-4FT256I | 1200 | 1.8V/2.5V/3.3V | 211  | -4    | ftBGA   | 256  | IND   |  |

| Part Number        | LUTs | Supply Voltage | I/Os | Grade | Package | Pins | Temp. |  |

| LCMXO2280C-3T100I  | 2280 | 1.8V/2.5V/3.3V | 73   | -3    | TQFP    | 100  | IND   |  |

| LCMXO2280C-4T100I  | 2280 | 1.8V/2.5V/3.3V | 73   | -4    | TQFP    | 100  | IND   |  |

| LCMXO2280C-3T144I  | 2280 | 1.8V/2.5V/3.3V | 113  | -3    | TQFP    | 144  | IND   |  |

| LCMXO2280C-4T144I  | 2280 | 1.8V/2.5V/3.3V | 113  | -4    | TQFP    | 144  | IND   |  |

| LCMXO2280C-3M132I  | 2280 | 1.8V/2.5V/3.3V | 101  | -3    | csBGA   | 132  | IND   |  |

| LCMXO2280C-4M132I  | 2280 | 1.8V/2.5V/3.3V | 101  | -4    | csBGA   | 132  | IND   |  |

| LCMXO2280C-3B256I  | 2280 | 1.8V/2.5V/3.3V | 211  | -3    | caBGA   | 256  | IND   |  |

| LCMXO2280C-4B256I  | 2280 | 1.8V/2.5V/3.3V | 211  | -4    | caBGA   | 256  | IND   |  |

| LCMXO2280C-3FT256I | 2280 | 1.8V/2.5V/3.3V | 211  | -3    | ftBGA   | 256  | IND   |  |

| LCMXO2280C-4FT256I | 2280 | 1.8V/2.5V/3.3V | 211  | -4    | ftBGA   | 256  | IND   |  |

| LCMX02280C-3FT324I | 2280 | 1.8V/2.5V/3.3V | 271  | -3    | ftBGA   | 324  | IND   |  |

|                    |      |                |      |       |         |      |       |  |

| LCMXO2280C-4FT324I | 2280 | 1.8V/2.5V/3.3V | 271  | -4    | ftBGA   | 324  | IND   |  |

| Part Number         | LUTs | Supply Voltage | l/Os | Grade | Package         | Pins | Temp. |

|---------------------|------|----------------|------|-------|-----------------|------|-------|

| LCMXO1200E-3TN100C  | 1200 | 1.2V           | 73   | -3    | Lead-Free TQFP  | 100  | COM   |

| LCMXO1200E-4TN100C  | 1200 | 1.2V           | 73   | -4    | Lead-Free TQFP  | 100  | COM   |

| LCMXO1200E-5TN100C  | 1200 | 1.2V           | 73   | -5    | Lead-Free TQFP  | 100  | COM   |

| LCMXO1200E-3TN144C  | 1200 | 1.2V           | 113  | -3    | Lead-Free TQFP  | 144  | COM   |

| LCMXO1200E-4TN144C  | 1200 | 1.2V           | 113  | -4    | Lead-Free TQFP  | 144  | COM   |

| LCMXO1200E-5TN144C  | 1200 | 1.2V           | 113  | -5    | Lead-Free TQFP  | 144  | COM   |

| LCMXO1200E-3MN132C  | 1200 | 1.2V           | 101  | -3    | Lead-Free csBGA | 132  | COM   |

| LCMXO1200E-4MN132C  | 1200 | 1.2V           | 101  | -4    | Lead-Free csBGA | 132  | COM   |

| LCMXO1200E-5MN132C  | 1200 | 1.2V           | 101  | -5    | Lead-Free csBGA | 132  | COM   |

| LCMXO1200E-3BN256C  | 1200 | 1.2V           | 211  | -3    | Lead-Free caBGA | 256  | COM   |

| LCMXO1200E-4BN256C  | 1200 | 1.2V           | 211  | -4    | Lead-Free caBGA | 256  | COM   |

| LCMXO1200E-5BN256C  | 1200 | 1.2V           | 211  | -5    | Lead-Free caBGA | 256  | COM   |

| LCMXO1200E-3FTN256C | 1200 | 1.2V           | 211  | -3    | Lead-Free ftBGA | 256  | COM   |

| LCMXO1200E-4FTN256C | 1200 | 1.2V           | 211  | -4    | Lead-Free ftBGA | 256  | COM   |

| LCMXO1200E-5FTN256C | 1200 | 1.2V           | 211  | -5    | Lead-Free ftBGA | 256  | COM   |

| Part Number         | LUTs | Supply Voltage | I/Os | Grade | Package         | Pins | Temp. |

|---------------------|------|----------------|------|-------|-----------------|------|-------|

| LCMXO2280E-3TN100C  | 2280 | 1.2V           | 73   | -3    | Lead-Free TQFP  | 100  | COM   |

| LCMXO2280E-4TN100C  | 2280 | 1.2V           | 73   | -4    | Lead-Free TQFP  | 100  | COM   |

| LCMXO2280E-5TN100C  | 2280 | 1.2V           | 73   | -5    | Lead-Free TQFP  | 100  | COM   |

| LCMXO2280E-3TN144C  | 2280 | 1.2V           | 113  | -3    | Lead-Free TQFP  | 144  | COM   |

| LCMXO2280E-4TN144C  | 2280 | 1.2V           | 113  | -4    | Lead-Free TQFP  | 144  | COM   |

| LCMXO2280E-5TN144C  | 2280 | 1.2V           | 113  | -5    | Lead-Free TQFP  | 144  | COM   |

| LCMXO2280E-3MN132C  | 2280 | 1.2V           | 101  | -3    | Lead-Free csBGA | 132  | COM   |

| LCMXO2280E-4MN132C  | 2280 | 1.2V           | 101  | -4    | Lead-Free csBGA | 132  | COM   |

| LCMXO2280E-5MN132C  | 2280 | 1.2V           | 101  | -5    | Lead-Free csBGA | 132  | COM   |

| LCMXO2280E-3BN256C  | 2280 | 1.2V           | 211  | -3    | Lead-Free caBGA | 256  | COM   |

| LCMXO2280E-4BN256C  | 2280 | 1.2V           | 211  | -4    | Lead-Free caBGA | 256  | COM   |

| LCMXO2280E-5BN256C  | 2280 | 1.2V           | 211  | -5    | Lead-Free caBGA | 256  | COM   |

| LCMXO2280E-3FTN256C | 2280 | 1.2V           | 211  | -3    | Lead-Free ftBGA | 256  | COM   |

| LCMXO2280E-4FTN256C | 2280 | 1.2V           | 211  | -4    | Lead-Free ftBGA | 256  | COM   |

| LCMXO2280E-5FTN256C | 2280 | 1.2V           | 211  | -5    | Lead-Free ftBGA | 256  | COM   |

| LCMXO2280E-3FTN324C | 2280 | 1.2V           | 271  | -3    | Lead-Free ftBGA | 324  | COM   |

| LCMXO2280E-4FTN324C | 2280 | 1.2V           | 271  | -4    | Lead-Free ftBGA | 324  | COM   |

| LCMXO2280E-5FTN324C | 2280 | 1.2V           | 271  | -5    | Lead-Free ftBGA | 324  | COM   |