Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                    |

| Number of LABs/CLBs            | 32                                                                          |

| Number of Logic Elements/Cells | 256                                                                         |

| Total RAM Bits                 | -                                                                           |

| Number of I/O                  | 78                                                                          |

| Number of Gates                | -                                                                           |

| Voltage - Supply               | 1.71V ~ 3.465V                                                              |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                             |

| Package / Case                 | 100-LFBGA, CSPBGA                                                           |

| Supplier Device Package        | 100-CSBGA (8x8)                                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lcmxo256c-5m100c |

|                                |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The ispLEVER design tool takes the output of the synthesis tool and places and routes the design. Generally, the place and route tool is completely automatic, although an interactive routing editor is available to optimize the design.

## **Clock/Control Distribution Network**

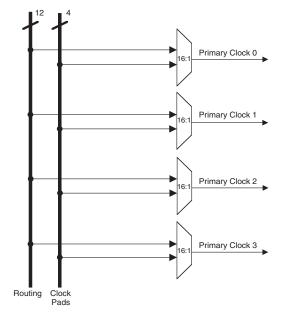

The MachXO family of devices provides global signals that are available to all PFUs. These signals consist of four primary clocks and four secondary clocks. Primary clock signals are generated from four 16:1 muxes as shown in Figure 2-7 and Figure 2-8. The available clock sources for the MachXO256 and MachXO640 devices are four dual function clock pins and 12 internal routing signals. The available clock sources for the MachXO2280 devices are four dual function clock pins, up to nine internal routing signals and up to six PLL outputs.

#### Figure 2-7. Primary Clocks for MachXO256 and MachXO640 Devices

#### Table 2-5. PLL Signal Descriptions

| Signal       | I/O | Description                                                                                                 |

|--------------|-----|-------------------------------------------------------------------------------------------------------------|

| CLKI         | I   | Clock input from external pin or routing                                                                    |

| CLKFB        | I   | PLL feedback input from PLL output, clock net, routing/external pin or internal feedback from CLKINTFB port |

| RST          | I   | "1" to reset the input clock divider                                                                        |

| CLKOS        | 0   | PLL output clock to clock tree (phase shifted/duty cycle changed)                                           |

| CLKOP        | 0   | PLL output clock to clock tree (No phase shift)                                                             |

| CLKOK        | 0   | PLL output to clock tree through secondary clock divider                                                    |

| LOCK         | 0   | "1" indicates PLL LOCK to CLKI                                                                              |

| CLKINTFB     | 0   | Internal feedback source, CLKOP divider output before CLOCKTREE                                             |

| DDAMODE      | I   | Dynamic Delay Enable. "1": Pin control (dynamic), "0": Fuse Control (static)                                |

| DDAIZR       | I   | Dynamic Delay Zero. "1": delay = 0, "0": delay = on                                                         |

| DDAILAG      | I   | Dynamic Delay Lag/Lead. "1": Lag, "0": Lead                                                                 |

| DDAIDEL[2:0] | I   | Dynamic Delay Input                                                                                         |

For more information on the PLL, please see details of additional technical documentation at the end of this data sheet.

## sysMEM Memory

The MachXO1200 and MachXO2280 devices contain sysMEM Embedded Block RAMs (EBRs). The EBR consists of a 9-Kbit RAM, with dedicated input and output registers.

#### sysMEM Memory Block

The sysMEM block can implement single port, dual port, pseudo dual port, or FIFO memories. Each block can be used in a variety of depths and widths as shown in Table 2-6.

#### Table 2-6. sysMEM Block Configurations

| Memory Mode      | Configurations                                                           |

|------------------|--------------------------------------------------------------------------|

| Single Port      | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18<br>256 x 36 |

| True Dual Port   | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18             |

| Pseudo Dual Port | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18<br>256 x 36 |

| FIFO             | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18<br>256 x 36 |

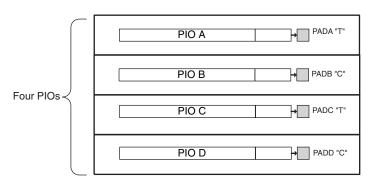

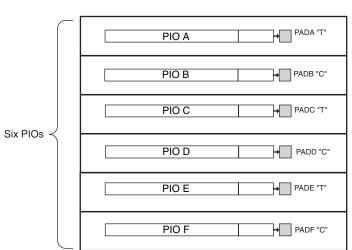

## **PIO Groups**

On the MachXO devices, PIO cells are assembled into two different types of PIO groups, those with four PIO cells and those with six PIO cells. PIO groups with four IOs are placed on the left and right sides of the device while PIO groups with six IOs are placed on the top and bottom. The individual PIO cells are connected to their respective sysIO buffers and PADs.

On all MachXO devices, two adjacent PIOs can be joined to provide a complementary Output driver pair. The I/O pin pairs are labeled as "T" and "C" to distinguish between the true and complement pins.

The MachXO1200 and MachXO2280 devices contain enhanced I/O capability. All PIO pairs on these larger devices can implement differential receivers. In addition, half of the PIO pairs on the left and right sides of these devices can be configured as LVDS transmit/receive pairs. PIOs on the top of these larger devices also provide PCI support.

#### Figure 2-15. Group of Four Programmable I/O Cells

This structure is used on the left and right of MachXO devices

Figure 2-16. Group of Six Programmable I/O Cells

# This structure is used on the top and bottom of MachXO devices $\label{eq:machine}$

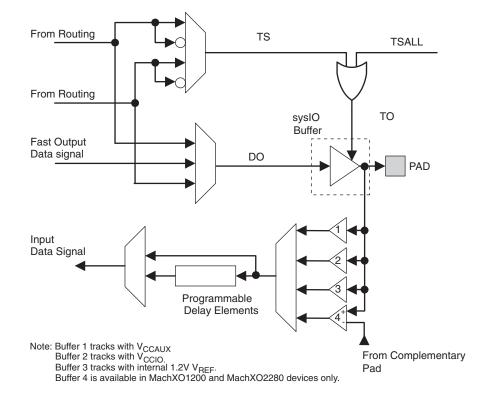

## PIO

The PIO blocks provide the interface between the sysIO buffers and the internal PFU array blocks. These blocks receive output data from the PFU array and a fast output data signal from adjacent PFUs. The output data and fast

output data signals are multiplexed and provide a single signal to the I/O pin via the sysIO buffer. Figure 2-17 shows the MachXO PIO logic.

The tristate control signal is multiplexed from the output data signals and their complements. In addition a global signal (TSALL) from a dedicated pad can be used to tristate the sysIO buffer.

The PIO receives an input signal from the pin via the sysIO buffer and provides this signal to the core of the device. In addition there are programmable elements that can be utilized by the design tools to avoid positive hold times.

#### Figure 2-17. MachXO PIO Block Diagram

## sysIO Buffer

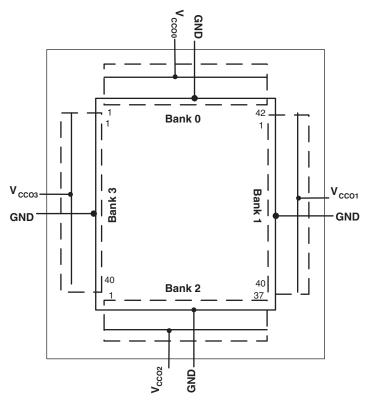

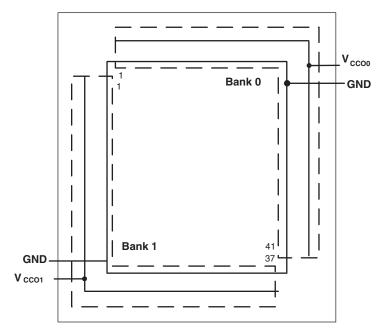

Each I/O is associated with a flexible buffer referred to as a sysIO buffer. These buffers are arranged around the periphery of the device in groups referred to as Banks. The sysIO buffers allow users to implement the wide variety of standards that are found in today's systems including LVCMOS, TTL, BLVDS, LVDS and LVPECL.

In the MachXO devices, single-ended output buffers and ratioed input buffers (LVTTL, LVCMOS and PCI) are powered using  $V_{CCIO}$ . In addition to the Bank  $V_{CCIO}$  supplies, the MachXO devices have a  $V_{CC}$  core logic power supply, and a  $V_{CCAUX}$  supply that powers up a variety of internal circuits including all the differential and referenced input buffers.

MachXO256 and MachXO640 devices contain single-ended input buffers and single-ended output buffers with complementary outputs on all the I/O Banks.

MachXO1200 and MachXO2280 devices contain two types of sysIO buffer pairs.

#### 1. Top and Bottom sysIO Buffer Pairs

The sysIO buffer pairs in the top and bottom Banks of the device consist of two single-ended output drivers and two sets of single-ended input buffers (for ratioed or absolute input levels). The I/O pairs on the top and bottom

#### Table 2-8. I/O Support Device by Device

|                                             | MachXO256                                                             | MachXO640                                                             | MachXO1200                                                                     | MachXO2280                                                                     |

|---------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Number of I/O Banks                         | 2                                                                     | 4                                                                     | 8                                                                              | 8                                                                              |

| Type of Input Buffers                       | Single-ended<br>(all I/O Banks)                                       | Single-ended<br>(all I/O Banks)                                       | Single-ended<br>(all I/O Banks)<br>Differential Receivers                      | Single-ended<br>(all I/O Banks)<br>Differential Receivers                      |

|                                             |                                                                       |                                                                       | (all I/O Banks)                                                                | (all I/O Banks)                                                                |

| Types of Output Buffers                     | Single-ended buffers<br>with complementary<br>outputs (all I/O Banks) | Single-ended buffers<br>with complementary<br>outputs (all I/O Banks) | Single-ended buffers<br>with complementary<br>outputs (all I/O Banks)          | Single-ended buffers<br>with complementary<br>outputs (all I/O Banks)          |

|                                             |                                                                       |                                                                       | Differential buffers with<br>true LVDS outputs (50%<br>on left and right side) | Differential buffers with<br>true LVDS outputs (50%<br>on left and right side) |

| Differential Output<br>Emulation Capability | All I/O Banks                                                         | All I/O Banks                                                         | All I/O Banks                                                                  | All I/O Banks                                                                  |

| PCI Support                                 | No                                                                    | No                                                                    | Top side only                                                                  | Top side only                                                                  |

#### Table 2-9. Supported Input Standards

|                                                                                  | VCCIO (Typ.) |      |      |      |      |  |

|----------------------------------------------------------------------------------|--------------|------|------|------|------|--|

| Input Standard                                                                   | 3.3V         | 2.5V | 1.8V | 1.5V | 1.2V |  |

| Single Ended Interfaces                                                          |              |      |      |      |      |  |

| LVTTL                                                                            | Yes          | Yes  | Yes  | Yes  | Yes  |  |

| LVCMOS33                                                                         | Yes          | Yes  | Yes  | Yes  | Yes  |  |

| LVCMOS25                                                                         | Yes          | Yes  | Yes  | Yes  | Yes  |  |

| LVCMOS18                                                                         |              |      | Yes  |      |      |  |

| LVCMOS15                                                                         |              |      |      | Yes  |      |  |

| LVCMOS12                                                                         | Yes          | Yes  | Yes  | Yes  | Yes  |  |

| PCI <sup>1</sup>                                                                 | Yes          |      |      |      |      |  |

| Differential Interfaces                                                          | •            | •    | •    | •    |      |  |

| BLVDS <sup>2</sup> , LVDS <sup>2</sup> , LVPECL <sup>2</sup> , RSDS <sup>2</sup> | Yes          | Yes  | Yes  | Yes  | Yes  |  |

Top Banks of MachXO1200 and MachXO2280 devices only.

MachXO1200 and MachXO2280 devices only.

#### Figure 2-20. MachXO640 Banks

Figure 2-21. MachXO256 Banks

## **Hot Socketing**

The MachXO devices have been carefully designed to ensure predictable behavior during power-up and powerdown. Leakage into I/O pins is controlled to within specified limits. This allows for easy integration with the rest of

# Initialization Supply Current<sup>1, 2, 3, 4</sup>

#### **Over Recommended Operating Conditions**

| Symbol             | Parameter                      | Device       | Typ.⁵ | Units |

|--------------------|--------------------------------|--------------|-------|-------|

|                    |                                | LCMXO256C    |       | mA    |

|                    |                                | LCMXO640C    | 17    | mA    |

|                    |                                | LCMXO1200C   | 21    | mA    |

|                    | Core Power Supply              | LCMXO2280C   | 23    | mA    |

| ICC                | Core Power Supply              | LCMXO256E    | 10    | mA    |

|                    |                                | LCMXO640E    | 14    | mA    |

|                    |                                | LCMXO1200E   | 18    | mA    |

|                    |                                | LCMXO2280E   | 20    | mA    |

| I <sub>CCAUX</sub> |                                | LCMXO256E/C  | 10    | mA    |

|                    | Auxiliary Power Supply         | LCMXO640E/C  | 13    | mA    |

|                    | $V_{CCAUX} = 3.3V$             | LCMXO1200E/C | 24    | mA    |

|                    |                                | LCMXO2280E/C | 25    | mA    |

| ICCIO              | Bank Power Supply <sup>6</sup> | All devices  | 2     | mA    |

1. For further information on supply current, please see details of additional technical documentation at the end of this data sheet.

2. Assumes all I/O pins are held at  $V_{CCIO}$  or GND.

3. Frequency = 0MHz.

4. Typical user pattern.

5.  $T_J = 25^{\circ}$ C, power supplies at nominal voltage.

6. Per Bank, V<sub>CCIO</sub> = 2.5V. Does not include pull-up/pull-down.

# Programming and Erase Flash Supply Current<sup>1, 2, 3, 4</sup>

| Symbol            | Parameter                      | Device                                                                                                                                                                                                                                                                                     | Typ.⁵ | Units |

|-------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|

|                   |                                | LCMXO256C                                                                                                                                                                                                                                                                                  | 9     | mA    |

|                   |                                | LCMXO640C                                                                                                                                                                                                                                                                                  | 11    | mA    |

|                   |                                | LCMXO1200C                                                                                                                                                                                                                                                                                 | 16    | mA    |

| 1                 | Core Power Supply              | LCMXO2280C                                                                                                                                                                                                                                                                                 | 22    | mA    |

| ICC               | Core Power Supply              | LCMXO256E                                                                                                                                                                                                                                                                                  | 6     | mA    |

|                   |                                | LCMXO640E                                                                                                                                                                                                                                                                                  | 8     | mA    |

|                   |                                | LCMXO1200E                                                                                                                                                                                                                                                                                 | 12    | mA    |

|                   |                                | LCMXO2280E                                                                                                                                                                                                                                                                                 | 14    | mA    |

|                   |                                | LCMXO256C       LCMXO640C       LCMXO1200C       LCMXO256E       LCMXO256E       LCMXO640E       LCMXO1200E       LCMXO2280E       LCMXO256C/E       LCMXO280E       LCMXO256C/E       LCMXO2280E       LCMXO256C/E       LCMXO256C/E       LCMXO40C/E       LCMXO1200/E       LCMXO1200/E | 8     | mA    |

| ICCAUX            | Auxiliary Power Supply         | LCMXO640C/E                                                                                                                                                                                                                                                                                | 10    | mA    |

|                   | $V_{CCAUX} = 3.3V$             | LCMXO1200/E                                                                                                                                                                                                                                                                                | 15    | mA    |

|                   |                                | LCMXO2280C/E                                                                                                                                                                                                                                                                               | 16    | mA    |

| I <sub>CCIO</sub> | Bank Power Supply <sup>6</sup> | All devices                                                                                                                                                                                                                                                                                | 2     | mA    |

1. For further information on supply current, please see details of additional technical documentation at the end of this data sheet.

2. Assumes all I/O pins are held at  $V_{CCIO}$  or GND.

3. Typical user pattern.

4. JTAG programming is at 25MHz.

5.  $T_J = 25^{\circ}C$ , power supplies at nominal voltage.

6. Per Bank. V<sub>CCIO</sub> = 2.5V. Does not include pull-up/pull-down.

# **Typical Building Block Function Performance<sup>1</sup>**

## Pin-to-Pin Performance (LVCMOS25 12mA Drive)

| Function        | -5 Timing | Units |

|-----------------|-----------|-------|

| Basic Functions |           |       |

| 16-bit decoder  | 6.7       | ns    |

| 4:1 MUX         | 4.5       | ns    |

| 16:1 MUX        | 5.1       | ns    |

#### **Register-to-Register Performance**

| Function                        | -5 Timing                | Units |

|---------------------------------|--------------------------|-------|

| Basic Functions                 |                          |       |

| 16:1 MUX                        | 487                      | MHz   |

| 16-bit adder                    | 292                      | MHz   |

| 16-bit counter                  | 388                      | MHz   |

| 64-bit counter                  | 200                      | MHz   |

| Embedded Memory Functions (1200 | 0 and 2280 Devices Only) |       |

| 256x36 Single Port RAM          | 284                      | MHz   |

| 512x18 True-Dual Port RAM       | 284                      | MHz   |

| Distributed Memory Functions    |                          |       |

| 16x2 Single Port RAM            | 434                      | MHz   |

| 64x2 Single Port RAM            | 320                      | MHz   |

| 128x4 Single Port RAM           | 261                      | MHz   |

| 32x2 Pseudo-Dual Port RAM       | 314                      | MHz   |

| 64x4 Pseudo-Dual Port RAM       | 271                      | MHz   |

The above timing numbers are generated using the ispLEVER design tool. Exact performance may vary with device and tool version. The tool uses internal parameters that have been characterized but are not tested on every device.

Rev. A 0.19

# **Derating Logic Timing**

Logic Timing provided in the following sections of the data sheet and the ispLEVER design tools are worst case numbers in the operating range. Actual delays may be much faster. The ispLEVER design tool from Lattice can provide logic timing numbers at a particular temperature and voltage.

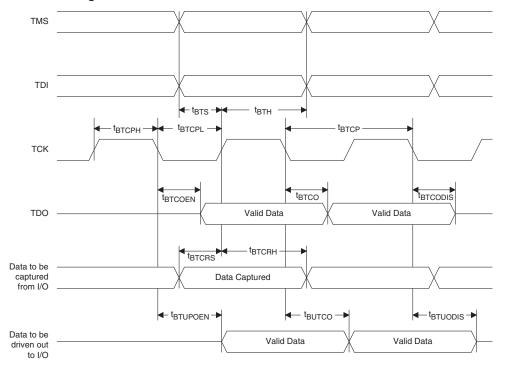

Figure 3-5. JTAG Port Timing Waveforms

# MachXO Family Data Sheet Pinout Information

June 2013

Data Sheet DS1002

## **Signal Descriptions**

| Signal Name                   | I/O     | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|-------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| General Purpose               |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                               |         | [Edge] indicates the edge of the device on which the pad is located. Valid edge designa-<br>tions are L (Left), B (Bottom), R (Right), T (Top).                                                                                                                                                                                                                                                                                                    |  |  |  |

|                               |         | [Row/Column Number] indicates the PFU row or the column of the device on which the PIO Group exists. When Edge is T (Top) or (Bottom), only need to specify Row Number. When Edge is L (Left) or R (Right), only need to specify Column Number.                                                                                                                                                                                                    |  |  |  |

| P[Edge] [Row/Column           | I/O     | [A/B/C/D/E/F] indicates the PIO within the group to which the pad is connected.                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| Number]_[A/B/C/D/E/F]         |         | Some of these user programmable pins are shared with special function pins. When not used as special function pins, these pins can be programmed as I/Os for user logic.                                                                                                                                                                                                                                                                           |  |  |  |

|                               |         | During configuration of the user-programmable I/Os, the user has an option to tri-state the I/Os and enable an internal pull-up resistor. This option also applies to unused pins (or those not bonded to a package pin). The default during configuration is for user-programmable I/Os to be tri-stated with an internal pull-up resistor enabled. When the device is erased, I/Os will be tri-stated with an internal pull-up resistor enabled. |  |  |  |

| GSRN                          | I       | Global RESET signal (active low). Dedicated pad, when not in use it can be used as an I/O pin.                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| TSALL                         | I       | TSALL is a dedicated pad for the global output enable signal. When TSALL is high all the outputs are tristated. It is a dual function pin. When not in use, it can be used as an I/O pin.                                                                                                                                                                                                                                                          |  |  |  |

| NC                            | —       | No connect.                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| GND                           | —       | GND - Ground. Dedicated pins.                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| V <sub>CC</sub>               | —       | VCC - The power supply pins for core logic. Dedicated pins.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| V <sub>CCAUX</sub>            | _       | VCCAUX - the Auxiliary power supply pin. This pin powers up a variety of internal circuits including all the differential and referenced input buffers. Dedicated pins.                                                                                                                                                                                                                                                                            |  |  |  |

| V <sub>CCIOx</sub>            | —       | V <sub>CCIO</sub> - The power supply pins for I/O Bank x. Dedicated pins.                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| SLEEPN <sup>1</sup>           | I       | Sleep Mode pin - Active low sleep pin.b When this pin is held high, the device operates normally.b This pin has a weak internal pull-up, but when unused, an external pull-up to $V_{CC}$ is recommended. When driven low, the device moves into Sleep mode after a specified time.                                                                                                                                                                |  |  |  |

| PLL and Clock Functions       | (Used a | as user programmable I/O pins when not used for PLL or clock pins)                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| [LOC][0]_PLL[T, C]_IN         | _       | Reference clock (PLL) input Pads: [LOC] indicates location. Valid designations are ULM (Upper PLL) and LLM (Lower PLL). $T = true$ and $C = complement$ .                                                                                                                                                                                                                                                                                          |  |  |  |

| [LOC][0]_PLL[T, C]_FB         |         | Optional feedback (PLL) input Pads: [LOC] indicates location. Valid designations are ULM (Upper PLL) and LLM (Lower PLL). T = true and C = complement.                                                                                                                                                                                                                                                                                             |  |  |  |

| PCLK [n]_[1:0]                | —       | Primary Clock Pads, n per side.                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| Test and Programming (De      | dicate  | d pins)                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| TMS                           | I       | Test Mode Select input pin, used to control the 1149.1 state machine.                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| ТСК                           | Ι       | Test Clock input pin, used to clock the 1149.1 state machine.                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| TDI                           | I       | Test Data input pin, used to load data into the device using an 1149.1 state machine.                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| TDO                           | 0       | Output pin -Test Data output pin used to shift data out of the device using 1149.1.                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 1 Applies to MachXO "C" devic |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

1. Applies to MachXO "C" devices only. NC for "E" devices.

<sup>© 2013</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# **Power Supply and NC**

| Signal           | 100 TQFP <sup>1</sup>                                                                                                                                   | 144 TQFP <sup>1</sup>                                | 100 csBGA <sup>2</sup>                                                                                    |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| VCC              | LCMXO256/640: 35, 90<br>LCMXO1200/2280: 17, 35, 66, 91                                                                                                  | 21, 52, 93, 129                                      | P7, B6                                                                                                    |

| VCCIO0           | LCMXO256: 60, 74, 92<br>LCMXO640: 80, 92<br>LCMXO1200/2280: 94                                                                                          | LCMXO640: 117, 135<br>LCMXO1200/2280: 135            | LCMXO256: H14, A14, B5<br>LCMXO640: B12, B5                                                               |

| VCCIO1           | LCMXO256: 10, 24, 41<br>LCMXO640: 60, 74<br>LCMXO1200/2280: 80                                                                                          | LCMXO640: 82, 98<br>LCMXO1200/2280: 117              | LCMXO256: G1, P1, P10<br>LCMXO640: H14, A14                                                               |

| VCCIO2           | LCMXO256: None<br>LCMXO640: 29, 41<br>LCMXO1200/2280: 70                                                                                                | LCMXO640: 38, 63<br>LCMXO1200/2280: 98               | LCMXO256: None<br>LCMXO640: P4, P10                                                                       |

| VCCIO3           | LCMXO256: None<br>LCMXO640: 10, 24<br>LCMXO1200/2280: 56                                                                                                | LCMXO640: 10, 26<br>LCMXO1200/2280: 82               | LCMXO256: None<br>LCMXO640: G1, P1                                                                        |

| VCCIO4           | LCMXO256/640: None<br>LCMXO1200/2280: 44                                                                                                                | LCMXO640: None<br>LCMXO1200/2280: 63                 | -                                                                                                         |

| VCCIO5           | LCMXO256/640: None<br>LCMXO1200/2280: 27                                                                                                                | LCMXO640: None<br>LCMXO1200/2280: 38                 | —                                                                                                         |

| VCCIO6           | LCMXO256/640: None<br>LCMXO1200/2280: 20                                                                                                                | LCMXO640: None<br>LCMXO1200/2280: 26                 | —                                                                                                         |

| VCCIO7           | LCMXO256/640: None<br>LCMXO1200/2280: 6                                                                                                                 | LCMXO640: None<br>LCMXO1200/2280: 10                 | —                                                                                                         |

| VCCAUX           | LCMXO256/640: 88<br>LCMXO1200/2280: 36, 90                                                                                                              | 53, 128                                              | B7                                                                                                        |

| GND <sup>3</sup> | LCMXO256: 40, 84, 62, 75, 93, 12,<br>25, 42<br>LCMXO640: 40, 84, 81, 93, 62, 75,<br>30, 42, 12, 25<br>LCMXO1200/2280: 9, 41, 59, 83,<br>100, 76, 50, 26 | 16, 59, 88, 123, 118, 136, 83, 99,<br>37, 64, 11, 27 | LCMXO256: N9, B9, G14, B13,<br>A4, H1, N2, N10<br>LCMXO640: N9, B9, A10, A4,<br>G14, B13, N3, N10, H1, N2 |

| NC <sup>4</sup>  |                                                                                                                                                         |                                                      | —                                                                                                         |

1. Pin orientation follows the conventional order from pin 1 marking of the top side view and counter-clockwise.

Pin orientation follows the contention of the top side view with alphabetical order ascending vertically and numerical order ascending horizontally.

All grounds must be electrically connected at the board level. For fpBGA and ftBGA packages, the total number of GND balls is less than the actual number of GND logic connections from the die to the common package GND plane.

NC pins should not be connected to any active signals, VCC or GND.

# LCMXO256 and LCMXO640 Logic Signal Connections: 100 TQFP (Cont.)

|            |                  | LCM  | XO256            |              | LCMXO640         |      |                  |              |

|------------|------------------|------|------------------|--------------|------------------|------|------------------|--------------|

| Pin Number | Ball<br>Function | Bank | Dual<br>Function | Differential | Ball<br>Function | Bank | Dual<br>Function | Differential |

| 43         | PB4A             | 1    |                  | Т            | PB8B             | 2    |                  |              |

| 44         | PB4B             | 1    |                  | С            | PB8C             | 2    |                  | Т            |

| 45         | PB4C             | 1    |                  | T            | PB8D             | 2    |                  | C            |

| 46         | PB4D             | 1    |                  | C            | PB9A             | 2    |                  |              |

| 47         | PB5A             | 1    |                  |              | PB9C             | 2    |                  | Т            |

| 48*        | SLEEPN           | -    | SLEEPN           |              | SLEEPN           | -    | SLEEPN           |              |

| 49         | PB5C             | 1    |                  | Т            | PB9D             | 2    |                  | С            |

| 50         | PB5D             | 1    |                  | C            | PB9F             | 2    |                  | -            |

| 51         | PR9B             | 0    |                  | C            | PR11D            | 1    |                  | С            |

| 52         | PR9A             | 0    |                  | T            | PR11B            | 1    |                  | C            |

| 53         | PR8B             | 0    |                  | C            | PR11C            | 1    |                  | T            |

| 54         | PR8A             | 0    |                  | T            | PR11A            | 1    |                  | T            |

| 55         | PR7D             | 0    |                  | C            | PR10D            | 1    |                  | C            |

| 56         | PR7C             | 0    |                  | Т            | PR10C            | 1    |                  | Т            |

| 57         | PR7B             | 0    |                  | C            | PR10B            | 1    |                  | C            |

| 58         | PR7A             | 0    |                  | Т            | PR10A            | 1    |                  | Т            |

| 59         | PR6B             | 0    |                  | C            | PR9D             | 1    |                  |              |

| 60         | VCCIO0           | 0    |                  | C            | VCCIO1           | 1    |                  |              |

| 61         | PR6A             | 0    |                  | Т            | PR9B             | 1    |                  |              |

|            |                  |      |                  | I            |                  |      |                  |              |

| 62         | GNDIO0           | 0    |                  |              | GNDIO1           | 1    |                  |              |

| 63         | PR5D             | 0    |                  | C            | PR7B             | 1    |                  |              |

| 64         | PR5C             | 0    |                  | Т            | PR6C             | 1    |                  |              |

| 65         | PR5B             | 0    |                  | C            | PR6B             | 1    |                  |              |

| 66         | PR5A             | 0    |                  | Т            | PR5D             | 1    |                  |              |

| 67         | PR4B             | 0    |                  | С            | PR5B             | 1    |                  |              |

| 68         | PR4A             | 0    |                  | Т            | PR4D             | 1    |                  |              |

| 69         | PR3D             | 0    |                  | С            | PR4B             | 1    |                  |              |

| 70         | PR3C             | 0    |                  | Т            | PR3D             | 1    |                  |              |

| 71         | PR3B             | 0    |                  | С            | PR3B             | 1    |                  |              |

| 72         | PR3A             | 0    |                  | Т            | PR2D             | 1    |                  |              |

| 73         | PR2B             | 0    |                  | С            | PR2B             | 1    |                  |              |

| 74         | VCCIO0           | 0    |                  |              | VCCIO1           | 1    |                  |              |

| 75         | GNDIO0           | 0    |                  |              | GNDIO1           | 1    |                  |              |

| 76         | PR2A             | 0    |                  | Т            | PT9F             | 0    |                  | С            |

| 77         | PT5C             | 0    |                  |              | PT9E             | 0    |                  | Т            |

| 78         | PT5B             | 0    |                  | С            | PT9C             | 0    |                  |              |

| 79         | PT5A             | 0    |                  | Т            | PT9A             | 0    |                  |              |

| 80         | PT4F             | 0    |                  | С            | VCCIO0           | 0    |                  |              |

| 81         | PT4E             | 0    |                  | Т            | GNDIO0           | 0    |                  |              |

| 82         | PT4D             | 0    |                  | С            | PT7E             | 0    |                  |              |

| 83         | PT4C             | 0    |                  | Т            | PT7A             | 0    |                  |              |

| 84         | GND              | -    | 1                |              | GND              | -    |                  |              |

# LCMXO1200 and LCMXO2280 Logic Signal Connections: 100 TQFP (Cont.)

|               |                  | I    | CMXO1200         |              | LCMXO2280        |      |                  |              |  |  |  |

|---------------|------------------|------|------------------|--------------|------------------|------|------------------|--------------|--|--|--|

| Pin<br>Number | Ball<br>Function | Bank | Dual<br>Function | Differential | Ball<br>Function | Bank | Dual<br>Function | Differential |  |  |  |

| 82            | PT9A             | 1    |                  |              | PT12C            | 1    |                  | Т            |  |  |  |

| 83            | GND              | -    |                  |              | GND              | -    |                  |              |  |  |  |

| 84            | PT8B             | 1    |                  | С            | PT11B            | 1    |                  | С            |  |  |  |

| 85            | PT8A             | 1    |                  | Т            | PT11A            | 1    |                  | Т            |  |  |  |

| 86            | PT7D             | 1    | PCLK1_1****      |              | PT10B            | 1    | PCLK1_1****      |              |  |  |  |

| 87            | PT6F             | 0    | PCLK0_0****      |              | PT9B             | 1    | PCLK1_0****      |              |  |  |  |

| 88            | PT6D             | 0    |                  | С            | PT8F             | 0    |                  | С            |  |  |  |

| 89            | PT6C             | 0    |                  | Т            | PT8E             | 0    |                  | Т            |  |  |  |

| 90            | VCCAUX           | -    |                  |              | VCCAUX           | -    |                  |              |  |  |  |

| 91            | VCC              | -    |                  |              | VCC              | -    |                  |              |  |  |  |

| 92            | PT5B             | 0    |                  |              | PT6D             | 0    |                  |              |  |  |  |

| 93            | PT4B             | 0    |                  |              | PT6F             | 0    |                  |              |  |  |  |

| 94            | VCCIO0           | 0    |                  |              | VCCIO0           | 0    |                  |              |  |  |  |

| 95            | PT3D             | 0    |                  | С            | PT4B             | 0    |                  | С            |  |  |  |

| 96            | PT3C             | 0    |                  | Т            | PT4A             | 0    |                  | Т            |  |  |  |

| 97            | PT3B             | 0    |                  |              | PT3B             | 0    |                  |              |  |  |  |

| 98            | PT2B             | 0    |                  | С            | PT2B             | 0    |                  | С            |  |  |  |

| 99            | PT2A             | 0    |                  | Т            | PT2A             | 0    |                  | Т            |  |  |  |

| 100**         | GNDIO0<br>GNDIO7 | -    |                  |              | GNDIO0<br>GNDIO7 | -    |                  |              |  |  |  |

\*Supports true LVDS outputs.

\*\*Double bonded to the pin.

\*\*\*NC for "E" devices.

\*\*\*\*Primary clock inputs are single-ended.

# LCMXO256 and LCMXO640 Logic Signal Connections: 100 csBGA (Cont.)

|                |                  | LCMXO256 | 6                |                   | LCMXO640       |                  |      |                  |                   |  |  |  |

|----------------|------------------|----------|------------------|-------------------|----------------|------------------|------|------------------|-------------------|--|--|--|

| Ball<br>Number | Ball<br>Function | Bank     | Dual<br>Function | Differen-<br>tial | Ball<br>Number | Ball<br>Function | Bank | Dual<br>Function | Differen-<br>tial |  |  |  |

| P13            | PB5A             | 1        |                  |                   | P13            | PB9C             | 2    |                  | Т                 |  |  |  |

| M12*           | SLEEPN           | -        | SLEEPN           |                   | M12*           | SLEEPN           | -    | SLEEPN           |                   |  |  |  |

| P14            | PB5C             | 1        |                  | Т                 | P14            | PB9D             | 2    |                  | С                 |  |  |  |

| N13            | PB5D             | 1        |                  | С                 | N13            | PB9F             | 2    |                  |                   |  |  |  |

| N14            | PR9B             | 0        |                  | С                 | N14            | PR11D            | 1    |                  | С                 |  |  |  |

| M14            | PR9A             | 0        |                  | Т                 | M14            | PR11B            | 1    |                  | С                 |  |  |  |

| L13            | PR8B             | 0        |                  | С                 | L13            | PR11C            | 1    |                  | Т                 |  |  |  |

| L14            | PR8A             | 0        |                  | Т                 | L14            | PR11A            | 1    |                  | Т                 |  |  |  |

| M13            | PR7D             | 0        |                  | С                 | M13            | PR10D            | 1    |                  | С                 |  |  |  |

| K14            | PR7C             | 0        |                  | Т                 | K14            | PR10C            | 1    |                  | Т                 |  |  |  |

| K13            | PR7B             | 0        |                  | С                 | K13            | PR10B            | 1    |                  | С                 |  |  |  |

| J14            | PR7A             | 0        |                  | Т                 | J14            | PR10A            | 1    |                  | Т                 |  |  |  |

| J13            | PR6B             | 0        |                  | С                 | J13            | PR9D             | 1    |                  |                   |  |  |  |

| H13            | PR6A             | 0        |                  | Т                 | H13            | PR9B             | 1    |                  |                   |  |  |  |

| G14            | GNDIO0           | 0        |                  |                   | G14            | GNDIO1           | 1    |                  |                   |  |  |  |

| G13            | PR5D             | 0        |                  | С                 | G13            | PR7B             | 1    |                  |                   |  |  |  |

| F14            | PR5C             | 0        |                  | Т                 | F14            | PR6C             | 1    |                  |                   |  |  |  |

| F13            | PR5B             | 0        |                  | С                 | F13            | PR6B             | 1    |                  |                   |  |  |  |

| E14            | PR5A             | 0        |                  | Т                 | E14            | PR5D             | 1    |                  |                   |  |  |  |

| E13            | PR4B             | 0        |                  | С                 | E13            | PR5B             | 1    |                  |                   |  |  |  |

| D14            | PR4A             | 0        |                  | Т                 | D14            | PR4D             | 1    |                  |                   |  |  |  |

| D13            | PR3D             | 0        |                  | С                 | D13            | PR4B             | 1    |                  |                   |  |  |  |

| C14            | PR3C             | 0        |                  | Т                 | C14            | PR3D             | 1    |                  |                   |  |  |  |

| C13            | PR3B             | 0        |                  | С                 | C13            | PR3B             | 1    |                  |                   |  |  |  |

| B14            | PR3A             | 0        |                  | Т                 | B14            | PR2D             | 1    |                  |                   |  |  |  |

| C12            | PR2B             | 0        |                  | С                 | C12            | PR2B             | 1    |                  |                   |  |  |  |

| B13            | GNDIO0           | 0        |                  |                   | B13            | GNDIO1           | 1    |                  |                   |  |  |  |

| A13            | PR2A             | 0        |                  | Т                 | A13            | PT9F             | 0    |                  | С                 |  |  |  |

| A12            | PT5C             | 0        |                  |                   | A12            | PT9E             | 0    |                  | Т                 |  |  |  |

| B11            | PT5B             | 0        |                  | С                 | B11            | PT9C             | 0    |                  |                   |  |  |  |

| A11            | PT5A             | 0        |                  | Т                 | A11            | PT9A             | 0    |                  |                   |  |  |  |

| B12            | PT4F             | 0        |                  | С                 | B12            | VCCIO0           | 0    |                  |                   |  |  |  |

| A10            | PT4E             | 0        |                  | Т                 | A10            | GNDIO0           | 0    |                  |                   |  |  |  |

| B10            | PT4D             | 0        |                  | С                 | B10            | PT7E             | 0    |                  |                   |  |  |  |

| A9             | PT4C             | 0        |                  | Т                 | A9             | PT7A             | 0    |                  |                   |  |  |  |

| A8             | PT4B             | 0        | PCLK0_1**        | С                 | A8             | PT6B             | 0    | PCLK0_1**        |                   |  |  |  |

| B8             | PT4A             | 0        | PCLK0_0**        | T                 | B8             | PT5B             | 0    | PCLK0_0**        | С                 |  |  |  |

| A7             | PT3D             | 0        |                  | C                 | A7             | PT5A             | 0    |                  | T                 |  |  |  |

| B7             | VCCAUX           | -        |                  | -                 | B7             | VCCAUX           | -    |                  |                   |  |  |  |

| A6             | PT3C             | 0        |                  | Т                 | A6             | PT4F             | 0    |                  |                   |  |  |  |

| B6             | VCC              | -        |                  |                   | B6             | VCC              | -    |                  |                   |  |  |  |

| A5             | PT3B             | 0        |                  | С                 | A5             | PT3F             | 0    |                  |                   |  |  |  |

|                |                  | v        |                  | ~                 |                |                  | •    | 1                |                   |  |  |  |

# LCMXO640, LCMXO1200 and LCMXO2280 Logic Signal Connections: 132 csBGA (Cont.)

|        |                  | LCM) | (O640            |              |        |                  | LC   | MXO1200          |              |        |                  | LCMXO2280 |                  |              |  |

|--------|------------------|------|------------------|--------------|--------|------------------|------|------------------|--------------|--------|------------------|-----------|------------------|--------------|--|

| Ball # | Ball<br>Function | Bank | Dual<br>Function | Differential | Ball # | Ball<br>Function | Bank | Dual<br>Function | Differential | Ball # | Ball<br>Function | Bank      | Dual<br>Function | Differential |  |

| B9     | PT7B             | 0    |                  | С            | B9     | PT9B             | 1    |                  | С            | B9     | PT12D            | 1         |                  | С            |  |

| A9     | PT7A             | 0    |                  | Т            | A9     | PT9A             | 1    |                  | Т            | A9     | PT12C            | 1         |                  | Т            |  |

| A8     | PT6B             | 0    | PCLK0_1***       | С            | A8     | PT7D             | 1    | PCLK1_1***       |              | A8     | PT10B            | 1         | PCLK1_1***       |              |  |

| B8     | PT6A             | 0    |                  | Т            | B8     | PT7B             | 1    |                  |              | B8     | PT9D             | 1         |                  |              |  |

| C8     | PT5B             | 0    | PCLK0_0***       | С            | C8     | PT6F             | 0    | PCLK1_0***       |              | C8     | PT9B             | 1         | PCLK1_0***       |              |  |

| B7     | PT5A             | 0    |                  | Т            | B7     | PT6D             | 0    |                  |              | B7     | PT8D             | 0         |                  |              |  |

| A7     | VCCAUX           | -    |                  |              | A7     | VCCAUX           | -    |                  |              | A7     | VCCAUX           | -         |                  |              |  |

| C7     | VCC              | -    |                  |              | C7     | VCC              | -    |                  |              | C7     | VCC              | -         |                  |              |  |

| A6     | PT4D             | 0    |                  | С            | A6     | PT5D             | 0    |                  | С            | A6     | PT7B             | 0         |                  | С            |  |

| B6     | PT4C             | 0    |                  | Т            | B6     | PT5C             | 0    |                  | Т            | B6     | PT7A             | 0         |                  | Т            |  |

| C6     | PT3F             | 0    |                  | С            | C6     | PT5B             | 0    |                  | С            | C6     | PT6D             | 0         |                  |              |  |

| B5     | PT3E             | 0    |                  | Т            | B5     | PT5A             | 0    |                  | Т            | B5     | PT6E             | 0         |                  | Т            |  |

| A5     | PT3D             | 0    |                  |              | A5     | PT4B             | 0    |                  |              | A5     | PT6F             | 0         |                  | С            |  |

| B4     | GNDIO0           | 0    |                  |              | B4     | GNDIO0           | 0    |                  |              | B4     | GNDIO0           | 0         |                  |              |  |

| A4     | PT3B             | 0    |                  |              | A4     | PT3D             | 0    |                  | С            | A4     | PT4B             | 0         |                  | С            |  |

| C4     | PT2F             | 0    |                  |              | C4     | PT3C             | 0    |                  | Т            | C4     | PT4A             | 0         |                  | Т            |  |

| A3     | PT2D             | 0    |                  | С            | A3     | PT3B             | 0    |                  | С            | A3     | PT3B             | 0         |                  | С            |  |

| A2     | PT2C             | 0    |                  | Т            | A2     | PT2B             | 0    |                  | С            | A2     | PT2B             | 0         |                  | С            |  |

| B3     | PT2B             | 0    |                  | С            | B3     | PT3A             | 0    |                  | Т            | B3     | PT3A             | 0         |                  | Т            |  |

| A1     | PT2A             | 0    |                  | Т            | A1     | PT2A             | 0    |                  | Т            | A1     | PT2A             | 0         |                  | Т            |  |

| F1     | GND              | -    |                  |              | F1     | GND              | -    |                  |              | F1     | GND              | -         |                  |              |  |

| P9     | GND              | -    |                  |              | P9     | GND              | -    |                  |              | P9     | GND              | -         |                  |              |  |

| J14    | GND              | -    |                  |              | J14    | GND              | -    |                  |              | J14    | GND              | -         |                  |              |  |

| C9     | GND              | -    |                  |              | C9     | GND              | -    |                  |              | C9     | GND              | -         |                  |              |  |

| C5     | VCCIO0           | 0    |                  |              | C5     | VCCIO0           | 0    |                  |              | C5     | VCCIO0           | 0         |                  |              |  |

| B11    | VCCIO0           | 0    |                  |              | B11    | VCCIO1           | 1    |                  |              | B11    | VCCIO1           | 1         |                  |              |  |

| E12    | VCCIO1           | 1    |                  |              | E12    | VCCIO2           | 2    |                  |              | E12    | VCCIO2           | 2         |                  |              |  |

| L12    | VCCIO1           | 1    |                  |              | L12    | VCCIO3           | 3    |                  |              | L12    | VCCIO3           | 3         |                  |              |  |

| M10    | VCCIO2           | 2    |                  |              | M10    | VCCIO4           | 4    |                  |              | M10    | VCCIO4           | 4         |                  |              |  |

| N2     | VCCIO2           | 2    |                  |              | N2     | VCCIO5           | 5    |                  |              | N2     | VCCIO5           | 5         |                  |              |  |

| D2     | VCCIO3           | 3    |                  |              | D2     | VCCIO7           | 7    |                  |              | D2     | VCCI07           | 7         |                  |              |  |

| K3     | VCCIO3           | 3    |                  |              | K3     | VCCIO6           | 6    |                  |              | K3     | VCCIO6           | 6         |                  |              |  |

\*Supports true LVDS outputs. \*\*NC for "E" devices. \*\*\*Primary clock inputs arer single-ended.

# LCMXO640, LCMXO1200 and LCMXO2280 Logic Signal Connections: 256 caBGA / 256 ftBGA (Cont.)

|                |                  | LCM) | KO640            |              |               |                 | LCN  | IXO1200          |              |                |                  | LCM  | /XO2280          |              |

|----------------|------------------|------|------------------|--------------|---------------|-----------------|------|------------------|--------------|----------------|------------------|------|------------------|--------------|

| Ball<br>Number | Ball<br>Function | Bank | Dual<br>Function | Differential | Ball          | Ball            | Bank | Dual<br>Function | Differential | Ball<br>Number | Ball<br>Function | Bank | Dual<br>Function | Differential |

| J13            | PR8C             | 1    | Tunction         | T            | J13           | PR11A           | 3    | runction         | T*           | J13            | PR14A            | 3    | Tunction         | T*           |

| GND            | GND              | -    |                  |              | GND           | GND             | -    |                  |              | GND            | GND              | -    |                  |              |

| K14            | PR8B             | 1    |                  | с            | K14           | PR10D           | 3    |                  | С            | K14            | PR13D            | 3    |                  | С            |

| J14            | PR8A             | 1    |                  | T            | J14           | PR10C           | 3    |                  | T            | J14            | PR13C            | 3    |                  | T            |

| K15            | PR7D             | 1    |                  | C            | K15           | PR10B           | 3    |                  | C*           | K15            | PR13B            | 3    |                  | C*           |

| J15            | PR7C             | 1    |                  | Т            | J15           | PR10A           | 3    |                  | T*           | J15            | PR13A            | 3    |                  | т*           |

| -              | -                | -    |                  |              | GND           | GNDIO3          | 3    |                  | -            | GND            | GNDIO3           | 3    |                  |              |

| -              | -                |      |                  |              | VCCIO3        | VCCIO3          | 3    |                  |              | VCCIO3         | VCCIO3           | 3    |                  |              |

| K12            | NC               |      |                  |              | K12           | PR9D            | 3    |                  | С            | K12            | PR11D            | 3    |                  | С            |

| J12            | NC               |      |                  |              | J12           | PR9C            | 3    |                  | Т            | J12            | PR11C            | 3    |                  | Т            |

| J16            | PR7B             | 1    |                  | С            | J16           | PR9B            | 3    |                  | C*           | J16            | PR11B            | 3    |                  | C*           |

| H16            | PR7A             | 1    |                  | Т            | H16           | PR9A            | 3    |                  | T*           | H16            | PR11A            | 3    |                  | T*           |

| H15            | PR6B             | 1    |                  | С            | H15           | PR8D            | 2    |                  | С            | H15            | PR10D            | 2    |                  | С            |

| G15            | PR6A             | 1    |                  | т            | G15           | PR8C            | 2    |                  | т            | G15            | PR10C            | 2    |                  | т            |

| H14            | PR5D             | 1    |                  | С            | H14           | PR8B            | 2    |                  | C*           | H14            | PR10B            | 2    |                  | C*           |

| G14            | PR5C             | 1    |                  | т            | G14           | PR8A            | 2    |                  | T*           | G14            | PR10A            | 2    |                  | T*           |

| GND            | GNDIO1           | 1    |                  |              | GND           | GNDIO2          | 2    |                  |              | GND            | GNDIO2           | 2    |                  |              |

| VCCIO1         | VCCIO1           | 1    |                  |              | VCCIO2        | VCCIO2          | 2    |                  |              | VCCIO2         | VCCIO2           | 2    |                  |              |

| H13            | PR6D             | 1    |                  | С            | H13           | PR7D            | 2    |                  | С            | H13            | PR9D             | 2    |                  | С            |

| H12            | PR6C             | 1    |                  | Т            | H12           | PR7C            | 2    |                  | Т            | H12            | PR9C             | 2    |                  | Т            |

| G13            | PR4D             | 1    |                  | С            | G13           | PR7B            | 2    |                  | C*           | G13            | PR9B             | 2    |                  | C*           |

| G12            | PR4C             | 1    |                  | Т            | G12           | PR7A            | 2    |                  | T*           | G12            | PR9A             | 2    |                  | T*           |

| G16            | PR5B             | 1    |                  | С            | G16           | PR6D            | 2    |                  | С            | G16            | PR7D             | 2    |                  | С            |

| F16            | PR5A             | 1    |                  | Т            | F16           | PR6C            | 2    |                  | Т            | F16            | PR7C             | 2    |                  | Т            |

| F15            | PR4B             | 1    |                  | С            | F15           | PR6B            | 2    |                  | C*           | F15            | PR7B             | 2    |                  | C*           |

| E15            | PR4A             | 1    |                  | Т            | E15           | PR6A            | 2    |                  | T*           | E15            | PR7A             | 2    |                  | T*           |

| E16            | PR3B             | 1    |                  | С            | E16           | PR5D            | 2    |                  | С            | E16            | PR6D             | 2    |                  | С            |

| D16            | PR3A             | 1    |                  | Т            | D16           | PR5C            | 2    |                  | Т            | D16            | PR6C             | 2    |                  | Т            |

| VCCIO1         | VCCIO1           | 1    |                  |              | VCCIO2        | VCCIO2          | 2    |                  |              | VCCIO2         | VCCIO2           | 2    |                  |              |

| GND            | GNDIO1           | 1    |                  |              | GND           | GNDIO2          | 2    |                  |              | GND            | GNDIO2           | 2    |                  |              |

| D15            | PR2D             | 1    |                  | С            | D15           | PR5B            | 2    |                  | C*           | D15            | PR6B             | 2    |                  | C*           |

| C15            | PR2C             | 1    |                  | Т            | C15           | PR5A            | 2    |                  | T*           | C15            | PR6A             | 2    |                  | T*           |

| C16            | PR2B             | 1    |                  | С            | C16           | PR4D            | 2    |                  | С            | C16            | PR5D             | 2    |                  | С            |