# E.J. Lattice Semiconductor Corporation - <u>LCMX0640C-3T100C Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| 2011.12                        |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                    |

| Number of LABs/CLBs            | 80                                                                          |

| Number of Logic Elements/Cells | 640                                                                         |

| Total RAM Bits                 |                                                                             |

| Number of I/O                  | 74                                                                          |

| Number of Gates                |                                                                             |

| Voltage - Supply               | 1.71V ~ 3.465V                                                              |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                             |

| Package / Case                 | 100-LQFP                                                                    |

| Supplier Device Package        | 100-TQFP (14x14)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lcmxo640c-3t100c |

|                                |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The devices use look-up tables (LUTs) and embedded block memories traditionally associated with FPGAs for flexible and efficient logic implementation. Through non-volatile technology, the devices provide the single-chip, highsecurity, instant-on capabilities traditionally associated with CPLDs. Finally, advanced process technology and careful design will provide the high pin-to-pin performance also associated with CPLDs.

The ispLEVER<sup>®</sup> design tools from Lattice allow complex designs to be efficiently implemented using the MachXO family of devices. Popular logic synthesis tools provide synthesis library support for MachXO. The ispLEVER tools use the synthesis tool output along with the constraints from its floor planning tools to place and route the design in the MachXO device. The ispLEVER tool extracts the timing from the routing and back-annotates it into the design for timing verification.

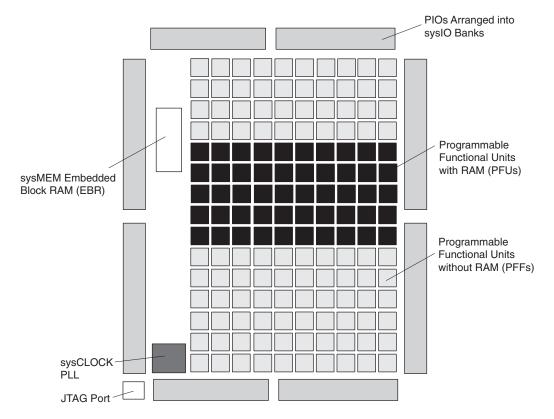

### Figure 2-1. Top View of the MachXO1200 Device<sup>1</sup>

1. Top view of the MachXO2280 device is similar but with higher LUT count, two PLLs, and three EBR blocks.

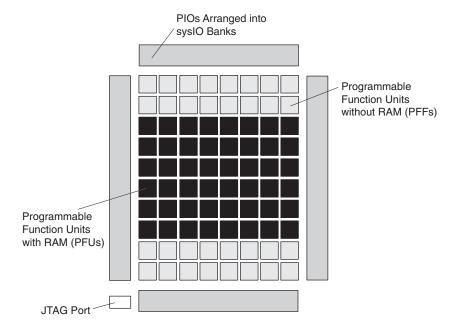

Figure 2-2. Top View of the MachXO640 Device

#### **Modes of Operation**

Each Slice is capable of four modes of operation: Logic, Ripple, RAM, and ROM. The Slice in the PFF is capable of all modes except RAM. Table 2-2 lists the modes and the capability of the Slice blocks.

#### Table 2-2. Slice Modes

|           | Logic              | Ripple                | RAM     | ROM          |

|-----------|--------------------|-----------------------|---------|--------------|

| PFU Slice | LUT 4x2 or LUT 5x1 | 2-bit Arithmetic Unit | SP 16x2 | ROM 16x1 x 2 |

| PFF Slice | LUT 4x2 or LUT 5x1 | 2-bit Arithmetic Unit | N/A     | ROM 16x1 x 2 |

**Logic Mode:** In this mode, the LUTs in each Slice are configured as 4-input combinatorial lookup tables (LUT4). A LUT4 can have 16 possible input combinations. Any logic function with four inputs can be generated by programming this lookup table. Since there are two LUT4s per Slice, a LUT5 can be constructed within one Slice. Larger lookup tables such as LUT6, LUT7, and LUT8 can be constructed by concatenating other Slices.

**Ripple Mode:** Ripple mode allows the efficient implementation of small arithmetic functions. In ripple mode, the following functions can be implemented by each Slice:

- Addition 2-bit

- Subtraction 2-bit

- Add/Subtract 2-bit using dynamic control

- Up counter 2-bit

- Down counter 2-bit

- Ripple mode multiplier building block

- Comparator functions of A and B inputs

- A greater-than-or-equal-to B

- A not-equal-to B

- A less-than-or-equal-to B

Two additional signals, Carry Generate and Carry Propagate, are generated per Slice in this mode, allowing fast arithmetic functions to be constructed by concatenating Slices.

**RAM Mode:** In this mode, distributed RAM can be constructed using each LUT block as a 16x2-bit memory. Through the combination of LUTs and Slices, a variety of different memories can be constructed.

The ispLEVER design tool supports the creation of a variety of different size memories. Where appropriate, the software will construct these using distributed memory primitives that represent the capabilities of the PFU. Table 2-3 shows the number of Slices required to implement different distributed RAM primitives. Figure 2-6 shows the distributed memory primitive block diagrams. Dual port memories involve the pairing of two Slices. One Slice functions as the read-write port, while the other companion Slice supports the read-only port. For more information on RAM mode in MachXO devices, please see details of additional technical documentation at the end of this data sheet.

#### Table 2-3. Number of Slices Required For Implementing Distributed RAM

|                  | SPR16x2 | DPR16x2 |

|------------------|---------|---------|

| Number of Slices | 1       | 2       |

Note: SPR = Single Port RAM, DPR = Dual Port RAM

The ispLEVER design tool takes the output of the synthesis tool and places and routes the design. Generally, the place and route tool is completely automatic, although an interactive routing editor is available to optimize the design.

### **Clock/Control Distribution Network**

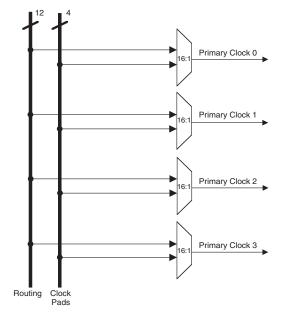

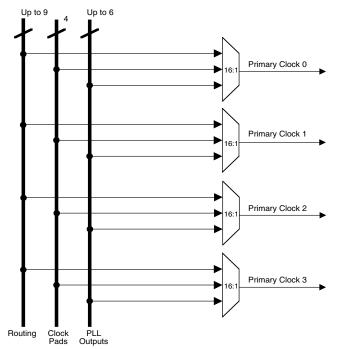

The MachXO family of devices provides global signals that are available to all PFUs. These signals consist of four primary clocks and four secondary clocks. Primary clock signals are generated from four 16:1 muxes as shown in Figure 2-7 and Figure 2-8. The available clock sources for the MachXO256 and MachXO640 devices are four dual function clock pins and 12 internal routing signals. The available clock sources for the MachXO2280 devices are four dual function clock pins, up to nine internal routing signals and up to six PLL outputs.

### Figure 2-7. Primary Clocks for MachXO256 and MachXO640 Devices

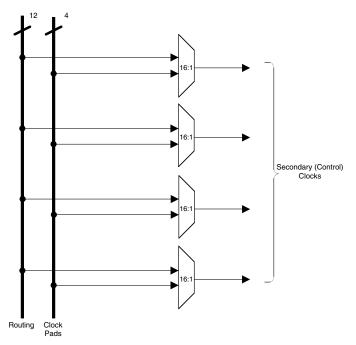

Four secondary clocks are generated from four 16:1 muxes as shown in Figure 2-9. Four of the secondary clock sources come from dual function clock pins and 12 come from internal routing.

Figure 2-9. Secondary Clocks for MachXO Devices

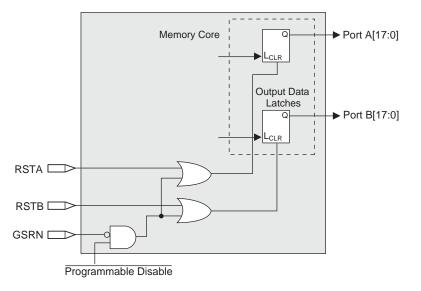

### Figure 2-13. Memory Core Reset

For further information on the sysMEM EBR block, see the details of additional technical documentation at the end of this data sheet.

#### EBR Asynchronous Reset

EBR asynchronous reset or GSR (if used) can only be applied if all clock enables are low for a clock cycle before the reset is applied and released a clock cycle after the reset is released, as shown in Figure 2-14. The GSR input to the EBR is always asynchronous.

#### Figure 2-14. EBR Asynchronous Reset (Including GSR) Timing Diagram

| Reset           |  |

|-----------------|--|

| Clock           |  |

| Clock<br>Enable |  |

If all clock enables remain enabled, the EBR asynchronous reset or GSR may only be applied and released after the EBR read and write clock inputs are in a steady state condition for a minimum of 1/f<sub>MAX</sub> (EBR clock). The reset release must adhere to the EBR synchronous reset setup time before the next active read or write clock edge.

If an EBR is pre-loaded during configuration, the GSR input must be disabled or the release of the GSR during device Wake Up must occur before the release of the device I/Os becoming active.

These instructions apply to all EBR RAM, ROM and FIFO implementations. For the EBR FIFO mode, the GSR signal is always enabled and the WE and RE signals act like the clock enable signals in Figure 2-14. The reset timing rules apply to the RPReset input vs the RE input and the RST input vs. the WE and RE inputs. Both RST and RPReset are always asynchronous EBR inputs.

Note that there are no reset restrictions if the EBR synchronous reset is used and the EBR GSR input is disabled

#### Table 2-10. Supported Output Standards

| Output Standard          | Drive                | V <sub>CCIO</sub> (Typ.) |  |  |

|--------------------------|----------------------|--------------------------|--|--|

| Single-ended Interfaces  |                      |                          |  |  |

| LVTTL                    | 4mA, 8mA, 12mA, 16mA | 3.3                      |  |  |

| LVCMOS33                 | 4mA, 8mA, 12mA, 14mA | 3.3                      |  |  |

| LVCMOS25                 | 4mA, 8mA, 12mA, 14mA | 2.5                      |  |  |

| LVCMOS18                 | 4mA, 8mA, 12mA, 14mA | 1.8                      |  |  |

| LVCMOS15                 | 4mA, 8mA             | 1.5                      |  |  |

| LVCMOS12                 | 2mA, 6mA             | 1.2                      |  |  |

| LVCMOS33, Open Drain     | 4mA, 8mA, 12mA, 14mA | <b>—</b>                 |  |  |

| LVCMOS25, Open Drain     | 4mA, 8mA, 12mA, 14mA | —                        |  |  |

| LVCMOS18, Open Drain     | 4mA, 8mA, 12mA, 14mA | —                        |  |  |

| LVCMOS15, Open Drain     | 4mA, 8mA             | <b>—</b>                 |  |  |

| LVCMOS12, Open Drain     | 2mA, 6mA             | <b>—</b>                 |  |  |

| PCI33 <sup>3</sup>       | N/A                  | 3.3                      |  |  |

| Differential Interfaces  |                      |                          |  |  |

| LVDS <sup>1, 2</sup>     | N/A                  | 2.5                      |  |  |

| BLVDS, RSDS <sup>2</sup> | N/A                  | 2.5                      |  |  |

| LVPECL <sup>2</sup>      | N/A                  | 3.3                      |  |  |

1. MachXO1200 and MachXO2280 devices have dedicated LVDS buffers.

2. These interfaces can be emulated with external resistors in all devices.

3. Top Banks of MachXO1200 and MachXO2280 devices only.

### sysIO Buffer Banks

The number of Banks vary between the devices of this family. Eight Banks surround the two larger devices, the MachXO1200 and MachXO2280 (two Banks per side). The MachXO640 has four Banks (one Bank per side). The smallest member of this family, the MachXO256, has only two Banks.

Each sysIO buffer Bank is capable of supporting multiple I/O standards. Each Bank has its own I/O supply voltage ( $V_{CCIO}$ ) which allows it to be completely independent from the other Banks. Figure 2-18, Figure 2-18, Figure 2-20 and Figure 2-21 shows the sysIO Banks and their associated supplies for all devices.

# MachXO Family Data Sheet DC and Switching Characteristics

#### June 2013

Data Sheet DS1002

### Absolute Maximum Ratings<sup>1, 2, 3</sup>

|                                              | LCMXO E (1.2V) | LCMXO C (1.8V/2.5V/3.3V) |

|----------------------------------------------|----------------|--------------------------|

| Supply Voltage V <sub>CC</sub>               | 0.5 to 1.32V   | 0.5 to 3.75V             |

| Supply Voltage V <sub>CCAUX</sub>            | 0.5 to 3.75V   | 0.5 to 3.75V             |

| Output Supply Voltage V <sub>CCIO</sub>      | 0.5 to 3.75V   | 0.5 to 3.75V             |

| I/O Tristate Voltage Applied <sup>4</sup>    | 0.5 to 3.75V   | 0.5 to 3.75V             |

| Dedicated Input Voltage Applied <sup>4</sup> | 0.5 to 3.75V   | 0.5 to 4.25V             |

| Storage Temperature (ambient)                | 65 to 150°C    | 65 to 150°C              |

| Junction Temp. (Tj)                          | +125°C         | +125°C                   |

1. Stress above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

2. Compliance with the Lattice Thermal Management document is required.

3. All voltages referenced to GND.

4. Overshoot and undershoot of -2V to (V<sub>IHMAX</sub> + 2) volts is permitted for a duration of <20ns.

### **Recommended Operating Conditions**<sup>1</sup>

| Symbol                          | Parameter                                           | Min.  | Max.  | Units |

|---------------------------------|-----------------------------------------------------|-------|-------|-------|

| Maa                             | Core Supply Voltage for 1.2V Devices                | 1.14  | 1.26  | V     |

| V <sub>CC</sub>                 | Core Supply Voltage for 1.8V/2.5V/3.3V Devices      | 1.71  | 3.465 | V     |

| V <sub>CCAUX</sub> <sup>3</sup> | Auxiliary Supply Voltage                            | 3.135 | 3.465 | V     |

| V <sub>CCIO<sup>2</sup></sub>   | I/O Driver Supply Voltage                           | 1.14  | 3.465 | V     |

| t <sub>JCOM</sub>               | Junction Temperature Commercial Operation           | 0     | +85   | °C    |

| t <sub>JIND</sub>               | Junction Temperature Industrial Operation           | -40   | 100   | °C    |

| t <sub>JFLASHCOM</sub>          | Junction Temperature, Flash Programming, Commercial | 0     | +85   | °C    |

| t <sub>JFLASHIND</sub>          | Junction Temperature, Flash Programming, Industrial | -40   | 100   | °C    |

Like power supplies must be tied together. For example, if V<sub>CCIO</sub> and V<sub>CC</sub> are both 2.5V, they must also be the same supply. 3.3V V<sub>CCIO</sub> and 1.2V V<sub>CCIO</sub> should be tied to V<sub>CCAUX</sub> or 1.2V V<sub>CC</sub> respectively.

2. See recommended voltages by I/O standard in subsequent table.

3.  $V_{CC}$  must reach minimum  $V_{CC}$  value before  $V_{CCAUX}$  reaches 2.5V.

### MachXO Programming/Erase Specifications

| Symbol                 | Parameter                                           | Min. | Max.   | Units  |

|------------------------|-----------------------------------------------------|------|--------|--------|

| N                      | Flash Programming Cycles per t <sub>RETENTION</sub> |      | 1,000  | Cycles |

| N <sub>PROGCYC</sub>   | Flash Functional Programming Cycles                 |      | 10,000 | Cycles |

| t <sub>RETENTION</sub> | Data Retention at 125° Junction Temperature         | 10   |        | Years  |

<sup>© 2013</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

### sysIO Differential Electrical Characteristics LVDS

| Parameter<br>Symbol                | Parameter Description                          | Test Conditions                                                | Min.                | Тур. | Max.  | Units |

|------------------------------------|------------------------------------------------|----------------------------------------------------------------|---------------------|------|-------|-------|

| V <sub>INP,</sub> V <sub>INM</sub> | Input Voltage                                  |                                                                | 0                   |      | 2.4   | V     |

| V <sub>THD</sub>                   | Differential Input Threshold                   |                                                                | +/-100              | _    | —     | mV    |

|                                    |                                                | $100mV \le V_{THD}$                                            | V <sub>THD</sub> /2 | 1.2  | 1.8   | V     |

| V <sub>CM</sub>                    | Input Common Mode Voltage                      | $200mV \le V_{THD}$                                            | V <sub>THD</sub> /2 | 1.2  | 1.9   | V     |

|                                    |                                                | $350mV \le V_{THD}$                                            | V <sub>THD</sub> /2 | 1.2  | 2.0   | V     |

| I <sub>IN</sub>                    | Input current                                  | Power on                                                       | —                   |      | +/-10 | μΑ    |

| V <sub>OH</sub>                    | Output high voltage for $V_{OP}$ or $V_{OM}$   | R <sub>T</sub> = 100 Ohm                                       | —                   | 1.38 | 1.60  | V     |

| V <sub>OL</sub>                    | Output low voltage for $V_{OP}$ or $V_{OM}$    | R <sub>T</sub> = 100 Ohm                                       | 0.9V                | 1.03 | —     | V     |

| V <sub>OD</sub>                    | Output voltage differential                    | (V <sub>OP</sub> - V <sub>OM</sub> ), R <sub>T</sub> = 100 Ohm | 250                 | 350  | 450   | mV    |

| $\Delta V_{OD}$                    | Change in V <sub>OD</sub> between high and low |                                                                | —                   | _    | 50    | mV    |

| V <sub>OS</sub>                    | Output voltage offset                          | $(V_{OP} - V_{OM})/2, R_{T} = 100 \text{ Ohm}$                 | 1.125               | 1.25 | 1.375 | V     |

| ΔV <sub>OS</sub>                   | Change in V <sub>OS</sub> between H and L      |                                                                | —                   | _    | 50    | mV    |

| I <sub>OSD</sub>                   | Output short circuit current                   | V <sub>OD</sub> = 0V Driver outputs shorted                    | _                   | _    | 6     | mA    |

### **Over Recommended Operating Conditions**

### LVDS Emulation

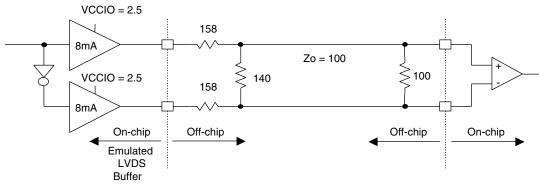

MachXO devices can support LVDS outputs via emulation (LVDS25E), in addition to the LVDS support that is available on-chip on certain devices. The output is emulated using complementary LVCMOS outputs in conjunction with resistors across the driver outputs on all devices. The scheme shown in Figure 3-1 is one possible solution for LVDS standard implementation. Resistor values in Figure 3-1 are industry standard values for 1% resistors.

#### Figure 3-1. LVDS Using External Resistors (LVDS25E)

Note: All resistors are  $\pm 1\%$ .

The LVDS differential input buffers are available on certain devices in the MachXO family.

For further information on LVPECL, BLVDS and other differential interfaces please see details of additional technical documentation at the end of the data sheet.

### RSDS

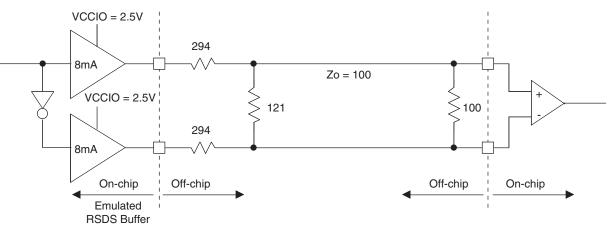

The MachXO family supports the differential RSDS standard. The output standard is emulated using complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs on all the devices. The RSDS input standard is supported by the LVDS differential input buffer on certain devices. The scheme shown in Figure 3-4 is one possible solution for RSDS standard implementation. Use LVDS25E mode with suggested resistors for RSDS operation. Resistor values in Figure 3-4 are industry standard values for 1% resistors.

Figure 3-4. RSDS (Reduced Swing Differential Standard)

#### Table 3-4. RSDS DC Conditions

| Parameter         | Description                 | Typical | Units |

|-------------------|-----------------------------|---------|-------|

| Z <sub>OUT</sub>  | Output impedance            | 20      | Ohms  |

| R <sub>S</sub>    | Driver series resistor      | 294     | Ohms  |

| R <sub>P</sub>    | Driver parallel resistor    | 121     | Ohms  |

| R <sub>T</sub>    | Receiver termination        | 100     | Ohms  |

| V <sub>OH</sub>   | Output high voltage         | 1.35    | V     |

| V <sub>OL</sub>   | Output low voltage          | 1.15    | V     |

| V <sub>OD</sub>   | Output differential voltage | 0.20    | V     |

| V <sub>CM</sub>   | Output common mode voltage  | 1.25    | V     |

| Z <sub>BACK</sub> | Back impedance              | 101.5   | Ohms  |

| I <sub>DC</sub>   | DC output current           | 3.66    | mA    |

### LCMXO1200 and LCMXO2280 Logic Signal Connections: 100 TQFP (Cont.)

|               |                  | CMXO1200 |                  | LCMXO2280    |                  |      |                  |              |

|---------------|------------------|----------|------------------|--------------|------------------|------|------------------|--------------|

| Pin<br>Number | Ball<br>Function | Bank     | Dual<br>Function | Differential | Ball<br>Function | Bank | Dual<br>Function | Differential |

| 82            | PT9A             | 1        |                  |              | PT12C            | 1    |                  | Т            |

| 83            | GND              | -        |                  |              | GND              | -    |                  |              |

| 84            | PT8B             | 1        |                  | С            | PT11B            | 1    |                  | С            |

| 85            | PT8A             | 1        |                  | Т            | PT11A            | 1    |                  | Т            |

| 86            | PT7D             | 1        | PCLK1_1****      |              | PT10B            | 1    | PCLK1_1****      |              |

| 87            | PT6F             | 0        | PCLK0_0****      |              | PT9B             | 1    | PCLK1_0****      |              |

| 88            | PT6D             | 0        |                  | С            | PT8F             | 0    |                  | С            |

| 89            | PT6C             | 0        |                  | Т            | PT8E             | 0    |                  | Т            |

| 90            | VCCAUX           | -        |                  |              | VCCAUX           | -    |                  |              |

| 91            | VCC              | -        |                  |              | VCC              | -    |                  |              |

| 92            | PT5B             | 0        |                  |              | PT6D             | 0    |                  |              |

| 93            | PT4B             | 0        |                  |              | PT6F             | 0    |                  |              |

| 94            | VCCIO0           | 0        |                  |              | VCCIO0           | 0    |                  |              |

| 95            | PT3D             | 0        |                  | С            | PT4B             | 0    |                  | С            |

| 96            | PT3C             | 0        |                  | Т            | PT4A             | 0    |                  | Т            |

| 97            | PT3B             | 0        |                  |              | PT3B             | 0    |                  |              |

| 98            | PT2B             | 0        |                  | С            | PT2B             | 0    |                  | С            |

| 99            | PT2A             | 0        |                  | Т            | PT2A             | 0    |                  | Т            |

| 100**         | GNDIO0<br>GNDIO7 | -        |                  |              | GNDIO0<br>GNDIO7 | -    |                  |              |

\*Supports true LVDS outputs.

\*\*Double bonded to the pin.

\*\*\*NC for "E" devices.

\*\*\*\*Primary clock inputs are single-ended.

# LCMXO256 and LCMXO640 Logic Signal Connections: 100 csBGA

|                |                  | LCMXO25 | 6                |                   | LCMXO640       |                  |      |                  |                   |

|----------------|------------------|---------|------------------|-------------------|----------------|------------------|------|------------------|-------------------|

| Ball<br>Number | Ball<br>Function | Bank    | Dual<br>Function | Differen-<br>tial | Ball<br>Number | Ball<br>Function | Bank | Dual<br>Function | Differen-<br>tial |

| B1             | PL2A             | 1       |                  | Т                 | B1             | PL2A             | 3    |                  | Т                 |

| C1             | PL2B             | 1       |                  | С                 | C1             | PL2C             | 3    |                  | Т                 |

| D2             | PL3A             | 1       |                  | Т                 | D2             | PL2B             | 3    |                  | С                 |

| D1             | PL3B             | 1       |                  | С                 | D1             | PL2D             | 3    |                  | С                 |

| C2             | PL3C             | 1       |                  | Т                 | C2             | PL3A             | 3    |                  | Т                 |

| E1             | PL3D             | 1       |                  | С                 | E1             | PL3B             | 3    |                  | С                 |

| E2             | PL4A             | 1       |                  | Т                 | E2             | PL3C             | 3    |                  | Т                 |

| F1             | PL4B             | 1       |                  | С                 | F1             | PL3D             | 3    |                  | С                 |

| F2             | PL5A             | 1       |                  | Т                 | F2             | PL4A             | 3    |                  |                   |

| G2             | PL5B             | 1       |                  | С                 | G2             | PL4C             | 3    |                  | Т                 |

| H1             | GNDIO1           | 1       |                  |                   | H1             | GNDIO3           | 3    |                  |                   |

| H2             | PL5C             | 1       |                  | Т                 | H2             | PL4D             | 3    |                  | С                 |

| J1             | PL5D             | 1       | GSRN             | С                 | J1             | PL5B             | 3    | GSRN             |                   |

| J2             | PL6A             | 1       |                  | Т                 | J2             | PL7B             | 3    |                  |                   |

| K1             | PL6B             | 1       | TSALL            | С                 | K1             | PL8C             | 3    | TSALL            | Т                 |

| K2             | PL7A             | 1       |                  | Т                 | K2             | PL8D             | 3    |                  | С                 |

| L1             | PL7B             | 1       |                  | С                 | L1             | PL9A             | 3    |                  |                   |

| L2             | PL7C             | 1       |                  | Т                 | L2             | PL9C             | 3    |                  |                   |

| M1             | PL7D             | 1       |                  | С                 | M1             | PL10A            | 3    |                  |                   |

| M2             | PL8A             | 1       |                  | Т                 | M2             | PL10C            | 3    |                  |                   |

| N1             | PL8B             | 1       |                  | С                 | N1             | PL11A            | 3    |                  |                   |

| M3             | PL9A             | 1       |                  | Т                 | M3             | PL11C            | 3    |                  |                   |

| N2             | GNDIO1           | 1       |                  |                   | N2             | GNDIO3           | 3    |                  |                   |

| P2             | TMS              | 1       | TMS              |                   | P2             | TMS              | 2    | TMS              |                   |

| P3             | PL9B             | 1       |                  | С                 | P3             | PB2C             | 2    |                  |                   |

| N4             | TCK              | 1       | ТСК              |                   | N4             | ТСК              | 2    | ТСК              |                   |

| P4             | PB2A             | 1       |                  | Т                 | P4             | VCCIO2           | 2    |                  |                   |

| N3             | PB2B             | 1       |                  | С                 | N3             | GNDIO2           | 2    |                  |                   |

| P5             | TDO              | 1       | TDO              |                   | P5             | TDO              | 2    | TDO              |                   |

| N5             | PB2C             | 1       |                  | Т                 | N5             | PB4C             | 2    |                  |                   |

| P6             | TDI              | 1       | TDI              |                   | P6             | TDI              | 2    | TDI              |                   |

| N6             | PB2D             | 1       |                  | С                 | N6             | PB4E             | 2    |                  |                   |

| P7             | VCC              | -       |                  |                   | P7             | VCC              | -    |                  |                   |

| N7             | PB3A             | 1       | PCLK1_1**        | Т                 | N7             | PB5B             | 2    | PCLK2_1**        |                   |

| P8             | PB3B             | 1       |                  | С                 | P8             | PB5D             | 2    |                  |                   |

| N8             | PB3C             | 1       | PCLK1_0**        | Т                 | N8             | PB6B             | 2    | PCLK2_0**        |                   |

| P9             | PB3D             | 1       |                  | С                 | P9             | PB6C             | 2    |                  |                   |

| N10            | GNDIO1           | 1       |                  | -                 | N10            | GNDIO2           | 2    |                  |                   |

| P11            | PB4A             | 1       |                  | Т                 | P11            | PB8B             | 2    |                  |                   |

| N11            | PB4B             | 1       |                  | C                 | N11            | PB8C             | 2    |                  | Т                 |

| P12            | PB4C             | 1       |                  | T                 | P12            | PB8D             | 2    |                  | C                 |

| N12            | PB4D             | 1       |                  | C                 | N12            | PB9A             | 2    | +                | •                 |

### LCMXO256 and LCMXO640 Logic Signal Connections: 100 csBGA (Cont.)

| LCMXO256       |                  |      |                  |                   | LCMXO640       |                  |      |                  |                   |  |

|----------------|------------------|------|------------------|-------------------|----------------|------------------|------|------------------|-------------------|--|

| Ball<br>Number | Ball<br>Function | Bank | Dual<br>Function | Differen-<br>tial | Ball<br>Number | Ball<br>Function | Bank | Dual<br>Function | Differen-<br>tial |  |

| P13            | PB5A             | 1    |                  |                   | P13            | PB9C             | 2    |                  | Т                 |  |

| M12*           | SLEEPN           | -    | SLEEPN           |                   | M12*           | SLEEPN           | -    | SLEEPN           |                   |  |

| P14            | PB5C             | 1    |                  | Т                 | P14            | PB9D             | 2    |                  | С                 |  |

| N13            | PB5D             | 1    |                  | С                 | N13            | PB9F             | 2    |                  |                   |  |

| N14            | PR9B             | 0    |                  | С                 | N14            | PR11D            | 1    |                  | С                 |  |

| M14            | PR9A             | 0    |                  | Т                 | M14            | PR11B            | 1    |                  | С                 |  |

| L13            | PR8B             | 0    |                  | С                 | L13            | PR11C            | 1    |                  | Т                 |  |

| L14            | PR8A             | 0    |                  | Т                 | L14            | PR11A            | 1    |                  | Т                 |  |

| M13            | PR7D             | 0    |                  | С                 | M13            | PR10D            | 1    |                  | С                 |  |

| K14            | PR7C             | 0    |                  | Т                 | K14            | PR10C            | 1    |                  | Т                 |  |

| K13            | PR7B             | 0    |                  | С                 | K13            | PR10B            | 1    |                  | С                 |  |

| J14            | PR7A             | 0    |                  | Т                 | J14            | PR10A            | 1    |                  | Т                 |  |

| J13            | PR6B             | 0    |                  | С                 | J13            | PR9D             | 1    |                  |                   |  |

| H13            | PR6A             | 0    |                  | Т                 | H13            | PR9B             | 1    |                  |                   |  |

| G14            | GNDIO0           | 0    |                  |                   | G14            | GNDIO1           | 1    |                  |                   |  |

| G13            | PR5D             | 0    |                  | С                 | G13            | PR7B             | 1    |                  |                   |  |

| F14            | PR5C             | 0    |                  | Т                 | F14            | PR6C             | 1    |                  |                   |  |

| F13            | PR5B             | 0    |                  | С                 | F13            | PR6B             | 1    |                  |                   |  |

| E14            | PR5A             | 0    |                  | Т                 | E14            | PR5D             | 1    |                  |                   |  |

| E13            | PR4B             | 0    |                  | С                 | E13            | PR5B             | 1    |                  |                   |  |

| D14            | PR4A             | 0    |                  | Т                 | D14            | PR4D             | 1    |                  |                   |  |

| D13            | PR3D             | 0    |                  | С                 | D13            | PR4B             | 1    |                  |                   |  |

| C14            | PR3C             | 0    |                  | Т                 | C14            | PR3D             | 1    |                  |                   |  |

| C13            | PR3B             | 0    |                  | С                 | C13            | PR3B             | 1    |                  |                   |  |

| B14            | PR3A             | 0    |                  | Т                 | B14            | PR2D             | 1    |                  |                   |  |

| C12            | PR2B             | 0    |                  | С                 | C12            | PR2B             | 1    |                  |                   |  |

| B13            | GNDIO0           | 0    |                  |                   | B13            | GNDIO1           | 1    |                  |                   |  |

| A13            | PR2A             | 0    |                  | Т                 | A13            | PT9F             | 0    |                  | С                 |  |

| A12            | PT5C             | 0    |                  |                   | A12            | PT9E             | 0    |                  | Т                 |  |

| B11            | PT5B             | 0    |                  | С                 | B11            | PT9C             | 0    |                  |                   |  |

| A11            | PT5A             | 0    |                  | Т                 | A11            | PT9A             | 0    |                  |                   |  |

| B12            | PT4F             | 0    |                  | С                 | B12            | VCCIO0           | 0    |                  |                   |  |

| A10            | PT4E             | 0    |                  | Т                 | A10            | GNDIO0           | 0    |                  |                   |  |

| B10            | PT4D             | 0    |                  | С                 | B10            | PT7E             | 0    |                  |                   |  |

| A9             | PT4C             | 0    |                  | Т                 | A9             | PT7A             | 0    |                  |                   |  |

| A8             | PT4B             | 0    | PCLK0_1**        | С                 | A8             | PT6B             | 0    | PCLK0_1**        |                   |  |

| B8             | PT4A             | 0    | PCLK0_0**        | T                 | B8             | PT5B             | 0    | PCLK0_0**        | С                 |  |

| A7             | PT3D             | 0    |                  | C                 | A7             | PT5A             | 0    |                  | T                 |  |

| B7             | VCCAUX           | -    |                  | -                 | B7             | VCCAUX           | -    |                  |                   |  |

| A6             | PT3C             | 0    |                  | Т                 | A6             | PT4F             | 0    |                  |                   |  |

| B6             | VCC              | -    |                  |                   | B6             | VCC              | -    |                  |                   |  |

| A5             | PT3B             | 0    |                  | С                 | A5             | PT3F             | 0    |                  |                   |  |

|                |                  | v    |                  | ~                 |                |                  | •    | 1                |                   |  |

## LCMXO256 and LCMXO640 Logic Signal Connections: 100 csBGA (Cont.)

|                |                  | LCMXO256 |                  |                   |                |                  | LCMXO640 | )                |                   |

|----------------|------------------|----------|------------------|-------------------|----------------|------------------|----------|------------------|-------------------|

| Ball<br>Number | Ball<br>Function | Bank     | Dual<br>Function | Differen-<br>tial | Ball<br>Number | Ball<br>Function | Bank     | Dual<br>Function | Differen-<br>tial |

| A4             | GNDIO0           | 0        |                  |                   | A4             | GNDIO0           | 0        |                  |                   |

| B4             | PT3A             | 0        |                  | Т                 | B4             | PT3B             | 0        |                  | С                 |

| A3             | PT2F             | 0        |                  | С                 | A3             | PT3A             | 0        |                  | Т                 |

| B3             | PT2E             | 0        |                  | Т                 | B3             | PT2F             | 0        |                  | С                 |

| A2             | PT2D             | 0        |                  | С                 | A2             | PT2E             | 0        |                  | Т                 |

| C3             | PT2C             | 0        |                  | Т                 | C3             | PT2B             | 0        |                  | С                 |

| A1             | PT2B             | 0        |                  | С                 | A1             | PT2C             | 0        |                  |                   |

| B2             | PT2A             | 0        |                  | Т                 | B2             | PT2A             | 0        |                  | Т                 |

| N9             | GND              | -        |                  |                   | N9             | GND              | -        |                  |                   |

| B9             | GND              | -        |                  |                   | B9             | GND              | -        |                  |                   |

| B5             | VCCIO0           | 0        |                  |                   | B5             | VCCIO0           | 0        |                  |                   |

| A14            | VCCIO0           | 0        |                  |                   | A14            | VCCIO1           | 1        |                  |                   |

| H14            | VCCIO0           | 0        |                  |                   | H14            | VCCIO1           | 1        |                  |                   |

| P10            | VCCIO1           | 1        |                  |                   | P10            | VCCIO2           | 2        |                  |                   |

| G1             | VCCIO1           | 1        |                  |                   | G1             | VCCIO3           | 3        |                  |                   |

| P1             | VCCIO1           | 1        |                  |                   | P1             | VCCIO3           | 3        |                  |                   |

\*NC for "E" devices.

\*\*Primary clock inputs are single-ended.

### LCMXO2280 Logic Signal Connections: 324 ftBGA

| LCMXO2280   |               |      |                |             |  |  |  |

|-------------|---------------|------|----------------|-------------|--|--|--|

| Ball Number | Ball Function | Bank | Dual Function  | Differentia |  |  |  |

| GND         | GNDIO7        | 7    |                |             |  |  |  |

| VCCIO7      | VCCIO7        | 7    |                |             |  |  |  |

| D4          | PL2A          | 7    | LUM0_PLLT_FB_A | Т           |  |  |  |

| F5          | PL2B          | 7    | LUM0_PLLC_FB_A | С           |  |  |  |

| B3          | PL3A          | 7    |                | T*          |  |  |  |

| C3          | PL3B          | 7    |                | C*          |  |  |  |

| E4          | PL3C          | 7    | LUM0_PLLT_IN_A | Т           |  |  |  |

| G6          | PL3D          | 7    | LUM0_PLLC_IN_A | С           |  |  |  |

| A1          | PL4A          | 7    |                | Τ*          |  |  |  |

| B1          | PL4B          | 7    |                | C*          |  |  |  |

| F4          | PL4C          | 7    |                | Т           |  |  |  |

| VCC         | VCC           | -    |                |             |  |  |  |

| E3          | PL4D          | 7    |                | С           |  |  |  |

| D2          | PL5A          | 7    |                | Τ*          |  |  |  |

| D3          | PL5B          | 7    |                | C*          |  |  |  |

| G5          | PL5C          | 7    |                | Т           |  |  |  |

| F3          | PL5D          | 7    |                | С           |  |  |  |

| C2          | PL6A          | 7    |                | Τ*          |  |  |  |

| VCCIO7      | VCCIO7        | 7    |                |             |  |  |  |

| GND         | GNDIO7        | 7    |                |             |  |  |  |

| C1          | PL6B          | 7    |                | C*          |  |  |  |

| H5          | PL6C          | 7    |                | Т           |  |  |  |

| G4          | PL6D          | 7    |                | С           |  |  |  |

| E2          | PL7A          | 7    |                | T*          |  |  |  |

| D1          | PL7B          | 7    | GSRN           | C*          |  |  |  |

| J6          | PL7C          | 7    |                | Т           |  |  |  |

| H4          | PL7D          | 7    |                | С           |  |  |  |

| F2          | PL8A          | 7    |                | T*          |  |  |  |

| E1          | PL8B          | 7    |                | C*          |  |  |  |

| GND         | GND           | -    |                |             |  |  |  |

| J3          | PL8C          | 7    |                | Т           |  |  |  |

| J5          | PL8D          | 7    |                | С           |  |  |  |

| G3          | PL9A          | 7    |                | T*          |  |  |  |

| H3          | PL9B          | 7    |                | C*          |  |  |  |

| K3          | PL9C          | 7    |                | Т           |  |  |  |

| K5          | PL9D          | 7    |                | С           |  |  |  |

| F1          | PL10A         | 7    |                | T*          |  |  |  |

| VCCIO7      | VCCIO7        | 7    |                |             |  |  |  |

| GND         | GNDIO7        | 7    |                |             |  |  |  |

| G1          | PL10B         | 7    |                | C*          |  |  |  |

| K4          | PL10C         | 7    |                | T           |  |  |  |

| K6          | PL10D         | 7    |                | C           |  |  |  |

### LCMXO2280 Logic Signal Connections: 324 ftBGA (Cont.)

| LCMXO2280   |               |      |               |              |  |  |

|-------------|---------------|------|---------------|--------------|--|--|

| Ball Number | Ball Function | Bank | Dual Function | Differential |  |  |

| GND         | GNDIO3        | 3    |               |              |  |  |

| VCCIO3      | VCCIO3        | 3    |               |              |  |  |

| P15         | PR20B         | 3    |               | С            |  |  |

| N14         | PR20A         | 3    |               | Т            |  |  |

| N15         | PR19B         | 3    |               | С            |  |  |

| M13         | PR19A         | 3    |               | Т            |  |  |

| R15         | PR18B         | 3    |               | C*           |  |  |

| T16         | PR18A         | 3    |               | Τ*           |  |  |

| N16         | PR17D         | 3    |               | С            |  |  |

| M14         | PR17C         | 3    |               | Т            |  |  |

| U17         | PR17B         | 3    |               | C*           |  |  |

| VCC         | VCC           | -    |               |              |  |  |

| U18         | PR17A         | 3    |               | Τ*           |  |  |

| R17         | PR16D         | 3    |               | С            |  |  |

| R16         | PR16C         | 3    |               | Т            |  |  |

| P16         | PR16B         | 3    |               | C*           |  |  |

| VCCIO3      | VCCIO3        | 3    |               |              |  |  |

| GND         | GNDIO3        | 3    |               |              |  |  |

| P17         | PR16A         | 3    |               | T*           |  |  |

| L13         | PR15D         | 3    |               | С            |  |  |

| M15         | PR15C         | 3    |               | Т            |  |  |

| T17         | PR15B         | 3    |               | C*           |  |  |

| T18         | PR15A         | 3    |               | T*           |  |  |

| L14         | PR14D         | 3    |               | С            |  |  |

| L15         | PR14C         | 3    |               | Т            |  |  |

| R18         | PR14B         | 3    |               | C*           |  |  |

| P18         | PR14A         | 3    |               | T*           |  |  |

| GND         | GND           | -    |               |              |  |  |

| K15         | PR13D         | 3    |               | С            |  |  |

| K13         | PR13C         | 3    |               | Т            |  |  |

| N17         | PR13B         | 3    |               | C*           |  |  |

| N18         | PR13A         | 3    |               | T*           |  |  |

| K16         | PR12D         | 3    |               | С            |  |  |

| K14         | PR12C         | 3    |               | Т            |  |  |

| M16         | PR12B         | 3    |               | C*           |  |  |

| L16         | PR12A         | 3    |               | T*           |  |  |

| GND         | GNDIO3        | 3    |               |              |  |  |

| VCCIO3      | VCCIO3        | 3    |               |              |  |  |

| J16         | PR11D         | 3    |               | С            |  |  |

| J14         | PR11C         | 3    |               | Т            |  |  |

| M17         | PR11B         | 3    |               | C*           |  |  |

| L17         | PR11A         | 3    |               | T*           |  |  |

| J15         | PR10D         | 2    |               | С            |  |  |

### **Conventional Packaging**

| Industrial         |      |                |      |       |         |      |       |

|--------------------|------|----------------|------|-------|---------|------|-------|

| Part Number        | LUTs | Supply Voltage | I/Os | Grade | Package | Pins | Temp. |

| LCMXO256C-3T100I   | 256  | 1.8V/2.5V/3.3V | 78   | -3    | TQFP    | 100  | IND   |

| LCMXO256C-4T100I   | 256  | 1.8V/2.5V/3.3V | 78   | -4    | TQFP    | 100  | IND   |

| LCMXO256C-3M100I   | 256  | 1.8V/2.5V/3.3V | 78   | -3    | csBGA   | 100  | IND   |

| LCMXO256C-4M100I   | 256  | 1.8V/2.5V/3.3V | 78   | -4    | csBGA   | 100  | IND   |

| Part Number        | LUTs | Supply Voltage | I/Os | Grade | Package | Pins | Temp. |

| LCMXO640C-3T100I   | 640  | 1.8V/2.5V/3.3V | 74   | -3    | TQFP    | 100  | IND   |

| LCMXO640C-4T100I   | 640  | 1.8V/2.5V/3.3V | 74   | -4    | TQFP    | 100  | IND   |

| LCMXO640C-3M100I   | 640  | 1.8V/2.5V/3.3V | 74   | -3    | csBGA   | 100  | IND   |

| LCMXO640C-4M100I   | 640  | 1.8V/2.5V/3.3V | 74   | -4    | csBGA   | 100  | IND   |

| LCMXO640C-3T144I   | 640  | 1.8V/2.5V/3.3V | 113  | -3    | TQFP    | 144  | IND   |

| LCMXO640C-4T144I   | 640  | 1.8V/2.5V/3.3V | 113  | -4    | TQFP    | 144  | IND   |

| LCMXO640C-3M132I   | 640  | 1.8V/2.5V/3.3V | 101  | -3    | csBGA   | 132  | IND   |

| LCMXO640C-4M132I   | 640  | 1.8V/2.5V/3.3V | 101  | -4    | csBGA   | 132  | IND   |

| LCMXO640C-3B256I   | 640  | 1.8V/2.5V/3.3V | 159  | -3    | caBGA   | 256  | IND   |

| LCMX0640C-4B256I   | 640  | 1.8V/2.5V/3.3V | 159  | -4    | caBGA   | 256  | IND   |

| LCMX0640C-3FT256I  | 640  | 1.8V/2.5V/3.3V | 159  | -3    | ftBGA   | 256  | IND   |

| LCMX0640C-4FT256I  | 640  | 1.8V/2.5V/3.3V | 159  | -4    | ftBGA   | 256  | IND   |

|                    |      |                |      | -     |         |      |       |

| Part Number        | LUTs | Supply Voltage | I/Os | Grade | Package | Pins | Temp. |

| LCMXO1200C-3T100I  | 1200 | 1.8V/2.5V/3.3V | 73   | -3    | TQFP    | 100  | IND   |

| LCMXO1200C-4T100I  | 1200 | 1.8V/2.5V/3.3V | 73   | -4    | TQFP    | 100  | IND   |

| LCMXO1200C-3T144I  | 1200 | 1.8V/2.5V/3.3V | 113  | -3    | TQFP    | 144  | IND   |

| LCMXO1200C-4T144I  | 1200 | 1.8V/2.5V/3.3V | 113  | -4    | TQFP    | 144  | IND   |

| LCMXO1200C-3M132I  | 1200 | 1.8V/2.5V/3.3V | 101  | -3    | csBGA   | 132  | IND   |

| LCMXO1200C-4M132I  | 1200 | 1.8V/2.5V/3.3V | 101  | -4    | csBGA   | 132  | IND   |

| LCMXO1200C-3B256I  | 1200 | 1.8V/2.5V/3.3V | 211  | -3    | caBGA   | 256  | IND   |

| LCMXO1200C-4B256I  | 1200 | 1.8V/2.5V/3.3V | 211  | -4    | caBGA   | 256  | IND   |

| LCMXO1200C-3FT256I | 1200 | 1.8V/2.5V/3.3V | 211  | -3    | ftBGA   | 256  | IND   |

| LCMXO1200C-4FT256I | 1200 | 1.8V/2.5V/3.3V | 211  | -4    | ftBGA   | 256  | IND   |

| Part Number        | LUTs | Supply Voltage | I/Os | Grade | Package | Pins | Temp. |

| LCMXO2280C-3T100I  | 2280 | 1.8V/2.5V/3.3V | 73   | -3    | TQFP    | 100  | IND   |

| LCMXO2280C-4T100I  | 2280 | 1.8V/2.5V/3.3V | 73   | -4    | TQFP    | 100  | IND   |

| LCMXO2280C-3T144I  | 2280 | 1.8V/2.5V/3.3V | 113  | -3    | TQFP    | 144  | IND   |

| LCMXO2280C-4T144I  | 2280 | 1.8V/2.5V/3.3V | 113  | -4    | TQFP    | 144  | IND   |

| LCMXO2280C-3M132I  | 2280 | 1.8V/2.5V/3.3V | 101  | -3    | csBGA   | 132  | IND   |

| LCMXO2280C-4M132I  | 2280 | 1.8V/2.5V/3.3V | 101  | -4    | csBGA   | 132  | IND   |

| LCMXO2280C-3B256I  | 2280 | 1.8V/2.5V/3.3V | 211  | -3    | caBGA   | 256  | IND   |

| LCMX02280C-4B256I  | 2280 | 1.8V/2.5V/3.3V | 211  | -4    | caBGA   | 256  | IND   |

| LCMXO2280C-3FT256I | 2280 | 1.8V/2.5V/3.3V | 211  | -3    | ftBGA   | 256  | IND   |

| LCMXO2280C-4FT256I | 2280 | 1.8V/2.5V/3.3V | 211  | -4    | ftBGA   | 256  | IND   |

| LCMX02280C-3FT324I | 2280 | 1.8V/2.5V/3.3V | 271  | -3    | ftBGA   | 324  | IND   |

|                    |      |                |      |       |         |      |       |

| LCMXO2280C-4FT324I | 2280 | 1.8V/2.5V/3.3V | 271  | -4    | ftBGA   | 324  | IND   |

# MachXO Family Data Sheet Supplemental Information

June 2013

Data Sheet DS1002

### **For Further Information**

A variety of technical notes for the MachXO family are available on the Lattice web site.

- TN1091, MachXO sysIO Usage Guide

- TN1089, MachXO sysCLOCK Design and Usage Guide

- TN1092, Memory Usage Guide for MachXO Devices

- TN1090, Power Estimation and Management for MachXO Devices

- TN1086, MachXO JTAG Programming and Configuration User's Guide

- TN1087, Minimizing System Interruption During Configuration Using TransFR Technology

- TN1097, MachXO Density Migration

- AN8066, Boundary Scan Testability with Lattice sysIO Capability

For further information on interface standards refer to the following web sites:

- JEDEC Standards (LVTTL, LVCMOS): www.jedec.org

- PCI: <u>www.pcisig.com</u>

<sup>© 2013</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# MachXO Family Data Sheet Revision History

June 2013

### **Revision History**

Data Sheet DS1002

| Date          | Version | Section                             | Change Summary                                                                                                         |

|---------------|---------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| February 2005 | 01.0    | —                                   | Initial release.                                                                                                       |

| October 2005  | 01.1    | Introduction                        | Distributed RAM information in family table updated. Added footnote 1 - fpBGA packaging to the family selection guide. |

|               |         | Architecture                        | sysIO Buffer section updated.                                                                                          |

|               |         |                                     | Hot Socketing section updated.                                                                                         |

|               |         |                                     | Sleep Mode section updated.                                                                                            |

|               |         |                                     | SLEEP Pin Characteristics section updated.                                                                             |

|               |         |                                     | Oscillator section updated.                                                                                            |

|               |         |                                     | Security section updated.                                                                                              |

|               |         | DC and Switching<br>Characteristics | Recommended Operating Conditions table updated.                                                                        |

|               |         |                                     | DC Electrical Characteristics table updated.                                                                           |

|               |         |                                     | Supply Current (Sleep Mode) table added with LCMXO256/640 data.                                                        |

|               |         |                                     | Supply Current (Standby) table updated with LCMXO256/640 data.                                                         |

|               |         |                                     | Initialization Supply Current table updated with LCMXO256/640 data.                                                    |

|               |         |                                     | Programming and Erase Flash Supply Current table updated with LCMXO256/640 data.                                       |

|               |         |                                     | Register-to-Register Performance table updated (rev. A 0.16).                                                          |

|               |         |                                     | External Switching Characteristics table updated (rev. A 0.16).                                                        |

|               |         |                                     | Internal Timing Parameter table updated (rev. A 0.16).                                                                 |

|               |         |                                     | Family Timing Adders updated (rev. A 0.16).                                                                            |

|               |         |                                     | sysCLOCK Timingupdated (rev. A 0.16).                                                                                  |

|               |         |                                     | MachXO "C" Sleep Mode Timing updated (A 0.16).                                                                         |

|               |         |                                     | JTAG Port Timing Specification updated (rev. A 0.16).                                                                  |

|               |         | Pinout Information                  | SLEEPIN description updated.                                                                                           |

|               |         |                                     | Pin Information Summary updated.                                                                                       |

|               |         |                                     | Power Supply and NC Connection table has been updated.                                                                 |

|               |         |                                     | Logic Signal Connection section has been updated to include all devices/packages.                                      |

|               |         | Ordering Information                | Part Number Description section has been updated.                                                                      |

|               |         |                                     | Ordering Part Number section has been updated (added LCMXO256C/LCMXO640C "4W").                                        |

|               |         | Supplemental<br>Information         | MachXO Density Migration Technical Note (TN1097) added.                                                                |

| November 2005 | 01.2    | Pinout Information                  | Added "Power Supply and NC Connections" summary information for LCMXO1200 and LCMXO2280 in 100 TQFP package.           |

| December 2005 | 01.3    | DC and Switching<br>Characteristics | Supply Current (Standby) table updated with LCMXO1200/2280 data.                                                       |

|               |         | Ordering Information                | Ordering Part Number section updated (added LCMXO2280C "4W").                                                          |

| April 2006    | 02.0    | Introduction                        | Introduction paragraphs updated.                                                                                       |

|               |         | Architecture                        | Architecture Overview paragraphs updated.                                                                              |

© 2013 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Date          | Version | Section                             | Change Summary                                                                                                                                                                       |

|---------------|---------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| November 2006 | 02.3    | DC and Switching<br>Characteristics | Corrections to MachXO "C" Sleep Mode Timing table - value for t <sub>WSLEEPN</sub> (400ns) changed from max. to min. Value for t <sub>WAWAKE</sub> (100ns) changed from min. to max. |

|               |         |                                     | Added Flash Download Time table.                                                                                                                                                     |

| December 2006 | 02.4    | Architecture                        | EBR Asynchronous Reset section added.                                                                                                                                                |

|               |         | Pinout Information                  | Power Supply and NC table: Pin/Ball orientation footnotes added.                                                                                                                     |

| February 2007 | 02.5    | Architecture                        | Updated EBR Asynchronous Reset section.                                                                                                                                              |

| August 2007   | 02.6    | DC and Switching<br>Characteristics | Updated sysIO Single-Ended DC Electrical Characteristics table.                                                                                                                      |

| November 2007 | 02.7    | DC and Switching<br>Characteristics | Added JTAG Port Timing Waveforms diagram.                                                                                                                                            |

|               |         | Pinout Information                  | Added Thermal Management text section.                                                                                                                                               |

|               |         | Supplemental<br>Information         | Updated title list.                                                                                                                                                                  |

| June 2009     | 02.8    | Introduction                        | Added 0.8-mm 256-pin caBGA package to MachXO Family Selection Guide table.                                                                                                           |

|               |         | Pinout Information                  | Added Logic Signal Connections table for 0.8-mm 256-pin caBGA package.                                                                                                               |

|               |         | Ordering Information                | Updated Part Number Description diagram and Ordering Part Number tables with 0.8-mm 256-pin caBGA package information.                                                               |

| July 2010     | 02.9    | DC and Switching<br>Characteristics | Updated sysCLOCK PLL Timing table.                                                                                                                                                   |

| June 2013     | 03.0    | All                                 | Updated document with new corporate logo.                                                                                                                                            |

|               |         | Architecture                        | Architecture Overview – Added information on the state of the register on power up and after configuration.                                                                          |

|               |         | DC and Switching<br>Characteristics | MachXO1200 and MachXO2280 Hot Socketing Specifications table – Removed footnote 4.                                                                                                   |

|               |         |                                     | Added MachXO Programming/Erase Specifications table.                                                                                                                                 |