# E.J. Lattice Semiconductor Corporation - <u>LCMXO640C-4FT256I Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Detailo                        |                                                                              |

|--------------------------------|------------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                     |

| Number of LABs/CLBs            | 80                                                                           |

| Number of Logic Elements/Cells | 640                                                                          |

| Total RAM Bits                 |                                                                              |

| Number of I/O                  | 159                                                                          |

| Number of Gates                |                                                                              |

| Voltage - Supply               | 1.71V ~ 3.465V                                                               |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                           |

| Package / Case                 | 256-LBGA                                                                     |

| Supplier Device Package        | 256-FTBGA (17x17)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lcmxo640c-4ft256i |

|                                |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

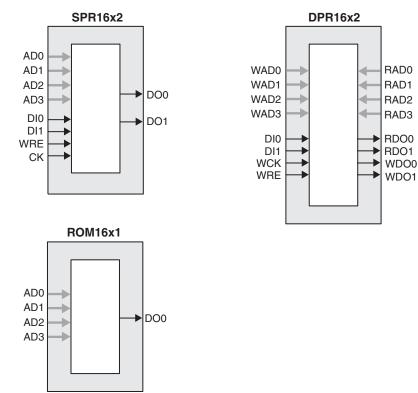

### Figure 2-6. Distributed Memory Primitives

**ROM Mode:** The ROM mode uses the same principal as the RAM modes, but without the Write port. Pre-loading is accomplished through the programming interface during configuration.

#### PFU Modes of Operation

Slices can be combined within a PFU to form larger functions. Table 2-4 tabulates these modes and documents the functionality possible at the PFU level.

| Table | 2-4. | PFU | Modes | of | Operation |

|-------|------|-----|-------|----|-----------|

|-------|------|-----|-------|----|-----------|

| Logic                      | Ripple            | RAM                        | ROM         |

|----------------------------|-------------------|----------------------------|-------------|

| LUT 4x8 or<br>MUX 2x1 x 8  | 2-bit Add x 4     | SPR16x2 x 4<br>DPR16x2 x 2 | ROM16x1 x 8 |

| LUT 5x4 or<br>MUX 4x1 x 4  | 2-bit Sub x 4     | SPR16x4 x 2<br>DPR16x4 x 1 | ROM16x2 x 4 |

| LUT 6x 2 or<br>MUX 8x1 x 2 | 2-bit Counter x 4 | SPR16x8 x 1                | ROM16x4 x 2 |

| LUT 7x1 or<br>MUX 16x1 x 1 | 2-bit Comp x 4    |                            | ROM16x8 x 1 |

## Routing

There are many resources provided in the MachXO devices to route signals individually or as buses with related control signals. The routing resources consist of switching circuitry, buffers and metal interconnect (routing) segments.

The inter-PFU connections are made with three different types of routing resources: x1 (spans two PFUs), x2 (spans three PFUs) and x6 (spans seven PFUs). The x1, x2, and x6 connections provide fast and efficient connections in the horizontal and vertical directions.

The EBR memory supports three forms of write behavior for single or dual port operation:

- 1. **Normal** data on the output appears only during the read cycle. During a write cycle, the data (at the current address) does not appear on the output. This mode is supported for all data widths.

- 2. Write Through a copy of the input data appears at the output of the same port. This mode is supported for all data widths.

- 3. **Read-Before-Write** when new data is being written, the old contents of the address appears at the output. This mode is supported for x9, x18 and x36 data widths.

#### **FIFO Configuration**

The FIFO has a write port with Data-in, CEW, WE and CLKW signals. There is a separate read port with Data-out, RCE, RE and CLKR signals. The FIFO internally generates Almost Full, Full, Almost Empty and Empty Flags. The Full and Almost Full flags are registered with CLKW. The Empty and Almost Empty flags are registered with CLKR. The range of programming values for these flags are in Table 2-7.

Table 2-7. Programmable FIFO Flag Ranges

| Flag Name         | Programming Range              |

|-------------------|--------------------------------|

| Full (FF)         | 1 to (up to 2 <sup>N</sup> -1) |

| Almost Full (AF)  | 1 to Full-1                    |

| Almost Empty (AE) | 1 to Full-1                    |

| Empty (EF)        | 0                              |

|                   | ·                              |

N = Address bit width

The FIFO state machine supports two types of reset signals: RSTA and RSTB. The RSTA signal is a global reset that clears the contents of the FIFO by resetting the read/write pointer and puts the FIFO flags in their initial reset state. The RSTB signal is used to reset the read pointer. The purpose of this reset is to retransmit the data that is in the FIFO. In these applications it is important to keep careful track of when a packet is written into or read from the FIFO.

#### Memory Core Reset

The memory array in the EBR utilizes latches at the A and B output ports. These latches can be reset asynchronously. RSTA and RSTB are local signals, which reset the output latches associated with Port A and Port B respectively. The Global Reset (GSRN) signal resets both ports. The output data latches and associated resets for both ports are as shown in Figure 2-13.

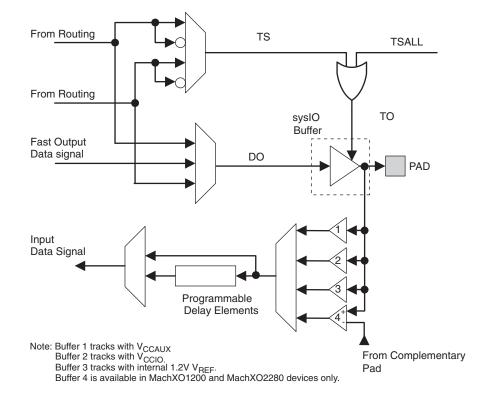

output data signals are multiplexed and provide a single signal to the I/O pin via the sysIO buffer. Figure 2-17 shows the MachXO PIO logic.

The tristate control signal is multiplexed from the output data signals and their complements. In addition a global signal (TSALL) from a dedicated pad can be used to tristate the sysIO buffer.

The PIO receives an input signal from the pin via the sysIO buffer and provides this signal to the core of the device. In addition there are programmable elements that can be utilized by the design tools to avoid positive hold times.

#### Figure 2-17. MachXO PIO Block Diagram

## sysIO Buffer

Each I/O is associated with a flexible buffer referred to as a sysIO buffer. These buffers are arranged around the periphery of the device in groups referred to as Banks. The sysIO buffers allow users to implement the wide variety of standards that are found in today's systems including LVCMOS, TTL, BLVDS, LVDS and LVPECL.

In the MachXO devices, single-ended output buffers and ratioed input buffers (LVTTL, LVCMOS and PCI) are powered using  $V_{CCIO}$ . In addition to the Bank  $V_{CCIO}$  supplies, the MachXO devices have a  $V_{CC}$  core logic power supply, and a  $V_{CCAUX}$  supply that powers up a variety of internal circuits including all the differential and referenced input buffers.

MachXO256 and MachXO640 devices contain single-ended input buffers and single-ended output buffers with complementary outputs on all the I/O Banks.

MachXO1200 and MachXO2280 devices contain two types of sysIO buffer pairs.

#### 1. Top and Bottom sysIO Buffer Pairs

The sysIO buffer pairs in the top and bottom Banks of the device consist of two single-ended output drivers and two sets of single-ended input buffers (for ratioed or absolute input levels). The I/O pairs on the top and bottom

#### Table 2-10. Supported Output Standards

| Output Standard          | Drive                | V <sub>CCIO</sub> (Typ.) |

|--------------------------|----------------------|--------------------------|

| Single-ended Interfaces  |                      |                          |

| LVTTL                    | 4mA, 8mA, 12mA, 16mA | 3.3                      |

| LVCMOS33                 | 4mA, 8mA, 12mA, 14mA | 3.3                      |

| LVCMOS25                 | 4mA, 8mA, 12mA, 14mA | 2.5                      |

| LVCMOS18                 | 4mA, 8mA, 12mA, 14mA | 1.8                      |

| LVCMOS15                 | 4mA, 8mA             | 1.5                      |

| LVCMOS12                 | 2mA, 6mA             | 1.2                      |

| LVCMOS33, Open Drain     | 4mA, 8mA, 12mA, 14mA | <b>—</b>                 |

| LVCMOS25, Open Drain     | 4mA, 8mA, 12mA, 14mA | —                        |

| LVCMOS18, Open Drain     | 4mA, 8mA, 12mA, 14mA | —                        |

| LVCMOS15, Open Drain     | 4mA, 8mA             | <b>—</b>                 |

| LVCMOS12, Open Drain     | 2mA, 6mA             | <b>—</b>                 |

| PCI33 <sup>3</sup>       | N/A                  | 3.3                      |

| Differential Interfaces  |                      |                          |

| LVDS <sup>1, 2</sup>     | N/A                  | 2.5                      |

| BLVDS, RSDS <sup>2</sup> | N/A                  | 2.5                      |

| LVPECL <sup>2</sup>      | N/A                  | 3.3                      |

1. MachXO1200 and MachXO2280 devices have dedicated LVDS buffers.

2. These interfaces can be emulated with external resistors in all devices.

3. Top Banks of MachXO1200 and MachXO2280 devices only.

### sysIO Buffer Banks

The number of Banks vary between the devices of this family. Eight Banks surround the two larger devices, the MachXO1200 and MachXO2280 (two Banks per side). The MachXO640 has four Banks (one Bank per side). The smallest member of this family, the MachXO256, has only two Banks.

Each sysIO buffer Bank is capable of supporting multiple I/O standards. Each Bank has its own I/O supply voltage ( $V_{CCIO}$ ) which allows it to be completely independent from the other Banks. Figure 2-18, Figure 2-18, Figure 2-20 and Figure 2-21 shows the sysIO Banks and their associated supplies for all devices.

the system. These capabilities make the MachXO ideal for many multiple power supply and hot-swap applications.

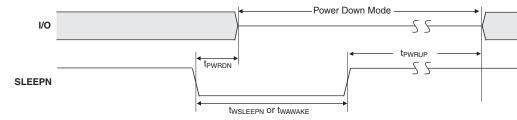

## Sleep Mode

The MachXO "C" devices ( $V_{CC} = 1.8/2.5/3.3V$ ) have a sleep mode that allows standby current to be reduced dramatically during periods of system inactivity. Entry and exit to Sleep mode is controlled by the SLEEPN pin.

During Sleep mode, the logic is non-operational, registers and EBR contents are not maintained, and I/Os are tristated. Do not enter Sleep mode during device programming or configuration operation. In Sleep mode, power supplies are in their normal operating range, eliminating the need for external switching of power supplies. Table 2-11 compares the characteristics of Normal, Off and Sleep modes.

| Characteristic                  | Normal        | Off             | Sleep           |

|---------------------------------|---------------|-----------------|-----------------|

| SLEEPN Pin                      | High          | —               | Low             |

| Static Icc                      | Typical <10mA | 0               | Typical <100uA  |

| I/O Leakage                     | <10µA         | <1mA            | <10µA           |

| Power Supplies VCC/VCCIO/VCCAUX | Normal Range  | 0               | Normal Range    |

| Logic Operation                 | User Defined  | Non Operational | Non operational |

| I/O Operation                   | User Defined  | Tri-state       | Tri-state       |

| JTAG and Programming circuitry  | Operational   | Non-operational | Non-operational |

| EBR Contents and Registers      | Maintained    | Non-maintained  | Non-maintained  |

Table 2-11. Characteristics of Normal, Off and Sleep Modes

## **SLEEPN Pin Characteristics**

The SLEEPN pin behaves as an LVCMOS input with the voltage standard appropriate to the VCC supply for the device. This pin also has a weak pull-up, along with a Schmidt trigger and glitch filter to prevent false triggering. An external pull-up to VCC is recommended when Sleep Mode is not used to ensure the device stays in normal operation mode. Typically, the device enters sleep mode several hundred nanoseconds after SLEEPN is held at a valid low and restarts normal operation as specified in the Sleep Mode Timing table. The AC and DC specifications portion of this data sheet shows a detailed timing diagram.

## Oscillator

Every MachXO device has an internal CMOS oscillator. The oscillator can be routed as an input clock to the clock tree or to general routing resources. The oscillator frequency can be divided by internal logic. There is a dedicated programming bit to enable/disable the oscillator. The oscillator frequency ranges from 18MHz to 26MHz.

## **Configuration and Testing**

The following section describes the configuration and testing features of the MachXO family of devices.

## IEEE 1149.1-Compliant Boundary Scan Testability

All MachXO devices have boundary scan cells that are accessed through an IEEE 1149.1 compliant test access port (TAP). This allows functional testing of the circuit board, on which the device is mounted, through a serial scan path that can access all critical logic nodes. Internal registers are linked internally, allowing test data to be shifted in and loaded directly onto test nodes, or test data to be captured and shifted out for verification. The test access port consists of dedicated I/Os: TDI, TDO, TCK and TMS. The test access port shares its power supply with one of the VCCIO Banks (MachXO256:  $V_{CCIO1}$ ; MachXO640:  $V_{CCIO2}$ ; MachXO1200 and MachXO2280:  $V_{CCIO5}$ ) and can operate with LVCMOS3.3, 2.5, 1.8, 1.5, and 1.2 standards.

For more details on boundary scan test, please see information regarding additional technical documentation at the end of this data sheet.

## **Device Configuration**

All MachXO devices contain a test access port that can be used for device configuration and programming.

The non-volatile memory in the MachXO can be configured in two different modes:

- In IEEE 1532 mode via the IEEE 1149.1 port. In this mode, the device is off-line and I/Os are controlled by BSCAN registers.

- In background mode via the IEEE 1149.1 port. This allows the device to remain operational in user mode while reprogramming takes place.

The SRAM configuration memory can be configured in three different ways:

- At power-up via the on-chip non-volatile memory.

- After a refresh command is issued via the IEEE 1149.1 port.

- In IEEE 1532 mode via the IEEE 1149.1 port.

Figure 2-22 provides a pictorial representation of the different programming modes available in the MachXO devices. On power-up, the SRAM is ready to be configured with IEEE 1149.1 serial TAP port using IEEE 1532 protocols.

#### Leave Alone I/O

When using IEEE 1532 mode for non-volatile memory programming, SRAM configuration, or issuing a refresh command, users may specify I/Os as high, low, tristated or held at current value. This provides excellent flexibility for implementing systems where reconfiguration or reprogramming occurs on-the-fly.

#### TransFR (Transparent Field Reconfiguration)

TransFR (TFR) is a unique Lattice technology that allows users to update their logic in the field without interrupting system operation using a single ispVM command. See TN1087, <u>Minimizing System Interruption During Configura-</u> tion Using TransFR Technology for details.

#### Security

The MachXO devices contain security bits that, when set, prevent the readback of the SRAM configuration and non-volatile memory spaces. Once set, the only way to clear the security bits is to erase the memory space.

For more information on device configuration, please see details of additional technical documentation at the end of this data sheet.

# MachXO External Switching Characteristics<sup>1</sup>

|                       |                                                                          |           | -    | 5    | -    | 4    | -    | 3    |       |  |

|-----------------------|--------------------------------------------------------------------------|-----------|------|------|------|------|------|------|-------|--|

| Parameter             | Description                                                              | Device    | Min. | Max. | Min. | Max. | Min. | Max. | Units |  |

| General I/O           | General I/O Pin Parameters (Using Global Clock without PLL) <sup>1</sup> |           |      |      |      |      |      |      |       |  |

|                       |                                                                          | LCMXO256  | _    | 3.5  | —    | 4.2  | —    | 4.9  | ns    |  |

| •                     | Best Case t <sub>PD</sub> Through 1 LUT                                  | LCMXO640  | _    | 3.5  | —    | 4.2  | —    | 4.9  | ns    |  |

| t <sub>PD</sub>       |                                                                          | LCMXO1200 | _    | 3.6  | —    | 4.4  | —    | 5.1  | ns    |  |

|                       |                                                                          | LCMXO2280 |      | 3.6  | —    | 4.4  | —    | 5.1  | ns    |  |

|                       |                                                                          | LCMXO256  |      | 4.0  | —    | 4.8  | —    | 5.6  | ns    |  |

| +                     | Best Case Clock to Output - From PFU                                     | LCMXO640  | _    | 4.0  | —    | 4.8  | —    | 5.7  | ns    |  |

| t <sub>CO</sub>       | Best Case Clock to Output - FIOIII FFO                                   | LCMXO1200 | _    | 4.3  | —    | 5.2  | —    | 6.1  | ns    |  |

|                       |                                                                          | LCMXO2280 |      | 4.3  | —    | 5.2  | —    | 6.1  | ns    |  |

|                       |                                                                          | LCMXO256  | 1.3  | —    | 1.6  | —    | 1.8  | —    | ns    |  |

| +                     | Clock to Data Setup - To PFU                                             | LCMXO640  | 1.1  | —    | 1.3  | —    | 1.5  | —    | ns    |  |

| t <sub>SU</sub>       | Clock to Data Setup - To PPO                                             | LCMXO1200 | 1.1  | —    | 1.3  | —    | 1.6  | —    | ns    |  |

|                       |                                                                          | LCMXO2280 | 1.1  | —    | 1.3  | —    | 1.5  | —    | ns    |  |

|                       |                                                                          | LCMXO256  | -0.3 | —    | -0.3 | —    | -0.3 | —    | ns    |  |

| +                     | Clock to Data Hold - To PFU                                              | LCMXO640  | -0.1 | —    | -0.1 |      | -0.1 | _    | ns    |  |

| t <sub>H</sub>        |                                                                          | LCMXO1200 | 0.0  | —    | 0.0  | —    | 0.0  | —    | ns    |  |

|                       |                                                                          | LCMXO2280 | -0.4 | —    | -0.4 |      | -0.4 | —    | ns    |  |

|                       |                                                                          | LCMXO256  |      | 600  | —    | 550  | —    | 500  | MHz   |  |

| f                     | Clock Frequency of I/O and PFU Register                                  | LCMXO640  |      | 600  | —    | 550  | —    | 500  | MHz   |  |

| f <sub>MAX_IO</sub>   | Clock Frequency of I/O and FFO Register                                  | LCMXO1200 | _    | 600  | —    | 550  |      | 500  | MHz   |  |

|                       |                                                                          | LCMXO2280 | _    | 600  | —    | 550  | —    | 500  | MHz   |  |

|                       |                                                                          | LCMXO256  | _    | 200  | —    | 220  | —    | 240  | ps    |  |

| +.                    | Global Clock Skew Across Device                                          | LCMXO640  |      | 200  | —    | 220  | —    | 240  | ps    |  |

| t <sub>SKEW_PRI</sub> | GIODAI GIOCK SKEW ACIOSS DEVICE                                          | LCMXO1200 |      | 220  | —    | 240  | —    | 260  | ps    |  |

|                       |                                                                          | LCMXO2280 | _    | 220  | —    | 240  | —    | 260  | ps    |  |

## **Over Recommended Operating Conditions**

1. General timing numbers based on LVCMOS2.5V, 12 mA. Rev. A 0.19

# MachXO Family Timing Adders<sup>1, 2, 3</sup>

| Buffer Type         | Description           | -5    | -4    | -3    | Units |

|---------------------|-----------------------|-------|-------|-------|-------|

| Input Adjusters     |                       |       | I     | 1     |       |

| LVDS25 <sup>₄</sup> | LVDS                  | 0.44  | 0.53  | 0.61  | ns    |

| BLVDS254            | BLVDS                 | 0.44  | 0.53  | 0.61  | ns    |

| LVPECL334           | LVPECL                | 0.42  | 0.50  | 0.59  | ns    |

| LVTTL33             | LVTTL                 | 0.01  | 0.01  | 0.01  | ns    |

| LVCMOS33            | LVCMOS 3.3            | 0.01  | 0.01  | 0.01  | ns    |

| LVCMOS25            | LVCMOS 2.5            | 0.00  | 0.00  | 0.00  | ns    |

| LVCMOS18            | LVCMOS 1.8            | 0.07  | 0.08  | 0.10  | ns    |

| LVCMOS15            | LVCMOS 1.5            | 0.14  | 0.17  | 0.19  | ns    |

| LVCMOS12            | LVCMOS 1.2            | 0.40  | 0.48  | 0.56  | ns    |

| PCI33 <sup>4</sup>  | PCI                   | 0.01  | 0.01  | 0.01  | ns    |

| Output Adjusters    |                       |       |       | •     |       |

| LVDS25E             | LVDS 2.5 E            | -0.13 | -0.15 | -0.18 | ns    |

| LVDS25⁴             | LVDS 2.5              | -0.21 | -0.26 | -0.30 | ns    |

| BLVDS25             | BLVDS 2.5             | -0.03 | -0.03 | -0.04 | ns    |

| LVPECL33            | LVPECL 3.3            | 0.04  | 0.04  | 0.05  | ns    |

| LVTTL33_4mA         | LVTTL 4mA drive       | 0.04  | 0.04  | 0.05  | ns    |

| LVTTL33_8mA         | LVTTL 8mA drive       | 0.06  | 0.07  | 0.08  | ns    |

| LVTTL33_12mA        | LVTTL 12mA drive      | -0.01 | -0.01 | -0.01 | ns    |

| LVTTL33_16mA        | LVTTL 16mA drive      | 0.50  | 0.60  | 0.70  | ns    |

| LVCMOS33_4mA        | LVCMOS 3.3 4mA drive  | 0.04  | 0.04  | 0.05  | ns    |

| LVCMOS33_8mA        | LVCMOS 3.3 8mA drive  | 0.06  | 0.07  | 0.08  | ns    |

| LVCMOS33_12mA       | LVCMOS 3.3 12mA drive | -0.01 | -0.01 | -0.01 | ns    |

| LVCMOS33_14mA       | LVCMOS 3.3 14mA drive | 0.50  | 0.60  | 0.70  | ns    |

| LVCMOS25_4mA        | LVCMOS 2.5 4mA drive  | 0.05  | 0.06  | 0.07  | ns    |

| LVCMOS25_8mA        | LVCMOS 2.5 8mA drive  | 0.10  | 0.12  | 0.13  | ns    |

| LVCMOS25_12mA       | LVCMOS 2.5 12mA drive | 0.00  | 0.00  | 0.00  | ns    |

| LVCMOS25_14mA       | LVCMOS 2.5 14mA drive | 0.34  | 0.40  | 0.47  | ns    |

| LVCMOS18_4mA        | LVCMOS 1.8 4mA drive  | 0.11  | 0.13  | 0.15  | ns    |

| LVCMOS18_8mA        | LVCMOS 1.8 8mA drive  | 0.05  | 0.06  | 0.06  | ns    |

| LVCMOS18_12mA       | LVCMOS 1.8 12mA drive | -0.06 | -0.07 | -0.08 | ns    |

| LVCMOS18_14mA       | LVCMOS 1.8 14mA drive | 0.06  | 0.07  | 0.09  | ns    |

| LVCMOS15_4mA        | LVCMOS 1.5 4mA drive  | 0.15  | 0.19  | 0.22  | ns    |

| LVCMOS15_8mA        | LVCMOS 1.5 8mA drive  | 0.05  | 0.06  | 0.07  | ns    |

| LVCMOS12_2mA        | LVCMOS 1.2 2mA drive  | 0.26  | 0.31  | 0.36  | ns    |

| LVCMOS12_6mA        | LVCMOS 1.2 6mA drive  | 0.05  | 0.06  | 0.07  | ns    |

| PCI33⁴              | PCI33                 | 1.85  | 2.22  | 2.59  | ns    |

### **Over Recommended Operating Conditions**

1. Timing adders are characterized but not tested on every device.

2. LVCMOS timing is measured with the load specified in Switching Test Conditions table.

3. All other standards tested according to the appropriate specifications.

4. I/O standard only available in LCMXO1200 and LCMXO2280 devices.

Rev. A 0.19

## MachXO "C" Sleep Mode Timing

| Symbol               | Parameter                 | Device    | Min. | Тур. | Max  | Units |

|----------------------|---------------------------|-----------|------|------|------|-------|

| t <sub>PWRDN</sub>   | SLEEPN Low to Power Down  | All       |      | —    | 400  | ns    |

|                      |                           | LCMXO256  | _    | —    | 400  | μs    |

| •                    | OLEEDN Lligh to Device Up | LCMXO640  | _    | —    | 600  | μs    |

| <sup>I</sup> PWRUP   | SLEEPN High to Power Up   | LCMXO1200 | _    | —    | 800  | μs    |

|                      |                           | LCMXO2280 | _    | —    | 1000 | μs    |

| t <sub>WSLEEPN</sub> | SLEEPN Pulse Width        | All       | 400  | —    | —    | ns    |

| t <sub>WAWAKE</sub>  | SLEEPN Pulse Rejection    | All       |      | —    | 100  | ns    |

Rev. A 0.19

## **Flash Download Time**

| Symbol               | Parameter                   |           | Min. | Тур. | Max. | Units |

|----------------------|-----------------------------|-----------|------|------|------|-------|

|                      | LCMXO256                    | —         |      | 0.4  | ms   |       |

| 1                    | (later of the two supplies) | LCMXO640  | —    |      | 0.6  | ms    |

| <sup>I</sup> REFRESH |                             | LCMXO1200 | —    |      | 0.8  | ms    |

|                      |                             | LCMXO2280 | —    |      | 1.0  | ms    |

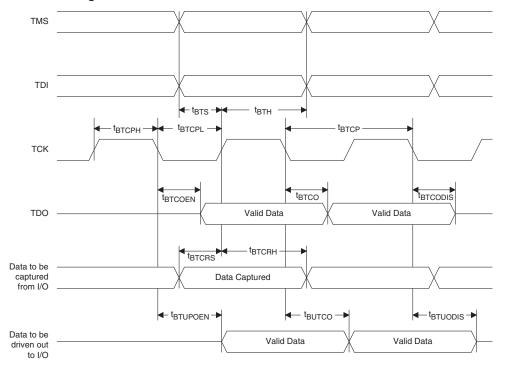

## **JTAG Port Timing Specifications**

| Symbol               | Parameter                                                            | Min. | Max. | Units |

|----------------------|----------------------------------------------------------------------|------|------|-------|

| f <sub>MAX</sub>     | TCK [BSCAN] clock frequency                                          | —    | 25   | MHz   |

| t <sub>BTCP</sub>    | TCK [BSCAN] clock pulse width                                        | 40   | —    | ns    |

| <sup>t</sup> втсрн   | TCK [BSCAN] clock pulse width high                                   | 20   | —    | ns    |

| t <sub>BTCPL</sub>   | TCK [BSCAN] clock pulse width low                                    | 20   | _    | ns    |

| t <sub>BTS</sub>     | TCK [BSCAN] setup time                                               | 8    |      | ns    |

| t <sub>втн</sub>     | TCK [BSCAN] hold time                                                | 10   | —    | ns    |

| t <sub>BTRF</sub>    | TCK [BSCAN] rise/fall time                                           | 50   | —    | mV/ns |

| t <sub>втсо</sub>    | TAP controller falling edge of clock to output valid                 |      | 10   | ns    |

| t <sub>BTCODIS</sub> | CODIS TAP controller falling edge of clock to output disabled        |      | 10   | ns    |

| t <sub>BTCOEN</sub>  | TAP controller falling edge of clock to output enabled               | —    | 10   | ns    |

| t <sub>BTCRS</sub>   | BSCAN test capture register setup time                               | 8    | —    | ns    |

| t <sub>BTCRH</sub>   | BSCAN test capture register hold time                                | 25   | —    | ns    |

| t <sub>BUTCO</sub>   | BSCAN test update register, falling edge of clock to output valid    | —    | 25   | ns    |

| t <sub>BTUODIS</sub> | BSCAN test update register, falling edge of clock to output disabled | —    | 25   | ns    |

| <sup>t</sup> BTUPOEN | BSCAN test update register, falling edge of clock to output enabled  | —    | 25   | ns    |

|                      |                                                                      |      |      |       |

Rev. A 0.19

Figure 3-5. JTAG Port Timing Waveforms

## **Power Supply and NC**

| Signal           | 100 TQFP <sup>1</sup>                                                                                                                                   | 144 TQFP <sup>1</sup>                                | 100 csBGA <sup>2</sup>                                                                                    |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| VCC              | LCMXO256/640: 35, 90<br>LCMXO1200/2280: 17, 35, 66, 91                                                                                                  | 21, 52, 93, 129                                      | P7, B6                                                                                                    |

| VCCIO0           | LCMXO256: 60, 74, 92<br>LCMXO640: 80, 92<br>LCMXO1200/2280: 94                                                                                          | LCMXO640: 117, 135<br>LCMXO1200/2280: 135            | LCMXO256: H14, A14, B5<br>LCMXO640: B12, B5                                                               |

| VCCIO1           | LCMXO256: 10, 24, 41<br>LCMXO640: 60, 74<br>LCMXO1200/2280: 80                                                                                          | LCMXO640: 82, 98<br>LCMXO1200/2280: 117              | LCMXO256: G1, P1, P10<br>LCMXO640: H14, A14                                                               |

| VCCIO2           | LCMXO256: None<br>LCMXO640: 29, 41<br>LCMXO1200/2280: 70                                                                                                | LCMXO640: 38, 63<br>LCMXO1200/2280: 98               | LCMXO256: None<br>LCMXO640: P4, P10                                                                       |

| VCCIO3           | LCMXO256: None<br>LCMXO640: 10, 24<br>LCMXO1200/2280: 56                                                                                                | LCMXO640: 10, 26<br>LCMXO1200/2280: 82               | LCMXO256: None<br>LCMXO640: G1, P1                                                                        |

| VCCIO4           | LCMXO256/640: None<br>LCMXO1200/2280: 44                                                                                                                | LCMXO640: None<br>LCMXO1200/2280: 63                 | -                                                                                                         |

| VCCIO5           | LCMXO256/640: None<br>LCMXO1200/2280: 27                                                                                                                | LCMXO640: None<br>LCMXO1200/2280: 38                 | —                                                                                                         |

| VCCIO6           | LCMXO256/640: None<br>LCMXO1200/2280: 20                                                                                                                | LCMXO640: None<br>LCMXO1200/2280: 26                 | —                                                                                                         |

| VCCIO7           | LCMXO256/640: None<br>LCMXO1200/2280: 6                                                                                                                 | LCMXO640: None<br>LCMXO1200/2280: 10                 | —                                                                                                         |

| VCCAUX           | LCMXO256/640: 88<br>LCMXO1200/2280: 36, 90                                                                                                              | 53, 128                                              | B7                                                                                                        |

| GND <sup>3</sup> | LCMXO256: 40, 84, 62, 75, 93, 12,<br>25, 42<br>LCMXO640: 40, 84, 81, 93, 62, 75,<br>30, 42, 12, 25<br>LCMXO1200/2280: 9, 41, 59, 83,<br>100, 76, 50, 26 | 16, 59, 88, 123, 118, 136, 83, 99,<br>37, 64, 11, 27 | LCMXO256: N9, B9, G14, B13,<br>A4, H1, N2, N10<br>LCMXO640: N9, B9, A10, A4,<br>G14, B13, N3, N10, H1, N2 |

| NC <sup>4</sup>  |                                                                                                                                                         |                                                      | —                                                                                                         |

1. Pin orientation follows the conventional order from pin 1 marking of the top side view and counter-clockwise.

Pin orientation follows the contention of the top side view with alphabetical order ascending vertically and numerical order ascending horizontally.

All grounds must be electrically connected at the board level. For fpBGA and ftBGA packages, the total number of GND balls is less than the actual number of GND logic connections from the die to the common package GND plane.

NC pins should not be connected to any active signals, VCC or GND.

# LCMXO256 and LCMXO640 Logic Signal Connections: 100 TQFP (Cont.)

|            |                  | LCM  | <b>(O256</b>     |              |                  | LCM  | XO640            |              |

|------------|------------------|------|------------------|--------------|------------------|------|------------------|--------------|

| Pin Number | Ball<br>Function | Bank | Dual<br>Function | Differential | Ball<br>Function | Bank | Dual<br>Function | Differential |

| 85         | PT4B             | 0    | PCLK0_1**        | С            | PT6B             | 0    | PCLK0_1**        |              |

| 86         | PT4A             | 0    | PCLK0_0**        | Т            | PT5B             | 0    | PCLK0_0**        | С            |

| 87         | PT3D             | 0    |                  | С            | PT5A             | 0    |                  | Т            |

| 88         | VCCAUX           | -    |                  |              | VCCAUX           | -    |                  |              |

| 89         | PT3C             | 0    |                  | Т            | PT4F             | 0    |                  |              |

| 90         | VCC              | -    |                  |              | VCC              | -    |                  |              |

| 91         | PT3B             | 0    |                  | С            | PT3F             | 0    |                  |              |

| 92         | VCCIO0           | 0    |                  |              | VCCIO0           | 0    |                  |              |

| 93         | GNDIO0           | 0    |                  |              | GNDIO0           | 0    |                  |              |

| 94         | PT3A             | 0    |                  | Т            | PT3B             | 0    |                  | С            |

| 95         | PT2F             | 0    |                  | С            | PT3A             | 0    |                  | Т            |

| 96         | PT2E             | 0    |                  | Т            | PT2F             | 0    |                  | С            |

| 97         | PT2D             | 0    |                  | С            | PT2E             | 0    |                  | Т            |

| 98         | PT2C             | 0    |                  | Т            | PT2B             | 0    |                  | С            |

| 99         | PT2B             | 0    |                  | С            | PT2C             | 0    |                  |              |

| 100        | PT2A             | 0    |                  | Т            | PT2A             | 0    |                  | Т            |

\* NC for "E" devices.

\*\* Primary clock inputs are single-ended.

# LCMXO1200 and LCMXO2280 Logic Signal Connections: 100 TQFP (Cont.)

|               |                  | L    | CMXO1200         |              |                  | L    | CMXO2280         |              |

|---------------|------------------|------|------------------|--------------|------------------|------|------------------|--------------|

| Pin<br>Number | Ball<br>Function | Bank | Dual<br>Function | Differential | Ball<br>Function | Bank | Dual<br>Function | Differential |

| 42            | PB9A             | 4    |                  | Т            | PB12A            | 4    |                  | Т            |

| 43            | PB9B             | 4    |                  | С            | PB12B            | 4    |                  | С            |

| 44            | VCCIO4           | 4    |                  |              | VCCIO4           | 4    |                  |              |

| 45            | PB10A            | 4    |                  | Т            | PB13A            | 4    |                  | Т            |

| 46            | PB10B            | 4    |                  | С            | PB13B            | 4    |                  | С            |

| 47***         | SLEEPN           | -    | SLEEPN           |              | SLEEPN           | -    | SLEEPN           |              |

| 48            | PB11A            | 4    |                  | Т            | PB16A            | 4    |                  | Т            |

| 49            | PB11B            | 4    |                  | С            | PB16B            | 4    |                  | С            |

| 50**          | GNDIO3<br>GNDIO4 | -    |                  |              | GNDIO3<br>GNDIO4 | -    |                  |              |

| 51            | PR16B            | 3    |                  |              | PR19B            | 3    |                  |              |

| 52            | PR15B            | 3    |                  | C*           | PR18B            | 3    |                  | C*           |

| 53            | PR15A            | 3    |                  | T*           | PR18A            | 3    |                  | T*           |

| 54            | PR14B            | 3    |                  | C*           | PR17B            | 3    |                  | C*           |

| 55            | PR14A            | 3    |                  | T*           | PR17A            | 3    |                  | T*           |

| 56            | VCCIO3           | 3    |                  |              | VCCIO3           | 3    |                  |              |

| 57            | PR12B            | 3    |                  | C*           | PR15B            | 3    |                  | C*           |

| 58            | PR12A            | 3    |                  | T*           | PR15A            | 3    |                  | T*           |

| 59            | GND              | -    |                  |              | GND              | -    |                  |              |

| 60            | PR10B            | 3    |                  | C*           | PR13B            | 3    |                  | C*           |

| 61            | PR10A            | 3    |                  | T*           | PR13A            | 3    |                  | T*           |

| 62            | PR9B             | 3    |                  | C*           | PR11B            | 3    |                  | C*           |

| 63            | PR9A             | 3    |                  | T*           | PR11A            | 3    |                  | T*           |

| 64            | PR8B             | 2    |                  | C*           | PR10B            | 2    |                  | C*           |

| 65            | PR8A             | 2    |                  | T*           | PR10A            | 2    |                  | T*           |

| 66            | VCC              | -    |                  |              | VCC              | -    |                  |              |

| 67            | PR6C             | 2    |                  |              | PR8C             | 2    |                  |              |

| 68            | PR6B             | 2    |                  | C*           | PR8B             | 2    |                  | C*           |

| 69            | PR6A             | 2    |                  | T*           | PR8A             | 2    |                  | T*           |

| 70            | VCCIO2           | 2    |                  |              | VCCIO2           | 2    |                  |              |

| 71            | PR4D             | 2    |                  |              | PR5D             | 2    |                  |              |

| 72            | PR4B             | 2    |                  | C*           | PR5B             | 2    |                  | C*           |

| 73            | PR4A             | 2    |                  | Τ*           | PR5A             | 2    |                  | Τ*           |

| 74            | PR2B             | 2    |                  | С            | PR3B             | 2    |                  | C*           |

| 75            | PR2A             | 2    |                  | Т            | PR3A             | 2    |                  | T*           |

| 76**          | GNDIO1<br>GNDIO2 | -    |                  |              | GNDIO1<br>GNDIO2 | -    |                  |              |

| 77            | PT11C            | 1    |                  |              | PT15C            | 1    |                  |              |

| 78            | PT11B            | 1    |                  | С            | PT14B            | 1    |                  | С            |

| 79            | PT11A            | 1    |                  | Т            | PT14A            | 1    |                  | Т            |

| 80            | VCCIO1           | 1    |                  |              | VCCIO1           | 1    |                  |              |

| 81            | PT9E             | 1    |                  |              | PT12D            | 1    |                  | С            |

# LCMXO256 and LCMXO640 Logic Signal Connections: 100 csBGA (Cont.)

|                |                  | LCMXO256 |                  |                   |                |                  | LCMXO640 | )                |                   |

|----------------|------------------|----------|------------------|-------------------|----------------|------------------|----------|------------------|-------------------|

| Ball<br>Number | Ball<br>Function | Bank     | Dual<br>Function | Differen-<br>tial | Ball<br>Number | Ball<br>Function | Bank     | Dual<br>Function | Differen-<br>tial |

| A4             | GNDIO0           | 0        |                  |                   | A4             | GNDIO0           | 0        |                  |                   |

| B4             | PT3A             | 0        |                  | Т                 | B4             | PT3B             | 0        |                  | С                 |

| A3             | PT2F             | 0        |                  | С                 | A3             | PT3A             | 0        |                  | Т                 |

| B3             | PT2E             | 0        |                  | Т                 | B3             | PT2F             | 0        |                  | С                 |

| A2             | PT2D             | 0        |                  | С                 | A2             | PT2E             | 0        |                  | Т                 |

| C3             | PT2C             | 0        |                  | Т                 | C3             | PT2B             | 0        |                  | С                 |

| A1             | PT2B             | 0        |                  | С                 | A1             | PT2C             | 0        |                  |                   |

| B2             | PT2A             | 0        |                  | Т                 | B2             | PT2A             | 0        |                  | Т                 |

| N9             | GND              | -        |                  |                   | N9             | GND              | -        |                  |                   |

| B9             | GND              | -        |                  |                   | B9             | GND              | -        |                  |                   |

| B5             | VCCIO0           | 0        |                  |                   | B5             | VCCIO0           | 0        |                  |                   |

| A14            | VCCIO0           | 0        |                  |                   | A14            | VCCIO1           | 1        |                  |                   |

| H14            | VCCIO0           | 0        |                  |                   | H14            | VCCIO1           | 1        |                  |                   |

| P10            | VCCIO1           | 1        |                  |                   | P10            | VCCIO2           | 2        |                  |                   |

| G1             | VCCIO1           | 1        |                  |                   | G1             | VCCIO3           | 3        |                  |                   |

| P1             | VCCIO1           | 1        |                  |                   | P1             | VCCIO3           | 3        |                  |                   |

\*NC for "E" devices.

\*\*Primary clock inputs are single-ended.

# LCMXO640, LCMXO1200 and LCMXO2280 Logic Signal Connections: 132 csBGA

|          |                  | LCM  | XO640            |              |          |                  | LC               | MXO1200          |              |          |                  | LC           | CMXO2280         |              |

|----------|------------------|------|------------------|--------------|----------|------------------|------------------|------------------|--------------|----------|------------------|--------------|------------------|--------------|

| Ball #   | Ball<br>Function | Bonk | Dual<br>Function | Differential | Ball #   | Ball<br>Function | Bonk             | Dual<br>Function | Differential | Ball #   | Ball<br>Function | Bonk         | Dual<br>Function | Differential |

| B1       | PL2A             | З    | Function         | T            | Ball #   | PL2A             | <b>Бапк</b><br>7 | Function         | T            | Ball #   | PL2A             | <b>Darik</b> | LUM0_PLLT_FB_A   | T            |

| C1       | PL2B             | 3    |                  | C            | C1       | PL3C             | 7                |                  | T            | C1       | PL3C             | 7            | LUM0_PLLT_IN_A   | T            |

| B2       | PL2C             | 3    |                  | Т            | B2       | PL2B             | 7                |                  | C            | B2       | PL2B             | 7            | LUM0_PLLC_FB_A   | C            |

| C2       | PL2D             | 3    |                  | C            | C2       | PL4A             | 7                |                  | T*           | C2       | PL4A             | 7            |                  | T*           |

| C2       | PL3A             | 3    |                  | Т            | C2       | PL3D             | 7                |                  | C            | C2       | PL3D             | 7            | LUM0_PLLC_IN_A   | C            |

| D1       | PL3B             | 3    |                  | C            | D1       | PL4B             | 7                |                  | C*           | D1       | PL4B             | 7            |                  | C*           |

| D3       | PL3D             | 3    |                  | 0            | D3       | PL4C             | 7                |                  | Ŭ            | D3       | PL4C             | 7            |                  | 0            |

| E1       | GNDIO3           | 3    |                  |              | E1       | GNDIO7           | 7                |                  |              | E1       | GNDIO7           | 7            |                  |              |

| E2       | PL5A             | 3    |                  | т            | E2       | PL6A             | 7                |                  | T*           | E2       | PL7A             | 7            |                  | T*           |

| E3       | PL5B             | 3    | GSRN             | C            | E3       | PL6B             | 7                | GSRN             | C*           | E3       | PL7B             | 7            | GSRN             | C*           |

| F2       | PL5D             | 3    | CONN             | 0            | F2       | PL6D             | 7                | CONN             | Ŭ            | F2       | PL7D             | 7            | CONN             | 0            |

| F3       | PL6B             | 3    |                  |              | F3       | PL7C             | 7                |                  | т            | F3       | PL9C             | 7            |                  | т            |

| G1       | PL6C             | 3    |                  | т            | G1       | PL7D             | 7                |                  | C            | G1       | PL9D             | 7            |                  | C            |

| G2       | PL6D             | 3    |                  | C            | G2       | PL8C             | 7                |                  | Т            | G2       | PL10C            | 7            |                  | Т            |

| G2<br>G3 | PL6D<br>PL7A     | 3    |                  | Т            | G2<br>G3 | PL8C             | 7                |                  | C            | G2<br>G3 | PL10C            | 7            |                  | C            |

| H2       | PL7A<br>PL7B     | 3    |                  | C            | H2       | PL8D<br>PL10A    | 6                |                  | C<br>T*      | H2       | PL10D<br>PL12A   | 6            |                  | C<br>T*      |

| H1       | PL7B<br>PL7C     | 3    |                  | C            | п2<br>Н1 | PL10A<br>PL10B   | 6                |                  | C*           | ⊓2<br>H1 | PL12A<br>PL12B   | 6            |                  | C*           |

|          |                  | -    |                  |              |          | VCC              |                  |                  | C            |          |                  | -            |                  | C            |

| H3       | VCC              |      |                  |              | H3       |                  | -                |                  |              | H3       | VCC              |              |                  | 0            |

| J1       | PL8A             | 3    | TOALL            |              | J1       | PL11B            | 6                | TOALL            | т            | J1       | PL14D            | 6            | TOALL            | C<br>T       |

| J2       | PL8C             | 3    | TSALL            | -            | J2       | PL11C            | 6                | TSALL            |              | J2       | PL14C            | 6            | TSALL            | 1            |

| J3       | PL9A             | 3    |                  | Т            | J3       | PL11D            | 6                |                  | C            | J3       | PL14B            | 6            |                  |              |

| K2       | PL9B             | 3    |                  | С            | K2       | PL12A            | 6                |                  | T*           | K2       | PL15A            | 6            |                  | T*           |

| K1       | PL9C             | 3    |                  |              | K1       | PL12B            | 6                |                  | C*           | K1       | PL15B            | 6            |                  | C*           |

| L2       | GNDIO3           | 3    |                  |              | L2       | GNDIO6           | 6                |                  |              | L2       | GNDIO6           | 6            |                  |              |

| L1       | PL10A            | 3    |                  | Т            | L1       | PL14A            | 6                | LLM0_PLLT_FB_A   | T*           | L1       | PL17A            | 6            | LLM0_PLLT_FB_A   | T*           |

| L3       | PL10B            | 3    |                  | С            | L3       | PL14B            | 6                | LLM0_PLLC_FB_A   | C*           | L3       | PL17B            | 6            | LLM0_PLLC_FB_A   | C*           |

| M1       | PL11A            | 3    |                  | Т            | M1       | PL15A            | 6                | LLM0_PLLT_IN_A   | T*           | M1       | PL18A            | 6            | LLM0_PLLT_IN_A   | T*           |

| N1       | PL11B            | 3    |                  | С            | N1       | PL16A            | 6                |                  | Т            | N1       | PL19A            | 6            |                  | Т            |

| M2       | PL11C            | 3    |                  | Т            | M2       | PL15B            | 6                | LLM0_PLLC_IN_A   | C*           | M2       | PL18B            | 6            | LLM0_PLLC_IN_A   | C*           |

| P1       | PL11D            | 3    |                  | С            | P1       | PL16B            | 6                |                  | С            | P1       | PL19B            | 6            |                  | С            |

| P2       | GNDIO2           | 2    |                  |              | P2       | GNDIO5           | 5                |                  |              | P2       | GNDIO5           | 5            |                  |              |

| P3       | TMS              | 2    | TMS              |              | P3       | TMS              | 5                | TMS              |              | P3       | TMS              | 5            | TMS              |              |

| M3       | PB2C             | 2    |                  | Т            | M3       | PB2C             | 5                |                  | Т            | M3       | PB2A             | 5            |                  | Т            |

| N3       | PB2D             | 2    |                  | С            | N3       | PB2D             | 5                |                  | С            | N3       | PB2B             | 5            |                  | С            |

| P4       | TCK              | 2    | TCK              |              | P4       | TCK              | 5                | ТСК              |              | P4       | TCK              | 5            | ТСК              |              |

| M4       | PB3B             | 2    |                  |              | M4       | PB3B             | 5                |                  |              | M4       | PB3B             | 5            |                  |              |

| N4       | PB3C             | 2    |                  | Т            | N4       | PB4A             | 5                |                  | Т            | N4       | PB4A             | 5            |                  | Т            |

| P5       | PB3D             | 2    |                  | С            | P5       | PB4B             | 5                |                  | С            | P5       | PB4B             | 5            |                  | С            |

| N5       | TDO              | 2    | TDO              |              | N5       | TDO              | 5                | TDO              |              | N5       | TDO              | 5            | TDO              |              |

| M5       | TDI              | 2    | TDI              |              | M5       | TDI              | 5                | TDI              |              | M5       | TDI              | 5            | TDI              |              |

| N6       | PB4E             | 2    |                  | Т            | N6       | PB5C             | 5                |                  |              | N6       | PB6C             | 5            |                  |              |

| P6       | VCC              | -    |                  |              | P6       | VCC              | -                |                  |              | P6       | VCC              | -            |                  |              |

| M6       | PB4F             | 2    |                  | С            | M6       | PB6A             | 5                |                  |              | M6       | PB8A             | 5            |                  |              |

| P7       | VCCAUX           | -    |                  |              | P7       | VCCAUX           | -                |                  |              | P7       | VCCAUX           | -            |                  |              |

| N7       | PB5A             | 2    |                  | Т            | N7       | PB6F             | 5                |                  |              | N7       | PB8F             | 5            |                  |              |

| M7       | PB5B             | 2    | PCLK2_1***       | С            | M7       | PB7B             | 4                | PCLK4_1***       |              | M7       | PB10F            | 4            | PCLK4_1***       |              |

| N8       | PB5D             | 2    |                  |              | N8       | PB7C             | 4                |                  | Т            | N8       | PB10C            | 4            |                  | Т            |

| P8       | PB6A             | 2    |                  | Т            | P8       | PB7D             | 4                |                  | С            | P8       | PB10D            | 4            |                  | С            |

| M8       | PB6B             | 2    | PCLK2_0***       | С            | M8       | PB7F             | 4                | PCLK4_0***       |              | M8       | PB10B            | 4            | PCLK4_0***       |              |

| N9       | PB7A             | 2    |                  | Т            | N9       | PB9A             | 4                |                  | Т            | N9       | PB12A            | 4            |                  | Т            |

# LCMXO640, LCMXO1200 and LCMXO2280 Logic Signal Connections: 132 csBGA (Cont.)

|            |              | LCM  | (O640    |              |            |                | LC | MXO1200  |              | LCMXO2280  |                |        |          |              |  |

|------------|--------------|------|----------|--------------|------------|----------------|----|----------|--------------|------------|----------------|--------|----------|--------------|--|

|            | Ball         |      | Dual     |              |            | Ball           |    | Dual     |              |            | Ball           |        | Dual     |              |  |

| Ball #     |              | Bank | Function | Differential | Ball #     | Function       |    | Function | Differential | Ball #     | Function       |        | Function | Differential |  |

| M9         | PB7B         | 2    |          | С            | M9         | PB9B           | 4  |          | C            | M9         | PB12B          | 4      |          | С            |  |

| N10        | PB7E         | 2    |          | Т            | N10        | PB9C           | 4  |          | Т            | N10        | PB12C          | 4      |          | Т            |  |

| P10        | PB7F         | 2    |          | С            | P10        | PB9D           | 4  |          | С            | P10        | PB12D          | 4      |          | С            |  |

| N11        | GNDIO2       | 2    |          |              | N11        | GNDIO4         | 4  |          |              | N11        | GNDIO4         | 4      |          | _            |  |

| P11        | PB8C         | 2    |          | Т            | P11        | PB10A          | 4  |          | Т            | P11        | PB13C          | 4      |          | Т            |  |

| M11        | PB8D         | 2    |          | C            | M11        | PB10B          | 4  |          | С            | M11        | PB13D          | 4      |          | С            |  |

| P12        | PB9C         | 2    |          | Т            | P12        | PB10C          | 4  |          |              | P12        | PB15B          | 4      |          |              |  |

| P13        | PB9D         | 2    |          | С            | P13        | PB11C          | 4  |          | Т            | P13        | PB16C          | 4      |          | Т            |  |

| N12**      | SLEEPN       | -    | SLEEPN   |              | N12**      | SLEEPN         | -  | SLEEPN   |              | N12**      | SLEEPN         | -      | SLEEPN   |              |  |

| P14        | PB9F         | 2    |          |              | P14        | PB11D          | 4  |          | C            | P14        | PB16D          | 4      |          | С            |  |

| N14        | PR11D        | 1    |          | С            | N14        | PR16B          | 3  |          | C            | N14        | PR19B          | 3      |          | C            |  |

| M14        | PR11C        | 1    |          | Т            | M14        | PR15B          | 3  |          | C*           | M14        | PR18B          | 3      |          | C*           |  |

| N13        | PR11B        | 1    |          | С            | N13        | PR16A          | 3  |          | T            | N13        | PR19A          | 3      |          | Т            |  |

| M12        | PR11A        | 1    |          | Т            | M12        | PR15A          | 3  |          | T*           | M12        | PR18A          | 3      |          | T*           |  |

| M13        | PR10B        | 1    |          | C            | M13        | PR14B          | 3  |          | C*           | M13        | PR17B          | 3      |          | C*           |  |

| L14        | PR10A        | 1    |          | Т            | L14        | PR14A          | 3  |          | T*           | L14        | PR17A          | 3      |          | T*           |  |

| L13        | GNDIO1       | 1    |          |              | L13        | GNDIO3         | 3  |          |              | L13        | GNDIO3         | 3      |          |              |  |

| K14        | PR8D         | 1    |          | C            | K14        | PR12B          | 3  |          | C*           | K14        | PR15B          | 3      |          | C*           |  |

| K13        | PR8C         | 1    |          | Т            | K13        | PR12A          | 3  |          | T*           | K13        | PR15A          | 3      |          | T*           |  |

| K12        | PR8B         | 1    |          | C<br>T       | K12        | PR11B          | 3  |          | C*           | K12        | PR14B          | 3      |          | C*           |  |

| J13        | PR8A         | 1    |          | Т            | J13        | PR11A          | 3  |          | T*           | J13        | PR14A          | 3      |          | T*           |  |

| J12        | PR7C         | 1    |          |              | J12        | PR10B          | 3  |          | C*           | J12        | PR13B          | 3      |          | C*           |  |

| H14        | PR7B         | 1    |          | C            | H14        | PR10A          | 3  |          | T*           | H14        | PR13A          | 3      |          | T*           |  |

| H13        | PR7A         | 1    |          | Т            | H13        | PR9B           | 3  |          | C*           | H13        | PR11B          | 3      |          | C*           |  |

| H12        | PR6D         | 1    |          | C            | H12        | PR9A           | 3  |          | T*           | H12        | PR11A          | 3      |          | T*           |  |

| G13        | PR6C         | 1    |          | Т            | G13        | PR8B           | 2  |          | C*           | G13        | PR10B          | 2      |          | C*           |  |

| G14        | PR6B<br>VCC  | 1    |          |              | G14        | PR8A<br>VCC    | 2  |          | Ι            | G14        | PR10A          | 2      |          | 1"           |  |

| G12        |              | -    |          | 0            | G12        |                | -  |          |              | G12        | VCC            |        |          |              |  |

| F14        | PR5D         | 1    |          | C<br>T       | F14        | PR6C           | 2  |          | C*           | F14        | PR8C           | 2      |          | C*           |  |

| F13<br>F12 | PR5C<br>PR4D | 1    |          | C            | F13<br>F12 | PR6B<br>PR6A   | 2  |          | T*           | F13<br>F12 | PR8B<br>PR8A   | 2      |          | T*           |  |

| E13        | PR4D<br>PR4C | 1    |          | Т            | E13        | PR5B           | 2  |          | C*           | E13        | PR7B           | 2      |          | C*           |  |

| E13        | PR4C<br>PR4B | 1    |          | 1            | E13        | PR5A           | 2  |          | T*           | E13        | PR7A           | 2      |          | T*           |  |

| D13        | GNDIO1       | 1    |          |              | D13        | GNDIO2         | 2  |          | 1            | D13        | GNDIO2         | 2      |          | 1            |  |

| D13        | PR3D         | 1    |          | С            | D13        | PR4B           | 2  |          | C*           | D13        | PR5B           | 2      |          | C*           |  |

| D14        | PR3D         | 1    |          | Т            | D14        | PR4D<br>PR4A   | 2  |          | T*           | D14        | PR5A           | 2      |          | T*           |  |

| C14        | PR2D         | 1    |          | C            | C14        | PR4A<br>PR3D   | 2  |          | C            | C14        | PR4D           | 2      |          | C            |  |

| B14        | PR2C         | 1    |          | Т            | B14        | PR2B           | 2  |          | C<br>C       | B14        | PR3B           | 2      |          | C*           |  |

| C13        | PR20         | 1    |          | C            | C13        | PR3C           | 2  |          | Т            | C13        | PR4C           | 2      |          | т            |  |

| A14        | PR26         | 1    |          | T            | A14        | PR2A           | 2  |          | T            | A14        | PR4C<br>PR3A   | 2      |          | T*           |  |

| A14        | PT9F         | 0    |          | C            | A14        | PT11D          | 1  |          | C            | A14        | PT16D          | 2<br>1 |          | C            |  |

| A13<br>A12 | PT9F<br>PT9E | 0    |          | Т            | A13<br>A12 | PT11B          | 1  |          | C<br>C       | A13<br>A12 | PT16D<br>PT16B | 1      |          | C            |  |

| B13        | PT9E<br>PT9D | 0    |          | C            | B13        | PT11B<br>PT11C | 1  |          | Т            | B13        | PT16D<br>PT16C | 1      |          | Т            |  |

| B13<br>B12 | PT9C         | 0    |          | Т            | B13<br>B12 | PT10F          | 1  |          |              | B13<br>B12 | PT15D          | 1      |          |              |  |

| C12        | PT9C<br>PT9B | 0    |          | C            | C12        | PT10F          | 1  |          | т            | C12        | PT16A          | 1      |          | Т            |  |

| A11        | PT9B<br>PT9A | 0    |          | Т            | A11        | PT11A<br>PT10D | 1  |          | C            | A11        | PT16A<br>PT14B | 1      |          | C            |  |

| C11        | PT9A<br>PT8C | 0    |          |              | C11        | PT10D<br>PT10C | 1  |          | Т            | C11        | PT14B<br>PT14A | 1      |          | Т            |  |

| A10        | GNDIO0       | 0    |          |              | A10        | GNDIO1         | 1  |          | 1            | A10        | GNDIO1         | 1      |          |              |  |

| B10        | PT7F         | 0    |          | С            | B10        | PT9F           | 1  |          | с            | B10        | PT12F          | 1      |          | с            |  |

| C10        | PT7E         | 0    |          | Т            | C10        | PT9F           | 1  |          | Т            | C10        | PT12F<br>PT12E | 1      |          | Т            |  |

| 010        | FI/E         | U    |          |              | 010        | FIAE           |    |          |              | 010        | FIIZE          |        |          |              |  |

# LCMXO640, LCMXO1200 and LCMXO2280 Logic Signal Connections: 144 TQFP (Cont.)

|               |                  | L    | CMXO640          |              |                  |      | LCMXO1200        |              |                  |      | LCMXO2280        |              |

|---------------|------------------|------|------------------|--------------|------------------|------|------------------|--------------|------------------|------|------------------|--------------|

| Pin<br>Number | Ball<br>Function | Bank | Dual<br>Function | Differential | Ball<br>Function | Bank | Dual<br>Function | Differential | Ball<br>Function | Bank | Dual<br>Function | Differential |

| 51            | TDI              | 2    | TDI              |              | TDI              | 5    | TDI              |              | TDI              | 5    | TDI              |              |

| 52            | VCC              | -    |                  |              | VCC              | -    |                  |              | VCC              | -    |                  |              |

| 53            | VCCAUX           | -    |                  |              | VCCAUX           | -    |                  |              | VCCAUX           | -    |                  |              |

| 54            | PB5A             | 2    |                  | Т            | PB6F             | 5    |                  |              | PB8F             | 5    |                  |              |

| 55            | PB5B             | 2    | PCLKT2_1***      | С            | PB7B             | 4    | PCLK4_1***       |              | PB10F            | 4    | PCLK4_1***       |              |

| 56            | PB5D             | 2    |                  |              | PB7C             | 4    |                  | Т            | PB10C            | 4    |                  | Т            |

| 57            | PB6A             | 2    |                  | Т            | PB7D             | 4    |                  | С            | PB10D            | 4    |                  | С            |

| 58            | PB6B             | 2    | PCLKT2_0***      | С            | PB7F             | 4    | PCLK4_0***       |              | PB10B            | 4    | PCLK4_0***       |              |

| 59            | GND              | -    |                  |              | GND              | -    |                  |              | GND              | -    |                  |              |

| 60            | PB7C             | 2    |                  |              | PB9A             | 4    |                  | Т            | PB12A            | 4    |                  | Т            |

| 61            | PB7E             | 2    |                  |              | PB9B             | 4    |                  | С            | PB12B            | 4    |                  | С            |

| 62            | PB8A             | 2    |                  |              | PB9E             | 4    |                  |              | PB12E            | 4    |                  |              |

| 63            | VCCIO2           | 2    |                  |              | VCCIO4           | 4    |                  |              | VCCIO4           | 4    |                  |              |

| 64            | GNDIO2           | 2    |                  |              | GNDIO4           | 4    |                  |              | GNDIO4           | 4    |                  |              |

| 65            | PB8C             | 2    |                  | Т            | PB10A            | 4    |                  | Т            | PB13A            | 4    |                  | т            |

| 66            | PB8D             | 2    |                  | C            | PB10B            | 4    |                  | C            | PB13B            | 4    |                  | C            |

| 67            | PB9A             | 2    |                  | T            | PB10C            | 4    |                  | Т            | PB13C            | 4    |                  | Т            |

| 68            | PB9C             | 2    |                  | T            | PB10D            | 4    |                  | C            | PB13D            | 4    |                  | C            |

| 69            | PB9B             | 2    |                  | C            | PB10F            | 4    |                  | Ū            | PB14D            | 4    |                  | 0            |

| 70**          | SLEEPN           | -    | SLEEPN           | Ŭ            | SLEEPN           | -    | SLEEPN           |              | SLEEPN           | -    | SLEEPN           |              |

| 70            | PB9D             | 2    | SLEEFN           | С            | PB11C            | 4    | SLEEFIN          | Т            | PB16C            | 4    | JLEEFIN          | т            |

| 71            | PB9D<br>PB9F     | 2    |                  | U            | PB11C<br>PB11D   | 4    |                  | C            | PB16C<br>PB16D   | 4    |                  | C            |

|               |                  |      |                  |              |                  |      |                  |              | -                |      |                  | c            |

| 73            | PR11D            | 1    |                  | С            | PR16B            | 3    |                  | С            | PR20B            | 3    |                  |              |

| 74            | PR11B            | 1    |                  | C            | PR16A            | 3    |                  | T            | PR20A            | 3    |                  | Т            |

| 75            | PR11C            | 1    |                  | Т            | PR15B            | 3    |                  | C*           | PR19B            | 3    |                  | С            |

| 76            | PR10D            | 1    |                  | С            | PR15A            | 3    |                  | T*           | PR19A            | 3    |                  | Т            |

| 77            | PR11A            | 1    |                  | Т            | PR14D            | 3    |                  | С            | PR17D            | 3    |                  | С            |

| 78            | PR10B            | 1    |                  | С            | PR14C            | 3    |                  | Т            | PR17C            | 3    |                  | Т            |

| 79            | PR10C            | 1    |                  | Т            | PR14B            | 3    |                  | C*           | PR17B            | 3    |                  | C*           |

| 80            | PR10A            | 1    |                  | Т            | PR14A            | 3    |                  | T*           | PR17A            | 3    |                  | T*           |

| 81            | PR9D             | 1    |                  |              | PR13D            | 3    |                  |              | PR16D            | 3    |                  |              |

| 82            | VCCIO1           | 1    |                  |              | VCCIO3           | 3    |                  |              | VCCIO3           | 3    |                  |              |

| 83            | GNDIO1           | 1    |                  |              | GNDIO3           | 3    |                  |              | GNDIO3           | 3    |                  |              |

| 84            | PR9A             | 1    |                  |              | PR12B            | 3    |                  | C*           | PR15B            | 3    |                  | C*           |

| 85            | PR8C             | 1    |                  |              | PR12A            | 3    |                  | T*           | PR15A            | 3    |                  | T*           |