Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                              |

|--------------------------------|------------------------------------------------------------------------------|

| Product Status                 | Active                                                                       |

| Number of LABs/CLBs            | 80                                                                           |

| Number of Logic Elements/Cells | 640                                                                          |

| Total RAM Bits                 | -                                                                            |

| Number of I/O                  | 74                                                                           |

| Number of Gates                | -                                                                            |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                           |

| Package / Case                 | 100-LQFP                                                                     |

| Supplier Device Package        | 100-TQFP (14x14)                                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lcmxo640e-3tn100i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## MachXO Family Data Sheet Architecture

June 2013 Data Sheet DS1002

#### **Architecture Overview**

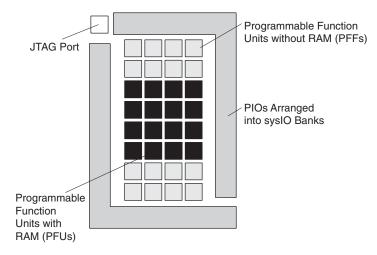

The MachXO family architecture contains an array of logic blocks surrounded by Programmable I/O (PIO). Some devices in this family have sysCLOCK PLLs and blocks of sysMEM™ Embedded Block RAM (EBRs). Figures 2-1, 2-2, and 2-3 show the block diagrams of the various family members.

The logic blocks are arranged in a two-dimensional grid with rows and columns. The EBR blocks are arranged in a column to the left of the logic array. The PIO cells are located at the periphery of the device, arranged into Banks. The PIOs utilize a flexible I/O buffer referred to as a sysIO interface that supports operation with a variety of interface standards. The blocks are connected with many vertical and horizontal routing channel resources. The place and route software tool automatically allocates these routing resources.

There are two kinds of logic blocks, the Programmable Functional Unit (PFU) and the Programmable Functional unit without RAM (PFF). The PFU contains the building blocks for logic, arithmetic, RAM, ROM, and register functions. The PFF block contains building blocks for logic, arithmetic, ROM, and register functions. Both the PFU and PFF blocks are optimized for flexibility, allowing complex designs to be implemented quickly and effectively. Logic blocks are arranged in a two-dimensional array. Only one type of block is used per row.

In the MachXO family, the number of sysIO Banks varies by device. There are different types of I/O Buffers on different Banks. See the details in later sections of this document. The sysMEM EBRs are large, dedicated fast memory blocks; these blocks are found only in the larger devices. These blocks can be configured as RAM, ROM or FIFO. FIFO support includes dedicated FIFO pointer and flag "hard" control logic to minimize LUT use.

The MachXO registers in PFU and sysl/O can be configured to be SET or RESET. After power up and device is configured, the device enters into user mode with these registers SET/RESET according to the configuration setting, allowing device entering to a known state for predictable system function.

The MachXO architecture provides up to two sysCLOCK™ Phase Locked Loop (PLL) blocks on larger devices. These blocks are located at either end of the memory blocks. The PLLs have multiply, divide, and phase shifting capabilities that are used to manage the frequency and phase relationships of the clocks.

Every device in the family has a JTAG Port that supports programming and configuration of the device as well as access to the user logic. The MachXO devices are available for operation from 3.3V, 2.5V, 1.8V, and 1.2V power supplies, providing easy integration into the overall system.

www.latticesemi.com 2-1 DS1002 Architecture\_01.5

Figure 2-3. Top View of the MachXO256 Device

#### **PFU Blocks**

The core of the MachXO devices consists of PFU and PFF blocks. The PFUs can be programmed to perform Logic, Arithmetic, Distributed RAM, and Distributed ROM functions. PFF blocks can be programmed to perform Logic, Arithmetic, and Distributed ROM functions. Except where necessary, the remainder of this data sheet will use the term PFU to refer to both PFU and PFF blocks.

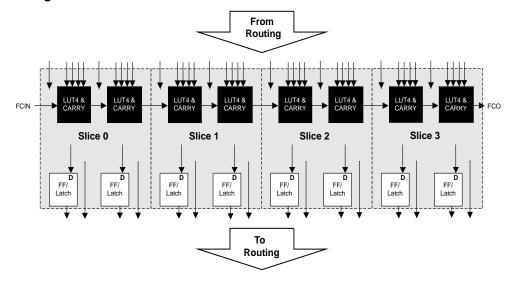

Each PFU block consists of four interconnected Slices, numbered 0-3 as shown in Figure 2-4. There are 53 inputs and 25 outputs associated with each PFU block.

Figure 2-4. PFU Diagram

#### **Slice**

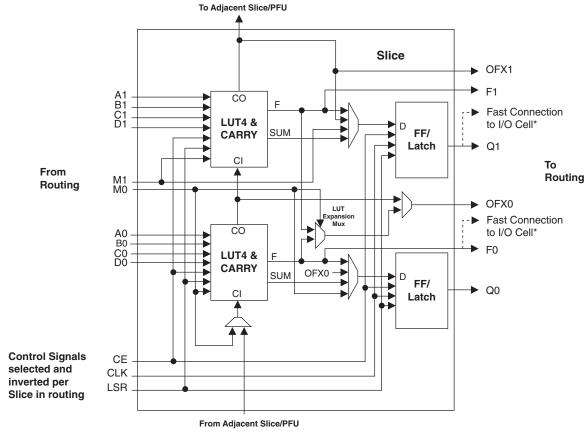

Each Slice contains two LUT4 lookup tables feeding two registers (programmed to be in FF or Latch mode), and some associated logic that allows the LUTs to be combined to perform functions such as LUT5, LUT6, LUT7, and LUT8. There is control logic to perform set/reset functions (programmable as synchronous/asynchronous), clock select, chip-select, and wider RAM/ROM functions. Figure 2-5 shows an overview of the internal logic of the Slice. The registers in the Slice can be configured for positive/negative and edge/level clocks.

There are 14 input signals: 13 signals from routing and one from the carry-chain (from the adjacent Slice/PFU). There are 7 outputs: 6 to the routing and one to the carry-chain (to the adjacent Slice/PFU). Table 2-1 lists the signals associated with each Slice.

Figure 2-5. Slice Diagram

Notes:

Some inter-Slice signals are not shown.

Table 2-1. Slice Signal Descriptions

| Function | Туре             | Signal Names   | Description                                              |

|----------|------------------|----------------|----------------------------------------------------------|

| Input    | Data signal      | A0, B0, C0, D0 | Inputs to LUT4                                           |

| Input    | Data signal      | A1, B1, C1, D1 | Inputs to LUT4                                           |

| Input    | Multi-purpose    | M0/M1          | Multipurpose Input                                       |

| Input    | Control signal   | CE             | Clock Enable                                             |

| Input    | Control signal   | LSR            | Local Set/Reset                                          |

| Input    | Control signal   | CLK            | System Clock                                             |

| Input    | Inter-PFU signal | FCIN           | Fast Carry In <sup>1</sup>                               |

| Output   | Data signals     | F0, F1         | LUT4 output register bypass signals                      |

| Output   | Data signals     | Q0, Q1         | Register Outputs                                         |

| Output   | Data signals     | OFX0           | Output of a LUT5 MUX                                     |

| Output   | Data signals     | OFX1           | Output of a LUT6, LUT7, LUT82 MUX depending on the Slice |

| Output   | Inter-PFU signal | FCO            | Fast Carry Out <sup>1</sup>                              |

- 1. See Figure 2-4 for connection details.

- 2. Requires two PFUs.

<sup>\*</sup> Only PFUs at the edges have fast connections to the I/O cell.

#### **Modes of Operation**

Each Slice is capable of four modes of operation: Logic, Ripple, RAM, and ROM. The Slice in the PFF is capable of all modes except RAM. Table 2-2 lists the modes and the capability of the Slice blocks.

Table 2-2. Slice Modes

|           | Logic              | Ripple                | RAM     | ROM          |

|-----------|--------------------|-----------------------|---------|--------------|

| PFU Slice | LUT 4x2 or LUT 5x1 | 2-bit Arithmetic Unit | SP 16x2 | ROM 16x1 x 2 |

| PFF Slice | LUT 4x2 or LUT 5x1 | 2-bit Arithmetic Unit | N/A     | ROM 16x1 x 2 |

**Logic Mode:** In this mode, the LUTs in each Slice are configured as 4-input combinatorial lookup tables (LUT4). A LUT4 can have 16 possible input combinations. Any logic function with four inputs can be generated by programming this lookup table. Since there are two LUT4s per Slice, a LUT5 can be constructed within one Slice. Larger lookup tables such as LUT6, LUT7, and LUT8 can be constructed by concatenating other Slices.

**Ripple Mode:** Ripple mode allows the efficient implementation of small arithmetic functions. In ripple mode, the following functions can be implemented by each Slice:

- Addition 2-bit

- Subtraction 2-bit

- Add/Subtract 2-bit using dynamic control

- Up counter 2-bit

- Down counter 2-bit

- Ripple mode multiplier building block

- · Comparator functions of A and B inputs

- A greater-than-or-equal-to B

- A not-equal-to B

- A less-than-or-equal-to B

Two additional signals, Carry Generate and Carry Propagate, are generated per Slice in this mode, allowing fast arithmetic functions to be constructed by concatenating Slices.

**RAM Mode:** In this mode, distributed RAM can be constructed using each LUT block as a 16x2-bit memory. Through the combination of LUTs and Slices, a variety of different memories can be constructed.

The ispLEVER design tool supports the creation of a variety of different size memories. Where appropriate, the software will construct these using distributed memory primitives that represent the capabilities of the PFU. Table 2-3 shows the number of Slices required to implement different distributed RAM primitives. Figure 2-6 shows the distributed memory primitive block diagrams. Dual port memories involve the pairing of two Slices. One Slice functions as the read-write port, while the other companion Slice supports the read-only port. For more information on RAM mode in MachXO devices, please see details of additional technical documentation at the end of this data sheet.

Table 2-3. Number of Slices Required For Implementing Distributed RAM

|                  | SPR16x2 | DPR16x2 |

|------------------|---------|---------|

| Number of Slices | 1       | 2       |

Note: SPR = Single Port RAM, DPR = Dual Port RAM

The EBR memory supports three forms of write behavior for single or dual port operation:

- 1. **Normal** data on the output appears only during the read cycle. During a write cycle, the data (at the current address) does not appear on the output. This mode is supported for all data widths.

- 2. **Write Through** a copy of the input data appears at the output of the same port. This mode is supported for all data widths.

- 3. **Read-Before-Write** when new data is being written, the old contents of the address appears at the output. This mode is supported for x9, x18 and x36 data widths.

#### **FIFO Configuration**

The FIFO has a write port with Data-in, CEW, WE and CLKW signals. There is a separate read port with Data-out, RCE, RE and CLKR signals. The FIFO internally generates Almost Full, Full, Almost Empty and Empty Flags. The Full and Almost Full flags are registered with CLKW. The Empty and Almost Empty flags are registered with CLKR. The range of programming values for these flags are in Table 2-7.

Table 2-7. Programmable FIFO Flag Ranges

| Flag Name         | Programming Range              |

|-------------------|--------------------------------|

| Full (FF)         | 1 to (up to 2 <sup>N</sup> -1) |

| Almost Full (AF)  | 1 to Full-1                    |

| Almost Empty (AE) | 1 to Full-1                    |

| Empty (EF)        | 0                              |

N = Address bit width

The FIFO state machine supports two types of reset signals: RSTA and RSTB. The RSTA signal is a global reset that clears the contents of the FIFO by resetting the read/write pointer and puts the FIFO flags in their initial reset state. The RSTB signal is used to reset the read pointer. The purpose of this reset is to retransmit the data that is in the FIFO. In these applications it is important to keep careful track of when a packet is written into or read from the FIFO.

#### **Memory Core Reset**

The memory array in the EBR utilizes latches at the A and B output ports. These latches can be reset asynchronously. RSTA and RSTB are local signals, which reset the output latches associated with Port A and Port B respectively. The Global Reset (GSRN) signal resets both ports. The output data latches and associated resets for both ports are as shown in Figure 2-13.

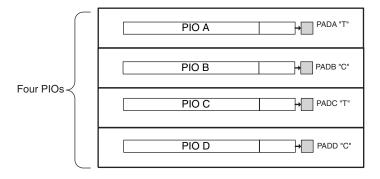

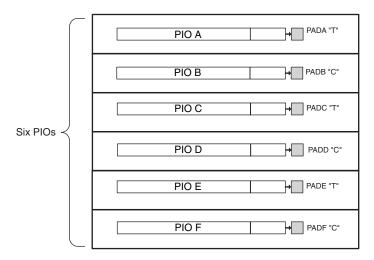

### **PIO Groups**

On the MachXO devices, PIO cells are assembled into two different types of PIO groups, those with four PIO cells and those with six PIO cells. PIO groups with four IOs are placed on the left and right sides of the device while PIO groups with six IOs are placed on the top and bottom. The individual PIO cells are connected to their respective sysIO buffers and PADs.

On all MachXO devices, two adjacent PIOs can be joined to provide a complementary Output driver pair. The I/O pin pairs are labeled as "T" and "C" to distinguish between the true and complement pins.

The MachXO1200 and MachXO2280 devices contain enhanced I/O capability. All PIO pairs on these larger devices can implement differential receivers. In addition, half of the PIO pairs on the left and right sides of these devices can be configured as LVDS transmit/receive pairs. PIOs on the top of these larger devices also provide PCI support.

Figure 2-15. Group of Four Programmable I/O Cells

This structure is used on the left and right of MachXO devices

Figure 2-16. Group of bSix Programmable I/O Cells

This structure is used on the top and bottom of MachXO devices

#### **PIO**

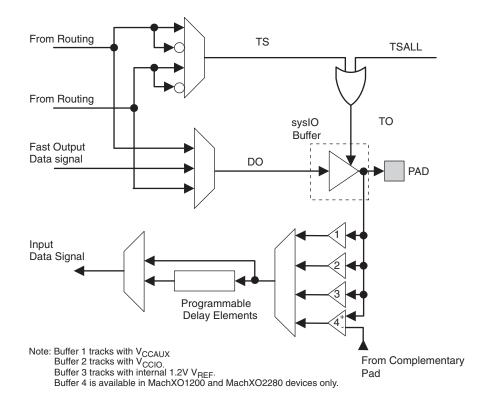

The PIO blocks provide the interface between the sysIO buffers and the internal PFU array blocks. These blocks receive output data from the PFU array and a fast output data signal from adjacent PFUs. The output data and fast

output data signals are multiplexed and provide a single signal to the I/O pin via the sysIO buffer. Figure 2-17 shows the MachXO PIO logic.

The tristate control signal is multiplexed from the output data signals and their complements. In addition a global signal (TSALL) from a dedicated pad can be used to tristate the sysIO buffer.

The PIO receives an input signal from the pin via the sysIO buffer and provides this signal to the core of the device. In addition there are programmable elements that can be utilized by the design tools to avoid positive hold times.

Figure 2-17. MachXO PIO Block Diagram

### sysIO Buffer

Each I/O is associated with a flexible buffer referred to as a sysIO buffer. These buffers are arranged around the periphery of the device in groups referred to as Banks. The sysIO buffers allow users to implement the wide variety of standards that are found in today's systems including LVCMOS, TTL, BLVDS, LVDS and LVPECL.

In the MachXO devices, single-ended output buffers and ratioed input buffers (LVTTL, LVCMOS and PCI) are powered using  $V_{CCIO}$ . In addition to the Bank  $V_{CCIO}$  supplies, the MachXO devices have a  $V_{CC}$  core logic power supply, and a  $V_{CCAUX}$  supply that powers up a variety of internal circuits including all the differential and referenced input buffers.

MachXO256 and MachXO640 devices contain single-ended input buffers and single-ended output buffers with complementary outputs on all the I/O Banks.

MachXO1200 and MachXO2280 devices contain two types of sysIO buffer pairs.

#### 1. Top and Bottom sysIO Buffer Pairs

The sysIO buffer pairs in the top and bottom Banks of the device consist of two single-ended output drivers and two sets of single-ended input buffers (for ratioed or absolute input levels). The I/O pairs on the top and bottom

## MachXO256 and MachXO640 Hot Socketing Specifications<sup>1, 2, 3</sup>

| Symbol   | Parameter                    | Condition                       | Min. | Тур. | Max     | Units |

|----------|------------------------------|---------------------------------|------|------|---------|-------|

| $I_{DK}$ | Input or I/O leakage Current | $0 \le V_{IN} \le V_{IH} (MAX)$ | -    |      | +/-1000 | μΑ    |

- 1. Insensitive to sequence of V<sub>CC,</sub> V<sub>CCAUX,</sub> and V<sub>CCIO</sub>. However, assumes monotonic rise/fall rates for V<sub>CC,</sub> V<sub>CCAUX,</sub> and V<sub>CCIO.</sub>

- 2.  $0 \le V_{CC} \le V_{CC}$  (MAX),  $0 \le V_{CCIO} \le V_{CCIO}$  (MAX) and  $0 \le V_{CCAUX} \le V_{CCAUX}$  (MAX).

- 3. I<sub>DK</sub> is additive to I<sub>PU</sub>, I<sub>PD</sub> or I<sub>BH</sub>.

## MachXO1200 and MachXO2280 Hot Socketing Specifications<sup>1, 2, 3</sup>

| Symbol          | Parameter                       | Condition                           | Min. | Тур. | Max.    | Units |  |

|-----------------|---------------------------------|-------------------------------------|------|------|---------|-------|--|

| Non-LVDS G      | Non-LVDS General Purpose syslOs |                                     |      |      |         |       |  |

| I <sub>DK</sub> | Input or I/O Leakage Current    | $0 \le V_{IN} \le V_{IH}$ (MAX.)    | _    | _    | +/-1000 | μΑ    |  |

| LVDS Genera     | LVDS General Purpose syslOs     |                                     |      |      |         |       |  |

| 1               | Input or I/O Leakage Current    | $V_{IN} \le V_{CCIO}$               | _    | _    | +/-1000 | μΑ    |  |

| IDK_LVDS        | Imput of 1/O Leakage Current    | V <sub>IN</sub> > V <sub>CCIO</sub> | _    | 35   | _       | mA    |  |

- 1. Insensitive to sequence of  $V_{CC,}$   $V_{CCAUX,}$  and  $V_{CCIO}$ . However, assumes monotonic rise/fall rates for  $V_{CC,}$   $V_{CCAUX,}$  and  $V_{CCIO,}$

- 2.  $0 \le V_{CC} \le V_{CC}$  (MAX),  $0 \le V_{CCIO} \le V_{CCIO}$  (MAX), and  $0 \le V_{CCAUX} \le V_{CCAUX}$  (MAX).

- 3.  $I_{DK}$  is additive to  $I_{PU}$ ,  $I_{PW}$  or  $I_{BH}$ .

#### **DC Electrical Characteristics**

#### **Over Recommended Operating Conditions**

| Symbol                                              | Parameter                                | Condition                                                                            | Min.                  | Тур. | Max.                  | Units |

|-----------------------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------|-----------------------|------|-----------------------|-------|

| I <sub>IL,</sub> I <sub>IH</sub> <sup>1, 4, 5</sup> | Input or I/O Leakage                     | $0 \le V_{IN} \le (V_{CCIO} - 0.2V)$                                                 | _                     | _    | 10                    | μΑ    |

| 'IL, 'IH                                            | linput of 1/O Leakage                    | $(V_{CCIO} - 0.2V) < V_{IN} \le 3.6V$                                                | _                     | _    | 40                    | μΑ    |

| I <sub>PU</sub>                                     | I/O Active Pull-up Current               | $0 \le V_{IN} \le 0.7 \ V_{CCIO}$                                                    | -30                   | _    | -150                  | μΑ    |

| I <sub>PD</sub>                                     | I/O Active Pull-down Current             | $V_{IL}$ (MAX) $\leq V_{IN} \leq V_{IH}$ (MAX)                                       | 30                    | _    | 150                   | μΑ    |

| I <sub>BHLS</sub>                                   | Bus Hold Low sustaining current          | $V_{IN} = V_{IL} (MAX)$                                                              | 30                    | _    | _                     | μΑ    |

| I <sub>BHHS</sub>                                   | Bus Hold High sustaining current         | $V_{IN} = 0.7V_{CCIO}$                                                               | -30                   | _    | _                     | μΑ    |

| I <sub>BHLO</sub>                                   | Bus Hold Low Overdrive current           | $0 \le V_{IN} \le V_{IH} (MAX)$                                                      | _                     | _    | 150                   | μΑ    |

| I <sub>BHHO</sub>                                   | Bus Hold High Overdrive current          | $0 \le V_{IN} \le V_{IH} (MAX)$                                                      | _                     | _    | -150                  | μΑ    |

| V <sub>BHT</sub> <sup>3</sup>                       | Bus Hold trip Points                     | $0 \le V_{IN} \le V_{IH} (MAX)$                                                      | V <sub>IL</sub> (MAX) | _    | V <sub>IH</sub> (MIN) | V     |

| C1                                                  | I/O Capacitance <sup>2</sup>             | $V_{CCIO} = 3.3V, 2.5V, 1.8V, 1.5V, 1.2V, V_{CC} = Typ., V_{IO} = 0 to V_{IH} (MAX)$ | _                     | 8    | _                     | pf    |

| C2                                                  | Dedicated Input Capacitance <sup>2</sup> | $V_{CCIO} = 3.3V, 2.5V, 1.8V, 1.5V, 1.2V, V_{CC} = Typ., V_{IO} = 0 to V_{IH} (MAX)$ | _                     | 8    | _                     | pf    |

<sup>1.</sup> Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tri-stated. It is not measured with the output driver active. Bus maintenance circuits are disabled.

<sup>2.</sup>  $T_A 25^{\circ}C$ , f = 1.0MHz

<sup>3.</sup> Please refer to  $V_{IL}$  and  $V_{IH}$  in the sysIO Single-Ended DC Electrical Characteristics table of this document.

<sup>4.</sup> Not applicable to SLEEPN pin.

<sup>5.</sup> When  $V_{IH}$  is higher than  $V_{CCIO}$ , a transient current typically of 30ns in duration or less with a peak current of 6mA can occur on the high-to-low transition. For MachXO1200 and MachXO2280 true LVDS output pins,  $V_{IH}$  must be less than or equal to  $V_{CCIO}$ .

Table 3-2. BLVDS DC Conditions1

| Over Recommended | Operating | <b>Conditions</b> |

|------------------|-----------|-------------------|

|------------------|-----------|-------------------|

|                     |                             | Non     | ninal   |       |

|---------------------|-----------------------------|---------|---------|-------|

| Symbol              | Description                 | Zo = 45 | Zo = 90 | Units |

| Z <sub>OUT</sub>    | Output impedance            | 100     | 100     | Ohms  |

| R <sub>TLEFT</sub>  | Left end termination        | 45      | 90      | Ohms  |

| R <sub>TRIGHT</sub> | Right end termination       | 45      | 90      | Ohms  |

| V <sub>OH</sub>     | Output high voltage         | 1.375   | 1.48    | V     |

| $V_{OL}$            | Output low voltage          | 1.125   | 1.02    | V     |

| V <sub>OD</sub>     | Output differential voltage | 0.25    | 0.46    | V     |

| V <sub>CM</sub>     | Output common mode voltage  | 1.25    | 1.25    | V     |

| I <sub>DC</sub>     | DC output current           | 11.2    | 10.2    | mA    |

<sup>1.</sup> For input buffer, see LVDS table.

#### **LVPECL**

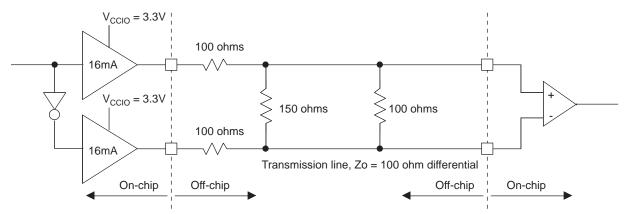

The MachXO family supports the differential LVPECL standard through emulation. This output standard is emulated using complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs on all the devices. The LVPECL input standard is supported by the LVDS differential input buffer on certain devices. The scheme shown in Figure 3-3 is one possible solution for point-to-point signals.

Figure 3-3. Differential LVPECL

Table 3-3. LVPECL DC Conditions1

#### **Over Recommended Operating Conditions**

| Symbol            | Description                 | Nominal | Units |

|-------------------|-----------------------------|---------|-------|

| Z <sub>OUT</sub>  | Output impedance            | 100     | Ohms  |

| R <sub>P</sub>    | Driver parallel resistor    | 150     | Ohms  |

| R <sub>T</sub>    | Receiver termination        | 100     | Ohms  |

| V <sub>OH</sub>   | Output high voltage         | 2.03    | V     |

| V <sub>OL</sub>   | Output low voltage          | 1.27    | V     |

| V <sub>OD</sub>   | Output differential voltage | 0.76    | V     |

| V <sub>CM</sub>   | Output common mode voltage  | 1.65    | V     |

| Z <sub>BACK</sub> | Back impedance              | 85.7    | Ohms  |

| I <sub>DC</sub>   | DC output current           | 12.7    | mA    |

<sup>1.</sup> For input buffer, see LVDS table.

# MachXO Internal Timing Parameters<sup>1</sup>

#### **Over Recommended Operating Conditions**

|                         |                                                              | _     | 5    | -4    |      | -3    |      |       |

|-------------------------|--------------------------------------------------------------|-------|------|-------|------|-------|------|-------|

| Parameter               | Description                                                  | Min.  | Max. | Min.  | Max. | Min.  | Max. | Units |

| PFU/PFF Log             | jic Mode Timing                                              |       | •    | •     | •    |       | •    | ,     |

| t <sub>LUT4_PFU</sub>   | LUT4 delay (A to D inputs to F output)                       | _     | 0.28 | _     | 0.34 | _     | 0.39 | ns    |

| t <sub>LUT6_PFU</sub>   | LUT6 delay (A to D inputs to OFX output)                     | _     | 0.44 | _     | 0.53 | _     | 0.62 | ns    |

| t <sub>LSR_PFU</sub>    | Set/Reset to output of PFU                                   | _     | 0.90 | _     | 1.08 | _     | 1.26 | ns    |

| t <sub>SUM_PFU</sub>    | Clock to Mux (M0,M1) input setup time                        | 0.10  | _    | 0.13  | _    | 0.15  | _    | ns    |

| t <sub>HM_PFU</sub>     | Clock to Mux (M0,M1) input hold time                         | -0.05 | _    | -0.06 | _    | -0.07 | _    | ns    |

| t <sub>SUD_PFU</sub>    | Clock to D input setup time                                  | 0.13  | _    | 0.16  | _    | 0.18  | _    | ns    |

| t <sub>HD_PFU</sub>     | Clock to D input hold time                                   | -0.03 | _    | -0.03 | _    | -0.04 | _    | ns    |

| t <sub>CK2Q_PFU</sub>   | Clock to Q delay, D-type register configuration              | _     | 0.40 | _     | 0.48 | _     | 0.56 | ns    |

| t <sub>LE2Q_PFU</sub>   | Clock to Q delay latch configuration                         | _     | 0.53 | _     | 0.64 | _     | 0.74 | ns    |

| t <sub>LD2Q_PFU</sub>   | D to Q throughput delay when latch is enabled                | _     | 0.55 | _     | 0.66 | _     | 0.77 | ns    |

|                         | rt Memory Mode Timing                                        | I     | I    | I     | I    | I     | I    | J.    |

| t <sub>CORAM_PFU</sub>  | Clock to Output                                              |       | 0.40 |       | 0.48 |       | 0.56 | ns    |

| t <sub>SUDATA_PFU</sub> | Data Setup Time                                              | -0.18 | _    | -0.22 | _    | -0.25 | _    | ns    |

| t <sub>HDATA_PFU</sub>  | Data Hold Time                                               | 0.28  | —    | 0.34  | —    | 0.39  | —    | ns    |

| t <sub>SUADDR_PFU</sub> | Address Setup Time                                           | -0.46 | _    | -0.56 | _    | -0.65 | _    | ns    |

| t <sub>HADDR_PFU</sub>  | Address Hold Time                                            | 0.71  | _    | 0.85  | _    | 0.99  | _    | ns    |

| t <sub>SUWREN_PFU</sub> | Write/Read Enable Setup Time                                 | -0.22 | _    | -0.26 | _    | -0.30 | _    | ns    |

| t <sub>HWREN_PFU</sub>  | Write/Read Enable Hold Time                                  | 0.33  | _    | 0.40  | _    | 0.47  | _    | ns    |

| PIO Input/Ou            | tput Buffer Timing                                           |       | •    | •     | •    |       | •    | ,     |

| t <sub>IN_PIO</sub>     | Input Buffer Delay                                           |       | 0.75 |       | 0.90 |       | 1.06 | ns    |

| t <sub>OUT_PIO</sub>    | Output Buffer Delay                                          | _     | 1.29 | _     | 1.54 | _     | 1.80 | ns    |

|                         | (1200 and 2280 Devices Only)                                 |       | •    | •     | •    |       | •    | ,     |

| t <sub>CO_EBR</sub>     | Clock to output from Address or Data with no output register | _     | 2.24 | _     | 2.69 | _     | 3.14 | ns    |

| t <sub>COO_EBR</sub>    | Clock to output from EBR output Register                     | _     | 0.54 | _     | 0.64 | _     | 0.75 | ns    |

| t <sub>SUDATA_EBR</sub> | Setup Data to EBR Memory                                     | -0.26 | _    | -0.31 | _    | -0.37 | _    | ns    |

| t <sub>HDATA_EBR</sub>  | Hold Data to EBR Memory                                      | 0.41  | _    | 0.49  | _    | 0.57  | _    | ns    |

| t <sub>SUADDR_EBR</sub> | Setup Address to EBR Memory                                  | -0.26 | —    | -0.31 | —    | -0.37 | —    | ns    |

| t <sub>HADDR_EBR</sub>  | Hold Address to EBR Memory                                   | 0.41  | _    | 0.49  | _    | 0.57  | _    | ns    |

| t <sub>SUWREN_EBR</sub> | Setup Write/Read Enable to EBR Memory                        | -0.17 | _    | -0.20 | _    | -0.23 | _    | ns    |

| t <sub>HWREN_EBR</sub>  | Hold Write/Read Enable to EBR Memory                         | 0.26  | —    | 0.31  | —    | 0.36  | —    | ns    |

| t <sub>SUCE_EBR</sub>   | Clock Enable Setup Time to EBR Output Register               | 0.19  | _    | 0.23  | _    | 0.27  | _    | ns    |

| t <sub>HCE_EBR</sub>    | Clock Enable Hold Time to EBR Output Register                | -0.13 | _    | -0.16 | _    | -0.18 | _    | ns    |

| t <sub>RSTO_EBR</sub>   | Reset To Output Delay Time from EBR Output Register          | _     | 1.03 | _     | 1.23 | _     | 1.44 | ns    |

| PLL Paramet             | ers (1200 and 2280 Devices Only)                             | •     |      |       |      | •     |      |       |

| t <sub>RSTREC</sub>     | Reset Recovery to Rising Clock                               | 1.00  | _    | 1.00  | _    | 1.00  | _    | ns    |

| t <sub>RSTSU</sub>      | Reset Signal Setup Time                                      | 1.00  | _    | 1.00  | _    | 1.00  | _    | ns    |

|                         | •                                                            |       |      |       |      |       |      |       |

<sup>1.</sup> Internal parameters are characterized but not tested on every device.

Rev. A 0.19

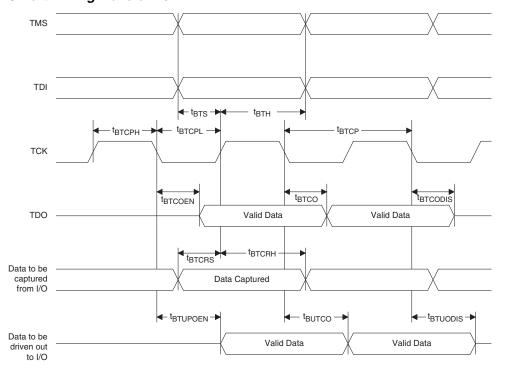

Figure 3-5. JTAG Port Timing Waveforms

# LCMXO1200 and LCMXO2280 Logic Signal Connections: 100 TQFP (Cont.)

|               |                  | L    | CMXO1200         |              | LCMXO2280        |      |                  |              |  |  |  |

|---------------|------------------|------|------------------|--------------|------------------|------|------------------|--------------|--|--|--|

| Pin<br>Number | Ball<br>Function | Bank | Dual<br>Function | Differential | Ball<br>Function | Bank | Dual<br>Function | Differential |  |  |  |

| 42            | PB9A             | 4    |                  | Т            | PB12A            | 4    |                  | Т            |  |  |  |

| 43            | PB9B             | 4    |                  | С            | PB12B            | 4    |                  | С            |  |  |  |

| 44            | VCCIO4           | 4    |                  |              | VCCIO4           | 4    |                  |              |  |  |  |

| 45            | PB10A            | 4    |                  | Т            | PB13A            | 4    |                  | Т            |  |  |  |

| 46            | PB10B            | 4    |                  | С            | PB13B            | 4    |                  | С            |  |  |  |

| 47***         | SLEEPN           | -    | SLEEPN           |              | SLEEPN           | -    | SLEEPN           |              |  |  |  |

| 48            | PB11A            | 4    |                  | Т            | PB16A            | 4    |                  | Т            |  |  |  |

| 49            | PB11B            | 4    |                  | С            | PB16B            | 4    |                  | С            |  |  |  |

| 50**          | GNDIO3<br>GNDIO4 | -    |                  |              | GNDIO3<br>GNDIO4 | -    |                  |              |  |  |  |

| 51            | PR16B            | 3    |                  |              | PR19B            | 3    |                  |              |  |  |  |

| 52            | PR15B            | 3    |                  | C*           | PR18B            | 3    |                  | C*           |  |  |  |

| 53            | PR15A            | 3    |                  | T*           | PR18A            | 3    |                  | T*           |  |  |  |

| 54            | PR14B            | 3    |                  | C*           | PR17B            | 3    |                  | C*           |  |  |  |

| 55            | PR14A            | 3    |                  | T*           | PR17A            | 3    |                  | T*           |  |  |  |

| 56            | VCCIO3           | 3    |                  |              | VCCIO3           | 3    |                  |              |  |  |  |

| 57            | PR12B            | 3    |                  | C*           | PR15B            | 3    |                  | C*           |  |  |  |

| 58            | PR12A            | 3    |                  | T*           | PR15A            | 3    |                  | T*           |  |  |  |

| 59            | GND              | -    |                  |              | GND              | -    |                  |              |  |  |  |

| 60            | PR10B            | 3    |                  | C*           | PR13B            | 3    |                  | C*           |  |  |  |

| 61            | PR10A            | 3    |                  | T*           | PR13A            | 3    |                  | T*           |  |  |  |

| 62            | PR9B             | 3    |                  | C*           | PR11B            | 3    |                  | C*           |  |  |  |

| 63            | PR9A             | 3    |                  | T*           | PR11A            | 3    |                  | T*           |  |  |  |

| 64            | PR8B             | 2    |                  | C*           | PR10B            | 2    |                  | C*           |  |  |  |

| 65            | PR8A             | 2    |                  | T*           | PR10A            | 2    |                  | T*           |  |  |  |

| 66            | VCC              | -    |                  |              | VCC              | -    |                  |              |  |  |  |

| 67            | PR6C             | 2    |                  |              | PR8C             | 2    |                  |              |  |  |  |

| 68            | PR6B             | 2    |                  | C*           | PR8B             | 2    |                  | C*           |  |  |  |

| 69            | PR6A             | 2    |                  | T*           | PR8A             | 2    |                  | T*           |  |  |  |

| 70            | VCCIO2           | 2    |                  |              | VCCIO2           | 2    |                  |              |  |  |  |

| 71            | PR4D             | 2    |                  |              | PR5D             | 2    |                  |              |  |  |  |

| 72            | PR4B             | 2    |                  | C*           | PR5B             | 2    |                  | C*           |  |  |  |

| 73            | PR4A             | 2    |                  | T*           | PR5A             | 2    |                  | T*           |  |  |  |

| 74            | PR2B             | 2    |                  | С            | PR3B             | 2    |                  | C*           |  |  |  |

| 75            | PR2A             | 2    |                  | Т            | PR3A             | 2    |                  | T*           |  |  |  |

| 76**          | GNDIO1<br>GNDIO2 | -    |                  |              | GNDIO1<br>GNDIO2 | -    |                  |              |  |  |  |

| 77            | PT11C            | 1    |                  |              | PT15C            | 1    |                  |              |  |  |  |

| 78            | PT11B            | 1    |                  | С            | PT14B            | 1    |                  | С            |  |  |  |

| 79            | PT11A            | 1    |                  | Т            | PT14A            | 1    |                  | Т            |  |  |  |

| 80            | VCCIO1           | 1    |                  |              | VCCIO1           | 1    |                  |              |  |  |  |

| 81            | PT9E             | 1    |                  |              | PT12D            | 1    |                  | С            |  |  |  |

# LCMXO256 and LCMXO640 Logic Signal Connections: 100 csBGA (Cont.)

|                |                  | LCMXO25 | 6                |                   | LCMXO640       |                  |      |                  |                   |  |  |

|----------------|------------------|---------|------------------|-------------------|----------------|------------------|------|------------------|-------------------|--|--|

| Ball<br>Number | Ball<br>Function | Bank    | Dual<br>Function | Differen-<br>tial | Ball<br>Number | Ball<br>Function | Bank | Dual<br>Function | Differen-<br>tial |  |  |

| P13            | PB5A             | 1       |                  |                   | P13            | PB9C             | 2    |                  | T                 |  |  |

| M12*           | SLEEPN           | -       | SLEEPN           |                   | M12*           | SLEEPN           | -    | SLEEPN           |                   |  |  |

| P14            | PB5C             | 1       |                  | Т                 | P14            | PB9D             | 2    |                  | С                 |  |  |

| N13            | PB5D             | 1       |                  | С                 | N13            | PB9F             | 2    |                  |                   |  |  |

| N14            | PR9B             | 0       |                  | С                 | N14            | PR11D            | 1    |                  | С                 |  |  |

| M14            | PR9A             | 0       |                  | Т                 | M14            | PR11B            | 1    |                  | С                 |  |  |

| L13            | PR8B             | 0       |                  | С                 | L13            | PR11C            | 1    |                  | Т                 |  |  |

| L14            | PR8A             | 0       |                  | T                 | L14            | PR11A            | 1    |                  | T                 |  |  |

| M13            | PR7D             | 0       |                  | С                 | M13            | PR10D            | 1    |                  | С                 |  |  |

| K14            | PR7C             | 0       |                  | Т                 | K14            | PR10C            | 1    |                  | T                 |  |  |

| K13            | PR7B             | 0       |                  | С                 | K13            | PR10B            | 1    |                  | С                 |  |  |

| J14            | PR7A             | 0       |                  | Т                 | J14            | PR10A            | 1    |                  | Т                 |  |  |

| J13            | PR6B             | 0       |                  | С                 | J13            | PR9D             | 1    |                  |                   |  |  |

| H13            | PR6A             | 0       |                  | Т                 | H13            | PR9B             | 1    |                  |                   |  |  |

| G14            | GNDIO0           | 0       |                  |                   | G14            | GNDIO1           | 1    |                  |                   |  |  |

| G13            | PR5D             | 0       |                  | С                 | G13            | PR7B             | 1    |                  |                   |  |  |

| F14            | PR5C             | 0       |                  | Т                 | F14            | PR6C             | 1    |                  |                   |  |  |

| F13            | PR5B             | 0       |                  | С                 | F13            | PR6B             | 1    |                  |                   |  |  |

| E14            | PR5A             | 0       |                  | Т                 | E14            | PR5D             | 1    |                  |                   |  |  |

| E13            | PR4B             | 0       |                  | С                 | E13            | PR5B             | 1    |                  |                   |  |  |

| D14            | PR4A             | 0       |                  | Т                 | D14            | PR4D             | 1    |                  |                   |  |  |

| D13            | PR3D             | 0       |                  | С                 | D13            | PR4B             | 1    |                  |                   |  |  |

| C14            | PR3C             | 0       |                  | Т                 | C14            | PR3D             | 1    |                  |                   |  |  |

| C13            | PR3B             | 0       |                  | С                 | C13            | PR3B             | 1    |                  |                   |  |  |

| B14            | PR3A             | 0       |                  | Т                 | B14            | PR2D             | 1    |                  |                   |  |  |

| C12            | PR2B             | 0       |                  | С                 | C12            | PR2B             | 1    |                  |                   |  |  |

| B13            | GNDIO0           | 0       |                  |                   | B13            | GNDIO1           | 1    |                  |                   |  |  |

| A13            | PR2A             | 0       |                  | Т                 | A13            | PT9F             | 0    |                  | С                 |  |  |

| A12            | PT5C             | 0       |                  |                   | A12            | PT9E             | 0    |                  | Т                 |  |  |

| B11            | PT5B             | 0       |                  | С                 | B11            | PT9C             | 0    |                  |                   |  |  |

| A11            | PT5A             | 0       |                  | Т                 | A11            | PT9A             | 0    |                  |                   |  |  |

| B12            | PT4F             | 0       |                  | С                 | B12            | VCCIO0           | 0    |                  |                   |  |  |

| A10            | PT4E             | 0       |                  | Т                 | A10            | GNDIO0           | 0    |                  |                   |  |  |

| B10            | PT4D             | 0       |                  | С                 | B10            | PT7E             | 0    |                  |                   |  |  |

| A9             | PT4C             | 0       |                  | Т                 | A9             | PT7A             | 0    |                  |                   |  |  |

| A8             | PT4B             | 0       | PCLK0_1**        | С                 | A8             | PT6B             | 0    | PCLK0_1**        |                   |  |  |

| B8             | PT4A             | 0       | PCLK0_0**        | Т                 | B8             | PT5B             | 0    | PCLK0_0**        | С                 |  |  |

| A7             | PT3D             | 0       |                  | С                 | A7             | PT5A             | 0    |                  | Т                 |  |  |

| B7             | VCCAUX           | -       |                  |                   | B7             | VCCAUX           | -    |                  |                   |  |  |

| A6             | PT3C             | 0       |                  | Т                 | A6             | PT4F             | 0    |                  |                   |  |  |

| B6             | VCC              | -       |                  |                   | B6             | VCC              | -    |                  |                   |  |  |

| <b>A</b> 5     | PT3B             | 0       |                  | С                 | A5             | PT3F             | 0    |                  |                   |  |  |

# LCMXO640, LCMXO1200 and LCMXO2280 Logic Signal Connections: 132 csBGA

|          |                  | LCMX | <b>CO640</b>     |              |          |                  | LC   | MXO1200          | 1200 LCMXO2280 |        |                  |      |                  |              |

|----------|------------------|------|------------------|--------------|----------|------------------|------|------------------|----------------|--------|------------------|------|------------------|--------------|

| Ball #   | Ball<br>Function | Bank | Dual<br>Function | Differential | Ball #   | Ball<br>Function | Bank | Dual<br>Function | Differential   | Ball # | Ball<br>Function | Bank | Dual<br>Function | Differential |

| B1       | PL2A             | 3    |                  | Т            | B1       | PL2A             | 7    |                  | Т              | B1     | PL2A             | 7    | LUM0_PLLT_FB_A   | T            |

| C1       | PL2B             | 3    |                  | С            | C1       | PL3C             | 7    |                  | Т              | C1     | PL3C             | 7    | LUM0_PLLT_IN_A   | Т            |

| B2       | PL2C             | 3    |                  | Т            | B2       | PL2B             | 7    |                  | С              | B2     | PL2B             | 7    | LUM0_PLLC_FB_A   | С            |

| C2       | PL2D             | 3    |                  | С            | C2       | PL4A             | 7    |                  | T*             | C2     | PL4A             | 7    |                  | T*           |

| C3       | PL3A             | 3    |                  | Т            | C3       | PL3D             | 7    |                  | С              | C3     | PL3D             | 7    | LUM0_PLLC_IN_A   | С            |

| D1       | PL3B             | 3    |                  | С            | D1       | PL4B             | 7    |                  | C*             | D1     | PL4B             | 7    |                  | C*           |

| D3       | PL3D             | 3    |                  |              | D3       | PL4C             | 7    |                  |                | D3     | PL4C             | 7    |                  |              |

| E1       | GNDIO3           | 3    |                  |              | E1       | GNDIO7           | 7    |                  |                | E1     | GNDIO7           | 7    |                  |              |

| E2       | PL5A             | 3    |                  | T            | E2       | PL6A             | 7    |                  | T*             | E2     | PL7A             | 7    |                  | T*           |

| E3       | PL5B             | 3    | GSRN             | С            | E3       | PL6B             | 7    | GSRN             | C*             | E3     | PL7B             | 7    | GSRN             | C*           |

| F2       | PL5D             | 3    |                  |              | F2       | PL6D             | 7    |                  |                | F2     | PL7D             | 7    |                  |              |

| F3       | PL6B             | 3    |                  |              | F3       | PL7C             | 7    |                  | Т              | F3     | PL9C             | 7    |                  | T            |

| G1       | PL6C             | 3    |                  | Т            | G1       | PL7D             | 7    |                  | С              | G1     | PL9D             | 7    |                  | С            |

| G2       | PL6D             | 3    |                  | С            | G2       | PL8C             | 7    |                  | Т              | G2     | PL10C            | 7    |                  | Т            |

| G3       | PL7A             | 3    |                  | Т            | G3       | PL8D             | 7    |                  | С              | G3     | PL10D            | 7    |                  | С            |

| H2       | PL7B             | 3    |                  | С            | H2       | PL10A            | 6    |                  | T*             | H2     | PL12A            | 6    |                  | T*           |

| H1       | PL7C             | 3    |                  |              | H1       | PL10B            | 6    |                  | C*             | H1     | PL12B            | 6    |                  | C*           |

| НЗ       | VCC              | -    |                  |              | НЗ       | VCC              | -    |                  |                | НЗ     | VCC              | -    |                  |              |

| J1       | PL8A             | 3    |                  |              | J1       | PL11B            | 6    |                  |                | J1     | PL14D            | 6    |                  | С            |

| J2       | PL8C             | 3    | TSALL            |              | J2       | PL11C            | 6    | TSALL            | Т              | J2     | PL14C            | 6    | TSALL            | T            |

| J3       | PL9A             | 3    |                  | Т            | J3       | PL11D            | 6    |                  | С              | J3     | PL14B            | 6    |                  |              |

| K2       | PL9B             | 3    |                  | С            | K2       | PL12A            | 6    |                  | T*             | K2     | PL15A            | 6    |                  | T*           |

| K1       | PL9C             | 3    |                  |              | K1       | PL12B            | 6    |                  | C*             | K1     | PL15B            | 6    |                  | C*           |

| L2       | GNDIO3           | 3    |                  |              | L2       | GNDIO6           | 6    |                  |                | L2     | GNDIO6           | 6    |                  |              |

| L1       | PL10A            | 3    |                  | Т            | L1       | PL14A            | 6    | LLM0_PLLT_FB_A   | T*             | L1     | PL17A            | 6    | LLM0_PLLT_FB_A   | T*           |

| L3       | PL10B            | 3    |                  | С            | L3       | PL14B            | 6    | LLM0_PLLC_FB_A   | C*             | L3     | PL17B            | 6    | LLM0_PLLC_FB_A   | C*           |

| M1       | PL11A            | 3    |                  | Т            | M1       | PL15A            | 6    | LLM0_PLLT_IN_A   | T*             | M1     | PL18A            | 6    | LLM0_PLLT_IN_A   | T*           |

| N1       | PL11B            | 3    |                  | С            | N1       | PL16A            | 6    |                  | Т              | N1     | PL19A            | 6    |                  | Т            |

| M2       | PL11C            | 3    |                  | Т            | M2       | PL15B            | 6    | LLM0_PLLC_IN_A   | C*             | M2     | PL18B            | 6    | LLM0_PLLC_IN_A   | C*           |

| P1       | PL11D            | 3    |                  | С            | P1       | PL16B            | 6    |                  | С              | P1     | PL19B            | 6    |                  | С            |

| P2       | GNDIO2           | 2    |                  |              | P2       | GNDIO5           | 5    |                  |                | P2     | GNDIO5           | 5    |                  |              |

| P3       | TMS              | 2    | TMS              |              | P3       | TMS              | 5    | TMS              |                | P3     | TMS              | 5    | TMS              |              |

| M3       | PB2C             | 2    |                  | Т            | M3       | PB2C             | 5    | _                | Т              | M3     | PB2A             | 5    |                  | Т            |

| N3       | PB2D             | 2    |                  | С            | N3       | PB2D             | 5    |                  | С              | N3     | PB2B             | 5    |                  | С            |

| P4       | TCK              | 2    | TCK              | -            | P4       | TCK              | 5    | TCK              | -              | P4     | TCK              | 5    | TCK              | -            |

| M4       | PB3B             | 2    |                  |              | M4       | PB3B             | 5    |                  |                | M4     | PB3B             | 5    |                  |              |

| N4       | PB3C             | 2    |                  | Т            | N4       | PB4A             | 5    |                  | Т              | N4     | PB4A             | 5    |                  | Т            |

| P5       | PB3D             | 2    |                  | C            | P5       | PB4B             | 5    |                  | С              | P5     | PB4B             | 5    |                  | С            |

| N5       | TDO              | 2    | TDO              |              | N5       | TDO              | 5    | TDO              |                | N5     | TDO              | 5    | TDO              |              |

| M5       | TDI              | 2    | TDI              |              | M5       | TDI              | 5    | TDI              |                | M5     | TDI              | 5    | TDI              |              |

| N6       | PB4E             | 2    | . 51             | Т            | N6       | PB5C             | 5    | 1.01             |                | N6     | PB6C             | 5    | 1.01             |              |

| P6       | VCC              | -    |                  | '            | P6       | VCC              | -    |                  |                | P6     | VCC              | -    |                  |              |

| M6       | PB4F             | 2    |                  | С            | M6       | PB6A             | 5    |                  |                | M6     | PB8A             | 5    |                  |              |

| P7       | VCCAUX           | -    |                  |              | P7       | VCCAUX           | -    |                  |                | P7     | VCCAUX           | -    |                  |              |

| N7       | PB5A             | 2    |                  | Т            | N7       | PB6F             | 5    |                  |                | N7     | PB8F             | 5    |                  |              |

| M7       | PB5B             | 2    | PCLK2_1***       | C            | M7       | PB7B             | 4    | PCLK4_1***       |                | M7     | PB10F            | 4    | PCLK4_1***       |              |

| N8       | PB5B<br>PB5D     | 2    | I ULIKZ_I        |              | N8       | PB7B<br>PB7C     | 4    | I OLN4_I         | Т              | N8     | PB10F<br>PB10C   | 4    | I OLN4_I         | Т            |

| P8       | PB6A             | 2    |                  | Т            | P8       | PB7D             | 4    |                  | C              | P8     | PB10D            | 4    |                  | C            |

|          |                  | 2    | PCLK2_0***       | C            |          | PB7F             |      | PCLK4_0***       | U              | M8     |                  |      | PCLK4_0***       |              |

| M8<br>N9 | PB6B<br>PB7A     | 2    | I-OLNZ_U         | T            | M8<br>N9 |                  | 4    | FULN4_U          | Т              | N9     | PB10B            | 4    | FULN4_U          | Т            |

| N9       | PD/A             | 2    |                  | 1            | 149      | PB9A             | 4    |                  | 1              | 149    | PB12A            | 4    |                  | 1            |

# LCMXO640, LCMXO1200 and LCMXO2280 Logic Signal Connections: 256 caBGA / 256 ftBGA (Cont.)

|          |                | LCMX | O640       |              |          |                | LCI      | MXO1200            |              |          |                | LCI  | MXO2280           |              |

|----------|----------------|------|------------|--------------|----------|----------------|----------|--------------------|--------------|----------|----------------|------|-------------------|--------------|

| Ball     | Ball           |      | Dual       |              | Ball     | Ball           | <u>.</u> | _ Dual             |              | Ball     | Ball           |      | _ Dual            |              |

| Number   |                | Bank | Function   | Differential |          | Function       | Bank     | Function           | Differential |          |                | Bank | Function          | Differential |

| J4       | PL8A           | 3    |            | Т            | J4       | PL13A          | 6        |                    | T*           | J4       | PL16A          | 6    |                   | T*<br>C*     |

| J5       | PL8B<br>PL11A  | 3    |            | C<br>T       | J5<br>R1 | PL13B<br>PL13C | 6        |                    | C*<br>T      | J5<br>R1 | PL16B<br>PL16C | 6    |                   | T            |

| R1<br>R2 | PL11A<br>PL11B | 3    |            | C            | R2       | PL13D          | 6        |                    | C            | R2       | PL16D          | 6    |                   | C            |

| -<br>-   | - FLIIB        | -    |            | C            | - nz     | -              | -        |                    | C            | GND      | GND            | -    |                   | C            |

| K5       | NC             | -    |            |              | -<br>K5  | PL14A          | 6        | LLM0_PLLT_FB_A     | T*           | K5       | PL17A          | 6    | LLM0_PLLT_FB_A    | T*           |

| K4       | NC             |      |            |              | K4       | PL14B          | 6        | LLM0_PLLC_FB_A     | C*           | K4       | PL17B          | 6    | LLM0_PLLC_FB_A    | C*           |

| L5       | PL10C          | 3    |            | Т            | L5       | PL14C          | 6        | CLINIO_1 CLO_1 B_X | Т            | L5       | PL17C          | 6    | LLINO_I LLO_I B_A | T            |

| L4       | PL10D          | 3    |            | С            | L4       | PL14D          | 6        |                    | С            | L4       | PL17D          | 6    |                   | С            |

| M5       | NC             |      |            |              | M5       | PL15A          | 6        | LLMO PLLT IN A     | T*           | M5       | PL18A          | 6    | LLM0_PLLT_IN_A    | T*           |

| M4       | NC             |      |            |              | M4       | PL15B          | 6        | LLM0_PLLC_IN_A     | C*           | M4       | PL18B          | 6    | LLM0_PLLC_IN_A    | C*           |

| N4       | PL11C          | 3    |            | Т            | N4       | PL16A          | 6        | LLINO_I LLO_IIV_A  | Т            | N4       | PL19A          | 6    | ELWIO_I ELO_IIV_A | T            |

| N3       | PL11D          | 3    |            | C            | N3       | PL16B          | 6        |                    | C            | N3       | PL19B          | 6    |                   | C            |

| VCCIO3   | VCCIO3         | 3    |            |              | VCCIO6   | VCCIO6         | 6        |                    |              | VCCIO6   | VCCIO6         | 6    |                   |              |

| GND      | GNDIO3         | 3    |            |              | GND      | GNDIO6         | 6        |                    |              | GND      | GNDIO6         | 6    |                   |              |

| GND      | GNDIO2         | 2    |            |              | GND      | GNDIO5         | 5        |                    |              | GND      | GNDIO5         | 5    |                   |              |

| VCCIO2   | VCCIO2         | 2    |            |              | VCCIO5   | VCCIO5         | 5        |                    |              | VCCIO5   | VCCIO5         | 5    |                   |              |

| P4       | TMS            | 2    | TMS        |              | P4       | TMS            | 5        | TMS                |              | P4       | TMS            | 5    | TMS               |              |

| P2       | NC             |      | TIVIO      |              | P2       | PB2A           | 5        | TIVIO              | Т            | P2       | PB2A           | 5    | TIVIO             | Т            |

| P3       | NC             |      |            |              | P3       | PB2B           | 5        |                    | C            | P3       | PB2B           | 5    |                   | C            |

| N5       | NC             |      |            |              | N5       | PB2C           | 5        |                    | Т            | N5       | PB2C           | 5    |                   | Т            |

| R3       | TCK            | 2    | TCK        |              | R3       | TCK            | 5        | TCK                | '            | R3       | TCK            | 5    | TCK               | '            |

| N6       | NC             |      | 1010       |              | N6       | PB2D           | 5        | TOIL               | С            | N6       | PB2D           | 5    | TOR               | С            |

| T2       | PB2A           | 2    |            | Т            | T2       | PB3A           | 5        |                    | Т            | T2       | PB3A           | 5    |                   | Т            |

| T3       | PB2B           | 2    |            | C            | T3       | PB3B           | 5        |                    | C            | T3       | PB3B           | 5    |                   | C            |

| R4       | PB2C           | 2    |            | Т            | R4       | PB3C           | 5        |                    | T            | R4       | PB3C           | 5    |                   | T            |

| R5       | PB2D           | 2    |            | C            | R5       | PB3D           | 5        |                    | C            | R5       | PB3D           | 5    |                   | C            |

| P5       | PB3A           | 2    |            | T            | P5       | PB4A           | 5        |                    | T            | P5       | PB4A           | 5    |                   | T            |

| P6       | PB3B           | 2    |            | C            | P6       | PB4B           | 5        |                    | C            | P6       | PB4B           | 5    |                   | C            |

| T5       | PB3C           | 2    |            | Т            | T5       | PB4C           | 5        |                    | Т            | T5       | PB4C           | 5    |                   | Т            |

| M6       | TDO            | 2    | TDO        |              | M6       | TDO            | 5        | TDO                | '            | M6       | TDO            | 5    | TDO               | '            |

| T4       | PB3D           | 2    |            | С            | T4       | PB4D           | 5        |                    | С            | T4       | PB4D           | 5    |                   | С            |

| R6       | PB4A           | 2    |            | T            | R6       | PB5A           | 5        |                    | T            | R6       | PB5A           | 5    |                   | T            |

| GND      | GNDIO2         | 2    |            |              | GND      | GNDIO5         | 5        |                    |              | GND      | GNDIO5         | 5    |                   |              |

| VCCIO2   | VCCIO2         | 2    |            |              | VCCIO5   | VCCIO5         | 5        |                    |              | VCCIO5   | VCCIO5         | 5    |                   |              |

| T6       | PB4B           | 2    |            | С            | T6       | PB5B           | 5        |                    | С            | T6       | PB5B           | 5    |                   | С            |

| N7       | TDI            | 2    | TDI        |              | N7       | TDI            | 5        | TDI                |              | N7       | TDI            | 5    | TDI               |              |

| T8       | PB4C           | 2    |            | Т            | T8       | PB5C           | 5        |                    | Т            | T8       | PB6A           | 5    |                   | Т            |

| T7       | PB4D           | 2    |            | С            | T7       | PB5D           | 5        |                    | С            | T7       | PB6B           | 5    |                   | С            |

| M7       | NC             |      |            |              | M7       | PB6A           | 5        |                    | Т            | M7       | PB7C           | 5    |                   | Т            |

| M8       | NC             |      |            |              | M8       | PB6B           | 5        |                    | С            | M8       | PB7D           | 5    |                   | С            |

| Т9       | VCCAUX         | -    |            |              | T9       | VCCAUX         | -        |                    |              | T9       | VCCAUX         | -    |                   |              |

| R7       | PB4E           | 2    |            | Т            | R7       | PB6C           | 5        |                    | Т            | R7       | PB8C           | 5    |                   | Т            |

| R8       | PB4F           | 2    |            | С            | R8       | PB6D           | 5        |                    | С            | R8       | PB8D           | 5    |                   | С            |

| -        | -              |      |            |              | VCCIO5   | VCCIO5         | 5        |                    |              | VCCIO5   | VCCIO5         | 5    |                   |              |

| -        | -              |      |            |              | GND      | GNDIO5         | 5        |                    |              | GND      | GNDIO5         | 5    |                   |              |

| P7       | PB5C           | 2    |            | Т            | P7       | PB6E           | 5        |                    | Т            | P7       | PB9A           | 4    |                   | Т            |

| P8       | PB5D           | 2    |            | С            | P8       | PB6F           | 5        |                    | С            | P8       | PB9B           | 4    |                   | С            |

| N8       | PB5A           | 2    |            | Т            | N8       | PB7A           | 4        |                    | Т            | N8       | PB10E          | 4    |                   | Т            |

| N9       | PB5B           | 2    | PCLK2_1*** | С            | N9       | PB7B           | 4        | PCLK4_1***         | С            | N9       | PB10F          | 4    | PCLK4_1***        | С            |

| P10      | PB7B           | 2    |            | С            | P10      | PB7D           | 4        |                    | С            | P10      | PB10D          | 4    |                   | С            |

| P9       | PB7A           | 2    |            | Т            | P9       | PB7C           | 4        |                    | Т            | P9       | PB10C          | 4    |                   | Т            |

| M9       | PB6B           | 2    | PCLK2_0*** | С            | M9       | PB7F           | 4        | PCLK4_0***         | С            | M9       | PB10B          | 4    | PCLK4_0***        | С            |

# LCMXO2280 Logic Signal Connections: 324 ftBGA

|             | T =           | LCMXO2280 |                |              |

|-------------|---------------|-----------|----------------|--------------|

| Ball Number | Ball Function | Bank      | Dual Function  | Differential |

| GND         | GNDIO7        | 7         |                |              |

| VCCIO7      | VCCIO7        | 7         |                |              |

| D4          | PL2A          | 7         | LUM0_PLLT_FB_A | Т            |

| F5          | PL2B          | 7         | LUM0_PLLC_FB_A | С            |

| B3          | PL3A          | 7         |                | T*           |

| C3          | PL3B          | 7         |                | C*           |

| E4          | PL3C          | 7         | LUM0_PLLT_IN_A | T            |

| G6          | PL3D          | 7         | LUM0_PLLC_IN_A | С            |

| A1          | PL4A          | 7         |                | T*           |

| B1          | PL4B          | 7         |                | C*           |

| F4          | PL4C          | 7         |                | Т            |

| VCC         | VCC           | -         |                |              |

| E3          | PL4D          | 7         |                | С            |

| D2          | PL5A          | 7         |                | T*           |

| D3          | PL5B          | 7         |                | C*           |

| G5          | PL5C          | 7         |                | Т            |

| F3          | PL5D          | 7         |                | С            |

| C2          | PL6A          | 7         |                | T*           |

| VCCIO7      | VCCIO7        | 7         |                |              |

| GND         | GNDIO7        | 7         |                |              |

| C1          | PL6B          | 7         |                | C*           |

| H5          | PL6C          | 7         |                | Т            |

| G4          | PL6D          | 7         |                | С            |

| E2          | PL7A          | 7         |                | T*           |

| D1          | PL7B          | 7         | GSRN           | C*           |

| J6          | PL7C          | 7         |                | Т            |

| H4          | PL7D          | 7         |                | С            |

| F2          | PL8A          | 7         |                | T*           |

| E1          | PL8B          | 7         |                | C*           |

| GND         | GND           | -         |                |              |

| J3          | PL8C          | 7         |                | Т            |

| J5          | PL8D          | 7         |                | С            |

| G3          | PL9A          | 7         |                | T*           |

| H3          | PL9B          | 7         |                | C*           |

| КЗ          | PL9C          | 7         |                | Т            |

| K5          | PL9D          | 7         |                | С            |

| F1          | PL10A         | 7         |                | T*           |

| VCCIO7      | VCCIO7        | 7         |                |              |

| GND         | GNDIO7        | 7         |                |              |

| G1          | PL10B         | 7         |                | C*           |

| K4          | PL10C         | 7         |                | Т            |

| K6          | PL10D         | 7         | +              | С            |

# LCMXO2280 Logic Signal Connections: 324 ftBGA (Cont.)

| Dall Number | Dell Function | LCMXO2280 | Duel Function | Differential |

|-------------|---------------|-----------|---------------|--------------|

| Ball Number | Ball Function | Bank      | Dual Function | Differential |

| A10         | PT8E          | 0         |               | Ţ            |

| VCCIO0      | VCCIO0        | 0         |               |              |

| GND         | GNDIO0        | 0         |               |              |

| A9          | PT8D          | 0         |               | С            |

| C9          | PT8C          | 0         |               | T            |

| B9          | PT8B          | 0         |               | С            |

| F9          | VCCAUX        | -         |               |              |

| A8          | PT8A          | 0         |               | T            |

| B8          | PT7D          | 0         |               | С            |

| C8          | PT7C          | 0         |               | Т            |

| VCC         | VCC           | -         |               |              |

| A7          | PT7B          | 0         |               | С            |

| B7          | PT7A          | 0         |               | Т            |

| A6          | PT6A          | 0         |               | Т            |

| B6          | PT6B          | 0         |               | С            |

| D8          | PT6C          | 0         |               | Т            |

| F8          | PT6D          | 0         |               | С            |

| C7          | PT6E          | 0         |               | Т            |

| E8          | PT6F          | 0         |               | С            |

| D7          | PT5D          | 0         |               | С            |

| VCCIO0      | VCCIO0        | 0         |               |              |

| GND         | GNDIO0        | 0         |               |              |

| E7          | PT5C          | 0         |               | Т            |

| A5          | PT5B          | 0         |               | С            |

| C6          | PT5A          | 0         |               | Т            |

| B5          | PT4A          | 0         |               | Т            |

| A4          | PT4B          | 0         |               | С            |

| D6          | PT4C          | 0         |               | Т            |

| F7          | PT4D          | 0         |               | С            |

| B4          | PT4E          | 0         |               | Т            |

| GND         | GND           | -         |               |              |

| C5          | PT4F          | 0         |               | С            |

| F6          | PT3D          | 0         |               | С            |

| E5          | PT3C          | 0         |               | Т            |

| E6          | PT3B          | 0         |               | С            |

| D5          | PT3A          | 0         |               | T            |

| A3          | PT2D          | 0         |               | С            |

| C4          | PT2C          | 0         |               | Т            |

| A2          | PT2B          | 0         |               | С            |

| B2          | PT2A          | 0         |               | Т            |

| VCCIO0      | VCCIO0        | 0         |               |              |

| GND         | GNDIO0        | 0         |               |              |

| E14         | GND           |           |               |              |

| Part Number        | LUTs | Supply Voltage | I/Os | Grade | Package | Pins | Temp. |

|--------------------|------|----------------|------|-------|---------|------|-------|

| LCMXO2280C-3T100C  | 2280 | 1.8V/2.5V/3.3V | 73   | -3    | TQFP    | 100  | COM   |

| LCMXO2280C-4T100C  | 2280 | 1.8V/2.5V/3.3V | 73   | -4    | TQFP    | 100  | COM   |