Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 18x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-VQFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128gp206a-e-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| <b>TABLE 1-1:</b> | PINOU       | T I/O DESC     | CRIPTIONS (CONTINUED)                                          |

|-------------------|-------------|----------------|----------------------------------------------------------------|

| Pin Name          | Pin<br>Type | Buffer<br>Type | Description                                                    |

| RG0-RG3           | I/O         | ST             | PORTG is a bidirectional I/O port.                             |

| RG6-RG9           | I/O         | ST             |                                                                |

| RG12-RG15         | I/O         | ST             |                                                                |

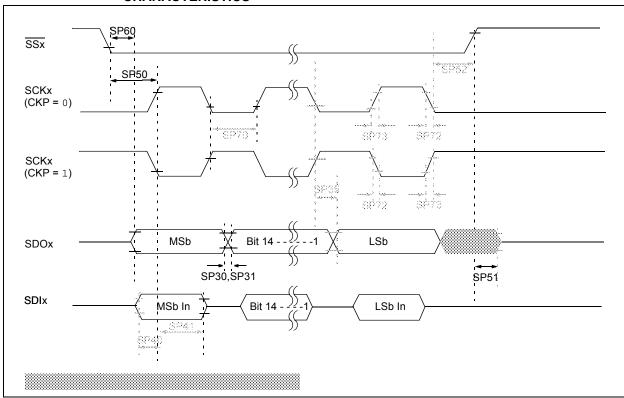

| SCK1              | I/O         | ST             | Synchronous serial clock input/output for SPI1.                |

| SDI1              | 1           | ST             | SPI1 data in.                                                  |

| SDO1              | 0           | _              | SPI1 data out.                                                 |

| SS1               | I/O         | ST             | SPI1 slave synchronization or frame pulse I/O.                 |

| SCK2              | I/O         | ST             | Synchronous serial clock input/output for SPI2.                |

| SDI2              | 1           | ST             | SPI2 data in.                                                  |

| SDO2              | 0           |                | SPI2 data out.                                                 |

| SS2               | I/O         | ST             | SPI2 slave synchronization or frame pulse I/O.                 |

| SCL1              | I/O         | ST             | Synchronous serial clock input/output for I2C1.                |

| SDA1              | I/O         | ST             | Synchronous serial data input/output for I2C1.                 |

| SCL2              | I/O         | ST             | Synchronous serial clock input/output for I2C2.                |

| SDA2              | I/O         | ST             | Synchronous serial data input/output for I2C2.                 |

| SOSCI             |             | ST/CMOS        | 32.768 kHz low-power oscillator crystal input; CMOS otherwise. |

| SOSCO             | 0           | _              | 32.768 kHz low-power oscillator crystal output.                |

| TMS               | 1           | ST             | JTAG Test mode select pin.                                     |

| тск               | 1           | ST             | JTAG test clock input pin.                                     |

| TDI               | 1           | ST             | JTAG test data input pin.                                      |

| TDO               | 0           | —              | JTAG test data output pin.                                     |

| T1CK              |             | ST             | Timer1 external clock input.                                   |

| T2CK              | I           | ST             | Timer2 external clock input.                                   |

| T3CK              | I           | ST             | Timer3 external clock input.                                   |

| T4CK              | I           | ST             | Timer4 external clock input.                                   |

| T5CK              | I           | ST             | Timer5 external clock input.                                   |

| T6CK              | I           | ST             | Timer6 external clock input.                                   |

| T7CK              | I           | ST             | Timer7 external clock input.                                   |

| T8CK              | I           | ST             | Timer8 external clock input.                                   |

| T9CK              |             | ST             | Timer9 external clock input.                                   |

| U1CTS             | I           | ST             | UART1 clear to send.                                           |

| U1RTS             | 0           | —              | UART1 ready to send.                                           |

| U1RX              | 1           | ST             | UART1 receive.                                                 |

| U1TX              | 0           |                | UART1 transmit.                                                |

| U2CTS             |             | ST             | UART2 clear to send.                                           |

| U2RTS             | 0           |                | UART2 ready to send.                                           |

| U2RX              |             | ST             | UART2 receive.                                                 |

| U2TX              | 0           | _              | UART2 transmit.                                                |

| VDD               | P           | —              | Positive supply for peripheral logic and I/O pins.             |

| VCAP              | P           | —              | CPU logic fiter capacitor connection.                          |

| Vss               | P           | <u> </u>       | Ground reference for logic and I/O pins.                       |

| VREF+             |             | Analog         | Analog voltage reference (high) input.                         |

| VREF-             |             | Analog         | Analog voltage reference (low) input.                          |

| Legend: CN        | IOS = CMO   | S compatible   | e input or output; Analog = Analog input; P = Power            |

### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend: CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels;

Analog = Analog input; O = Output; P = Power I = Input

### 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to  $\leq$  8 MHz for start-up with PLL enabled to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLDBF to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration word.

## 2.8 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 3 or REAL ICE is selected as a debugger, it automatically initializes all of the A/D input pins (ANx) as "digital" pins, by setting all bits in the ADPCFG and ADPCFG2 registers.

The bits in the registers that correspond to the A/D pins that are initialized by ICD 3 or REAL ICE, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain A/D pins as analog input pins during the debug session, the user application must clear the corresponding bits in the ADPCFG and ADPCFG2 registers during initialization of the ADC module.

When ICD 3 or REAL ICE is used as a programmer, the user application firmware must correctly configure the ADPCFG and ADPCFG2 registers. Automatic initialization of these registers is only done during debugger operation. Failure to correctly configure the register(s) will result in all A/D pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

## 2.9 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic-low state.

Alternatively, connect a 1k to 10k resistor between Vss and the unused pins.

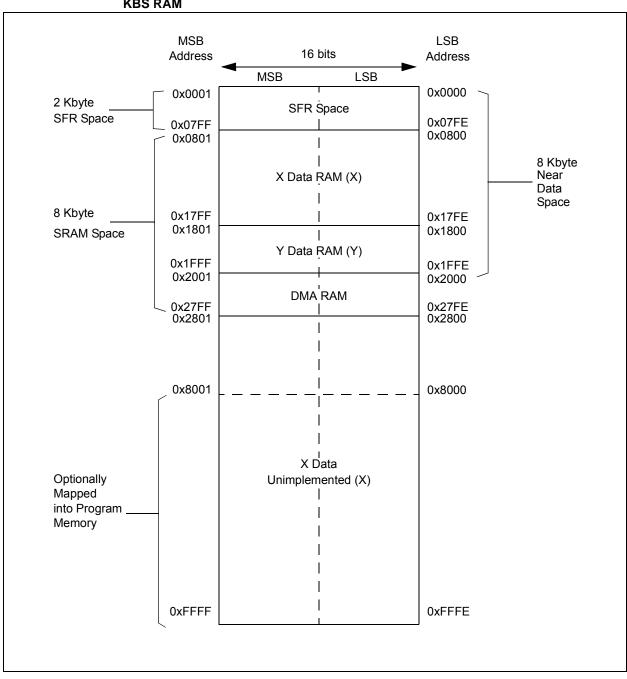

#### FIGURE 4-3: DATA MEMORY MAP FOR dsPIC33FJXXXGPX06A/X08A/X10A DEVICES WITH 8 KBS RAM

## TABLE 4-23: ECAN2 REGISTER MAP WHEN C2CTRL1.WIN = 1 FOR dsPIC33FJXXXGP706A/708A/710A DEVICES ONLY

| File Name  | Addr      | Bit 15    | Bit 14 | Bit 13              | Bit 12 | Bit 11 | Bit 10 | Bit 9         | Bit 8        | Bit 7                         | Bit 6     | Bit 5  | Bit 4        | Bit 3              | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|------------|-----------|-----------|--------|---------------------|--------|--------|--------|---------------|--------------|-------------------------------|-----------|--------|--------------|--------------------|-------|--------|-------|---------------|

|            | 0500      |           |        |                     |        |        |        | Se            | e definition | n when WIN = x                |           |        |              |                    |       |        |       |               |

|            | -<br>051E |           |        |                     |        |        |        |               |              |                               |           |        |              |                    |       |        |       |               |

| C2BUFPNT1  | 0520      |           | F3BF   | ><3:0>              |        |        | F2BF   | <b>~</b> 3:0> |              |                               | F1BF      | <3:0>  |              |                    | F0BF  | P<3:0> |       | 0000          |

| C2BUFPNT2  | 0522      |           | F7BF   | F7BP<3:0> F6BP<3:0> |        |        |        |               | F5BF         | ><3:0>                        |           |        | F4BF         | P<3:0>             |       | 0000   |       |               |

| C2BUFPNT3  | 0524      |           | F11B   | ><3:0>              |        |        | F10BF  | ><3:0>        |              |                               | F9BF      | ><3:0> |              |                    | F8BF  | P<3:0> |       | 0000          |

| C2BUFPNT4  | 0526      |           | F15B   | P<3:0>              |        |        | F14BF  | ><3:0>        |              |                               | F13BI     | ><3:0> |              |                    | F12B  | P<3:0> |       | 0000          |

| C2RXM0SID  | 0530      |           |        |                     | SID<   | 10:3>  |        |               |              |                               | SID<2:0>  |        | —            | MIDE               | —     | EID<1  | 7:16> | xxxx          |

| C2RXM0EID  | 0532      |           |        |                     | EID<   | 15:8>  |        |               |              |                               |           |        | EID∙         | <7:0>              |       |        |       | xxxx          |

| C2RXM1SID  | 0534      |           |        |                     | SID<   | 10:3>  |        |               |              |                               | SID<2:0>  |        | _            | MIDE               | _     | EID<1  | 7:16> | xxxx          |

| C2RXM1EID  | 0536      |           |        |                     | EID<   | 15:8>  |        |               |              |                               |           |        | EID          | <7:0>              |       |        |       | xxxx          |

| C2RXM2SID  | 0538      |           |        |                     | SID<   | 10:3>  |        |               |              |                               | SID<2:0>  |        | -            | MIDE               | —     | EID<   | 7:16> | xxxx          |

| C2RXM2EID  | 053A      |           |        |                     | EID<   | 15:8>  |        |               |              |                               |           |        | EID          | <7:0>              |       |        |       | xxxx          |

| C2RXF0SID  | 0540      |           |        |                     | SID<   | 10:3>  |        |               |              | SID<2:0> — E>                 |           |        | EXIDE        | EXIDE — EID<17:16> |       |        | xxxx  |               |

| C2RXF0EID  | 0542      |           |        |                     | EID<   | 15:8>  |        |               |              | EID<7:0>                      |           |        |              | xxxx               |       |        |       |               |

| C2RXF1SID  | 0544      |           |        |                     | SID<   | 10:3>  |        |               |              |                               | SID<2:0>  |        | —            | EXIDE              | —     | EID<'  | 7:16> | xxxx          |

| C2RXF1EID  | 0546      |           |        |                     | EID<   | 15:8>  |        |               |              | EID<7:0>                      |           |        |              |                    | xxxx  |        |       |               |

| C2RXF2SID  | 0548      |           |        |                     | SID<   | 10:3>  |        |               |              | SID<2:0> —                    |           |        | EXIDE        |                    | EID<  | 7:16>  | xxxx  |               |

| C2RXF2EID  | 054A      |           |        |                     | EID<   | 15:8>  |        |               |              | EID<7:0>                      |           |        |              |                    |       | xxxx   |       |               |

| C2RXF3SID  | 054C      |           |        |                     | SID<   | 10:3>  |        |               |              | SID<2:0> — EXIDE              |           |        | — EID<17:16> |                    | xxxx  |        |       |               |

| C2RXF3EID  | 054E      |           |        |                     | EID<   | 15:8>  |        |               |              | EID<7:0>                      |           |        |              |                    |       | xxxx   |       |               |

| C2RXF4SID  | 0550      |           |        |                     | SID<   | 10:3>  |        |               |              | SID<2:0> — EXIDE — EID<17:16> |           |        |              |                    | 7:16> | xxxx   |       |               |

| C2RXF4EID  | 0552      |           |        |                     | EID<   |        |        |               |              |                               |           |        | EID          | <7:0>              |       | -      |       | XXXX          |

| C2RXF5SID  | 0554      |           |        |                     | SID<   |        |        |               |              |                               | SID<2:0>  |        | —            | EXIDE              | —     | EID<'  | 7:16> | XXXX          |

| C2RXF5EID  | 0556      |           |        |                     | EID<   |        |        |               |              |                               |           |        | EID          | <7:0>              |       |        |       | XXXX          |

| C2RXF6SID  | 0558      |           |        |                     | SID<   |        |        |               |              |                               | SID<2:0>  |        | —            | EXIDE              | —     | EID<   | 7:16> | XXXX          |

| C2RXF6EID  | 055A      |           |        |                     | EID<   |        |        |               |              |                               |           |        | EID          | <7:0>              |       |        |       | xxxx          |

| C2RXF7SID  | 055C      |           |        |                     | SID<   |        |        |               |              |                               | SID<2:0>  |        | -            | EXIDE              | —     | EID<   | 7:16> | xxxx          |

| C2RXF7EID  | 055E      | EID<15:8> |        |                     |        |        |        |               |              | EID                           | <7:0>     |        |              |                    | xxxx  |        |       |               |

| C2RXF8SID  | 0560      |           |        |                     | SID<   |        |        |               |              | SID<2:0> — EXIDE — EID<17     |           |        | /:16>        | XXXX               |       |        |       |               |

| C2RXF8EID  | 0562      |           |        |                     | EID<   |        |        |               |              | EID<7:0>                      |           |        | 7.40         | XXXX               |       |        |       |               |

| C2RXF9SID  | 0564      |           |        |                     | SID<   |        |        |               |              |                               | SID<2:0>  |        |              | EXIDE              |       | EID<   | 7:16> | XXXX          |

| C2RXF9EID  | 0566      |           |        |                     | EID<   |        |        |               |              |                               | 010 40-0- |        |              | <7:0>              |       |        | 7.40  | XXXX          |

| C2RXF10SID | 0568      |           |        |                     | SID<   |        |        |               |              |                               | SID<2:0>  |        | —            | EXIDE              |       | EID<   | 7:16> | XXXX          |

dsPIC33FJXXXGPX06A/X08A/X10A

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 5.4.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

The user can program one row of program Flash memory at a time. To do this, it is necessary to erase the 8-row erase page that contains the desired row. The general process is:

- 1. Read eight rows of program memory (512 instructions) and store in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase the block (see Example 5-1):

- a) Set the NVMOP bits (NVMCON<3:0>) to '0010' to configure for block erase. Set the ERASE bit (NVMCON<6>) and the WREN bit (NVMCON<14>).

- b) Write the starting address of the page to be erased into the TBLPAG and W registers.

- c) Write 0x55 to NVMKEY.

- d) Write 0xAA to NVMKEY.

- e) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 64 instructions from data RAM into the program memory buffers (see Example 5-2).

- 5. Write the program block to Flash memory:

- a) Set the NVMOP bits to '0001' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 0x55 to NVMKEY.

- c) Write 0xAA to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

- Repeat steps 4 and 5, using the next available 64 instructions from the block in data RAM by incrementing the value in TBLPAG, until all 512 instructions are written back to Flash memory.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as shown in Example 5-3.

### EXAMPLE 5-1: ERASING A PROGRAM MEMORY PAGE

| ; Set up NVMCON for block erase operation |                                         |

|-------------------------------------------|-----------------------------------------|

| MOV #0x4042, W0                           | i                                       |

| MOV W0, NVMCON                            | ; Initialize NVMCON                     |

| ; Init pointer to row to be ERASED        |                                         |

| MOV #tblpage(PROG_ADDR), W0               | ;                                       |

| MOV W0, TBLPAG                            | ; Initialize PM Page Boundary SFR       |

| MOV #tbloffset(PROG_ADDR), W0             | ; Initialize in-page EA[15:0] pointer   |

| TBLWTL W0, [W0]                           | ; Set base address of erase block       |

| DISI #5                                   | ; Block all interrupts with priority <7 |

|                                           | ; for next 5 instructions               |

| MOV #0x55, W0                             |                                         |

| MOV W0, NVMKEY                            | ; Write the 55 key                      |

| MOV #0xAA, W1                             | i                                       |

| MOV W1, NVMKEY                            | ; Write the AA key                      |

| BSET NVMCON, #WR                          | ; Start the erase sequence              |

| NOP                                       | ; Insert two NOPs after the erase       |

| NOP                                       | ; command is asserted                   |

|                                           |                                         |

| U-0           | U-0           | U-0                           | U-0             | U-0                                    | R/W-1           | R/W-0      | R/W-0 |  |  |  |  |

|---------------|---------------|-------------------------------|-----------------|----------------------------------------|-----------------|------------|-------|--|--|--|--|

|               | _             | _                             |                 | _                                      |                 | U2EIP<2:0> |       |  |  |  |  |

| bit 15        |               |                               |                 |                                        |                 |            | bit   |  |  |  |  |

|               |               |                               |                 |                                        |                 |            |       |  |  |  |  |

| U-0           | R/W-1         | R/W-0                         | R/W-0           | U-0                                    | U-0             | U-0        | U-0   |  |  |  |  |

|               |               | U1EIP<2:0>                    |                 |                                        | —               | —          |       |  |  |  |  |

| bit 7         |               |                               |                 |                                        |                 |            | bit ( |  |  |  |  |

| Legend:       |               |                               |                 |                                        |                 |            |       |  |  |  |  |

| R = Readabl   | le bit        | W = Writable I                | oit             | U = Unimpler                           | mented bit, rea | d as '0'   |       |  |  |  |  |

| -n = Value at |               | '1' = Bit is set              |                 | 0' = Bit is cleared x = Bit is unknown |                 |            |       |  |  |  |  |

|               |               |                               |                 |                                        |                 |            | -     |  |  |  |  |

| bit 15-11     | Unimplemen    | ted: Read as 'o               | )'              |                                        |                 |            |       |  |  |  |  |

| bit 10-8      | U2EIP<2:0>:   | UART2 Error In                | nterrupt Prior  | ity bits                               |                 |            |       |  |  |  |  |

|               | 111 = Interru | pt is priority 7 (ł           | nighest priorit | y interrupt)                           |                 |            |       |  |  |  |  |

|               | •             |                               |                 |                                        |                 |            |       |  |  |  |  |

|               | •             |                               |                 |                                        |                 |            |       |  |  |  |  |

|               | 001 = Interru | 001 = Interrupt is priority 1 |                 |                                        |                 |            |       |  |  |  |  |

|               | 000 = Interru | pt source is dis              | abled           |                                        |                 |            |       |  |  |  |  |

| bit 7         | Unimplemen    | ted: Read as 'd               | )'              |                                        |                 |            |       |  |  |  |  |

| bit 6-4       | U1EIP<2:0>:   | UART1 Error In                | nterrupt Prior  | ity bits                               |                 |            |       |  |  |  |  |

|               | 111 = Interru | pt is priority 7 (I           | nighest priorit | y interrupt)                           |                 |            |       |  |  |  |  |

|               | •             |                               |                 |                                        |                 |            |       |  |  |  |  |

|               | •             |                               |                 |                                        |                 |            |       |  |  |  |  |

|               | 001 = Interru | pt is priority 1              |                 |                                        |                 |            |       |  |  |  |  |

|               |               | pt source is dis              | abled           |                                        |                 |            |       |  |  |  |  |

|               |               |                               |                 |                                        |                 |            |       |  |  |  |  |

### bit 3-0 Unimplemented: Read as '0'

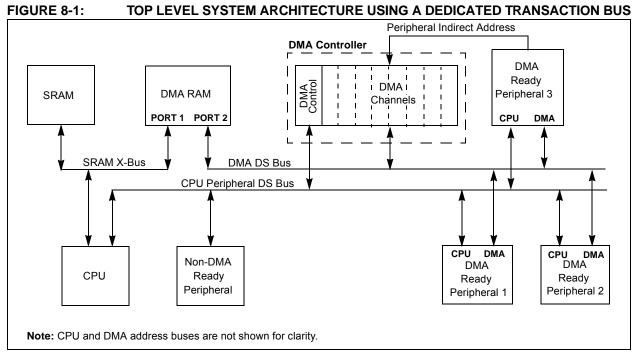

## 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/X08A/ X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 22. "Direct Memory Access (DMA)" (DS70182) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

Direct Memory Access (DMA) is a very efficient mechanism of copying data between peripheral SFRs (e.g., UART Receive register, Input Capture 1 buffer), and buffers or variables stored in RAM, with minimal CPU intervention. The DMA controller can automatically copy entire blocks of data without requiring the user software to read or write the peripheral Special Function Registers (SFRs) every time a peripheral interrupt occurs. The DMA controller uses a dedicated bus for data transfers and therefore, does not steal cycles from the code execution flow of the CPU. To exploit the DMA capability, the corresponding user buffers or variables must be located in DMA RAM.

The dsPIC33FJXXXGPX06A/X08A/X10A peripherals that can utilize DMA are listed in Table 8-1 along with their associated Interrupt Request (IRQ) numbers.

### TABLE 8-1: PERIPHERALS WITH DMA SUPPORT

| Peripheral         | IRQ Number |

|--------------------|------------|

| INT0               | 0          |

| Input Capture 1    | 1          |

| Input Capture 2    | 5          |

| Output Compare 1   | 2          |

| Output Compare 2   | 6          |

| Timer2             | 7          |

| Timer3             | 8          |

| SPI1               | 10         |

| SPI2               | 33         |

| UART1 Reception    | 11         |

| UART1 Transmission | 12         |

| UART2 Reception    | 30         |

| UART2 Transmission | 31         |

| ADC1               | 13         |

| ADC2               | 21         |

| DCI                | 60         |

| ECAN1 Reception    | 34         |

| ECAN1 Transmission | 70         |

| ECAN2 Reception    | 55         |

| ECAN2 Transmission | 71         |

The DMA controller features eight identical data transfer channels.

Each channel has its own set of control and status registers. Each DMA channel can be configured to copy data either from buffers stored in dual port DMA RAM to peripheral SFRs, or from peripheral SFRs to buffers in DMA RAM.

The DMA controller supports the following features:

- · Word or byte sized data transfers

- Transfers from peripheral to DMA RAM or DMA RAM to peripheral

- Indirect Addressing of DMA RAM locations with or without automatic post-increment

- Peripheral Indirect Addressing In some peripherals, the DMA RAM read/write addresses may be partially derived from the peripheral

- One-Shot Block Transfers Terminating DMA transfer after one block transfer

- Continuous Block Transfers Reloading DMA RAM buffer start address after every block transfer is complete

- Ping-Pong Mode Switching between two DMA RAM start addresses between successive block transfers, thereby filling two buffers alternately

- Automatic or manual initiation of block transfers

- Each channel can select from 20 possible sources of data sources or destinations

For each DMA channel, a DMA interrupt request is generated when a block transfer is complete. Alternatively, an interrupt can be generated when half of the block has been filled.

## 8.1 DMAC Registers

Each DMAC Channel x (x = 0, 1, 2, 3, 4, 5, 6 or 7) contains the following registers:

- A 16-bit DMA Channel Control register (DMAxCON)

- A 16-bit DMA Channel IRQ Select register (DMAxREQ)

- A 16-bit DMA RAM Primary Start Address Offset register (DMAxSTA)

- A 16-bit DMA RAM Secondary Start Address Offset register (DMAxSTB)

- A 16-bit DMA Peripheral Address register (DMAxPAD)

- A 10-bit DMA Transfer Count register (DMAxCNT)

An additional pair of status registers, DMACS0 and DMACS1, are common to all DMAC channels.

#### REGISTER 8-7: DMACS0: DMA CONTROLLER STATUS REGISTER 0

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| PWCOL7 | PWCOL6 | PWCOL5 | PWCOL4 | PWCOL3 | PWCOL2 | PWCOL1 | PWCOL0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| XWCOL7 | XWCOL6 | XWCOL5 | XWCOL4 | XWCOL3 | XWCOL2 | XWCOL1 | XWCOL0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:      |           | C = Clear only bit                                                                               |                        |                    |

|--------------|-----------|--------------------------------------------------------------------------------------------------|------------------------|--------------------|

| R = Readab   | ole bit   | W = Writable bit                                                                                 | U = Unimplemented bit, | read as '0'        |

| -n = Value a | It POR    | '1' = Bit is set                                                                                 | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15       | 1 = Write | 7: Channel 7 Peripheral Writ<br>collision detected<br>rite collision detected                    | e Collision Flag bit   |                    |

| bit 14       | 1 = Write | 5: Channel 6 Peripheral Writ<br>collision detected<br>rite collision detected                    | e Collision Flag bit   |                    |

| bit 13       | 1 = Write | 5: Channel 5 Peripheral Writ<br>collision detected<br>rite collision detected                    | e Collision Flag bit   |                    |

| bit 12       | 1 = Write | <ol> <li>Channel 4 Peripheral Writ<br/>collision detected<br/>rite collision detected</li> </ol> | e Collision Flag bit   |                    |

| bit 11       | 1 = Write | 3: Channel 3 Peripheral Writ<br>collision detected<br>rite collision detected                    | e Collision Flag bit   |                    |

| bit 10       | 1 = Write | 2: Channel 2 Peripheral Writ<br>collision detected<br>rite collision detected                    | e Collision Flag bit   |                    |

| bit 9        | 1 = Write | I: Channel 1 Peripheral Writ<br>collision detected<br>rite collision detected                    | e Collision Flag bit   |                    |

| bit 8        | 1 = Write | <b>D:</b> Channel 0 Peripheral Writ<br>collision detected<br>rite collision detected             | e Collision Flag bit   |                    |

| bit 7        | 1 = Write | 7: Channel 7 DMA RAM Writ<br>collision detected<br>rite collision detected                       | e Collision Flag bit   |                    |

| bit 6        | 1 = Write | 5: Channel 6 DMA RAM Writ<br>collision detected<br>rite collision detected                       | te Collision Flag bit  |                    |

| bit 5        | 1 = Write | 5: Channel 5 DMA RAM Writ<br>collision detected<br>rite collision detected                       | e Collision Flag bit   |                    |

| bit 4        | 1 = Write | I: Channel 4 DMA RAM Write<br>collision detected<br>rite collision detected                      | te Collision Flag bit  |                    |

| U-0           | U-0                                                                                              | U-0                                                                                               | U-0            | R-1               | R-1              | R-1             | R-1   |  |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------|-------------------|------------------|-----------------|-------|--|--|--|--|--|

| —             | _                                                                                                | —                                                                                                 | —              |                   | LSTCH            | +<3:0>          |       |  |  |  |  |  |

| oit 15        | ÷                                                                                                |                                                                                                   |                |                   |                  |                 | bit   |  |  |  |  |  |

| R-0           | R-0                                                                                              | R-0                                                                                               | R-0            | R-0               | R-0              | R-0             | R-0   |  |  |  |  |  |

| PPST7         | PPST6                                                                                            | PPST5                                                                                             | PPST4          | PPST3             | PPST2            | PPST1           | PPST0 |  |  |  |  |  |

| bit 7         |                                                                                                  |                                                                                                   |                |                   |                  | I               | bit   |  |  |  |  |  |

| Legend:       |                                                                                                  |                                                                                                   |                |                   |                  |                 |       |  |  |  |  |  |

| R = Readabl   | e bit                                                                                            | W = Writable                                                                                      | bit            | U = Unimplem      | nented bit, read | as '0'          |       |  |  |  |  |  |

| -n = Value at | POR                                                                                              | '1' = Bit is set                                                                                  |                | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |  |  |  |  |  |

| bit 15-12     | Unimplemen                                                                                       | ted: Read as '                                                                                    | 0'             |                   |                  |                 |       |  |  |  |  |  |

| bit 11-8      | LSTCH<3:0>                                                                                       | : Last DMA Ch                                                                                     | annel Active t | oits              |                  |                 |       |  |  |  |  |  |

|               | 1111 = No DM                                                                                     | MA transfer ha                                                                                    | s occurred sin | ce system Res     | et               |                 |       |  |  |  |  |  |

|               | 1110-1000 =                                                                                      |                                                                                                   |                |                   |                  |                 |       |  |  |  |  |  |

|               |                                                                                                  | lata transfer wa                                                                                  |                |                   |                  |                 |       |  |  |  |  |  |

|               |                                                                                                  | 0110 = Last data transfer was by DMA Channel 6                                                    |                |                   |                  |                 |       |  |  |  |  |  |

|               | 0101 = Last data transfer was by DMA Channel 5<br>0100 = Last data transfer was by DMA Channel 4 |                                                                                                   |                |                   |                  |                 |       |  |  |  |  |  |

|               | 0011 = Last data transfer was by DMA Channel 3                                                   |                                                                                                   |                |                   |                  |                 |       |  |  |  |  |  |

|               | 0010 = Last data transfer was by DMA Channel 2                                                   |                                                                                                   |                |                   |                  |                 |       |  |  |  |  |  |

|               |                                                                                                  | 0001 = Last data transfer was by DMA Channel 1                                                    |                |                   |                  |                 |       |  |  |  |  |  |

| bit 7         |                                                                                                  | 0000 = Last data transfer was by DMA Channel 0<br>PPST7: Channel 7 Ping-Pong Mode Status Flag bit |                |                   |                  |                 |       |  |  |  |  |  |

|               | 1 = DMA7STE                                                                                      | B register selec                                                                                  | ted            | S Flag bit        |                  |                 |       |  |  |  |  |  |

| bit 6         |                                                                                                  | 0 = DMA7STA register selected PPST6: Channel 6 Ping-Pong Mode Status Flag bit                     |                |                   |                  |                 |       |  |  |  |  |  |

|               |                                                                                                  | 1 = DMA6STB register selected                                                                     |                |                   |                  |                 |       |  |  |  |  |  |

|               |                                                                                                  | A register selec                                                                                  |                |                   |                  |                 |       |  |  |  |  |  |

| bit 5         | PPST5: Chan                                                                                      | nel 5 Ping-Por                                                                                    | ng Mode Statu  | s Flag bit        |                  |                 |       |  |  |  |  |  |

|               | 1 = DMA5STE                                                                                      | <b>PPST5:</b> Channel 5 Ping-Pong Mode Status Flag bit<br>1 = DMA5STB register selected           |                |                   |                  |                 |       |  |  |  |  |  |

|               | 0 = DMA5STA                                                                                      | A register selec                                                                                  | ted            |                   |                  |                 |       |  |  |  |  |  |

| bit 4         | PPST4: Chan                                                                                      | inel 4 Ping-Por                                                                                   | ng Mode Statu  | s Flag bit        |                  |                 |       |  |  |  |  |  |

|               |                                                                                                  | B register select<br>A register select                                                            |                |                   |                  |                 |       |  |  |  |  |  |

| bit 3         | PPST3: Chan                                                                                      | inel 3 Ping-Por                                                                                   | ng Mode Statu  | s Flag bit        |                  |                 |       |  |  |  |  |  |

|               |                                                                                                  | B register select<br>A register select                                                            |                |                   |                  |                 |       |  |  |  |  |  |

| bit 2         | PPST2: Channel 2 Ping-Pong Mode Status Flag bit                                                  |                                                                                                   |                |                   |                  |                 |       |  |  |  |  |  |

|               | 1 = DMA2STE                                                                                      | B register select                                                                                 | ted            |                   |                  |                 |       |  |  |  |  |  |

| bit 1         |                                                                                                  | inel 1 Ping-Por                                                                                   |                | s Flao bit        |                  |                 |       |  |  |  |  |  |

|               | 1 = DMA1STE                                                                                      | B register select<br>register select                                                              | cted           |                   |                  |                 |       |  |  |  |  |  |

| bit 0         |                                                                                                  | inel 0 Ping-Por                                                                                   |                | s Flag bit        |                  |                 |       |  |  |  |  |  |

|               |                                                                                                  | B register selec                                                                                  | -              |                   |                  |                 |       |  |  |  |  |  |

#### REGISTER 10-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2 (CONTINUED)

| bit 3 | <b>OC4MD:</b> Output Compare 4 Module Disable bit                                                        |

|-------|----------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Output Compare 4 module is disabled</li><li>0 = Output Compare 4 module is enabled</li></ul> |

| bit 2 | <b>OC3MD:</b> Output Compare 3 Module Disable bit                                                        |

|       | <ul><li>1 = Output Compare 3 module is disabled</li><li>0 = Output Compare 3 module is enabled</li></ul> |

| bit 1 | <b>OC2MD:</b> Output Compare 2 Module Disable bit                                                        |

|       | <ul><li>1 = Output Compare 2 module is disabled</li><li>0 = Output Compare 2 module is enabled</li></ul> |

| bit 0 | <b>OC1MD:</b> Output Compare 1 Module Disable bit                                                        |

|       | 1 = Output Compare 1 module is disabled                                                                  |

|       | 0 = Output Compare 1 module is enabled                                                                   |

|       |                                                                                                          |

| REGISTER      | 12-1: T1CO                                              | N: TIMER1 C                                          | ONTROL R        | EGISTER                 |                  |                 |       |  |  |  |  |

|---------------|---------------------------------------------------------|------------------------------------------------------|-----------------|-------------------------|------------------|-----------------|-------|--|--|--|--|

| R/W-0         | U-0                                                     | R/W-0                                                | U-0             | U-0                     | U-0              | U-0             | U-0   |  |  |  |  |

| TON           |                                                         | TSIDL                                                | —               | _                       | —                | —               | _     |  |  |  |  |

| bit 15        |                                                         |                                                      |                 |                         |                  |                 | bit 8 |  |  |  |  |

|               |                                                         |                                                      |                 |                         |                  |                 |       |  |  |  |  |

| U-0           | R/W-0                                                   | R/W-0                                                | R/W-0           | U-0                     | R/W-0            | R/W-0           | U-0   |  |  |  |  |

|               | TGATE                                                   | TCKP                                                 | S<1:0>          |                         | TSYNC            | TCS             | _     |  |  |  |  |

| bit 7         |                                                         |                                                      |                 |                         |                  |                 | bit 0 |  |  |  |  |

| <del></del>   |                                                         |                                                      |                 |                         |                  |                 |       |  |  |  |  |

| Legend:       |                                                         |                                                      |                 |                         |                  | 1               |       |  |  |  |  |

| R = Readabl   |                                                         | W = Writable                                         |                 | -                       | mented bit, read |                 |       |  |  |  |  |

| -n = Value at | POR                                                     | '1' = Bit is set                                     |                 | '0' = Bit is cle        | eared            | x = Bit is unkn | own   |  |  |  |  |

| bit 15        | <b>TON:</b> Timer1<br>1 = Starts 16-<br>0 = Stops 16-   | bit Timer1                                           |                 |                         |                  |                 |       |  |  |  |  |

| bit 14        | -                                                       | ited: Read as '                                      | 0'              |                         |                  |                 |       |  |  |  |  |

| bit 13        | -                                                       | in Idle Mode bi                                      |                 |                         |                  |                 |       |  |  |  |  |

|               | 1 = Discontin                                           |                                                      | ration when     | device enters lo<br>ode | lle mode         |                 |       |  |  |  |  |

| bit 12-7      | Unimplemen                                              | ted: Read as '                                       | 0'              |                         |                  |                 |       |  |  |  |  |

| bit 6         | <b>TGATE:</b> Timer1 Gated Time Accumulation Enable bit |                                                      |                 |                         |                  |                 |       |  |  |  |  |

|               |                                                         | When TCS = 1:                                        |                 |                         |                  |                 |       |  |  |  |  |

|               | •                                                       | This bit is ignored.                                 |                 |                         |                  |                 |       |  |  |  |  |

|               |                                                         | When TCS = 0:<br>1 = Gated time accumulation enabled |                 |                         |                  |                 |       |  |  |  |  |

|               |                                                         | ne accumulatio                                       |                 |                         |                  |                 |       |  |  |  |  |

| bit 5-4       | TCKPS<1:0>                                              | : Timer1 Input                                       | Clock Presca    | ale Select bits         |                  |                 |       |  |  |  |  |

|               | 11 <b>= 1:256</b>                                       |                                                      |                 |                         |                  |                 |       |  |  |  |  |

|               |                                                         | 10 = 1:64                                            |                 |                         |                  |                 |       |  |  |  |  |

|               | 01 = 1:8<br>00 = 1:1                                    |                                                      |                 |                         |                  |                 |       |  |  |  |  |

| bit 3         | Unimplemen                                              | ted: Read as '                                       | 0'              |                         |                  |                 |       |  |  |  |  |

| bit 2         | TSYNC: Time                                             | er1 External Cl                                      | ock Input Syr   | hchronization S         | elect bit        |                 |       |  |  |  |  |

|               | When TCS =                                              |                                                      |                 |                         |                  |                 |       |  |  |  |  |

|               |                                                         | ize external clo                                     |                 |                         |                  |                 |       |  |  |  |  |

|               | 0 = Do not sy<br>When TCS =                             | nchronize exte                                       | ernal clock inp | but                     |                  |                 |       |  |  |  |  |

|               | This bit is ign                                         |                                                      |                 |                         |                  |                 |       |  |  |  |  |

| bit 1         | -                                                       | Clock Source                                         | Select bit      |                         |                  |                 |       |  |  |  |  |

|               |                                                         | clock from pin                                       |                 | rising edge)            |                  |                 |       |  |  |  |  |

|               | 0 = Internal c                                          |                                                      |                 |                         |                  |                 |       |  |  |  |  |

| bit 0         | Unimplemen                                              | ted: Read as '                                       | 0'              |                         |                  |                 |       |  |  |  |  |

|               |                                                         |                                                      |                 |                         |                  |                 |       |  |  |  |  |

## **19.3 Modes of Operation**

The CAN module can operate in one of several operation modes selected by the user. These modes include:

- Initialization Mode

- Disable Mode

- Normal Operation Mode

- Listen Only Mode

- Listen All Messages Mode

- Loopback Mode

Modes are requested by setting the REQOP<2:0> bits (CiCTRL1<10:8>). Entry into a mode is Acknowledged by monitoring the OPMODE<2:0> bits (CiCTRL1<7:5>). The module will not change the mode and the OPMODE bits until a change in mode is acceptable, generally during bus Idle time, which is defined as at least 11 consecutive recessive bits.

### 19.3.1 INITIALIZATION MODE

In the Initialization mode, the module will not transmit or receive. The error counters are cleared and the interrupt flags remain unchanged. The programmer will have access to Configuration registers that are access restricted in other modes. The module will protect the user from accidentally violating the CAN protocol through programming errors. All registers which control the configuration of the module cannot be modified while the module is on-line. The CAN module will not be allowed to enter the Configuration mode while a transmission is taking place. The Configuration mode serves as a lock to protect the following registers:

- All Module Control Registers

- Baud Rate and Interrupt Configuration Registers

- Bus Timing Registers

- Identifier Acceptance Filter Registers

- Identifier Acceptance Mask Registers

### 19.3.2 DISABLE MODE

In Disable mode, the module will not transmit or receive. The module has the ability to set the WAKIF bit due to bus activity, however, any pending interrupts will remain and the error counters will retain their value.

If the REQOP<2:0> bits (CiCTRL1<10:8>) = 001, the module will enter the Module Disable mode. If the module is active, the module will wait for 11 recessive bits on the CAN bus, detect that condition as an Idle bus, then accept the module disable command. When the OPMODE<2:0> bits (CiCTRL1<7:5>) = 001, that indicates whether the module successfully went into Module Disable mode. The I/O pins will revert to normal I/O function when the module is in the Module Disable mode.

The module can be programmed to apply a low-pass filter function to the CiRX input line while the module or the CPU is in Sleep mode. The WAKFIL bit (CiCFG2<14>) enables or disables the filter.

Note: Typically, if the CAN module is allowed to transmit in a particular mode of operation and a transmission is requested immediately after the CAN module has been placed in that mode of operation, the module waits for 11 consecutive recessive bits on the bus before starting transmission. If the user switches to Disable mode within this 11-bit period, then this transmission is aborted and the corresponding TXABT bit is set and TXREQ bit is cleared.

## 19.3.3 NORMAL OPERATION MODE

Normal Operation mode is selected when REQOP<2:0> = 000. In this mode, the module is activated and the I/O pins will assume the CAN bus functions. The module will transmit and receive CAN bus messages via the CiTX and CiRX pins.

## 19.3.4 LISTEN ONLY MODE

If the Listen Only mode is activated, the module on the CAN bus is passive. The transmitter buffers revert to the port I/O function. The receive pins remain inputs. For the receiver, no error flags or Acknowledge signals are sent. The error counters are deactivated in this state. The Listen Only mode can be used for detecting the baud rate on the CAN bus. To use this, it is necessary that there are at least two further nodes that communicate with each other.

### 19.3.5 LISTEN ALL MESSAGES MODE

The module can be set to ignore all errors and receive any message. The Listen All Messages mode is activated by setting REQOP<2:0> = '111'. In this mode, the data which is in the message assembly buffer, until the time an error occurred, is copied in the receive buffer and can be read via the CPU interface.

### 19.3.6 LOOPBACK MODE

If the Loopback mode is activated, the module will connect the internal transmit signal to the internal receive signal at the module boundary. The transmit and receive pins revert to their port I/O function.

| U-0             | U-0                                                                                                                                                  | R/W-0            | R/W-0     | r-0               | R/W-1            | R/W-0           | R/W-0 |  |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------|-------------------|------------------|-----------------|-------|--|--|--|--|

| _               | —                                                                                                                                                    | CSIDL            | ABAT      | —                 |                  | REQOP<2:0>      |       |  |  |  |  |

| bit 15          |                                                                                                                                                      |                  |           |                   |                  |                 | bit   |  |  |  |  |

| R-1             | R-0                                                                                                                                                  | R-0              | U-0       | R/W-0             | U-0              | U-0             | R/W-0 |  |  |  |  |

|                 | OPMODE<2:0                                                                                                                                           |                  | _         | CANCAP            | _                | _               | WIN   |  |  |  |  |

| bit 7           |                                                                                                                                                      |                  |           |                   |                  |                 | bit   |  |  |  |  |

| Legend:         |                                                                                                                                                      |                  |           |                   |                  |                 |       |  |  |  |  |

| R = Readable    | hit                                                                                                                                                  | W = Writable     | hit       | II = I Inimplen   | nented bit, read | 1 as 'N'        |       |  |  |  |  |

| -n = Value at I |                                                                                                                                                      | '1' = Bit is se  |           | '0' = Bit is clea |                  | r = Bit is Rese | rved  |  |  |  |  |

|                 | Ölt                                                                                                                                                  | 1 Dit io oo      |           |                   |                  |                 |       |  |  |  |  |

| bit 15-14       | Unimplemer                                                                                                                                           | nted: Read as    | '0'       |                   |                  |                 |       |  |  |  |  |

| bit 13          | CSIDL: Stop                                                                                                                                          | o in Idle Mode I | oit       |                   |                  |                 |       |  |  |  |  |

|                 | 1 = Discontinue module operation when device enters Idle mode                                                                                        |                  |           |                   |                  |                 |       |  |  |  |  |

|                 |                                                                                                                                                      | module opera     |           |                   |                  |                 |       |  |  |  |  |

| bit 12          | ABAT: Abort All Pending Transmissions bit                                                                                                            |                  |           |                   |                  |                 |       |  |  |  |  |

|                 | <ul> <li>1 = Signal all transmit buffers to abort transmission</li> <li>0 = Module will clear this bit when all transmissions are aborted</li> </ul> |                  |           |                   |                  |                 |       |  |  |  |  |

| bit 11          | Reserved: D                                                                                                                                          |                  |           |                   |                  |                 |       |  |  |  |  |

| bit 10-8        | <b>REQOP&lt;2:0&gt;:</b> Request Operation Mode bits                                                                                                 |                  |           |                   |                  |                 |       |  |  |  |  |

|                 | 111 = Set Listen All Messages mode                                                                                                                   |                  |           |                   |                  |                 |       |  |  |  |  |

|                 | 110 = Reserved - do not use                                                                                                                          |                  |           |                   |                  |                 |       |  |  |  |  |

|                 | 101 = Reserved - do not use                                                                                                                          |                  |           |                   |                  |                 |       |  |  |  |  |

|                 | 100 = Set Configuration mode                                                                                                                         |                  |           |                   |                  |                 |       |  |  |  |  |

|                 | 011 = Set Listen Only Mode<br>010 = Set Loopback mode                                                                                                |                  |           |                   |                  |                 |       |  |  |  |  |

|                 | 001 = Set Disable mode                                                                                                                               |                  |           |                   |                  |                 |       |  |  |  |  |

|                 | 000 = Set Normal Operation mode                                                                                                                      |                  |           |                   |                  |                 |       |  |  |  |  |

| bit 7-5         | OPMODE<2:0>: Operation Mode bits                                                                                                                     |                  |           |                   |                  |                 |       |  |  |  |  |

|                 | 111 = Module is in Listen All Messages mode                                                                                                          |                  |           |                   |                  |                 |       |  |  |  |  |

|                 | 110 = Reserved<br>101 = Reserved                                                                                                                     |                  |           |                   |                  |                 |       |  |  |  |  |

|                 | 100 = Module is in Configuration mode                                                                                                                |                  |           |                   |                  |                 |       |  |  |  |  |

|                 | 011 = Module is in Listen Only mode                                                                                                                  |                  |           |                   |                  |                 |       |  |  |  |  |

|                 | 010 = Module is in Loopback mode                                                                                                                     |                  |           |                   |                  |                 |       |  |  |  |  |

|                 | 001 = Module is in Disable mode<br>000 = Module is in Normal Operation mode                                                                          |                  |           |                   |                  |                 |       |  |  |  |  |

| bit 4           |                                                                                                                                                      | nted: Read as    | -         |                   |                  |                 |       |  |  |  |  |

| bit 3           | CANCAP: CAN Message Receive Timer Capture Event Enable bit                                                                                           |                  |           |                   |                  |                 |       |  |  |  |  |

|                 | 1 = Enable input capture based on CAN message receive                                                                                                |                  |           |                   |                  |                 |       |  |  |  |  |

|                 | 0 = Disable 0                                                                                                                                        |                  |           | 0                 |                  |                 |       |  |  |  |  |

| bit 2-1         | Unimplemer                                                                                                                                           | nted: Read as    | '0'       |                   |                  |                 |       |  |  |  |  |

| bit 0           | WIN: SFR M                                                                                                                                           | lap Window Se    | elect bit |                   |                  |                 |       |  |  |  |  |

|                 | 1 = Use filter window<br>0 = Use buffer window                                                                                                       |                  |           |                   |                  |                 |       |  |  |  |  |

|                 |                                                                                                                                                      |                  |           |                   |                  |                 |       |  |  |  |  |

### REGISTER 19-1: CiCTRL1: ECAN™ CONTROL REGISTER 1

| U-0               | U-0                                                                                                                                                                        | U-0              | U-0 | R-0              | R-0                  | R-0      | R-0                |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|------------------|----------------------|----------|--------------------|--|--|--|

| _                 | —                                                                                                                                                                          | _                | —   | SLOT<3:0>        |                      |          |                    |  |  |  |

| bit 15            |                                                                                                                                                                            |                  |     |                  |                      |          | bit                |  |  |  |

| U-0               | U-0                                                                                                                                                                        | U-0              | U-0 | R-0              | R-0                  | R-0      | R-0                |  |  |  |

|                   | —                                                                                                                                                                          | _                | _   | ROV              | RFUL                 | TUNF     | TMPTY              |  |  |  |

| bit 7             |                                                                                                                                                                            |                  |     |                  |                      |          | bit                |  |  |  |

| Legend:           |                                                                                                                                                                            |                  |     |                  |                      |          |                    |  |  |  |

| R = Readab        | le bit                                                                                                                                                                     | W = Writable     | bit | U = Unimpler     | mented bit, read     | d as '0' |                    |  |  |  |

| -n = Value at POR |                                                                                                                                                                            | '1' = Bit is set | t   | '0' = Bit is cle | '0' = Bit is cleared |          | x = Bit is unknown |  |  |  |