Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| Detalls                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 18x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128gp206a-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"dsPlC33F/PlC24H Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

Note: To access the documents listed below, browse to the documentation section of the dsPIC33FJ256GP710A product page on the Microchip web site (www.microchip.com) or select a family reference manual section from the following list.

> In addition to parameters, features, and other documentation, the resulting page provides links to the related family reference manual sections.

- Section 1. "Introduction" (DS70197)

- Section 2. "CPU" (DS70204)

- Section 3. "Data Memory" (DS70202)

- Section 4. "Program Memory" (DS70203)

- Section 5. "Flash Programming" (DS70191)

- Section 6. "Interrupts" (DS70184)

- Section 7. "Oscillator" (DS70186)

- Section 8. "Reset" (DS70192)

- Section 9. "Watchdog Timer and Power-Saving Modes" (DS70196)

- Section 10. "I/O Ports" (DS70193)

- Section 11. "Timers" (DS70205)

- Section 12. "Input Capture" (DS70198)

- Section 13. "Output Compare" (DS70209)

- Section 16. "Analog-to-Digital Converter (ADC)" (DS70183)

- Section 17. "UART" (DS70188)

- Section 18. "Serial Peripheral Interface (SPI)" (DS70206)

- Section 19. "Inter-Integrated Circuit<sup>™</sup> (I2C<sup>™</sup>)" (DS70195)

- Section 20. "Data Converter Interface (DCI)" (DS70288)

- Section 21. "Enhanced Controller Area Network (ECAN™)" (DS70185)

- Section 22. "Direct Memory Access (DMA)" (DS70182)

- Section 23. "CodeGuard™ Security" (DS70199)

- Section 24. "Programming and Diagnostics" (DS70207)

- Section 25. "Device Configuration" (DS70194)

### TABLE 4-27: PORTC REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|-----------|------|---------|---------|---------|---------|--------|--------|-------|-------|-------|-------|-------|--------|--------|--------|--------|-------|---------------|

| TRISC     | 02CC | TRISC15 | TRISC14 | TRISC13 | TRISC12 |        | _      |       |       | _     | —     |       | TRISC4 | TRISC3 | TRISC2 | TRISC1 |       | F01E          |

| PORTC     | 02CE | RC15    | RC14    | RC13    | RC12    | _      | _      | _     | -     | _     | _     | _     | RC4    | RC3    | RC2    | RC1    | _     | xxxx          |

| LATC      | 02D0 | LATC15  | LATC14  | LATC13  | LATC12  |        |        | _     |       | _     | _     | -     | LATC4  | LATC3  | LATC2  | LATC1  |       | xxxx          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

### TABLE 4-28: PORTD REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISD     | 02D2 | TRISD15 | TRISD14 | TRISD13 | TRISD12 | TRISD11 | TRISD10 | TRISD9 | TRISD8 | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | FFFF          |

| PORTD     | 02D4 | RD15    | RD14    | RD13    | RD12    | RD11    | RD10    | RD9    | RD8    | RD7    | RD6    | RD5    | RD4    | RD3    | RD2    | RD1    | RD0    | xxxx          |

| LATD      | 02D6 | LATD15  | LATD14  | LATD13  | LATD12  | LATD11  | LATD10  | LATD9  | LATD8  | LATD7  | LATD6  | LATD5  | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  | xxxx          |

| ODCD      | 06D2 | ODCD15  | ODCD14  | ODCD13  | ODCD12  | ODCD11  | ODCD10  | ODCD9  | ODCD8  | ODCD7  | ODCD6  | ODCD5  | ODCD4  | ODCD3  | ODCD2  | ODCD1  | ODCD0  | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

### TABLE 4-29: PORTE REGISTER MAP<sup>(1)</sup>

|           | -    | -      |        |        |        |        |        |       |       |        |        |        |        |        |        |        |        |               |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| TRISE     | 02D8 | —      | —      | —      | —      | —      | _      | _     | —     | TRISE7 | TRISE6 | TRISE5 | TRISE4 | TRISE3 | TRISE2 | TRISE1 | TRISE0 | OOFF          |

| PORTE     | 02DA | _      | _      | _      | _      | _      | _      | _     | _     | RE7    | RE6    | RE5    | RE4    | RE3    | RE2    | RE1    | RE0    | xxxx          |

| LATE      | 02DC | _      | _      | _      | _      | _      | _      | _     | _     | LATE7  | LATE6  | LATE5  | LATE4  | LATE3  | LATE2  | LATE1  | LATE0  | xxxx          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

### TABLE 4-30: PORTF REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All Resets |

|-----------|------|--------|--------|---------|---------|--------|--------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| TRISF     | 02DE | _      | _      | TRISF13 | TRISF12 | _      | -      | _     | TRISF8 | TRISF7 | TRISF6 | TRISF5 | TRISF4 | TRISF3 | TRISF2 | TRISF1 | TRISF0 | 31FF       |

| PORTF     | 02E0 | _      | _      | RF13    | RF12    | _      | _      | _     | RF8    | RF7    | RF6    | RF5    | RF4    | RF3    | RF2    | RF1    | RF0    | xxxx       |

| LATF      | 02E2 | _      | _      | LATF13  | LATF12  | _      | _      | _     | LATF8  | LATF7  | LATF6  | LATF5  | LATF4  | LATF3  | LATF2  | LATF1  | LATF0  | xxxx       |

| ODCF      | 06DE | _      | _      | ODCF13  | ODCF12  | _      | _      | _     | ODCF8  | ODCF7  | ODCF6  | ODCF5  | ODCF4  | ODCF3  | ODCF2  | ODCF1  | ODCF0  | 0000       |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

### 4.2.7 SOFTWARE STACK

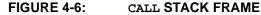

In addition to its use as a working register, the W15 register in the dsPIC33FJXXXGPX06A/X08A/X10A devices is also used as a software Stack Pointer. The Stack Pointer always points to the first available free word and grows from lower to higher addresses. It pre-decrements for stack pops and post-increments for stack pushes, as shown in Figure 4-6. For a PC push during any CALL instruction, the MSb of the PC is zero-extended before the push, ensuring that the MSb is always clear.

**Note:** A PC push during exception processing concatenates the SRL register to the MSb of the PC prior to the push.

The Stack Pointer Limit register (SPLIM) associated with the Stack Pointer sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' because all stack operations must be word-aligned. Whenever an EA is generated using W15 as a source or destination pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation. Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address 0x2000 in RAM, initialize the SPLIM with the value 0x1FFE.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0x0800. This prevents the stack from interfering with the Special Function Register (SFR) space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

#### 4.2.8 DATA RAM PROTECTION FEATURE

The dsPIC33F product family supports Data RAM protection features which enable segments of RAM to be protected when used in conjunction with Boot and Secure Code Segment Security. BSRAM (Secure RAM segment for BS) is accessible only from the Boot Segment Flash code when enabled. SSRAM (Secure RAM segment for RAM) is accessible only from the Secure Segment Flash code when enabled. See Table 4-1 for an overview of the BSRAM and SSRAM SFRs.

#### 4.3 Instruction Addressing Modes

The addressing modes in Table 4-35 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions are somewhat different from those in the other instruction types.

### 4.3.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file reg-

# 7.0 INTERRUPT CONTROLLER

- **Note 1:** This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/X08A/ X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 6. "Interrupts" (DS70184) in the "dsPIC33F/PIC24H Familv Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33FJXXXGPX06A/X08A/X10A interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33FJXXXGPX06A/X08A/X10A CPU. It has the following features:

- Up to eight processor exceptions and software traps

- Seven user-selectable priority levels

- Interrupt Vector Table (IVT) with up to 118 vectors

- A unique vector for each interrupt or exception source

- · Fixed priority within a specified user priority level

- Alternate Interrupt Vector Table (AIVT) for debug support

- · Fixed interrupt entry and return latencies

### 7.1 Interrupt Vector Table

The Interrupt Vector Table is shown in Figure 7-1. The IVT resides in program memory, starting at location 000004h. The IVT contains 126 vectors consisting of eight non-maskable trap vectors plus up to 118 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority; this priority is linked to their position in the vector table. All other things being equal, lower addresses have a higher natural priority. For example, the interrupt associated with vector 0 will take priority over interrupts at any other vector address.

dsPIC33FJXXXGPX06A/X08A/X10A devices implement up to 67 unique interrupts and five non-maskable traps. These are summarized in Table 7-1 and Table 7-2.

### 7.1.1 ALTERNATE VECTOR TABLE

The Alternate Interrupt Vector Table (AIVT) is located after the IVT, as shown in Figure 7-1. Access to the AIVT is provided by the ALTIVT control bit (INTCON2<15>). If the ALTIVT bit is set, all interrupt and exception processes use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors.

The AIVT supports debugging by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time. If the AIVT is not needed, the AIVT should be programmed with the same addresses used in the IVT.

# 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33FJXXXGPX06A/X08A/X10A device clears its registers in response to a Reset, which forces the PC to zero. The digital signal controller then begins program execution at location 0x000000. The user programs a GOTO instruction at the Reset address which redirects program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT and AIVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

| R/W-0         | R/W-0          | U-0                             | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

|---------------|----------------|---------------------------------|------------------|------------------|------------------|-----------------|---------|

| T6IF          | DMA4IF         |                                 | OC8IF            | OC7IF            | OC6IF            | OC5IF           | IC6IF   |

| bit 15        |                |                                 |                  |                  | •                |                 | bit     |

|               |                |                                 |                  |                  |                  |                 |         |

| R/W-0         | R/W-0          | R/W-0                           | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

| IC5IF         | IC4IF          | IC3IF                           | DMA3IF           | C1IF             | C1RXIF           | SPI2IF          | SPI2EIF |

| bit 7         |                |                                 |                  |                  |                  |                 | bit     |

| Legend:       |                |                                 |                  |                  |                  |                 |         |

| R = Readable  | e bit          | W = Writable                    | bit              | U = Unimplei     | mented bit, read | as '0'          |         |

| -n = Value at | POR            | '1' = Bit is set                |                  | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

|               |                |                                 |                  |                  |                  |                 |         |

| bit 15        |                | Interrupt Flag                  |                  |                  |                  |                 |         |

|               |                | equest has oc                   |                  |                  |                  |                 |         |

| bit 11        | •              | equest has no                   |                  | amplata Intorr   | unt Flog Status  | hit.            |         |

| bit 14        |                | equest has oc                   |                  |                  | upt Flag Status  | DIL             |         |

|               |                | equest has no                   |                  |                  |                  |                 |         |

| bit 13        | Unimplemen     | ted: Read as '                  | 0'               |                  |                  |                 |         |

| bit 12        | OC8IF: Outpu   | ut Compare Ch                   | annel 8 Interr   | upt Flag Status  | s bit            |                 |         |

|               |                | equest has oc                   |                  |                  |                  |                 |         |

| L:1 11        | •              | equest has no                   |                  | unt Flag Otation | - h:+            |                 |         |

| bit 11        | •              | request has oc                  |                  | upt Flag Status  |                  |                 |         |

|               | •              | equest has no                   |                  |                  |                  |                 |         |

| bit 10        | OC6IF: Outpu   | ut Compare Ch                   | annel 6 Interr   | upt Flag Status  | s bit            |                 |         |

|               | •              | equest has oc<br>equest has no  |                  |                  |                  |                 |         |

| bit 9         | •              | •                               |                  | upt Flag Status  | s bit            |                 |         |

|               | -              | equest has oc                   |                  | apt i lag olalat |                  |                 |         |

|               |                | equest has no                   |                  |                  |                  |                 |         |

| bit 8         | -              | Capture Chann                   | -                | -lag Status bit  |                  |                 |         |

|               |                | equest has oc                   |                  |                  |                  |                 |         |

| bit 7         | •              | equest has no<br>Capture Chann  |                  | -lag Status hit  |                  |                 |         |

|               |                | equest has oc                   |                  | lay Status bit   |                  |                 |         |

|               |                | equest has no                   |                  |                  |                  |                 |         |

| bit 6         | IC4IF: Input C | Capture Chann                   | el 4 Interrupt F | Flag Status bit  |                  |                 |         |

|               | •              | equest has oc                   |                  |                  |                  |                 |         |

| L:1 F         | -              | equest has no                   |                  | The Otative hit  |                  |                 |         |

| bit 5         |                | Capture Chann<br>request has oc | -                | -lag Status bit  |                  |                 |         |

|               | •              | equest has no                   |                  |                  |                  |                 |         |

| bit 4         | DMA3IF: DM     | A Channel 3 D                   | ata Transfer C   | Complete Interr  | upt Flag Status  | bit             |         |

|               |                | equest has oc                   |                  |                  |                  |                 |         |

| L:1 0         | -              | equest has no                   |                  | L :4             |                  |                 |         |

| bit 3         |                | Event Interrup                  | -                | JIC              |                  |                 |         |

|               |                | equest has oc<br>equest has no  |                  |                  |                  |                 |         |

### 11.2 Open-Drain Configuration

In addition to the PORT, LAT and TRIS registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired 5V tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See the "**Pin Diagrams**" section for the available pins and their functionality.

### 11.3 Configuring Analog Port Pins

The use of the ADxPCFGH, ADxPCFGL and TRIS registers control the operation of the ADC port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) is converted.

Clearing any bit in the ADxPCFGH or ADxPCFGL register configures the corresponding bit to be an analog pin. This is also the Reset state of any I/O pin that has an analog (ANx) function associated with it.

| Note: | In devices with two ADC modules, if the     |

|-------|---------------------------------------------|

|       | corresponding PCFG bit in either            |

|       | AD1PCFGH(L) and AD2PCFGH(L) is              |

|       | cleared, the pin is configured as an analog |

|       | input.                                      |

When reading the PORT register, all pins configured as analog input channels will read as cleared (a low level).

Pins configured as digital inputs will not convert an analog input. Analog levels on any pin that is defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

| Note: | The voltage on an analog input pin can be |

|-------|-------------------------------------------|

|       | between -0.3V to (VDD + 0.3 V).           |

### 11.4 I/O Port Write/Read Timing

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP.

### 11.5 Input Change Notification

The input change notification function of the I/O ports allows the dsPIC33FJXXXGPX06A/X08A/X10A devices to generate interrupt requests to the processor in response to a change-of-state on selected input pins. This feature is capable of detecting input change-of-states even in Sleep mode, when the clocks are disabled. Depending on the device pin count, there are up to 24 external signals (CN0 through CN23) that can be selected (enabled) for generating an interrupt request on a change-of-state.

There are four control registers associated with the CN module. The CNEN1 and CNEN2 registers contain the CN interrupt enable (CNxIE) control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up connected to it. The pull-ups act as a current source that is connected to the pin and eliminate the need for external resistors when push button or keypad devices are connected. The pull-ups are enabled separately using the CNPU1 and CNPU2 registers, which contain the weak pull-up enable (CNxPUE) bits for each of the CN pins. Setting any of the control bits enables the weak pull-ups for the corresponding pins.

Note: Pull-ups on change notification pins should always be disabled whenever the port pin is configured as a digital output.

### EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

| MOV  | 0xFF00, W0 | ; | Configure PORTB<15:8> as inputs |

|------|------------|---|---------------------------------|

| MOV  | W0, TRISBB | ; | and PORTB<7:0> as outputs       |

| NOP  |            | ; | Delay 1 cycle                   |

| btss | PORTB, #13 | i | Next Instruction                |

|      |            |   |                                 |

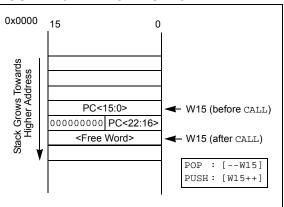

## 15.0 OUTPUT COMPARE

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/ X08A/X10A families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 13. "Output Compare" (DS70209) of the *"dsPIC33F/PIC24H Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The output compare module can select either Timer2 or Timer3 for its time base. The module compares the value of the timer with the value of one or two Compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the Compare register value. The output compare module generates either a single output pulse, or a sequence of output pulses, by changing the state of the output pin on the compare match events. The output compare module can also generate interrupts on compare match events.

The output compare module has multiple operating modes:

- Active-Low One-Shot mode

- Active-High One-Shot mode

- Toggle mode

- Delayed One-Shot mode

- Continuous Pulse mode

- PWM mode without Fault Protection

- · PWM mode with Fault Protection

### FIGURE 15-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM

# 17.0 INTER-INTEGRATED CIRCUIT™ (I<sup>2</sup>C™)

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/X08A/ X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 19. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70195) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Inter-Integrated Circuit ( $I^2C$ ) module provides complete hardware support for both Slave and Multi-Master modes of the  $I^2C$  serial communication standard, with a 16-bit interface.

The dsPIC33FJXXXGPX06A/X08A/X10A devices have up to two I<sup>2</sup>C interface modules, denoted as I2C1 and I2C2. Each I<sup>2</sup>C module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each  $I^2C$  module 'x' (x = 1 or 2) offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Port allows bidirectional transfers between master and slaves

- Serial clock synchronization for I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation; detects bus collision and will arbitrate accordingly

## 17.1 Operating Modes

The hardware fully implements all the master and slave functions of the  $I^2C$  Standard and Fast mode specifications, as well as 7 and 10-bit addressing.

The  $I^2C$  module can operate either as a slave or a master on an  $I^2C$  bus.

The following types of I<sup>2</sup>C operation are supported:

- I<sup>2</sup>C slave operation with 7-bit addressing

- I<sup>2</sup>C slave operation with 10-bit addressing

- I<sup>2</sup>C master operation with 7-bit or 10-bit addressing

For details about the communication sequence in each of these modes, please refer to the "*dsPIC33F/PIC24H Family Reference Manual*".

### REGISTER 18-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 4   | URXINV: Receive Polarity Inversion bit<br>1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                 |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                    |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul> |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                         |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                      |

| bit 0   | STSEL: Stop Bit Selection bit<br>1 = Two Stop bits<br>0 = One Stop bit                                                                                                             |

- **Note 1:** Refer to **Section 17. "UART**" (DS70188) in the *"dsPIC33F/PIC24H Family Reference Manual"* for information on enabling the UART module for receive or transmit operation.

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

### REGISTER 19-22: CiRXFUL1: ECAN™ RECEIVE BUFFER FULL REGISTER 1

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXFUL15 | RXFUL14 | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10 | RXFUL9 | RXFUL8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| RXFUL7 | RXFUL6 | RXFUL5 | RXFUL4 | RXFUL3 | RXFUL2 | RXFUL1 | RXFUL0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           | C = Clear only bit |                                                   |                    |  |  |

|-------------------|--------------------|---------------------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit   | = Writable bit U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set   | '0' = Bit is cleared                              | x = Bit is unknown |  |  |

bit 15-0

RXFUL15:RXFUL0: Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (clear by application software)

### REGISTER 19-23: CIRXFUL2: ECAN™ RECEIVE BUFFER FULL REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXFUL31 | RXFUL30 | RXFUL29 | RXFUL28 | RXFUL27 | RXFUL26 | RXFUL25 | RXFUL24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXFUL23 | RXFUL22 | RXFUL21 | RXFUL20 | RXFUL19 | RXFUL18 | RXFUL17 | RXFUL16 |

| bit 7   | •       |         |         |         |         |         | bit 0   |

| Legend:           | C = Clear only bit |                       |                    |

|-------------------|--------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit   | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set   | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **RXFUL31:RXFUL16:** Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (clear by application software)

### **REGISTER 21-1:** ADxCON1: ADCx CONTROL REGISTER 1 (where x = 1 or 2)

| R/W-0  | U-0   | R/W-0  | R/W-0   | U-0   | R/W-0 | R/W-0 | R/W-0  |

|--------|-------|--------|---------|-------|-------|-------|--------|

| ADON   | —     | ADSIDL | ADDMABM | —     | AD12B | FORM  | /<1:0> |

| bit 15 |       |        |         |       |       |       | bit 8  |

|        |       |        |         |       |       |       |        |

| R/W-0  | R/W-0 | R/W-0  | U-0     | R/W-0 | R/W-0 | R/W-0 | R/C-0  |

|        |       |        |         |       |       | HC HS | HC HS  |

|           |   |        |      | HC,HS | HC, HS |

|-----------|---|--------|------|-------|--------|

| SSRC<2:0> | _ | SIMSAM | ASAM | SAMP  | DONE   |

| bit 7     |   |        |      |       | bit 0  |

| Legend: HC = Cleared by hardw |                  | HS = Set by hardware               | C = Clear only bit |  |

|-------------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit              | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR             | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 15  | ADON: ADC Operating Mode bit                                                                                                                                                                                       |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = ADC module is operating                                                                                                                                                                                        |

|         | 0 = ADC is off                                                                                                                                                                                                     |

| bit 14  | Unimplemented: Read as '0'                                                                                                                                                                                         |

| bit 13  | ADSIDL: Stop in Idle Mode bit                                                                                                                                                                                      |

|         | <ul> <li>1 = Discontinue module operation when device enters Idle mode</li> <li>0 = Continue module operation in Idle mode</li> </ul>                                                                              |

| bit 12  | ADDMABM: DMA Buffer Build Mode bit                                                                                                                                                                                 |

|         | 1 = DMA buffers are written in the order of conversion. The module will provide an address to the DMA                                                                                                              |

|         | channel that is the same as the address used for the non-DMA stand-alone buffer                                                                                                                                    |

|         | <ul> <li>DMA buffers are written in Scatter/Gather mode. The module will provide a scatter/gather address<br/>to the DMA channel, based on the index of the analog input and the size of the DMA buffer</li> </ul> |

| bit 11  | Unimplemented: Read as '0'                                                                                                                                                                                         |

| bit 10  | AD12B: 10-Bit or 12-Bit Operation Mode bit                                                                                                                                                                         |

|         | 1 = 12-bit, 1-channel ADC operation                                                                                                                                                                                |

|         | 0 = 10-bit, 4-channel ADC operation                                                                                                                                                                                |

| bit 9-8 | FORM<1:0>: Data Output Format bits                                                                                                                                                                                 |

|         | For 10-bit operation:                                                                                                                                                                                              |

|         | 11 = Signed fractional (Dout = sddd dddd dd00 0000, where s = .NOT.d<9>)<br>10 = Fractional (Dout = dddd dddd dd00 0000)                                                                                           |

|         | 01 = Signed integer (DOUT = ssss sssd dddd dddd, where s = .NOT.d<9>)                                                                                                                                              |

|         | 00 = Integer (DOUT = 0000 00dd dddd dddd)                                                                                                                                                                          |

|         | For 12-bit operation:                                                                                                                                                                                              |

|         | 11 = Signed fractional (DOUT = sddd dddd dddd 0000, where $s = .NOT.d<11>$ )                                                                                                                                       |

|         | 10 = Fractional (Dout = dddd  dddd  dddd  0000)<br>01 = Signed Integer (Dout = ssss  sddd  dddd  dddd, where s = .NOT.d<11>)                                                                                       |

|         | 00 = Integer (DOUT = 0000 dddd dddd dddd)                                                                                                                                                                          |

| bit 7-5 | SSRC<2:0>: Sample Clock Source Select bits                                                                                                                                                                         |

|         | 111 = Internal counter ends sampling and starts conversion (auto-convert)                                                                                                                                          |

|         | 110 = Reserved                                                                                                                                                                                                     |

|         | 101 = Reserved                                                                                                                                                                                                     |

|         | 100 = GP timer (Timer5 for ADC1, Timer3 for ADC2) compare ends sampling and starts conversion<br>011 = Reserved                                                                                                    |

|         | 010 = GP timer (Timer3 for ADC1, Timer5 for ADC2) compare ends sampling and starts conversion                                                                                                                      |

|         | 001 = Active transition on INTO pin ends sampling and starts conversion                                                                                                                                            |

|         | 000 = Clearing sample bit ends sampling and starts conversion                                                                                                                                                      |

| bit 4   | Unimplemented: Read as '0'                                                                                                                                                                                         |

|         |                                                                                                                                                                                                                    |

### REGISTER 21-2: ADxCON2: ADCx CONTROL REGISTER 2 (where x = 1 or 2)

| R/W-0         | R/W-0                      | R/W-0                           | U-0                                           | U-0             | R/W-0             | R/W-0             | R/W-0        |

|---------------|----------------------------|---------------------------------|-----------------------------------------------|-----------------|-------------------|-------------------|--------------|

| VCFG<2:0>     |                            |                                 |                                               |                 | CSCNA             | CHPS              | 6<1:0>       |

| bit 15        |                            |                                 |                                               | •               |                   |                   | bit 8        |

| R-0           | U-0                        | R/W-0                           | R/W-0                                         | R/W-0           | R/W-0             | R/W-0             | R/W-0        |

| BUFS          | —                          |                                 | SMP                                           | <3:0>           |                   | BUFM              | ALTS         |

| bit 7         |                            |                                 |                                               |                 |                   | 1                 | bit (        |

| Legend:       |                            |                                 |                                               |                 |                   |                   |              |

| R = Readable  | e bit                      | W = Writabl                     | e bit                                         | U = Unimple     | mented bit, rea   | d as '0'          |              |

| -n = Value at | POR                        | '1' = Bit is s                  | et                                            | '0' = Bit is cl | eared             | x = Bit is unkr   | nown         |

| bit 15-13     | VCFG<2:0>:                 | : Converter Vo                  | oltage Reference                              | Configuration   | n bits            |                   |              |

|               |                            | VREF+                           | VREF-                                         |                 |                   |                   |              |

|               | 000                        | Avdd                            | Avss                                          |                 |                   |                   |              |

|               | 001 Exte                   | ernal VREF+                     | Avss                                          |                 |                   |                   |              |

|               | 010                        | Avdd                            | External VREF-                                |                 |                   |                   |              |

|               | 011 Exte                   | ernal VREF+                     | External VREF-                                |                 |                   |                   |              |

|               | 1xx                        | Avdd                            | Avss                                          |                 |                   |                   |              |

| bit 12-11     | Unimpleme                  | nted: Read as                   | <b>s</b> 'O'                                  |                 |                   |                   |              |

| bit 10        | CSCNA: Sca                 | an Input Selec                  | tions for CH0+ d                              | uring Sample    | A bit             |                   |              |

|               | 1 = Scan inp               |                                 |                                               |                 |                   |                   |              |

|               | 0 = Do not s               | •                               |                                               |                 |                   |                   |              |

| bit 9-8       |                            |                                 | nnels Utilized bits                           |                 |                   |                   |              |

|               |                            |                                 | < <b>1:0&gt; is: U-0, Ur</b><br>, CH2 and CH3 | nimplemente     | d, Read as '0'    |                   |              |

|               |                            | rts CH0, CH1                    |                                               |                 |                   |                   |              |

|               | 00 = Conve                 | rts CH0                         |                                               |                 |                   |                   |              |

| bit 7         | BUFS: Buffe                | r Fill Status bi                | t (only valid whe                             | n BUFM = 1)     |                   |                   |              |

|               |                            |                                 | second half of b<br>first half of buffe       |                 |                   |                   |              |

| bit 6         |                            | nted: Read as                   |                                               |                 |                   |                   |              |

| bit 5-2       | SMPI<3:0>:<br>operations p |                                 | ment Rate for DN                              | /A Addresses    | bits or number    | of sample/conv    | version      |

|               |                            | -                               | MA address or g                               | enerates inter  | rrupt after comp  | pletion of every  | 16th sample  |

|               | conv                       | ersion operat                   | ion                                           |                 |                   |                   |              |

|               |                            | ements the DI<br>/ersion operat | VA address or g<br>ion                        | enerates inter  | rrupt after comp  | pletion of every  | 15th sample  |

|               | •                          |                                 |                                               |                 |                   |                   |              |

|               | •                          | omonto the Di                   | MA address or a                               | ionoratoa into  | rrunt offer com   | plation of over   | 2nd comple   |

|               |                            | ersion operati                  | MA address or g<br>on                         |                 | mupt alter com    | pletion of every  | / Zhu Sample |

|               | 0000 = Incre               |                                 | /A address or ge                              | enerates interr | upt after comple  | etion of every sa | ample/conver |

| bit 1         | BUFM: Buffe                | er Fill Mode Se                 | elect bit                                     |                 |                   |                   |              |

|               |                            | -                               | f buffer on first ir                          |                 | econd half of the | e buffer on nex   | t interrupt  |

|               | 0 = Always                 | starts filling bu               | ifter from the beg                            | Jinning         |                   |                   |              |

| bit 0         | -                          | -                               | ifter from the beg<br>nple Mode Selec         |                 |                   |                   |              |

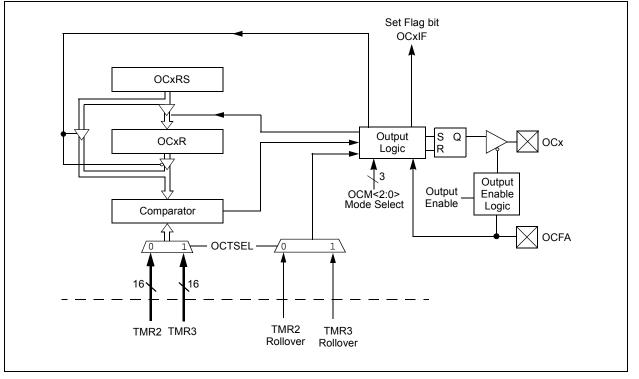

### 22.4 Watchdog Timer (WDT)

For dsPIC33FJXXXGPX06A/X08A/X10A devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler and then can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a nominal WDT time-out period (TWDT) of 1 ms in 5-bit mode, or 4 ms in 7-bit mode.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>) which allow the selection of a total of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods ranging from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSC bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

If the WDT is enabled, it will continue to run during Sleep or Idle modes. When the WDT time-out occurs, the device will wake the device and code execution will continue from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bits (RCON<3,2>) will need to be cleared in software after the device wakes up.

The WDT flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

The WDT is enabled or disabled by the FWDTEN Configuration bit in the FWDT Configuration register. When the FWDTEN Configuration bit is set, the WDT is always enabled.

The WDT can be optionally controlled in software when the FWDTEN Configuration bit has been programmed to '0'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user to enable the WDT for critical code segments and disable the WDT during non-critical segments for maximum power savings.

Note: If the WINDIS bit (FWDT<6>) is cleared, the CLRWDT instruction should be executed by the application software only during the last 1/4 of the WDT period. This CLRWDT window can be determined by using a timer. If a CLRWDT instruction is executed before this window, a WDT Reset occurs.

### FIGURE 22-2: WDT BLOCK DIAGRAM

### 24.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

### 24.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

### 24.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

### 24.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

### 24.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- Flexible macro language

- · MPLAB IDE compatibility

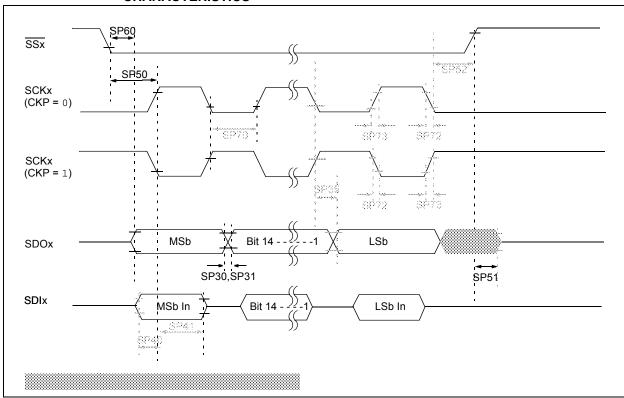

# FIGURE 25-13: SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

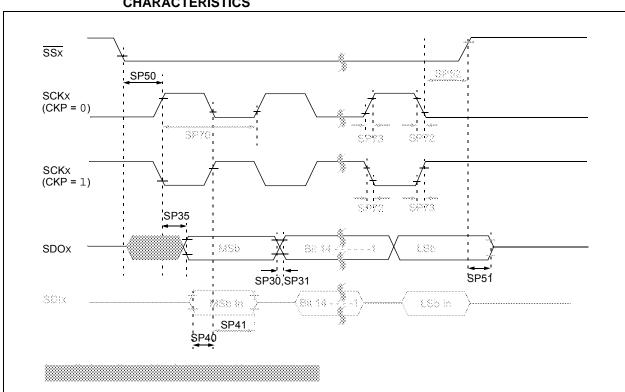

# FIGURE 25-15: SPIX SLAVE MODE (FULL-DUPLEX CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

### 26.1 High Temperature DC Characteristics

### TABLE 26-1: OPERATING MIPS VS. VOLTAGE

| Characteristic | VDD Range                   | Temperature Range | Max MIPS                     |

|----------------|-----------------------------|-------------------|------------------------------|

| Characteristic | (in Volts)                  | (in °C)           | dsPIC33FJXXXGPX06A/X08A/X10A |

| HDC5           | VBOR to 3.6V <sup>(1)</sup> | -40°C to +150°C   | 20                           |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules such as the ADC will have degraded performance. Device functionality is tested but not characterized. Refer to parameter BO10 in Table 25-11 for the minimum and maximum BOR values.

### TABLE 26-2: THERMAL OPERATING CONDITIONS

| TABLE 20-2. THERMAL OPERATING CONDITIONS                                                                                                                                               |        |               |     |      |      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|-----|------|------|

| Rating                                                                                                                                                                                 | Symbol | Min           | Тур | Max  | Unit |

| High Temperature Devices                                                                                                                                                               |        |               |     |      |      |

| Operating Junction Temperature Range                                                                                                                                                   | TJ     | -40           | —   | +155 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                    | TA     | -40           | _   | +150 | °C   |

| Power Dissipation:<br>Internal chip power dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$<br>I/O Pin Power Dissipation:<br>$I/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$ | PD     |               |     |      | W    |

| Maximum Allowed Power Dissipation                                                                                                                                                      | PDMAX  | (Tj - Ta)/θja |     |      | W    |

### TABLE 26-3: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARACTERISTICS |           |                | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |     |     |       |                 |

|--------------------|-----------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|-----------------|

| Parameter<br>No.   | Symbol    | Characteristic | Min                                                                                                                                                    | Тур | Мах | Units | Conditions      |

| Operating V        | Voltage   |                |                                                                                                                                                        |     |     |       |                 |

| HDC10              | Supply Vo | Itage          |                                                                                                                                                        |     |     |       |                 |

|                    | Vdd       | _              | 3.0                                                                                                                                                    | 3.3 | 3.6 | V     | -40°C to +150°C |

#### TABLE 26-4: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHARACTERISTICS       |                                                                                                               |      | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |            |                                     |  |  |  |

|--------------------------|---------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------------|--|--|--|

| Parameter<br>No.         | Typical                                                                                                       | Мах  | Units                                                                                                                                                  | Conditions |                                     |  |  |  |

| Power-Down Current (IPD) |                                                                                                               |      |                                                                                                                                                        |            |                                     |  |  |  |

| HDC60e                   | 250                                                                                                           | 2000 | μA                                                                                                                                                     | +150°C     | +150°C 3.3V Base Power-Down Current |  |  |  |

| Note 1. Ba               | Note 1. Base IPD is measured with all peripherals and clocks shut down. All I/Os are configured as inputs and |      |                                                                                                                                                        |            |                                     |  |  |  |

**Note 1:** Base IPD is measured with all peripherals and clocks shut down. All I/Os are configured as inputs and pulled to Vss. WDT, etc., are all switched off, and VREGS (RCON<8>) = 1.

2: The ∆ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

3: These currents are measured on the device containing the most memory in this family.

4: These parameters are characterized, but are not tested in manufacturing.

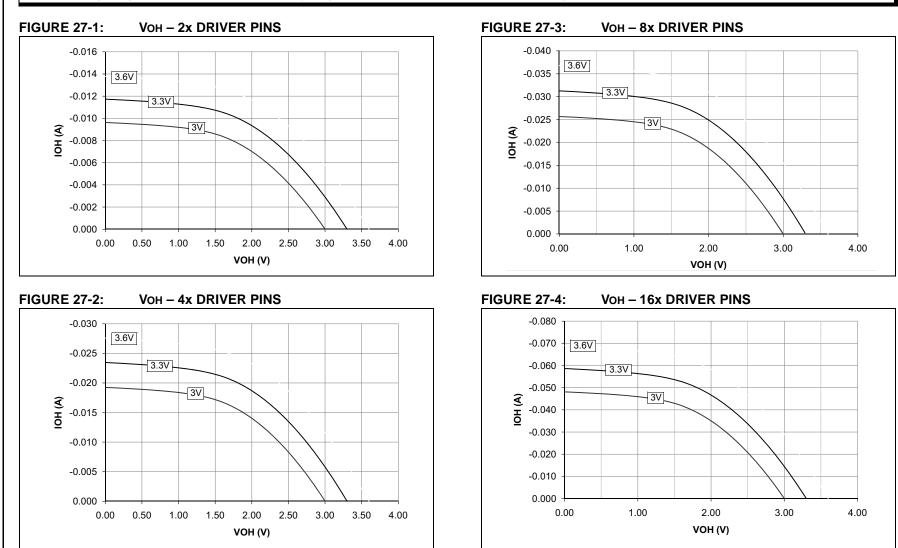

# 27.0 DC AND AC DEVICE CHARACTERISTICS GRAPHS

Note: The graphs provided following this note are a statistical summary based on a limited number of samples and are provided for design guidance purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

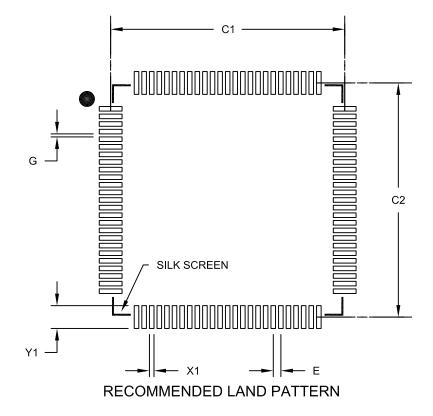

100-Lead Plastic Thin Quad Flatpack (PF) - 14x14x1 mm Body 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | MILLIMETERS |      |          |      |

|---------------------------|-------------|------|----------|------|

| Dimensior                 | MIN         | NOM  | MAX      |      |

| Contact Pitch             | E           |      | 0.50 BSC |      |

| Contact Pad Spacing       | C1          |      | 15.40    |      |

| Contact Pad Spacing       | C2          |      | 15.40    |      |

| Contact Pad Width (X100)  | X1          |      |          | 0.30 |

| Contact Pad Length (X100) | Y1          |      |          | 1.50 |

| Distance Between Pads     | G           | 0.20 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2110B

# APPENDIX B: REVISION HISTORY

### Revision A (April 2009)

This is the initial released version of the document.

### **Revision B (October 2009)**

The revision includes the following global update:

Added Note 2 to the shaded table that appears at the beginning of each chapter. This new note provides information regarding the availability of registers and their associated bits

This revision also includes minor typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in the following table.

#### TABLE B-1: MAJOR SECTION UPDATES

| Section Name                                                         | Update Description                                                                                                                                          |

|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "High-Performance, 16-Bit Digital Signal Controllers"                | Added information on high temperature operation (see " <b>Operating Range</b> ").                                                                           |

| Section 10.0 "Power-Saving Features"                                 | Updated the last paragraph to clarify the number of cycles that occur prior to the start of instruction execution (see <b>Section 10.2.2 "Idle Mode</b> "). |

| Section 11.0 "I/O Ports"                                             | Changed the reference to digital-only pins to 5V tolerant pins in the second paragraph of <b>Section 11.2</b> " <b>Open-Drain Configuration</b> ".          |

| Section 18.0 "Universal Asynchronous<br>Receiver Transmitter (UART)" | Updated the two baud rate range features to: 10 Mbps to 38 bps at 40 MIPS.                                                                                  |

| Section 21.0 "10-Bit/12-Bit<br>Analog-to-Digital Converter (ADC)"    | Updated the ADCx block diagram (see Figure 21-1).                                                                                                           |

| Section 22.0 "Special Features"                                      | Updated the second paragraph and removed the fourth paragraph in <b>Section 22.1 "Configuration Bits"</b> .                                                 |

|                                                                      | Updated the Device Configuration Register Map (see Table 22-1).                                                                                             |

|                                                                      | Added the FPWRT<2:0> bit field for the FWDT register to the Configurative Bits Description table (see Table 22-1).                                          |

| Section 25.0 "Electrical Characteristics"                            | Updated the Absolute Maximum Ratings for high temperature and added Note 4.                                                                                 |

|                                                                      | Updated Power-Down Current parameters DC60d, DC60a, DC60b, and DC60d (see Table 25-7).                                                                      |

|                                                                      | Added I2Cx Bus Data Timing Requirements (Master Mode) parameter IM51 (see Table 25-36).                                                                     |

|                                                                      | Updated the SPIx Module Slave Mode (CKE = 1) Timing Characteristics (see Figure 25-12).                                                                     |

|                                                                      | Updated the Internal LPRC Accuracy parameters (see Table 25-19).                                                                                            |

|                                                                      | Updated the ADC Module Specifications (12-bit Mode) parameters AD23a and AD24a (see Table 25-42).                                                           |

|                                                                      | Updated the ADC Module Specifications (10-bit Mode) parameters AD23b and AD24b (see Table 25-43).                                                           |

| Section 26.0 "High Temperature Electrical Characteristics"           | Added new chapter with high temperature specifications.                                                                                                     |

| "Product Identification System"                                      | Added the "H" definition for high temperature.                                                                                                              |