Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Betalls                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Active                                                                             |

| Core Processor             | dsPIC                                                                              |

| Core Size                  | 16-Bit                                                                             |

| Speed                      | 40 MIPs                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                    |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                |

| Number of I/O              | 53                                                                                 |

| Program Memory Size        | 128KB (128K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 8K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                          |

| Data Converters            | A/D 18x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 64-VFQFN Exposed Pad                                                               |

| Supplier Device Package    | 64-VQFN (9x9)                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128gp206at-i-mr |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section

2. "CPU" (DS70204) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJXXXGPX06A/X08A/X10A CPU module has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for DSP. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space. The actual amount of program memory implemented varies by device. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

The dsPIC33FJXXXGPX06A/X08A/X10A devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can serve as a data, address or address offset register. The 16th working register (W15) operates as a software Stack Pointer (SP) for interrupts and calls.

The dsPIC33FJXXXGPX06A/X08A/X10A instruction set has two classes of instructions: MCU and DSP. These two instruction classes are seamlessly integrated into a single CPU. The instruction set includes many addressing modes and is designed for optimum C compiler efficiency. For most instructions, the dsPIC33FJXXXGPX06A/X08A/X10A is capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing A + B = C operations to be executed in a single cycle.

A block diagram of the CPU is shown in Figure 3-1. The programmer's model for the dsPIC33FJXXXGPX06A/ X08A/X10A is shown in Figure 3-2.

#### 3.1 Data Addressing Overview

The data space can be addressed as 32K words or 64 Kbytes and is split into two blocks, referred to as X and Y data memory. Each memory block has its own indepen-

dent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear data space. Certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y data space boundary is device-specific.

Overhead-free circular buffers (Modulo Addressing mode) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. Furthermore, the X AGU circular addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms.

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K program word boundary defined by the 8-bit Program Space Visibility Page (PSVPAG) register. The program to data space mapping feature lets any instruction access program space as if it were data space. The data space also includes 2 Kbytes of DMA RAM, which is primarily used for DMA data transfers, but may be used as general purpose RAM.

### 3.2 DSP Engine Overview

The DSP engine features a high-speed, 17-bit by 17-bit multiplier, a 40-bit ALU, two 40-bit saturating accumulators and a 40-bit bidirectional barrel shifter. The barrel shifter is capable of shifting a 40-bit value, up to 16 bits right or left, in a single cycle. The DSP instructions operate seamlessly with all other instructions and have been designed for optimal real-time performance. The MAC instruction and other associated instructions can concurrently fetch two data operands from memory while multiplying two W registers and accumulating and optionally saturating the result in the same cycle. This instruction functionality requires that the RAM memory data space be split for these instructions and linear for all others. Data space partitioning is achieved in a transparent and flexible manner through dedicating certain working registers to each address space.

### 3.3 Special MCU Features

The dsPIC33FJXXXGPX06A/X08A/X10A features a 17-bit by 17-bit, single-cycle multiplier that is shared by both the MCU ALU and DSP engine. The multiplier can perform signed, unsigned and mixed-sign multiplication. Using a 17-bit by 17-bit multiplier for 16-bit by 16-bit multiplication not only allows you to perform mixed-sign multiplication, it also achieves accurate results for special operations, such as (-1.0) x (-1.0).

The dsPIC33FJXXXGPX06A/X08A/X10A supports 16/16 and 32/16 divide operations, both fractional and integer. All divide instructions are iterative operations. They must be executed within a REPEAT loop, resulting in a total execution time of 19 instruction cycles. The divide operation can be interrupted during any of those 19 cycles without loss of data.

A 40-bit barrel shifter is used to perform up to a 16-bit, left or right shift in a single cycle. The barrel shifter can be used by both MCU and DSP instructions.

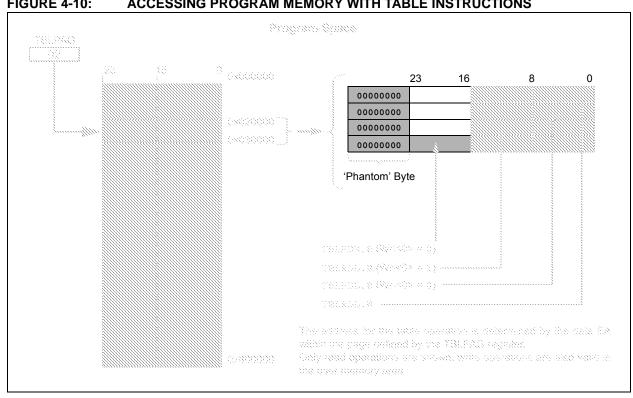

#### 4.6.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE **INSTRUCTIONS**

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit word wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the least significant data word and TBLRDH and TBLWTH access the space which contains the upper data byte.

Two table instructions are provided to move byte or word sized (16-bit) data to and from program space. Both function as either byte or word operations.

• TBLRDL (Table Read Low): In Word mode, it maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

• TBLRDH (Table Read High): In Word mode, it maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom byte', will always be '0'.

In Byte mode, it maps the upper or lower byte of the program word to D<7:0> of the data address, as above. Note that the data will always be '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in Section 5.0 "Flash Program Memory".

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

FIGURE 4-10: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

#### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

| bit 3 | ADDRERR: Address Error Trap Status bit             |

|-------|----------------------------------------------------|

|       | 1 = Address error trap has occurred                |

|       | 0 = Address error trap has not occurred            |

| bit 2 | STKERR: Stack Error Trap Status bit                |

|       | <ol> <li>Stack error trap has occurred</li> </ol>  |

|       | 0 = Stack error trap has not occurred              |

| bit 1 | <b>OSCFAIL:</b> Oscillator Failure Trap Status bit |

|       | 1 = Oscillator failure trap has occurred           |

|       | 0 = Oscillator failure trap has not occurred       |

| bit 0 | Unimplemented: Read as '0'                         |

#### REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

| bit 2 | OC1IF: Output Compare Channel 1 Interrupt Flag Status bit |

|-------|-----------------------------------------------------------|

|       | 1 = Interrupt request has occurred                        |

|       | 0 = Interrupt request has not occurred                    |

| bit 1 | IC1IF: Input Capture Channel 1 Interrupt Flag Status bit  |

|       | 1 = Interrupt request has occurred                        |

|       | 0 = Interrupt request has not occurred                    |

| bit 0 | INTOIF: External Interrupt 0 Flag Status bit              |

1 = Interrupt request has occurred0 = Interrupt request has not occurred

© 2009-2012 Microchip Technology Inc.

| -       -       -       DMA1IP<2:0>         bit 15         U-0       R/W-1       R/W-0       U-0       R/W-1       R/W-0         -       AD1IP<2:0>       -       U1TXIP<2:0>         bit 7       -       U1TXIP<2:0>       -       U1TXIP<2:0>         bit 7       -       -       U1TXIP<2:0>       -       U1TXIP<2:0>         bit 7       -       -       U1TXIP<2:0>       -       U1TXIP<2:0>         bit 15       -       -       U1TXIP<2:0>       -       U1TXIP<2:0>         bit 7       -       -       U1ITXIP<2:0>       -       U1TXIP<2:0>         bit 15-11       Unimplemented: Read as '0'       -       -       -       -         bit 10-8       DMA1IP       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | U-0          | U-0                   | U-0                 | U-0            | U-0               | R/W-1             | R/W-0           | R/W-0 |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------|---------------------|----------------|-------------------|-------------------|-----------------|-------|--|--|

| U-0       R/W-1       R/W-0       R/W-0       U-0       R/W-1       R/W-0         —       AD1IP<2:0>       —       U1TXIP<2:0>         bit 7         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _            | _                     | _                   |                | _                 | DMA1IP<2:0>       |                 |       |  |  |

| <ul> <li>AD1IP&lt;2:0&gt; U1TXIP&lt;2:0&gt;</li> <li>bit 7</li> </ul> Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' <ul> <li>-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknow</li> </ul> bit 15-11 Unimplemented: Read as '0' bit 10-8 DMA1IP<2:0>: DMA Channel 1 Data Transfer Complete Interrupt Priority bits <ul> <li>111 = Interrupt is priority 7 (highest priority interrupt)</li> <li>.</li>     &lt;</ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 15       |                       |                     |                |                   |                   |                 | bit   |  |  |

| <ul> <li>AD1IP&lt;2:0&gt; U1TXIP&lt;2:0&gt;</li> <li>bit 7</li> <li>Legend:<br/>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br/>-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknow</li> <li>bit 15-11 Unimplemented: Read as '0'<br/>bit 10-8 DMA1IP&lt;2:0&gt;: DMA Channel 1 Data Transfer Complete Interrupt Priority bits<br/>111 = Interrupt is priority 7 (highest priority interrupt)         <ul> <li>.</li> <li>.</li></ul></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              |                       | D/M/ O              | DAM 0          | 11.0              |                   |                 |       |  |  |

| bit 7 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknow bit 15-11 Unimplemented: Read as '0' bit 10-8 DMA1IP<2:0>: DMA Channel 1 Data Transfer Complete Interrupt Priority bits 111 = Interrupt is priority 7 (highest priority interrupt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0-0          | R/VV-1                |                     | R/W-U          | 0-0               | R/W-I             |                 | R/W-0 |  |  |

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknow<br>bit 15-11 Unimplemented: Read as '0'<br>bit 10-8 DMA1IP<2:0>: DMA Channel 1 Data Transfer Complete Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <br>hit 7    |                       | AD IIF \2.0>        |                | —                 |                   | 011XIF \2.0>    | bit   |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknow<br>bit 15-11 Unimplemented: Read as '0'<br>bit 10-8 DMA1IP<2:0>: DMA Channel 1 Data Transfer Complete Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |                       |                     |                |                   |                   |                 | Dit   |  |  |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknow         bit 15-11       Unimplemented: Read as '0'         bit 10-8       DMA1IP<2:0>: DMA Channel 1 Data Transfer Complete Interrupt Priority bits         111 = Interrupt is priority 7 (highest priority interrupt)       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Legend:      |                       |                     |                |                   |                   |                 |       |  |  |

| bit 15-11 Unimplemented: Read as '0'<br>bit 10-8 DMA1IP<2:0>: DMA Channel 1 Data Transfer Complete Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R = Readab   | ole bit               | W = Writable        | bit            | U = Unimplei      | mented bit, read  | d as '0'        |       |  |  |

| bit 10-8 DMA1IP<2:0>: DMA Channel 1 Data Transfer Complete Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -n = Value a | It POR                | '1' = Bit is set    |                | '0' = Bit is cle  | eared             | x = Bit is unkr | nown  |  |  |

| bit 10-8 DMA1IP<2:0>: DMA Channel 1 Data Transfer Complete Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |                       |                     |                |                   |                   |                 |       |  |  |

| <pre>111 = Interrupt is priority 7 (highest priority interrupt) 001 = Interrupt is priority 1 000 = Interrupt source is disabled bit 7 Unimplemented: Read as '0' bit 6-4 AD1IP&lt;2:0&gt;: ADC1 Conversion Complete Interrupt Priority bits 111 = Interrupt is priority 7 (highest priority interrupt) 001 = Interrupt is priority 1 000 = Interrupt source is disabled bit 3 Unimplemented: Read as '0' bit 2-0 U1TXIP&lt;2:0&gt;: UART1 Transmitter Interrupt Priority bits 111 = Interrupt is priority 7 (highest priority interrupt) 001 = Interrupt is priority 7 (highest priority interrupt) 001 = Interrupt is priority 7 (highest priority interrupt) 001 = Interrupt is priority 7 (highest priority interrupt) 001 = Interrupt is priority 1</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              | -                     |                     |                |                   |                   |                 |       |  |  |

| <ul> <li>i. i. i</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit 10-8     |                       |                     |                | -                 | e Interrupt Prior | ity bits        |       |  |  |

| <ul> <li>bit 7</li> <li>Unimplemented: Read as '0'</li> <li>bit 6-4</li> <li>AD1IP&lt;2:0&gt;: ADC1 Conversion Complete Interrupt Priority bits         <ol> <li>111 = Interrupt is priority 7 (highest priority interrupt)</li> <li>.</li> <li>.</li></ol></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              | 111 = Interru         | upt is priority 7 ( | highest priori | ity interrupt)    |                   |                 |       |  |  |

| <ul> <li>bit 7</li> <li>Unimplemented: Read as '0'</li> <li>bit 6-4</li> <li>AD1IP&lt;2:0&gt;: ADC1 Conversion Complete Interrupt Priority bits         <ol> <li>111 = Interrupt is priority 7 (highest priority interrupt)</li> <li>.</li> <li>.</li></ol></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              | •                     |                     |                |                   |                   |                 |       |  |  |

| <ul> <li>bit 7 Unimplemented: Read as '0'</li> <li>bit 6-4 AD1IP&lt;2:0&gt;: ADC1 Conversion Complete Interrupt Priority bits         <ol> <li>111 = Interrupt is priority 7 (highest priority interrupt)</li> <li>.</li> <li>.</li> <li>.001 = Interrupt is priority 1                  000 = Interrupt source is disabled</li> </ol> </li> <li>bit 3 Unimplemented: Read as '0'         <ol> <li>Unimplemented: Read as '0'</li> <li>U1TXIP&lt;2:0&gt;: UART1 Transmitter Interrupt Priority bits             <ol> <li></li></ol></li></ol></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              | •                     |                     |                |                   |                   |                 |       |  |  |

| <ul> <li>bit 7 Unimplemented: Read as '0'</li> <li>bit 6-4 AD1IP&lt;2:0&gt;: ADC1 Conversion Complete Interrupt Priority bits <ul> <li>111 = Interrupt is priority 7 (highest priority interrupt)</li> <li>.</li> <li>.</li></ul></li></ul> |              |                       |                     |                |                   |                   |                 |       |  |  |

| bit 6-4 AD1IP<2:0>: ADC1 Conversion Complete Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              | 000 = Interru         | upt source is dis   | abled          |                   |                   |                 |       |  |  |

| <pre>111 = Interrupt is priority 7 (highest priority interrupt)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | bit 7        | Unimpleme             | nted: Read as '     | 0'             |                   |                   |                 |       |  |  |

| <ul> <li>i.</li> <li>i</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 6-4      | AD1IP<2:0>            | ADC1 Conversion     | sion Complet   | te Interrupt Prio | rity bits         |                 |       |  |  |

| <pre>000 = Interrupt source is disabled<br/>bit 3 Unimplemented: Read as '0'<br/>bit 2-0 U1TXIP&lt;2:0&gt;: UART1 Transmitter Interrupt Priority bits<br/>111 = Interrupt is priority 7 (highest priority interrupt)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              | 111 = Interru         | upt is priority 7 ( | highest priori | ity interrupt)    |                   |                 |       |  |  |

| <pre>000 = Interrupt source is disabled<br/>bit 3 Unimplemented: Read as '0'<br/>bit 2-0 U1TXIP&lt;2:0&gt;: UART1 Transmitter Interrupt Priority bits<br/>111 = Interrupt is priority 7 (highest priority interrupt)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              | •                     |                     |                |                   |                   |                 |       |  |  |

| <pre>000 = Interrupt source is disabled<br/>bit 3 Unimplemented: Read as '0'<br/>bit 2-0 U1TXIP&lt;2:0&gt;: UART1 Transmitter Interrupt Priority bits<br/>111 = Interrupt is priority 7 (highest priority interrupt)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              | •                     |                     |                |                   |                   |                 |       |  |  |

| bit 3 Unimplemented: Read as '0'<br>bit 2-0 U1TXIP<2:0>: UART1 Transmitter Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |                       |                     |                |                   |                   |                 |       |  |  |

| bit 2-0 U1TXIP<2:0>: UART1 Transmitter Interrupt Priority bits 111 = Interrupt is priority 7 (highest priority interrupt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              | 000 <b>= Interr</b> u | upt source is dis   | abled          |                   |                   |                 |       |  |  |

| <pre>111 = Interrupt is priority 7 (highest priority interrupt)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | bit 3        | Unimpleme             | nted: Read as '     | 0'             |                   |                   |                 |       |  |  |

| •<br>•<br>001 = Interrupt is priority 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit 2-0      | U1TXIP<2:0            | >: UART1 Trans      | smitter Interr | upt Priority bits |                   |                 |       |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              | 111 = Interru         | upt is priority 7 ( | highest priori | ity interrupt)    |                   |                 |       |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              | •                     |                     |                |                   |                   |                 |       |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              | •                     |                     |                |                   |                   |                 |       |  |  |

| 000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |                       |                     |                |                   |                   |                 |       |  |  |