Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 18x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-VQFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128gp306a-e-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33F PRODUCT FAMILIES

The dsPIC33F General Purpose Family of devices are ideal for a wide variety of 16-bit MCU embedded applications. The controllers with codec interfaces are well-suited for speech and audio processing applications.

The device names, pin counts, memory sizes and peripheral availability of each family are listed below, followed by their pinout diagrams.

| Device             | Pins | Program<br>Flash<br>Memory<br>(Kbyte) | RAM<br>(Kbyte) <sup>(1)</sup> | 16-bit Timer | Input Capture | Output Compare<br>Std. PWM | Codec<br>Interface | ADC             | UART | IdS | I²C™ | Enhanced<br>CAN™ | I/O Pins (Max) <sup>(2)</sup> | Packages |

|--------------------|------|---------------------------------------|-------------------------------|--------------|---------------|----------------------------|--------------------|-----------------|------|-----|------|------------------|-------------------------------|----------|

| dsPIC33FJ64GP206A  | 64   | 64                                    | 8                             | 9            | 8             | 8                          | 1                  | 1 ADC, 18<br>ch | 2    | 2   | 1    | 0                | 53                            | PT, MR   |

| dsPIC33FJ64GP306A  | 64   | 64                                    | 16                            | 9            | 8             | 8                          | 1                  | 1 ADC, 18<br>ch | 2    | 2   | 2    | 0                | 53                            | PT, MR   |

| dsPIC33FJ64GP310A  | 100  | 64                                    | 16                            | 9            | 8             | 8                          | 1                  | 1 ADC, 32<br>ch | 2    | 2   | 2    | 0                | 85                            | PF, PT   |

| dsPIC33FJ64GP706A  | 64   | 64                                    | 16                            | 9            | 8             | 8                          | 1                  | 2 ADC, 18<br>ch | 2    | 2   | 2    | 2                | 53                            | PT, MR   |

| dsPIC33FJ64GP708A  | 80   | 64                                    | 16                            | 9            | 8             | 8                          | 1                  | 2 ADC, 24<br>ch | 2    | 2   | 2    | 2                | 69                            | PT       |

| dsPIC33FJ64GP710A  | 100  | 64                                    | 16                            | 9            | 8             | 8                          | 1                  | 2 ADC, 32<br>ch | 2    | 2   | 2    | 2                | 85                            | PF, PT   |

| dsPIC33FJ128GP206A | 64   | 128                                   | 8                             | 9            | 8             | 8                          | 1                  | 1 ADC, 18<br>ch | 2    | 2   | 1    | 0                | 53                            | PT, MR   |

| dsPIC33FJ128GP306A | 64   | 128                                   | 16                            | 9            | 8             | 8                          | 1                  | 1 ADC, 18<br>ch | 2    | 2   | 2    | 0                | 53                            | PT, MR   |

| dsPIC33FJ128GP310A | 100  | 128                                   | 16                            | 9            | 8             | 8                          | 1                  | 1 ADC, 32<br>ch | 2    | 2   | 2    | 0                | 85                            | PF, PT   |

| dsPIC33FJ128GP706A | 64   | 128                                   | 16                            | 9            | 8             | 8                          | 1                  | 2 ADC, 18<br>ch | 2    | 2   | 2    | 2                | 53                            | PT, MR   |

| dsPIC33FJ128GP708A | 80   | 128                                   | 16                            | 9            | 8             | 8                          | 1                  | 2 ADC, 24<br>ch | 2    | 2   | 2    | 2                | 69                            | PT       |

| dsPIC33FJ128GP710A | 100  | 128                                   | 16                            | 9            | 8             | 8                          | 1                  | 2 ADC, 32<br>ch | 2    | 2   | 2    | 2                | 85                            | PF, PT   |

| dsPIC33FJ256GP506A | 64   | 256                                   | 16                            | 9            | 8             | 8                          | 1                  | 1 ADC, 18<br>ch | 2    | 2   | 2    | 1                | 53                            | PT, MR   |

| dsPIC33FJ256GP510A | 100  | 256                                   | 16                            | 9            | 8             | 8                          | 1                  | 1 ADC, 32<br>ch | 2    | 2   | 2    | 1                | 85                            | PF, PT   |

| dsPIC33FJ256GP710A | 100  | 256                                   | 30                            | 9            | 8             | 8                          | 1                  | 2 ADC, 32<br>ch | 2    | 2   | 2    | 2                | 85                            | PF, PT   |

Note 1: RAM size is inclusive of 2 Kbytes DMA RAM.

2: Maximum I/O pin count includes pins shared by the peripheral functions.

# 4.2 Data Address Space

The dsPIC33FJXXXGPX06A/X08A/X10A CPU has a separate 16-bit wide data memory space. The data space is accessed using separate Address Generation Units (AGUs) for read and write operations. Data memory maps of devices with different RAM sizes are shown in Figure 4-3 through Figure 4-5.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the data space. This arrangement gives a data space address range of 64 Kbytes or 32K words. The lower half of the data memory space (that is, when EA<15> = 0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the Program Space Visibility area (see Section 4.6.3 "Reading Data from Program Memory Using Program Space Visibility").

dsPIC33FJXXXGPX06A/X08A/X10A devices implement a total of up to 30 Kbytes of data memory. Should an EA point to a location outside of this area, an all-zero word or byte will be returned.

#### 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byte addressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all data space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

#### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve data space memory usage efficiency, the dsPIC33FJXXXGPX06A/X08A/X10A instruction set supports both word and byte operations. As a consequence of byte accessibility, all effective address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] will result in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

Data byte reads will read the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSb of the data path. That is, data memory and registers are organized as two parallel byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register which matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed; if it occurred on a write, the instruction will be executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the Least Significant Byte. The Most Significant Byte is not modified.

A sign-extend instruction (SE) is provided to allow users to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, users can clear the MSb of any W register by executing a zero-extend (ZE) instruction on the appropriate address.

### 4.2.3 SFR SPACE

The first 2 Kbytes of the Near Data Space, from 0x0000 to 0x07FF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33FJXXXGPX06A/X08A/X10A core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control, and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'. A complete listing of implemented SFRs, including their addresses, is shown in Table 4-1 through Table 4-34.

| Note: | The actual set of peripheral features and interrupts varies by the device. Please   |

|-------|-------------------------------------------------------------------------------------|

|       | refer to the corresponding device tables<br>and pinout diagrams for device-specific |

|       | information.                                                                        |

# 4.2.4 NEAR DATA SPACE

The 8-Kbyte area between 0x0000 and 0x1FFF is referred to as the Near Data Space. Locations in this space are directly addressable via a 13-bit absolute address field within all memory direct instructions. Additionally, the whole data space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a working register as an Address Pointer.

### 4.2.5 X AND Y DATA SPACES

The core has two data spaces, X and Y. These data spaces can be considered either separate (for some DSP instructions), or as one unified linear address range (for MCU instructions). The data spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X data space is used by all instructions and supports all addressing modes. There are separate read and write data buses for X data space. The X read data bus is the read data path for all instructions that view data space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y data space is used in concert with the X data space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths.

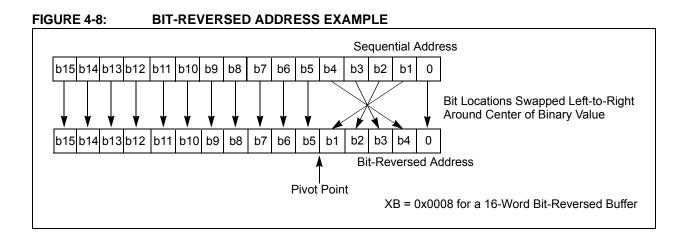

Both the X and Y data spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X data space.

All data memory writes, including in DSP instructions, view data space as combined X and Y address space. The boundary between the X and Y data spaces is device-dependent and is not user-programmable.

All effective addresses are 16 bits wide and point to bytes within the data space. Therefore, the data space address range is 64 Kbytes, or 32K words, though the implemented memory locations vary by device.

#### 4.2.6 DMA RAM

Every dsPIC33FJXXXGPX06A/X08A/X10A device contains 2 Kbytes of dual ported DMA RAM located at the end of Y data space. Memory locations is part of Y data RAM and is in the DMA RAM space are accessible simultaneously by the CPU and the DMA controller module. DMA RAM is utilized by the DMA controller to store data to be transferred to various peripherals using DMA, as well as data transferred from various peripherals using DMA. The DMA RAM can be accessed by the DMA controller without having to steal cycles from the CPU.

When the CPU and the DMA controller attempt to concurrently write to the same DMA RAM location, the hardware ensures that the CPU is given precedence in accessing the DMA RAM location. Therefore, the DMA RAM provides a reliable means of transferring DMA data without ever having to stall the CPU.

Note: DMA RAM can be used for general purpose data storage if the DMA function is not required in an application.

### TABLE 4-36: BIT-REVERSED ADDRESS SEQUENCE (16-ENTRY)

|    |    | Norm | al Addres | s       |    |    | Bit-Rev | versed Ad | dress   |

|----|----|------|-----------|---------|----|----|---------|-----------|---------|

| A3 | A2 | A1   | A0        | Decimal | A3 | A2 | A1      | A0        | Decimal |

| 0  | 0  | 0    | 0         | 0       | 0  | 0  | 0       | 0         | 0       |

| 0  | 0  | 0    | 1         | 1       | 1  | 0  | 0       | 0         | 8       |

| 0  | 0  | 1    | 0         | 2       | 0  | 1  | 0       | 0         | 4       |

| 0  | 0  | 1    | 1         | 3       | 1  | 1  | 0       | 0         | 12      |

| 0  | 1  | 0    | 0         | 4       | 0  | 0  | 1       | 0         | 2       |

| 0  | 1  | 0    | 1         | 5       | 1  | 0  | 1       | 0         | 10      |

| 0  | 1  | 1    | 0         | 6       | 0  | 1  | 1       | 0         | 6       |

| 0  | 1  | 1    | 1         | 7       | 1  | 1  | 1       | 0         | 14      |

| 1  | 0  | 0    | 0         | 8       | 0  | 0  | 0       | 1         | 1       |

| 1  | 0  | 0    | 1         | 9       | 1  | 0  | 0       | 1         | 9       |

| 1  | 0  | 1    | 0         | 10      | 0  | 1  | 0       | 1         | 5       |

| 1  | 0  | 1    | 1         | 11      | 1  | 1  | 0       | 1         | 13      |

| 1  | 1  | 0    | 0         | 12      | 0  | 0  | 1       | 1         | 3       |

| 1  | 1  | 0    | 1         | 13      | 1  | 0  | 1       | 1         | 11      |

| 1  | 1  | 1    | 0         | 14      | 0  | 1  | 1       | 1         | 7       |

| 1  | 1  | 1    | 1         | 15      | 1  | 1  | 1       | 1         | 15      |

# 5.2 RTSP Operation

The dsPIC33FJXXXGPX06A/X08A/X10A Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user to erase a page of memory, which consists of eight rows (512 instructions) at a time, and to program one row or one word at a time. Table 25-12 illustrates typical erase and programming times. The 8-row erase pages and single row write rows are edge-aligned, from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively.

The program memory implements holding buffers that can contain 64 instructions of programming data. Prior to the actual programming operation, the write data must be loaded into the buffers in sequential order. The instruction words loaded must always be from a group of 64 boundary.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register. A total of 64 TBLWTL and TBLWTH instructions are required to load the instructions.

All of the table write operations are single-word writes (two instruction cycles) because only the buffers are written. A programming cycle is required for programming each row.

# 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

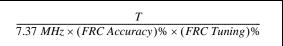

The programming time depends on the FRC accuracy (see Table 25-19) and the value of the FRC Oscillator Tuning register (see Register 9-4). Use the following formula to calculate the minimum and maximum values for the Row Write Time, Page Erase Time and Word Write Cycle Time parameters (see Table 25-12).

#### EQUATION 5-1: PROGRAMMING TIME

For example, if the device is operating at +125°C, the FRC accuracy will be  $\pm 5\%$ . If the TUN<5:0> bits (see Register 9-4) are set to `b111111, the minimum row write time is equal to Equation 5-2.

#### EQUATION 5-2: MINIMUM ROW WRITE TIME

$$T_{RW} = \frac{11064 \ Cycles}{7.37 \ MHz \times (1 + 0.05) \times (1 - 0.00375)} = 1.435 ms$$

The maximum row write time is equal to Equation 5-3.

#### EQUATION 5-3: MAXIMUM ROW WRITE TIME

$$T_{RW} = \frac{11064 \ Cycles}{7.37 \ MHz \times (1 - 0.05) \times (1 - 0.00375)} = 1.586 ms$$

Setting the WR bit (NVMCON<15>) starts the operation, and the WR bit is automatically cleared when the operation is finished.

# 5.4 Control Registers

The two SFRs that are used to read and write the program Flash memory are:

NVMCON: Flash Memory Control Register

#### • NVMKEY: Non-Volatile Memory Key Register

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and the start of the programming cycle.

NVMKEY (Register 5-2) is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 0x55 and 0xAA to the NVMKEY register. Refer to **Section 5.3 "Programming Operations"** for further details.

| -       -       -       DMA1IP<2:0>         bit 15         U-0       R/W-1       R/W-0       U-0       R/W-1       R/W-0         -       AD1IP<2:0>       -       U1TXIP<2:0>         bit 7       -       U1TXIP<2:0>       -       U1TXIP<2:0>         bit 7       -       -       U1TXIP<2:0>       -       U1TXIP<2:0>         bit 7       -       -       U1TXIP<2:0>       -       U1TXIP<2:0>         bit 15       -       -       U1TXIP<2:0>       -       U1TXIP<2:0>         bit 7       -       -       U1ITXIP<2:0>       -       U1TXIP<2:0>         bit 15-11       Unimplemented: Read as '0'       -       -       -       -         bit 10-8       DMA1IP       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | U-0          | U-0                   | U-0                 | U-0            | U-0               | R/W-1             | R/W-0           | R/W-0 |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------|---------------------|----------------|-------------------|-------------------|-----------------|-------|--|--|

| U-0       R/W-1       R/W-0       R/W-0       U-0       R/W-1       R/W-0         —       AD1IP<2:0>       —       U1TXIP<2:0>         bit 7         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _            | _                     | _                   |                | _                 | DMA1IP<2:0>       |                 |       |  |  |

| <ul> <li>AD1IP&lt;2:0&gt; U1TXIP&lt;2:0&gt;</li> <li>bit 7</li> </ul> Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' <ul> <li>-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknow</li> </ul> bit 15-11 Unimplemented: Read as '0' bit 10-8 DMA1IP<2:0>: DMA Channel 1 Data Transfer Complete Interrupt Priority bits <ul> <li>111 = Interrupt is priority 7 (highest priority interrupt)</li> <li>.</li>     &lt;</ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 15       |                       |                     |                |                   |                   |                 | bit   |  |  |

| <ul> <li>AD1IP&lt;2:0&gt; U1TXIP&lt;2:0&gt;</li> <li>bit 7</li> <li>Legend:<br/>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br/>-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknow</li> <li>bit 15-11 Unimplemented: Read as '0'<br/>bit 10-8 DMA1IP&lt;2:0&gt;: DMA Channel 1 Data Transfer Complete Interrupt Priority bits<br/>111 = Interrupt is priority 7 (highest priority interrupt)         <ul> <li>.</li> <li>.</li></ul></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              |                       |                     | DAM 0          | 11.0              |                   |                 |       |  |  |

| bit 7 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknow bit 15-11 Unimplemented: Read as '0' bit 10-8 DMA1IP<2:0>: DMA Channel 1 Data Transfer Complete Interrupt Priority bits 111 = Interrupt is priority 7 (highest priority interrupt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0-0          | R/VV-1                |                     | R/W-U          | 0-0               | R/W-I             |                 | R/W-0 |  |  |

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknow<br>bit 15-11 Unimplemented: Read as '0'<br>bit 10-8 DMA1IP<2:0>: DMA Channel 1 Data Transfer Complete Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <br>hit 7    |                       | AD IIF \2.0>        |                | —                 |                   | 011XIF \2.0>    | bit   |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknow<br>bit 15-11 Unimplemented: Read as '0'<br>bit 10-8 DMA1IP<2:0>: DMA Channel 1 Data Transfer Complete Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |                       |                     |                |                   |                   |                 | Dit   |  |  |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknow         bit 15-11       Unimplemented: Read as '0'         bit 10-8       DMA1IP<2:0>: DMA Channel 1 Data Transfer Complete Interrupt Priority bits         111 = Interrupt is priority 7 (highest priority interrupt)       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Legend:      |                       |                     |                |                   |                   |                 |       |  |  |

| bit 15-11 Unimplemented: Read as '0'<br>bit 10-8 DMA1IP<2:0>: DMA Channel 1 Data Transfer Complete Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R = Readab   | ole bit               | W = Writable        | bit            | U = Unimplei      | mented bit, read  | d as '0'        |       |  |  |

| bit 10-8 DMA1IP<2:0>: DMA Channel 1 Data Transfer Complete Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -n = Value a | It POR                | '1' = Bit is set    |                | '0' = Bit is cle  | eared             | x = Bit is unkr | nown  |  |  |

| bit 10-8 DMA1IP<2:0>: DMA Channel 1 Data Transfer Complete Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |                       |                     |                |                   |                   |                 |       |  |  |

| <pre>111 = Interrupt is priority 7 (highest priority interrupt) 001 = Interrupt is priority 1 000 = Interrupt source is disabled bit 7 Unimplemented: Read as '0' bit 6-4 AD1IP&lt;2:0&gt;: ADC1 Conversion Complete Interrupt Priority bits 111 = Interrupt is priority 7 (highest priority interrupt) 001 = Interrupt is priority 1 000 = Interrupt source is disabled bit 3 Unimplemented: Read as '0' bit 2-0 U1TXIP&lt;2:0&gt;: UART1 Transmitter Interrupt Priority bits 111 = Interrupt is priority 7 (highest priority interrupt) 001 = Interrupt is priority 7 (highest priority interrupt) 001 = Interrupt is priority 7 (highest priority interrupt) 001 = Interrupt is priority 7 (highest priority interrupt) 001 = Interrupt is priority 1</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              | -                     |                     |                |                   |                   |                 |       |  |  |

| <ul> <li>i. i. i</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit 10-8     |                       |                     |                | -                 | e Interrupt Prior | ity bits        |       |  |  |

| <ul> <li>bit 7</li> <li>Unimplemented: Read as '0'</li> <li>bit 6-4</li> <li>AD1IP&lt;2:0&gt;: ADC1 Conversion Complete Interrupt Priority bits         <ol> <li>111 = Interrupt is priority 7 (highest priority interrupt)</li> <li>.</li> <li>.</li></ol></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              | 111 = Interru         | upt is priority 7 ( | highest priori | ity interrupt)    |                   |                 |       |  |  |

| <ul> <li>bit 7</li> <li>Unimplemented: Read as '0'</li> <li>bit 6-4</li> <li>AD1IP&lt;2:0&gt;: ADC1 Conversion Complete Interrupt Priority bits         <ol> <li>111 = Interrupt is priority 7 (highest priority interrupt)</li> <li>.</li> <li>.</li></ol></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              | •                     |                     |                |                   |                   |                 |       |  |  |

| <ul> <li>bit 7 Unimplemented: Read as '0'</li> <li>bit 6-4 AD1IP&lt;2:0&gt;: ADC1 Conversion Complete Interrupt Priority bits         <ol> <li>111 = Interrupt is priority 7 (highest priority interrupt)</li> <li>.</li> <li>.</li> <li>.001 = Interrupt is priority 1                  000 = Interrupt source is disabled</li> </ol> </li> <li>bit 3 Unimplemented: Read as '0'         <ol> <li>Unimplemented: Read as '0'</li> <li>U1TXIP&lt;2:0&gt;: UART1 Transmitter Interrupt Priority bits             <ol> <li></li></ol></li></ol></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              | •                     |                     |                |                   |                   |                 |       |  |  |

| <ul> <li>bit 7 Unimplemented: Read as '0'</li> <li>bit 6-4 AD1IP&lt;2:0&gt;: ADC1 Conversion Complete Interrupt Priority bits <ul> <li>111 = Interrupt is priority 7 (highest priority interrupt)</li> <li>.</li> <li>.</li></ul></li></ul> |              |                       |                     |                |                   |                   |                 |       |  |  |

| bit 6-4 AD1IP<2:0>: ADC1 Conversion Complete Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              | 000 = Interru         | upt source is dis   | abled          |                   |                   |                 |       |  |  |

| <pre>111 = Interrupt is priority 7 (highest priority interrupt)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | bit 7        | Unimpleme             | nted: Read as '     | 0'             |                   |                   |                 |       |  |  |

| <ul> <li>i.</li> <li>i</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 6-4      | AD1IP<2:0>            | ADC1 Conversion     | sion Complet   | te Interrupt Prio | rity bits         |                 |       |  |  |

| <pre>000 = Interrupt source is disabled<br/>bit 3 Unimplemented: Read as '0'<br/>bit 2-0 U1TXIP&lt;2:0&gt;: UART1 Transmitter Interrupt Priority bits<br/>111 = Interrupt is priority 7 (highest priority interrupt)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              | 111 = Interru         | upt is priority 7 ( | highest priori | ity interrupt)    |                   |                 |       |  |  |

| <pre>000 = Interrupt source is disabled<br/>bit 3 Unimplemented: Read as '0'<br/>bit 2-0 U1TXIP&lt;2:0&gt;: UART1 Transmitter Interrupt Priority bits<br/>111 = Interrupt is priority 7 (highest priority interrupt)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              | •                     |                     |                |                   |                   |                 |       |  |  |

| <pre>000 = Interrupt source is disabled<br/>bit 3 Unimplemented: Read as '0'<br/>bit 2-0 U1TXIP&lt;2:0&gt;: UART1 Transmitter Interrupt Priority bits<br/>111 = Interrupt is priority 7 (highest priority interrupt)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              | •                     |                     |                |                   |                   |                 |       |  |  |

| bit 3 Unimplemented: Read as '0'<br>bit 2-0 U1TXIP<2:0>: UART1 Transmitter Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |                       |                     |                |                   |                   |                 |       |  |  |

| bit 2-0 U1TXIP<2:0>: UART1 Transmitter Interrupt Priority bits 111 = Interrupt is priority 7 (highest priority interrupt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              | 000 <b>= Interr</b> u | upt source is dis   | abled          |                   |                   |                 |       |  |  |

| <pre>111 = Interrupt is priority 7 (highest priority interrupt)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | bit 3        | Unimpleme             | nted: Read as '     | 0'             |                   |                   |                 |       |  |  |

| •<br>•<br>001 = Interrupt is priority 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit 2-0      | U1TXIP<2:0            | >: UART1 Trans      | smitter Interr | upt Priority bits |                   |                 |       |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              | 111 = Interru         | upt is priority 7 ( | highest priori | ity interrupt)    |                   |                 |       |  |  |